Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113ph005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the Z8 Encore! XP F0823 Series products.

| Program Memory Address (Hex) | Function                 |

|------------------------------|--------------------------|

| Z8F0823 and Z8F0813 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0423 and Z8F0413 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0223 and Z8F0213 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-07FF                    | Program Memory           |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps

Note: \*See the <u>Trap and Interrupt Vectors in Order of Priority section on page 55</u> for a list of the interrupt vectors and traps.

Embedded in Life An IXYS Company

ilog<sup>®</sup> Embedded in Life

ilog Embedded in Life An IXYS Company 17

| Address (Hex)    | Register Description      | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------|----------|-------------|-------------|

| Timer 1 (cont'd) |                           |          |             |             |

| F0A              | Timer 1 Reload High Byte  | T1RH     | FF          | <u>85</u>   |

| F0B              | Timer 1 Reload Low Byte   | T1RL     | FF          | <u>85</u>   |

| F0C              | Timer 1 PWM High Byte     | T1PWMH   | 00          | <u>86</u>   |

| F0D              | Timer 1 PWM Low Byte      | T1PWML   | 00          | <u>86</u>   |

| F0E              | Timer 1 Control 0         | T1CTL0   | 00          | <u>87</u>   |

| F0F              | Timer 1 Control 1         | T1CTL1   | 00          | <u>84</u>   |

| F10–F3F          | Reserved                  | —        | XX          |             |

| UART             |                           |          |             |             |

| F40              | UART0 Transmit Data       | U0TXD    | XX          | <u>109</u>  |

|                  | UART0 Receive Data        | U0RXD    | XX          | <u>109</u>  |

| F41              | UART0 Status 0            | U0STAT0  | 0000011Xb   | <u>110</u>  |

| F42              | UART0 Control 0           | U0CTL0   | 00          | <u>112</u>  |

| F43              | UART0 Control 1           | U0CTL1   | 00          | <u>112</u>  |

| F44              | UART0 Status 1            | U0STAT1  | 00          | <u>111</u>  |

| F45              | UART0 Address Compare     | U0ADDR   | 00          | <u>115</u>  |

| F46              | UART0 Baud Rate High Byte | U0BRH    | FF          | <u>115</u>  |

| F47              | UART0 Baud Rate Low Byte  | U0BRL    | FF          | <u>115</u>  |

| F48–F6F          | Reserved                  | —        | XX          |             |

| Analog-to-Digita | al Converter (ADC)        |          |             |             |

| F70              | ADC Control 0             | ADCCTL0  | 00          | <u>127</u>  |

| F71              | ADC Control 1             | ADCCTL1  | 80          | <u>127</u>  |

| F72              | ADC Data High Byte        | ADCD_H   | XX          | <u>130</u>  |

| F73              | ADC Data Low Bits         | ADCD_L   | XX          | <u>130</u>  |

| F74–F7F          | Reserved                  | —        | XX          |             |

| Low Power Con    | trol                      |          |             |             |

| F80              | Power Control 0           | PWRCTL0  | 80          | <u>32</u>   |

| F81              | Reserved                  | _        | XX          |             |

| LED Controller   |                           |          |             |             |

| F82              | LED Drive Enable          | LEDEN    | 00          | <u>51</u>   |

| F83              | LED Drive Level High Byte | LEDLVLH  | 00          | <u>52</u>   |

| Note: XX=Undefi  |                           |          |             |             |

#### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

ilog<sup>®</sup> Embedded in Life An∎IXYS Company 19

| Address (Hex)    | Register Description                  | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------------------|----------|-------------|-------------|

| GPIO Port B (co  | nt'd)                                 |          |             |             |

| FD6              | Port B Input Data                     | PBIN     | XX          | <u>43</u>   |

| FD7              | Port B Output Data                    | PBOUT    | 00          | <u>43</u>   |

| GPIO Port C      |                                       |          |             |             |

| FD8              | Port C Address                        | PCADDR   | 00          | <u>40</u>   |

| FD9              | Port C Control                        | PCCTL    | 00          | <u>42</u>   |

| FDA              | Port C Input Data                     | PCIN     | XX          | <u>43</u>   |

| FDB              | Port C Output Data                    | PCOUT    | 00          | <u>43</u>   |

| FDC-FEF          | Reserved                              |          | XX          |             |

| Watchdog Time    | r (WDT)                               |          |             |             |

| FF0              | Reset Status                          | RSTSTAT  | XX          | <u>94</u>   |

|                  | Watchdog Timer Control                | WDTCTL   | XX          | <u>94</u>   |

| FF1              | Watchdog Timer Reload Upper Byte      | WDTU     | FF          | <u>95</u>   |

| FF2              | Watchdog Timer Reload High Byte       | WDTH     | FF          | <u>95</u>   |

| FF3              | Watchdog Timer Reload Low Byte        | WDTL     | FF          | <u>95</u>   |

| FF4–FF5          | Reserved                              | _        | XX          |             |

| Trim Bit Control | l                                     |          |             |             |

| FF6              | Trim Bit Address                      | TRMADR   | 00          | 148         |

| FF7              | Trim Data                             | TRMDR    | XX          | <u>149</u>  |

| Flash Memory C   | Controller                            |          |             |             |

| FF8              | Flash Control                         | FCTL     | 00          | 141         |

| FF8              | Flash Status                          | FSTAT    | 00          | 142         |

| FF9              | Flash Page Select                     | FPS      | 00          | <u>143</u>  |

|                  | Flash Sector Protect                  | FPROT    | 00          | <u>144</u>  |

| FFA              | Flash Programming Frequency High Byte | FFREQH   | 00          | <u>145</u>  |

| FFB              | Flash Programming Frequency Low Byte  | FFREQL   | 00          | <u>145</u>  |

#### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

**Note:** This register is only reset during a Power-On Reset sequence. Other System Reset events do not affect it.

| Bit     | 7        | 6    | 5     | 4   | 3        | 2   | 1    | 0        |

|---------|----------|------|-------|-----|----------|-----|------|----------|

| Field   | Reserved | Rese | erved | VBO | Reserved | ADC | COMP | Reserved |

| RESET   | 1        | 0    | 0     | 0   | 0        | 0   | 0    | 0        |

| R/W     | R/W      | R/W  | R/W   | R/W | R/W      | R/W | R/W  | R/W      |

| Address | F80H     |      |       |     |          |     |      |          |

| Bit         | Description                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 1.                                                                                                      |

| [6:5]       | Reserved<br>These bits are reserved and must be programmed to 00.                                                                                                         |

| [4]<br>VBO  | Voltage Brown-Out Detector Disable<br>This bit and the VBO_AO Flash option bit must both enable the VBO for the VBO to be active<br>0 = VBO enabled.<br>1 = VBO disabled. |

| [3]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                      |

| [2]<br>ADC  | Analog-to-Digital Converter Disable<br>0 = Analog-to-Digital Converter enabled.<br>1 = Analog-to-Digital Converter disabled.                                              |

| [1]<br>COMP | Comparator Disable<br>0 = Comparator is enabled.<br>1 = Comparator is disabled.                                                                                           |

| [0]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                      |

32

An∎IXYS Company

| Port                | Pin  | Mnemonic                      | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|------|-------------------------------|--------------------------------|-----------------------------------------|

| Port B <sup>3</sup> | PB03 | Reserved                      |                                | AFS1[0]: 0                              |

|                     |      | ANA0                          | ADC Analog Input               | AFS1[0]: 1                              |

|                     | PB1  | Reserved                      |                                | AFS1[1]: 0                              |

|                     |      | ANA1                          | ADC Analog Input               | AFS1[1]: 1                              |

|                     | PB2  | Reserved                      |                                | AFS1[2]: 0                              |

|                     |      | ANA2                          | ADC Analog Input               | AFS1[2]: 1                              |

|                     | PB3  | CLKIN                         | External Clock Input           | AFS1[3]: 0                              |

|                     |      | ANA3                          | ADC Analog Input               | AFS1[3]: 1                              |

|                     | PB4  | Reserved                      |                                | AFS1[4]: 0                              |

|                     |      | ANA7                          | ADC Analog Input               | AFS1[4]: 1                              |

|                     | PB5  | Reserved                      |                                | AFS1[5]: 0                              |

|                     |      | V <sub>REF</sub> <sup>4</sup> | ADC Voltage Reference          | AFS1[5]: 1                              |

|                     | PB6  | Reserved                      |                                | AFS1[6]: 0                              |

|                     |      | Reserved                      |                                | AFS1[6]: 1                              |

|                     | PB7  | Reserved                      |                                | AFS1[7]: 0                              |

|                     |      | Reserved                      |                                | AFS1[7]: 1                              |

#### Table 17. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in the <u>Port A–C Alternate Function</u> <u>Subregisters</u> section on page 43 automatically enables the associated alternate function.

2. Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in the <u>Timer Pin Signal Operation</u> section on page 83.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, alternate function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

4. V<sub>REF</sub> is available on PB5 in 28-pin products only.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

6. V<sub>REF</sub> is available on PC2 in 20-pin parts only.

bedded in Life

40

PC[2:0]. All other signal pins are 5V-tolerant, and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

## **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see the <u>Oscillator Control Register Definitions</u> section on page 171) such that the external oscillator is selected as the system clock. For 8-pin devices, use PA1 instead of PB3.

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see the <u>Interrupt Controller</u> chapter on page 54.

# **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data, and output data. Table 18 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register<br>Mnemonic    | Port Register Name                                           |

|------------------------------|--------------------------------------------------------------|

| P <i>x</i> ADDR              | Port A–C Address Register (Selects subregisters).            |

| P <i>x</i> CTL               | Port A-C Control Register (Provides access to subregisters). |

| PxIN                         | Port A–C Input Data Register.                                |

| P <i>x</i> OUT               | Port A–C Output Data Register.                               |

| Port Subregister<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                | Data Direction.                                              |

| P <i>x</i> AF                | Alternate Function.                                          |

| P <i>x</i> OC                | Output Control (Open-Drain).                                 |

|                              |                                                              |

**Table 18. GPIO Port Registers and Subregisters**

#### ilog Embedded in Life An ∎IXYS Company 51

## Port A–C Output Data Register

The Port A–C Output Data Register (Table 31) controls the output data to the pins.

#### Table 31. Port A–C Output Data Register (PxOUT)

| Bit     | 7                | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|------------------|-------|-------|-------|-------|-------|-------|-------|

| Field   | POUT7            | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET   | 0                | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W              | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | FD3H, FD7H, FDBH |       |       |       |       |       |       |       |

#### Bit Description

[7:0] **Port Output Data**

PxOUT These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 = Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.

Note: x indicates the specific GPIO port pin number (7–0).

## **LED Drive Enable Register**

The LED Drive Enable Register, shown in Table 32, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | LEDEN[7:0] |     |     |     |     |     |     |     |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F82H       |     |     |     |     |     |     |     |

#### Table 32. LED Drive Enable (LEDEN)

| [7:0] | LED Drive Enable |  |

|-------|------------------|--|

Description

LEDEN These bits determine which Port C pins are connected to an internal current sink.

1= Connect controlled current sink to the Port C pin.

Bit

<sup>0 =</sup> Tristate the Port C pin.

ILO G Embedded in Life

■IXYS Company

53

# LED Drive Level Low Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 34). These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit     | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |  |

|---------|-----|-----------------------------|---|----|----|---|---|---|--|

| Field   |     | LEDLVLL[7:0]                |   |    |    |   |   |   |  |

| RESET   | 0   | 0                           | 0 | 0  | 0  | 0 | 0 | 0 |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |  |

| Address |     |                             |   | F8 | 4H |   |   |   |  |

#### Table 34. LED Drive Level Low Register (LEDLVLL)

Bit

Description

[7:0]

LED Level High Bit

LEDLVLL

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3mA.

01 = 7mA.

10 = 13mA.

11 = 20mA.

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

|          | 0004H                               | Watchdog Timer (see the Watchdog Timer section on page 91)                 |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          | 0036H                               | Port C Pin 0, both input edges                                             |

| Lowest   | 0038H                               | Reserved                                                                   |

#### Table 35. Trap and Interrupt Vectors in Order of Priority

#### Table 43. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7       | 6                           | 5      | 4      | 3             | 2      | 1      | 0      |  |

|---------|---------|-----------------------------|--------|--------|---------------|--------|--------|--------|--|

| Field   | PA7VENH | PA6CENH                     | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |

| RESET   | 0       | 0                           | 0      | 0      | 0             | 0      | 0      | 0      |  |

| R/W     | R/W     | R/W R/W R/W R/W R/W R/W R/W |        |        |               |        |        |        |  |

| Address |         | FC4H                        |        |        |               |        |        |        |  |

| Bit             | Description                                                                                                                                                                         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VENH  | Port A Bit[7] Interrupt Request Enable High Bit                                                                                                                                     |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit                                                                                                                       |

| [5:0]<br>PAxENH | <b>Port A Bit[x] Interrupt Request Enable High Bit</b><br>For selection of Port A as the interrupt source, see the <u>Shared Interrupt Select Register</u> sec-<br>tion on page 67. |

Note: x indicates the specific GPIO Port A pin number (5–0).

#### Table 44. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7       | 6                           | 5      | 4      | 3      | 2      | 1      | 0      |  |

|---------|---------|-----------------------------|--------|--------|--------|--------|--------|--------|--|

| Field   | PA7VENL | PA6CENL                     | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |  |

| RESET   | 0       | 0                           | 0      | 0      | 0      | 0      | 0      | 0      |  |

| R/W     | R/W     | R/W R/W R/W R/W R/W R/W R/W |        |        |        |        |        |        |  |

| Address |         | FC5H                        |        |        |        |        |        |        |  |

| Description                                                  |                                                                                                                |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Port A Bit[7] Interrupt Request Enable Low Bit               |                                                                                                                |

| Port A Bit[7] or Comparator Interrupt Request Enable Low Bit |                                                                                                                |

| Port A Bit[x] Interrupt Request Enable Low Bit               |                                                                                                                |

| _                                                            | Port A Bit[7] Interrupt Request Enable Low Bit<br>Port A Bit[7] or Comparator Interrupt Request Enable Low Bit |

Note: x indicates the specific GPIO Port A pin number (5–0).

nbedded in Life

73

enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps to configure a timer for COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COUNTER Mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER Mode. After the first timer reload in COUNTER Mode, counting always begins at the reset value of 0001H. In COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER Mode, the number of timer input transitions since the timer start is computed via the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

#### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER Mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER Mode, the prescaler is disabled.

ilog<sup>°</sup> Embedded in Life TXYS Company **79**

input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the capture occurs on a rising edge or a falling edge of the Timer Input signal. When the capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is because of an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not caused by an input capture event.

Observe the following steps to configure a timer for CAPTURE RESTART Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode; setting the mode also involves writing to TMODEHI bit in TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

> ilog Embedded in Life An IXYS Company 85

|         |            | -                           | - | - |   |   | - |   |  |

|---------|------------|-----------------------------|---|---|---|---|---|---|--|

| Bit     | 7          | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

| Field   | TRH        |                             |   |   |   |   |   |   |  |

| RESET   | 1          | 1                           | 1 | 1 | 1 | 1 | 1 | 1 |  |

| R/W     | R/W        | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | F02H, F0AH |                             |   |   |   |   |   |   |  |

#### Table 53. Timer 0–1 Reload High Byte Register (TxRH)

#### Table 54. Timer 0–1 Reload Low Byte Register (TxRL)

| Bit     | 7          | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |  |

|---------|------------|-----|-----|-------|------|-----|-----|-----|--|--|

| Field   |            | TRL |     |       |      |     |     |     |  |  |

| RESET   | 1          | 1   | 1   | 1     | 1    | 1   | 1   | 1   |  |  |

| R/W     | R/W        | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |

| Address |            |     |     | F03H, | F0BH |     |     |     |  |  |

| Bit     | Descriptio | n   |     |       |      |     |     |     |  |  |

| [7]     |            |     |     |       |      |     |     |     |  |  |

| [6]     |            |     |     |       |      |     |     |     |  |  |

| [5]     |            |     |     |       |      |     |     |     |  |  |

| [4]     |            |     |     |       |      |     |     |     |  |  |

| [3]     |            |     |     |       |      |     |     |     |  |  |

| [2]     |            |     |     |       |      |     |     |     |  |  |

| [1]     |            |     |     |       |      |     |     |     |  |  |

| [0]     |            |     |     |       |      |     |     |     |  |  |

TRH and TRL—Timer Reload Register High and Low

These two bytes form the 16-bit reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE Mode, these two bytes form the 16-bit compare value.

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control</li> <li>This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.</li> <li>When the UART receiver is not enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0.</li> <li>Reads from the Baud Rate High and Low Byte registers return the current BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the High Byte is read.</li> </ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared encoder/decoder is disabled. UART operates normally.</li> <li>1 = Infrared encoder/decoder is enabled. The UART transmits and receives data through the infrared encoder/decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

ILO O hbedded in Life IXYS Company

120

The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the endec clock counter is reset, resynchronizing the endec to the incoming signal, allowing the endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART control registers as defined in the <u>Universal Asynchronous Receiver/Transmitter</u> chapter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the endec before enabling the GPIO port alternate function for the corresponding pin.

nbedded in Life

124

- CEN resets to 0 to indicate the conversion is complete

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS Mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Observe the following steps for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

#### **Software Compensation Procedure**

The value read from the ADC high and low byte registers are uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following formula yields the compensated value:

$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL)*GAINCAL)/2$

where GAINCAL is the gain calibration byte, OFFCAL is the offset calibration byte and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. The OFFCAL value is in two's complement format, as are the compensated and uncompensated ADC values.

**Note:** The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits. Also note that in the second term, the multiplication must be performed before the division by 2<sup>16</sup>. Otherwise, the second term evaluates to zero incorrectly.

**Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit non-unity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

# **ADC Control Register Definitions**

The following sections define the ADC Control registers.

## **ADC Control Register 0**

The ADC Control Register selects the analog input channel and initiates the analog-to-digital conversion.

## **ADC Calibration Data**

#### Table 94. ADC Calibration Bits

| Bit       | 7                                   | 6               | 5              | 4   | 3   | 2   | 1   | 0   |  |

|-----------|-------------------------------------|-----------------|----------------|-----|-----|-----|-----|-----|--|

| Field     | ADC_CAL                             |                 |                |     |     |     |     |     |  |

| RESET     | U                                   | U U U U U U U U |                |     |     |     |     |     |  |

| R/W       | R/W                                 | R/W             | R/W            | R/W | R/W | R/W | R/W | R/W |  |

| Address   | Information Page Memory 0060H–007DH |                 |                |     |     |     |     |     |  |

| Note: U = | Unchanged b                         | y Reset. R/M    | / = Read/Write | е.  |     |     |     |     |  |

# Bit Description [7:0] Analog-to-Digital Converter Calibration Values ADC\_CAL Contains factory-calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in the Software Compensation Procedure section on page 126. The location of each calibration byte is provided in Table 95.

#### Table 95. ADC Calibration Data Location

| Info Page<br>Address | Memory<br>Address | Compensation<br>Usage | ADC Mode                | Reference<br>Type |

|----------------------|-------------------|-----------------------|-------------------------|-------------------|

| 60                   | FE60              | Offset                | Single-Ended Unbuffered | Internal 2.0V     |

| 08                   | FE08              | Gain High Byte        | Single-Ended Unbuffered | Internal 2.0V     |

| 09                   | FE09              | Gain Low Byte         | Single-Ended Unbuffered | Internal 2.0V     |

| 63                   | FE63              | Offset                | Single-Ended Unbuffered | Internal 1.0V     |

| 0A                   | FE0A              | Gain High Byte        | Single-Ended Unbuffered | Internal 1.0V     |

| 0B                   | FE0B              | Gain Low Byte         | Single-Ended Unbuffered | Internal 1.0V     |

| 66                   | FE66              | Offset                | Single-Ended Unbuffered | External 2.0V     |

| 0C                   | FE0C              | Gain High Byte        | Single-Ended Unbuffered | External 2.0V     |

| 0D                   | FE0D              | Gain Low Byte         | Single-Ended Unbuffered | External 2.0V     |

163

ilog Ibedded in Life

In the following list of OCD Commands, data and commands sent from the host to the OCD are identified by 'DBG  $\leftarrow$  Command/Data'. Data sent from the OCD back to the host is identified by 'DBG  $\rightarrow$  Data'.

**Read OCD Revision (00H).** The Read OCD Revision command determines the version of the OCD. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The Read OCD Status Register command reads the OCDSTAT Register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

**Read Runtime Counter (03H).** The Runtime Counter counts system clock cycles in between breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory, Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction, and Execute Instruction commands.

```

DBG \leftarrow 03H

DBG \rightarrow RuntimeCounter[15:8]

DBG \rightarrow RuntimeCounter[7:0]

```

Write OCD Control Register (04H). The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of returning the device to normal operating mode is to reset the device.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

**Read OCD Control Register (05H).** The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

**Write Program Counter (06H).** The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### ilog<sup>°</sup> Embedded in Life An IXYS Company 206

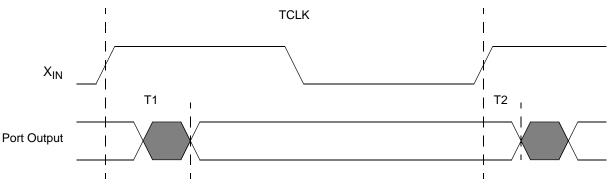

# **General Purpose I/O Port Output Timing**

Figure 30 and Table 131 provide timing information for GPIO Port pins.

|                |                                                 | Delay (ns) |         |

|----------------|-------------------------------------------------|------------|---------|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |

| GPIO Port pins |                                                 |            |         |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _          | 15      |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |

#### Table 131. GPIO Port Output Timing