Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113pj005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ilog<sup>®</sup>

ii

### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2011 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

| Table 106. | Assembly Language Syntax Example 1 175                                |

|------------|-----------------------------------------------------------------------|

| Table 107. | Assembly Language Syntax Example 2                                    |

|            | Notational Shorthand                                                  |

| Table 109. | Additional Symbols                                                    |

| Table 110. | Arithmetic Instructions                                               |

| Table 111. | Bit Manipulation Instructions                                         |

| Table 112. | Block Transfer Instructions 179                                       |

| Table 113. | CPU Control Instructions 180                                          |

| Table 114. | Load Instructions                                                     |

| Table 115. | Logical Instructions                                                  |

| Table 116. | Program Control Instructions                                          |

| Table 117. | Rotate and Shift Instructions                                         |

| Table 118. | eZ8 CPU Instruction Summary 182                                       |

|            | Opcode Map Abbreviations 193                                          |

| Table 120. | Absolute Maximum Ratings 196                                          |

| Table 121. | DC Characteristics                                                    |

| Table 122. | Power Consumption                                                     |

| Table 123. | AC Characteristics                                                    |

| Table 124. | Internal Precision Oscillator Electrical Characteristics              |

| Table 125. | Power-On Reset and Voltage Brown-Out Electrical Characteristics       |

|            | and Timing 201                                                        |

|            | Flash Memory Electrical Characteristics and Timing 202                |

|            | Watchdog Timer Electrical Characteristics and Timing 202              |

|            | Analog-to-Digital Converter Electrical Characteristics and Timing 203 |

|            | Comparator Electrical Characteristics                                 |

|            | GPIO Port Input Timing 205                                            |

|            | GPIO Port Output Timing 206                                           |

|            | On-Chip Debugger Timing                                               |

|            | UART Timing With CTS 208                                              |

|            | UART Timing Without CTS 209                                           |

| Table 135. | Z8 Encore! XP F0823 Series Ordering Matrix 211                        |

8

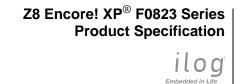

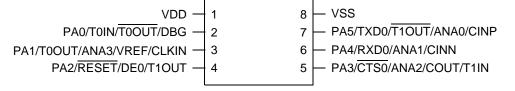

Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

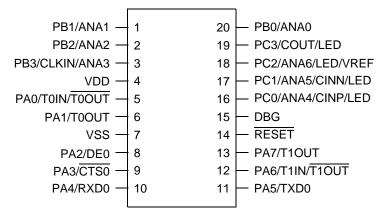

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

9

IXYS Company

**Note:** \*Analog input alternate functions (ANA) are not available on Z8F0x13 devices.

# **Signal Descriptions**

>

Table 3 lists the Z8 Encore! XP F0823 Series signals. To determine the signals available for the specific package styles, see the Pin Configurations section on page 7.

| Signal Mnemonic      | I/O     | Description                                                                                                                                                                                                                                                                                             |

|----------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/   | O Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]              | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0] <sup>1</sup> | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]              | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| UART Controllers     |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                 | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                 | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                 | I       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                   | Ο       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 Register. The DE signal can be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers               |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT          | 0       | Timer Output 0–1. These signals are output from the timers.                                                                                                                                                                                                                                             |

| T0OUT/T1OUT          | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM DUAL OUTPUT Mode.                                                                                                                                                                                                          |

| T0IN/T1IN            | I       | Timer Input 0–1. These signals are used as the capture, gating and counter inputs. The T0IN signal is multiplexed T0OUT signals.                                                                                                                                                                        |

| Comparator           |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN            | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| Notes:               |         |                                                                                                                                                                                                                                                                                                         |

#### **Table 3. Signal Descriptions**

1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

#### Table 40. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit           | 7                                                                        | 6           | 5          | 4           | 3       | 2        | 1 | 0      |  |  |

|---------------|--------------------------------------------------------------------------|-------------|------------|-------------|---------|----------|---|--------|--|--|

| Field         | Reserved                                                                 | T1ENH       | T0ENH      | U0RENH      | U0TENH  | Reserved |   | ADCENH |  |  |

| RESET         | 0                                                                        | 0           | 0          | 0           | 0       | (        | ) | 0      |  |  |

| R/W           | R/W                                                                      | R/W         | R/W        | R/W         | R/W     | R/       | W | R/W    |  |  |

| Address       |                                                                          | FC1H        |            |             |         |          |   |        |  |  |

| Bit           | Description                                                              |             |            |             |         |          |   |        |  |  |

| [7]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.     |             |            |             |         |          |   |        |  |  |

| [6]<br>T1ENH  | Timer 1 Interrupt Request Enable High Bit                                |             |            |             |         |          |   |        |  |  |

| [5]<br>T0ENH  | Timer 0 Interrupt Request Enable High Bit                                |             |            |             |         |          |   |        |  |  |

| [4]<br>U0RENH | UART 0 Re                                                                | ceive Inter | rupt Reque | st Enable H | igh Bit |          |   |        |  |  |

| [3]<br>U0TENH | UART 0 Transmit Interrupt Request Enable High Bit                        |             |            |             |         |          |   |        |  |  |

| [2:1]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |             |            |             |         |          |   |        |  |  |

| [0]           | ADC Interrupt Request Enable High Bit                                    |             |            |             |         |          |   |        |  |  |

[0] ADCENH

## Table 41. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5            | 4             | 3             | 2        | 1 | 0      |  |

|---------|----------|-------|--------------|---------------|---------------|----------|---|--------|--|

| Field   | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved |   | ADCENL |  |

| RESET   | 0        | 0     | 0            | 0             | 0             | 0        |   | 0      |  |

| R/W     | R        | R/W   | R/W          | R/W           | R/W           | R        |   | R/W    |  |

| Address |          | FC2H  |              |               |               |          |   |        |  |

| Bit          | Description                                                             |

|--------------|-------------------------------------------------------------------------|

| [7]          | Reserved<br>This bit is reserved and must be programmed to 0 when read. |

| [6]<br>T1ENL | Timer 1 Interrupt Request Enable Low Bit                                |

| Z8 Encore! XP <sup>®</sup> F082<br>Product Spec |      |

|-------------------------------------------------|------|

|                                                 | ilog |

Embedded in Life An IXYS Company 70

# Architecture

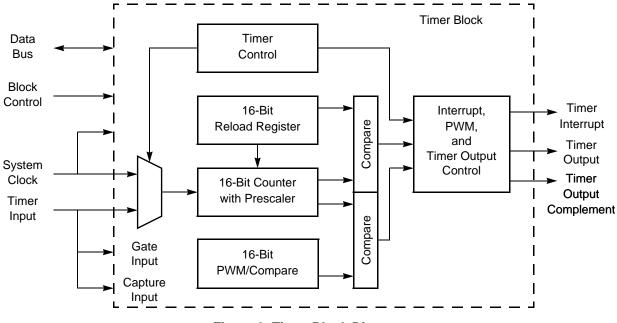

Figure 9 displays the architecture of the timers.

Figure 9. Timer Block Diagram

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

# **Timer Operating Modes**

The timers can be configured to operate in the following modes:

## **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

## CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

## Embedded in Life IXYS Company 92

## Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

## Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information about programming of the WDT\_RES Flash Option Bit, see **the** <u>Flash Option Bits</u> chapter on page 146.

## **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see the <u>Reset Status Register</u> section on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

## WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and F0823 Series are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. For more information about Stop Mode Recovery, see **the** <u>Reset and Stop Mode Recovery</u> chapter on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

#### ilog<sup>®</sup> Embedded in Life An∎IXYS Company 94

<u>Watchdog Timer Reload High Byte Register (WDTH)</u>: see page 95 <u>Watchdog Timer Reload Low Byte Register (WDTL)</u>: see page 95

# Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status Register.

| Bit              | 7           | 6                                                                                                                     | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|

| Field            |             | WDTUNLK                                                                                                               |   |   |   |   |   |   |  |

| RESET            | Х           | Х                                                                                                                     | Х | Х | Х | Х | Х | Х |  |

| R/W              | W           | W                                                                                                                     | W | W | W | W | W | W |  |

| Address          |             | FF0H                                                                                                                  |   |   |   |   |   |   |  |

| Bit              | Description |                                                                                                                       |   |   |   |   |   |   |  |

| [7:0]<br>WDTUNLK |             | Watchdog Timer Unlock<br>The software must write the correct unlocking sequence to this register before it is allowed |   |   |   |   |   |   |  |

Table 60. Watchdog Timer Control Register (WDTCTL)

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 61 through 63, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT Reload Value must not be set to a value less than 000004H.

to modify the contents of the Watchdog Timer reload registers.

| Bit   | Description                                                              |

|-------|--------------------------------------------------------------------------|

| [7:0] | WDT Reload Low                                                           |

| WDTL  | Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value. |

# Operation

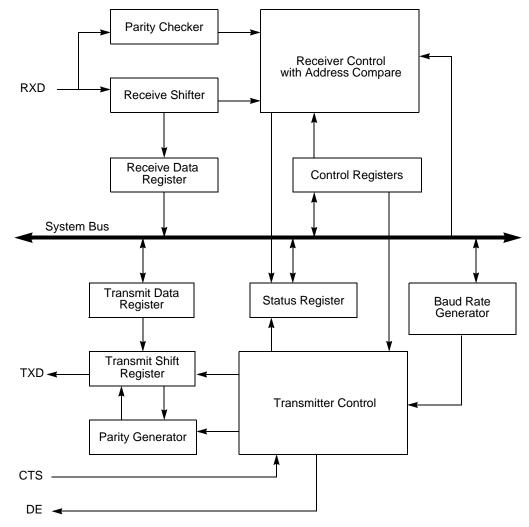

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

nbedded in Life

102

## **Receiving Data Using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Observe the following steps to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR Mode

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

Embedded in Life

# **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 68 and Table 69) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

| Bit        | 7           | 6                                                                                                                                           | 5    | 4   | 3    | 2    | 1    | 0    |  |  |

|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|------|------|--|--|

| Field      | TEN         | REN                                                                                                                                         | CTSE | PEN | PSEL | SBRK | STOP | LBEN |  |  |

| RESET      | 0           | 0                                                                                                                                           | 0    | 0   | 0    | 0    | 0    | 0    |  |  |

| R/W        | R/W         | R/W                                                                                                                                         | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |  |  |

| Address    |             | F42H                                                                                                                                        |      |     |      |      |      |      |  |  |

| Bit        | Description |                                                                                                                                             |      |     |      |      |      |      |  |  |

| [7]<br>TEN |             | <b>Transmit Enable</b><br>This bit enables or disables the transmitter. The enable is also controlled by the $\overline{\text{CTS}}$ signal |      |     |      |      |      |      |  |  |

#### Table 68. UART Control 0 Register (U0CTL0)

| DI          | Description                                                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TEN  | Transmit Enable         This bit enables or disables the transmitter. The enable is also controlled by the CTS signal and the CTSE bit. If the CTS signal is low and the CTSE bit is 1, the transmitter is enabled.         0 = Transmitter disabled.         1 = Transmitter enabled.                                                                 |

| [6]<br>REN  | Receive EnableThis bit enables or disables the receiver.0 = Receiver disabled.1 = Receiver enabled.                                                                                                                                                                                                                                                    |

| [5]<br>CTSE | <b>CTSE</b> — <b>CTS Enable</b><br>0 = The CTS signal has no effect on the transmitter.<br>1 = The UART recognizes the CTS signal as an enable control from the transmitter.                                                                                                                                                                           |

| [4]<br>PEN  | <ul> <li>Parity Enable</li> <li>This bit enables or disables parity. Even or odd is determined by the PSEL bit.</li> <li>0 = Parity is disabled.</li> <li>1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit .</li> </ul>                                                                 |

| [3]<br>PSEL | <ul> <li>Parity Select</li> <li>0 = Even parity is transmitted and expected on all received data.</li> <li>1 = Odd parity is transmitted and expected on all received data.</li> </ul>                                                                                                                                                                 |

| [2]<br>SBRK | <ul> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = Forces a break condition by setting the output of the transmitter to zero.</li> </ul> |

#### ilog Embedded in Life An∎IXYS Company 115

# **UART Address Compare Register**

The UART Address Compare Register stores the multinode network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

| Bit     | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   |  |  |  |

|---------|-----|-----|-----|------|-------|-----|-----|-----|--|--|--|

| Field   |     |     |     | COMP | _ADDR |     |     |     |  |  |  |

| RESET   | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |  |  |  |

| Address |     |     |     | F4   | F45H  |     |     |     |  |  |  |

| Bit       | Description                                             |

|-----------|---------------------------------------------------------|

| [7:0]     | Compare Address                                         |

| COMP_ADDR | This 8-bit value is compared to incoming address bytes. |

# **UART Baud Rate High and Low Byte Registers**

The UART Baud Rate High and Low Byte registers (Table 71 and Table 72) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   | BRH |     |     |     |     |     |     |     |

| RESET   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F4  | 6H  |     |     |     |

Table 71. UART Baud Rate High Byte Register (U0BRH)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   | BRL |     |     |     |     |     |     |     |

| RESET   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F4  | 7H  |     |     |     |

## 137

nbedded in Life

## Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

FFREQ[15:0] = System Clock Frequency (Hz) 1000

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768 Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of Z8 Encore! XP F0823 Series devices.

## Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access with the On-Chip Debugger. Programming the FRP Flash Option Bit prevents reading of the user code with the On-Chip Debugger. For more information, see the <u>Flash Option Bits</u> section on page 146 and the <u>On-Chip Debugger</u> chapter on page 156.

# Flash Code Protection Against Accidental Program and Erasure

F0823 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash Option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

## Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash Option Bits combine to provide three levels of Flash Program Memory protection as listed in Table 80. For more information, see the <u>Flash Option Bits</u> section on page 146.

#### illog<sup>®</sup> Ibedded in Life IXYS Company 138

# Table 80. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code program-<br>ming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-<br>Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                    |

## Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

## **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F0823 Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 79</u> on page 134.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

ilog Ibedded in Life

145

## Flash Sector Protect Register

The Flash Sector Protect (FPROT) Register is shared with the Flash Page Select Register. When the Flash Control Register is written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| Bit     | 7      | 6                           | 5      | 4      | 3      | 2      | 1      | 0      |  |

|---------|--------|-----------------------------|--------|--------|--------|--------|--------|--------|--|

| Field   | SPROT7 | SPROT6                      | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |

| RESET   | 0      | 0                           | 0      | 0      | 0      | 0      | 0      | 0      |  |

| R/W     | R/W    | R/W R/W R/W R/W R/W R/W R/W |        |        |        |        |        |        |  |

| Address | FF9H   |                             |        |        |        |        |        |        |  |

Table 84. Flash Sector Protect Register (FPROT)

#### Bit Description

#### [7] Sector Protection

- SPROT*n* Each bit corresponds to a 1024-byte Flash sector on devices in the 8K range, while the remaining devices correspond to a 512-byte Flash sector. To determine the appropriate Flash memory sector address range and sector number for your Z8F0823 Series product, please refer to <u>Table 79</u> on page 134 and to Figure 20, which follows the table.

- For Z8F08x3 and Z8F04x3 devices, all bits are used.

- For Z8F02x3 devices, the upper 4 bits are unused.

- For Z8F01x3 devices, the upper 6 bits are unused.

Note: n indicates the specific Flash sector (7–0).

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$$

177

#### Table 108. Notational Shorthand (Continued)

| Notation | Description           | Operand | Range                                                                                                                   |  |  |

|----------|-----------------------|---------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| RA       | Relative Address      | Х       | X represents an index in the range of +127 to -128 which is an offset relative to the address of the next instruction   |  |  |

| rr       | Working Register Pair | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                       |  |  |

| RR       | Register Pair         | Reg     | Reg. represents an even number in the range of 00H to FEH.                                                              |  |  |

| Vector   | Vector Address        | Vector  | Vector represents a number in the range of 00H to FFH.                                                                  |  |  |

| X        | Indexed               | #Index  | The register or register pair to be indexed is offset<br>by the signed Index value (#Index) in a +127 to<br>-128 range. |  |  |

Table 109 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

#### Table 109. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.

$dst \leftarrow dst + src$

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

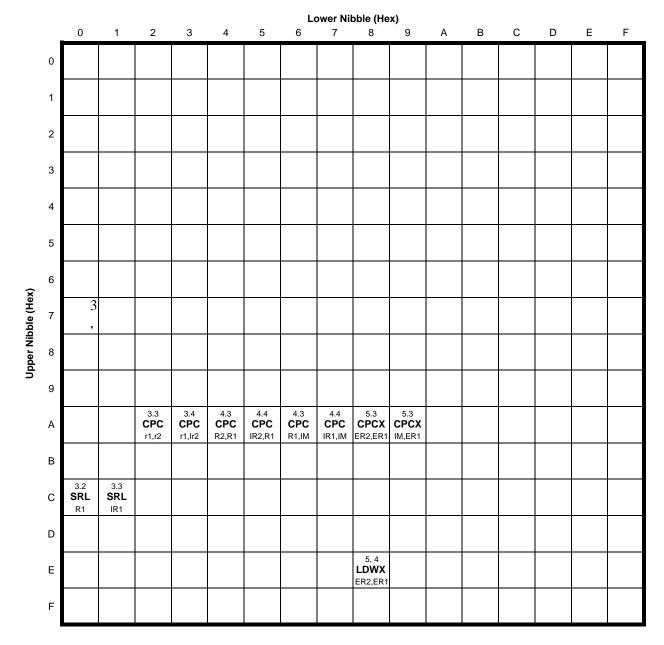

Figure 28. Second Opcode Map after 1FH

225

LDEI 179, 180 LDX 180 LEA 180 load 180 load constant 179 load constant to/from program memory 180 load constant with auto-increment addresses 180 load effective address 180 load external data 180 load external data to/from data memory and autoincrement addresses 179 load external to/from data memory and auto-increment addresses 180 load instructions 180 load using extended addressing 180 logical AND 181 logical AND/extended addressing 181 logical exclusive OR 181 logical exclusive OR/extended addressing 181 logical instructions 181 logical OR 181 logical OR/extended addressing 181 low power modes 30

## Μ

master interrupt enable 56 memory data 15 program 13 mode CAPTURE 89 **CAPTURE/COMPARE 89 CONTINUOUS 88 COUNTER 89** GATED 89 **ONE-SHOT 88 PWM 89** modes 89 **MULT 179** multiply 179 MULTIPROCESSOR mode, UART 103

## Ν

NOP (no operation) 180 notation b 176 cc 176 DA 176 ER 176 IM 176 IR 176 Ir 176 **IRR 176** Irr 176 p 176 R 176 r 176 RA 177 RR 177 rr 177 vector 177 X 177 notational shorthand 176

# 0

OCD architecture 156 auto-baud detector/generator 159 baud rate limits 160 block diagram 156 breakpoints 161 commands 162 control register 166 data format 159 DBG pin to RS-232 Interface 157 DEBUG mode 158 debugger break 181 interface 157 serial errors 160 status register 168 timing 207 **OCD** commands execute instruction (12H) 166 read data memory (0DH) 165 read OCD control register (05H) 163