Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decails                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113qb005sg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Figures

| Figure 1.  | Z8 Encore! XP F0823 Series Block Diagram 3                                           |

|------------|--------------------------------------------------------------------------------------|

| Figure 2.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package        |

| Figure 3.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package             |

| Figure 4.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package             |

| Figure 5.  | Power-On Reset Operation                                                             |

| Figure 6.  | Voltage Brown-Out Reset Operation                                                    |

| Figure 7.  | GPIO Port Pin Block Diagram                                                          |

| Figure 8.  | Interrupt Controller Block Diagram                                                   |

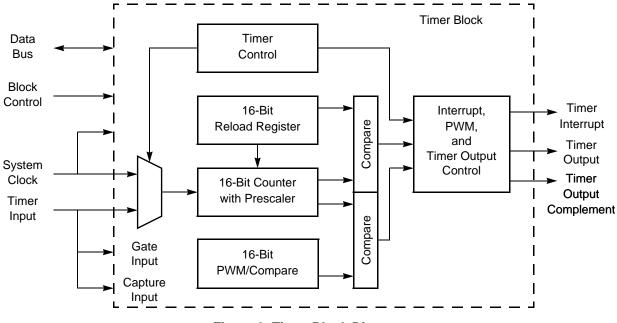

| Figure 9.  | Timer Block Diagram                                                                  |

| Figure 10. | UART Block Diagram                                                                   |

| Figure 11. | UART Asynchronous Data Format without Parity                                         |

| Figure 12. | UART Asynchronous Data Format with Parity                                            |

| Figure 13. | UART Asynchronous MULTIPROCESSOR Mode Data Format 103                                |

| Figure 14. | UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity) 105              |

| Figure 15. | UART Receiver Interrupt Service Routine Flow                                         |

| Figure 16. | Infrared Data Communication System Block Diagram 117                                 |

| Figure 17. | Infrared Data Transmission                                                           |

| Figure 18. | IrDA Data Reception                                                                  |

| Figure 19. | Analog-to-Digital Converter Block Diagram 122                                        |

| Figure 20. | Flash Memory Arrangement 135                                                         |

| Figure 21. | Flash Controller Operation Flowchart                                                 |

| Figure 22. | On-Chip Debugger Block Diagram 156                                                   |

| Figure 23. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface,<br># 1 of 2 157 |

| Figure 24. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface,<br># 2 of 2     |

| Figure 25. | OCD Data Format                                                                      |

| Figure 26. | Opcode Map Cell Description 192                                                      |

| Figure 27. | First Opcode Map                                                                     |

| Figure 28. | Second Opcode Map after 1FH 195                                                      |

| Figure 29. | Port Input Sample Timing 205                                                         |

n 🗖 IXYS Company

# **Register Map**

Table 8 lists an address map of the Z8 Encore! XP F0823 Series Register File. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, nor all GPIO ports. Consider registers for unimplemented peripherals to be reserved.

| Address (Hex)  | Register Description              | Mnemonic      | Reset (Hex) | Page<br>No. |

|----------------|-----------------------------------|---------------|-------------|-------------|

| General-Purpos | e RAM                             |               |             |             |

| Z8F0823/Z8F081 | 13 Devices                        |               |             |             |

| 000–3FF        | General-Purpose Register File RAM | _             | XX          |             |

| 400-EFF        | Reserved                          | _             | XX          |             |

| Z8F0423/Z8F041 | 13 Devices                        |               |             |             |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |             |

| 400–EFF        | Reserved                          | _             | XX          |             |

| Z8F0223/Z8F021 | 13 Devices                        |               |             |             |

| 000–1FF        | General-Purpose Register File RAM |               | XX          |             |

| 200–EFF        | Reserved                          | _             | XX          |             |

| Z8F0123/Z8F011 | 13 Devices                        |               |             |             |

| 000–0FF        | General-Purpose Register File RAM |               | XX          |             |

| 100-EFF        | Reserved                          | _             | XX          |             |

| Timer 0        |                                   |               |             |             |

| F00            | Timer 0 High Byte                 | T0H           | 00          | <u>84</u>   |

| F01            | Timer 0 Low Byte                  | TOL           | 01          | <u>84</u>   |

| F02            | Timer 0 Reload High Byte          | TORH          | FF          | <u>85</u>   |

| F03            | Timer 0 Reload Low Byte           | TORL          | FF          | <u>85</u>   |

| F04            | Timer 0 PWM High Byte             | <b>T0PWMH</b> | 00          | <u>86</u>   |

| F05            | Timer 0 PWM Low Byte              | TOPWML        | 00          | <u>86</u>   |

| F06            | Timer 0 Control 0                 | TOCTLO        | 00          | <u>87</u>   |

| F07            | Timer 0 Control 1                 | T0CTL1        | 00          | <u>88</u>   |

| Timer 1        |                                   |               |             |             |

| F08            | Timer 1 High Byte                 | T1H           | 00          | <u>84</u>   |

| F09            | Timer 1 Low Byte                  | T1L           | 01          | <u>84</u>   |

#### Table 8. Register File Address Map

Note: XX=Undefined.

ILOG<sup>°</sup> Embedded in Life □IXYS Company 22

During a System Reset or Stop Mode Recovery, the IPO requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

#### Table 40. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit           | 7                                                             | 6                                                                        | 5           | 4            | 3        | 2    | 1     | 0      |

|---------------|---------------------------------------------------------------|--------------------------------------------------------------------------|-------------|--------------|----------|------|-------|--------|

| Field         | Reserved                                                      | T1ENH                                                                    | T0ENH       | U0RENH       | U0TENH   | Rese | erved | ADCENH |

| RESET         | 0                                                             | 0                                                                        | 0           | 0            | 0        | (    | )     | 0      |

| R/W           | R/W                                                           | R/W                                                                      | R/W         | R/W          | R/W      | R/   | W     | R/W    |

| Address       |                                                               | FC1H                                                                     |             |              |          |      |       |        |

| Bit           | Description                                                   | n                                                                        |             |              |          |      |       |        |

| [7]           | Reserved<br>This bit is reserved and must be programmed to 0. |                                                                          |             |              |          |      |       |        |

| [6]<br>T1ENH  | Timer 1 Interrupt Request Enable High Bit                     |                                                                          |             |              |          |      |       |        |

| [5]<br>T0ENH  | Timer 0 Interrupt Request Enable High Bit                     |                                                                          |             |              |          |      |       |        |

| [4]<br>U0RENH | UART 0 Re                                                     | ceive Inter                                                              | rupt Reque  | st Enable H  | igh Bit  |      |       |        |

| [3]<br>U0TENH | UART 0 Tra                                                    | ansmit Inte                                                              | rrupt Reque | est Enable I | High Bit |      |       |        |

| [2:1]         | Reserved<br>These bits a                                      | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |             |              |          |      |       |        |

| [0]           | ADC Interr                                                    | upt Reques                                                               | t Enable Hi | igh Bit      |          |      |       |        |

[0] ADCENH

#### Table 41. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5            | 4             | 3             | 2    | 1     | 0      |

|---------|----------|-------|--------------|---------------|---------------|------|-------|--------|

| Field   | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Rese | erved | ADCENL |

| RESET   | 0        | 0     | 0            | 0             | 0             | (    | )     | 0      |

| R/W     | R        | R/W   | R/W          | R/W           | R/W           | F    | २     | R/W    |

| Address |          |       |              | FC            | 2H            |      |       |        |

| Bit          | Description                                                             |

|--------------|-------------------------------------------------------------------------|

| [7]          | Reserved<br>This bit is reserved and must be programmed to 0 when read. |

| [6]<br>T1ENL | Timer 1 Interrupt Request Enable Low Bit                                |

#### Table 43. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address |         |         |        | FC     | 4H            |        |        |        |

| Bit             | Description                                                                                                                                                                         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VENH  | Port A Bit[7] Interrupt Request Enable High Bit                                                                                                                                     |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit                                                                                                                       |

| [5:0]<br>PAxENH | <b>Port A Bit[x] Interrupt Request Enable High Bit</b><br>For selection of Port A as the interrupt source, see the <u>Shared Interrupt Select Register</u> sec-<br>tion on page 67. |

Note: x indicates the specific GPIO Port A pin number (5–0).

#### Table 44. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|---------|---------|--------|--------|--------|--------|--------|--------|

| Field   | PA7VENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |

| RESET   | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address |         |         |        | FC     | 5H     |        |        |        |

| Description                                                  |                                                                                                                |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Port A Bit[7] Interrupt Request Enable Low Bit               |                                                                                                                |

| Port A Bit[7] or Comparator Interrupt Request Enable Low Bit |                                                                                                                |

| Port A Bit[x] Interrupt Request Enable Low Bit               |                                                                                                                |

| _                                                            | Port A Bit[7] Interrupt Request Enable Low Bit<br>Port A Bit[7] or Comparator Interrupt Request Enable Low Bit |

Note: x indicates the specific GPIO Port A pin number (5–0).

# Embedded in Life

# **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) register (Table 49) determines the source of the PADxS interrupts. The Shared Interrupt Select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit     | 7        | 6     | 5   | 4   | 3    | 2     | 1   | 0   |

|---------|----------|-------|-----|-----|------|-------|-----|-----|

| Field   | Reserved | PA6CS |     |     | Rese | erved |     |     |

| RESET   | 0        | 0     | 0   | 0   | 0    | 0     | 0   | 0   |

| R/W     | R/W      | R/W   | R/W | R/W | R/W  | R/W   | R/W | R/W |

| Address |          |       |     | FC  | EH   |       |     |     |

#### Table 49. Shared Interrupt Select Register (IRQSS)

| Bit          | Description                                                                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]          | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                   |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The comparator is used as an interrupt for PA6CS interrupt requests.</li> </ul> |

| [5:0]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                           |

| Z8 Encore! XP <sup>®</sup> F082<br>Product Spec |      |

|-------------------------------------------------|------|

|                                                 | ilog |

Embedded in Life An IXYS Company 70

# Architecture

Figure 9 displays the architecture of the timers.

Figure 9. Timer Block Diagram

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

# **Timer Operating Modes**

The timers can be configured to operate in the following modes:

### **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

#### ilog Embedded in Life An IXYS Company

90

| Bit                      | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6]<br>TPOL<br>(cont'd.) | <b>COMPARATOR COUNTER Mode</b><br>When the timer is disabled, the Timer Output signal is set to the value of this bit. When the<br>timer is enabled, the Timer Output signal is complemented upon timer reload.                                                                                                                                                                                                                                                                                                       |

|                          | <b>Caution:</b> When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, TxOUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.                                                                                                                    |

| [5:3]<br>PRES            | Prescale Value<br>The timer input clock is divided by 2 <sup>PRES</sup> , where PRES can be set from 0 to 7. The prescaler is<br>reset each time the timer is disabled. This reset ensures proper clock division each time the<br>timer is restarted.<br>000 = Divide by 1.<br>001 = Divide by 2.<br>010 = Divide by 4.<br>011 = Divide by 8.<br>100 = Divide by 16.<br>101 = Divide by 32.<br>110 = Divide by 64.<br>111 = Divide by 128.                                                                            |

| [2:0]<br>TMODE           | Timer Mode<br>This field, along with the TMODEHI bit in TxCTL0 Register, determines the operating mode of<br>the timer. TMODEHI is the most significant bit of the timer mode selection value.<br>0000 = ONE-SHOT Mode.<br>0001 = CONTINUOUS Mode.<br>0010 = COUNTER Mode.<br>0010 = COUNTER Mode.<br>0111 = PWM SINGLE OUTPUT Mode.<br>0100 = CAPTURE Mode.<br>0110 = GATED Mode.<br>0111 = CAPTURE/COMPARE Mode.<br>1000 = PWM DUAL OUTPUT Mode.<br>1001 = CAPTURE RESTART Mode.<br>1010 = COMPARATOR COUNTER Mode. |

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control</li> <li>This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.</li> <li>When the UART receiver is not enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0.</li> <li>Reads from the Baud Rate High and Low Byte registers return the current BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the High Byte is read.</li> </ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared encoder/decoder is disabled. UART operates normally.</li> <li>1 = Infrared encoder/decoder is enabled. The UART transmits and receives data through the infrared encoder/decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### ilog Embedded in Life An∎IXYS Company 115

# **UART Address Compare Register**

The UART Address Compare Register stores the multinode network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

| Bit     | 7   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|-----------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | COMP_ADDR |     |     |     |     |     |     |  |

| RESET   | 0   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F45H      |     |     |     |     |     |     |  |

| Table 70. UART Address Compare Register (U0ADDR | Table 70. UART Address Com | npare Register (U0ADDR) |

|-------------------------------------------------|----------------------------|-------------------------|

|-------------------------------------------------|----------------------------|-------------------------|

| Bit       | Description                                             |

|-----------|---------------------------------------------------------|

| [7:0]     | Compare Address                                         |

| COMP_ADDR | This 8-bit value is compared to incoming address bytes. |

# **UART Baud Rate High and Low Byte Registers**

The UART Baud Rate High and Low Byte registers (Table 71 and Table 72) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | BRH  |     |     |     |     |     |     |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F46H |     |     |     |     |     |     |  |

Table 71. UART Baud Rate High Byte Register (U0BRH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------|-----|-----|-----|-----|-----|-----|

| Field   |     | BRL  |     |     |     |     |     |     |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F47H |     |     |     |     |     |     |

dded in Life

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 73 provides information about data rate errors for a 5.5296MHz System Clock.

|                          | 5.5296MHz S              | ystem Clock          |           |

|--------------------------|--------------------------|----------------------|-----------|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |

| 1250.0                   | N/A                      | N/A                  | N/A       |

| 625.0                    | N/A                      | N/A                  | N/A       |

| 250.0                    | 1                        | 345.6                | 38.24     |

| 115.2                    | 3                        | 115.2                | 0.00      |

| 57.6                     | 6                        | 57.6                 | 0.00      |

| 38.4                     | 9                        | 38.4                 | 0.00      |

| 19.2                     | 18                       | 19.2                 | 0.00      |

| 9.60                     | 36                       | 9.60                 | 0.00      |

| 4.80                     | 72                       | 4.80                 | 0.00      |

| 2.40                     | 144                      | 2.40                 | 0.00      |

| 1.20                     | 288                      | 1.20                 | 0.00      |

| 0.60                     | 576                      | 0.60                 | 0.00      |

| 0.30                     | 1152                     | 0.30                 | 0.00      |

#### Table 73. UART Baud Rates

> ilog Embedded in Life An∎IXYS Company

> 127

| Bit            | 7                                                                                                                                                                                                                                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5      | 4    | 3   | 2          | 1   | 0   |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----|------------|-----|-----|--|--|--|

| Field          | CEN                                                                                                                                                                                                                                       | REFSELL                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | REFEXT | CONT |     | ANAIN[3:0] |     |     |  |  |  |

| RESET          | 0                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0      | 0    | 0   | 0          | 0   | 0   |  |  |  |

| R/W            | R/W                                                                                                                                                                                                                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W    | R/W  | R/W | R/W        | R/W | R/W |  |  |  |

| Address        |                                                                                                                                                                                                                                           | F70H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |      |     |            |     |     |  |  |  |

| Bit            | Description                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |      |     |            |     |     |  |  |  |

| [7]<br>CEN     | 0 = Conv<br>this t<br>1 = Begi                                                                                                                                                                                                            | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul>                                                                                              |        |      |     |            |     |     |  |  |  |

| [6]<br>REFSELL | In conjur<br>mines th<br>SELH, R<br>00 = Inte<br>01 = Inte                                                                                                                                                                                | Voltage Reference Level Select Low Bit<br>In conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this deter-<br>mines the level of the internal voltage reference; the following details the effects of {REF-<br>SELH, REFSELL}. This reference is independent of the Comparator reference.<br>00 = Internal Reference Disabled, reference comes from external pin.<br>01 = Internal Reference set to 1.0V.<br>10 = Internal Reference set to 2.0V (default). |        |      |     |            |     |     |  |  |  |

| [5]<br>REFEXT  | 0 = Exte                                                                                                                                                                                                                                  | <b>External Reference Select</b><br>0 = External reference buffer is disabled; $V_{REF}$ pin is available for GPIO functions.<br>1 = The internal ADC reference is buffered and connected to the V <sub>REF</sub> pin.                                                                                                                                                                                                                                                              |        |      |     |            |     |     |  |  |  |

| [4]<br>CONT    | <ul> <li>Continuous Conversion</li> <li>0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.</li> <li>1 = Continuous conversion. ADC data updated every 256 system clock cycles.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |      |     |            |     |     |  |  |  |

#### Table 74. ADC Control Register 0 (ADCCTL0)

# Embedded in Life An IXYS Company 130

# ADC Data High Byte Register

The ADC Data High Byte Register contains the upper eight bits of the ADC output. The output is an 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit     | 7    | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|-------|---|---|---|---|---|---|

| Field   |      | ADCDH |   |   |   |   |   |   |

| RESET   | Х    | Х     | Х | Х | Х | Х | Х | Х |

| R/W     | R    | R     | R | R | R | R | R | R |

| Address | F72H |       |   |   |   |   |   |   |

| Table 76. | ADC Dat | a High B      | vte Registe | er (ADCD_H) |

|-----------|---------|---------------|-------------|-------------|

|           |         | ~ · · · · · · | ,           |             |

# Bit Description [7:0] ADC Data High Byte ADCDH This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

#### ILOG Embedded in Life An IXYS Company 140

## Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

## **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

# **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the Zilog application note titled, <u>Third-Party Flash Programming Support for Z8 Encore! MCUs (AN0117)</u>, available for download at <u>www.zilog.com</u>.

# Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

#### Table 108. Notational Shorthand (Continued)

| Notation | Description           | Operand | Range                                                                                                                     |

|----------|-----------------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| RA       | Relative Address      | Х       | X represents an index in the range of $+127$ to $-128$ which is an offset relative to the address of the next instruction |

| rr       | Working Register Pair | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                         |

| RR       | Register Pair         | Reg     | Reg. represents an even number in the range of 00H to FEH.                                                                |

| Vector   | Vector Address        | Vector  | Vector represents a number in the range of 00H to FFH.                                                                    |

| X        | Indexed               | #Index  | The register or register pair to be indexed is offset<br>by the signed Index value (#Index) in a +127 to<br>-128 range.   |

Table 109 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

#### Table 109. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.

$dst \leftarrow dst + src$

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

ilog<sup>®</sup> Embedded in Life An ∎IXYS Company 183

| Assembly         |                                                                                           |     | ress<br>ode | _ Opcode(s) | Flags |   |   |   |   |   | Fetch  | Instr. |

|------------------|-------------------------------------------------------------------------------------------|-----|-------------|-------------|-------|---|---|---|---|---|--------|--------|

| Mnemonic         | Symbolic Operation                                                                        | dst | src         | (Hex)       | С     | Ζ | S | ۷ | D | Н | Cycles |        |

| ADD dst, src     | $dst \gets dst + src$                                                                     | r   | r           | 02          | *     | * | * | * | 0 | * | 2      | 3      |

|                  |                                                                                           | r   | lr          | 03          | _     |   |   |   |   |   | 2      | 4      |

|                  |                                                                                           | R   | R           | 04          | -     |   |   |   |   |   | 3      | 3      |

|                  |                                                                                           | R   | IR          | 05          | -     |   |   |   |   |   | 3      | 4      |

|                  |                                                                                           | R   | IM          | 06          | -     |   |   |   |   |   | 3      | 3      |

|                  |                                                                                           | IR  | IM          | 07          | -     |   |   |   |   |   | 3      | 4      |

| ADDX dst, src    | $dst \gets dst + src$                                                                     | ER  | ER          | 08          | *     | * | * | * | 0 | * | 4      | 3      |

|                  |                                                                                           | ER  | IM          | 09          | -     |   |   |   |   |   | 4      | 3      |

| AND dst, src     | $dst \gets dst \; AND \; src$                                                             | r   | r           | 52          | _     | * | * | 0 | _ | - | 2      | 3      |

|                  |                                                                                           | r   | lr          | 53          | -     |   |   |   |   |   | 2      | 4      |

|                  |                                                                                           | R   | R           | 54          | -     |   |   |   |   |   | 3      | 3      |

|                  |                                                                                           | R   | IR          | 55          | -     |   |   |   |   |   | 3      | 4      |

|                  |                                                                                           | R   | IM          | 56          | -     |   |   |   |   |   | 3      | 3      |

|                  |                                                                                           | IR  | IM          | 57          | -     |   |   |   |   |   | 3      | 4      |

| ANDX dst, src    | $dst \gets dst \; AND \; src$                                                             | ER  | ER          | 58          | _     | * | * | 0 | _ | _ | 4      | 3      |

|                  |                                                                                           | ER  | IM          | 59          | -     |   |   |   |   |   | 4      | 3      |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next<br>3 instructions |     |             | 2F          | _     | _ | _ | _ | _ | _ | 1      | 2      |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r   |             | E2          | _     | _ | _ | - | _ | - | 2      | 2      |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r   |             | E2          | -     | _ | _ | 0 | _ | _ | 2      | 2      |

| BRK              | Debugger Break                                                                            |     |             | 00          | -     | - | - | - | _ | - | 1      | 1      |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r   |             | E2          | -     | _ | _ | 0 | _ | _ | 2      | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                                       | R   |             | D5          | Х     | * | * | 0 | _ | _ | 2      | 2      |

| BTJ p, bit, src, | if src[bit] = p                                                                           |     | r           | F6          | _     | _ | _ | - | _ | _ | 3      | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr          | F7          | -     |   |   |   |   |   | 3      | 4      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

|   |                                |                                  |                                      |                              |                                |                                  | Lo                            | ower Nil                                  | bble (He                          | x)                           |                            |                          |                           |                           |                         |                          |

|---|--------------------------------|----------------------------------|--------------------------------------|------------------------------|--------------------------------|----------------------------------|-------------------------------|-------------------------------------------|-----------------------------------|------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|--------------------------|

|   | 0                              | 1                                | 2                                    | 3                            | 4                              | 5                                | 6                             | 7                                         | 8                                 | 9                            | А                          | В                        | С                         | D                         | Е                       | F                        |

| 0 | 1.1<br>BRK                     | 2.2<br>SRP<br>IM                 | 2.3<br><b>ADD</b><br>r1,r2           | 2.4<br><b>ADD</b><br>r1,lr2  | 3.3<br><b>ADD</b><br>R2,R1     | 3.4<br><b>ADD</b><br>IR2,R1      | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM                      | 4.3<br>ADDX<br>ER2,ER1            | 4.3<br>ADDX<br>IM,ER1        | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1        | 2.3<br><b>RLC</b><br>IR1         | 2.3<br>ADC<br>r1,r2                  | 2.4<br>ADC<br>r1,lr2         | 3.3<br>ADC<br>R2,R1            | 3.4<br>ADC<br>IR2,R1             | 3.3<br>ADC<br>R1,IM           | 3.4<br>ADC<br>IR1,IM                      | 4.3<br>ADCX<br>ER2,ER1            | 4.3<br>ADCX<br>IM,ER1        |                            |                          |                           |                           |                         | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1               | 2.3<br>INC<br>IR1                | 2.3<br><b>SUB</b><br>r1,r2           | 2.4<br>SUB<br>r1,lr2         | 3.3<br><b>SUB</b><br>R2,R1     | 3.4<br>SUB<br>IR2,R1             | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br>SUB<br>IR1,IM                      | 4.3<br><b>SUBX</b><br>ER2,ER1     | 4.3<br><b>SUBX</b><br>IM,ER1 |                            |                          |                           |                           |                         | 1                        |

| 3 | 2.2<br>DEC<br>R1               | 2.3<br>DEC<br>IR1                | 2.3<br>SBC<br>r1,r2                  | 2.4<br>SBC<br>r1,lr2         | 3.3<br>SBC<br>R2,R1            | 3.4<br>SBC<br>IR2,R1             | 3.3<br>SBC<br>R1,IM           | 3.4<br>SBC<br>IR1,IM                      | 4.3<br><b>SBCX</b><br>ER2,ER1     | 4.3<br>SBCX                  |                            |                          |                           |                           |                         |                          |

| 4 | 2.2<br>DA<br>R1                | 2.3<br>DA<br>IR1                 | 2.3<br><b>OR</b>                     | 2.4<br>OR                    | 3.3<br>OR<br>R2,R1             | 3.4<br><b>OR</b>                 | 3.3<br><b>OR</b>              | 3.4<br><b>OR</b>                          | 4.3<br>ORX<br>ER2,ER1             | 4.3<br>ORX                   |                            |                          |                           |                           |                         |                          |

| 5 | 2.2<br><b>POP</b><br>R1        | 2.3<br><b>POP</b>                | r1,r2<br>2.3<br>AND                  | r1,lr2<br>2.4<br>AND         | 3.3<br>AND<br>R2,R1            | 3.4<br>AND                       | 81,IM<br>3.3<br><b>AND</b>    | 3.4<br>AND                                | 4.3<br>ANDX                       | 4.3<br>ANDX                  |                            |                          |                           |                           |                         | 1.2<br>WDT               |

| 6 | 2.2<br>COM                     | IR1<br>2.3<br>COM                | r1,r2<br>2.3<br>TCM                  | r1,lr2<br>2.4<br>TCM         | 3.3<br>TCM                     | 3.4<br>TCM                       | 81,IM<br>3.3<br><b>TCM</b>    | 3.4<br>TCM                                | 4.3<br><b>TCMX</b>                | 4.3<br><b>TCMX</b>           |                            |                          |                           |                           |                         | 1.2<br>STOP              |

| 7 | R1<br>2.2<br><b>PUSH</b><br>R2 | IR1<br>2.3<br><b>PUSH</b><br>IR2 | r1,r2<br>2.3<br><b>TM</b>            | r1,lr2<br>2.4<br><b>TM</b>   | R2,R1<br>3.3<br><b>TM</b>      | IR2,R1<br>3.4<br><b>TM</b>       | R1,IM<br>3.3<br><b>TM</b>     | IR1,IM<br>3.4<br><b>TM</b>                | ER2,ER1<br>4.3<br><b>TMX</b>      | 4.3<br><b>TMX</b>            |                            |                          |                           |                           |                         | 1.2<br>HALT              |

| 8 | 2.5<br>DECW<br>RR1             | 2.6<br>DECW<br>IRR1              | r1,r2<br>2.5<br>LDE                  | r1,lr2<br>2.9<br><b>LDEI</b> | R2,R1<br>3.2<br>LDX            | IR2,R1<br>3.3<br>LDX             | R1,IM<br>3.4<br>LDX           | IR1,IM<br>3.5<br><b>LDX</b>               | 3.4<br>LDX                        | IM,ER1<br>3.4<br>LDX         |                            |                          |                           |                           |                         | 1.2<br><b>DI</b>         |

| 9 | 2.2<br>RL<br>R1                | 2.3<br>RL<br>IR1                 | r1,Irr2<br>2.5<br>LDE                | 2.9<br>LDEI<br>Ir2,Irr1      | r1,ER2<br>3.2<br>LDX<br>r2,ER1 | Ir1,ER2<br>3.3<br>LDX<br>Ir2,ER1 | 3.4<br>LDX<br>R2,IRR1         | IRR2,IR1<br>3.5<br><b>LDX</b><br>IR2,IRR1 | r1,rr2,X<br>3.3<br>LEA<br>r1,r2,X | 3.5<br><b>LEA</b>            |                            |                          |                           |                           |                         | 1.2<br>El                |

| A | 2.5<br>INCW<br>RR1             | 2.6<br>INCW                      | r2,Irr1<br>2.3<br><b>CP</b><br>r1,r2 | 2.4<br><b>CP</b><br>r1,lr2   | 3.3<br><b>CP</b><br>R2,R1      | 3.4<br><b>CP</b><br>IR2,R1       | 3.3<br>CP<br>R1,IM            | 3.4<br>CP<br>IR1,IM                       | 4.3<br>CPX<br>ER2,ER1             | 4.3<br>CPX<br>IM,ER1         |                            |                          |                           |                           |                         | 1.4<br>RET               |

| в | 2.2<br>CLR<br>R1               | 2.3<br>CLR<br>IR1                | 2.3<br>XOR<br>r1,r2                  | 2.4<br>XOR<br>r1,lr2         | 3.3<br>XOR<br>R2,R1            | 3.4<br>XOR<br>IR2,R1             | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br>XOR<br>IR1,IM                      | 4.3<br><b>XORX</b><br>ER2,ER1     | 4.3<br><b>XORX</b><br>IM,ER1 |                            |                          |                           |                           |                         | 1.5<br>IRET              |

| С | 2.2<br>RRC<br>R1               | 2.3<br>RRC<br>IR1                | 2.5<br>LDC<br>r1,lrr2                | 2.9<br>LDCI<br>Ir1,Irr2      | 2.3<br>JP<br>IRR1              | 2.9<br>LDC<br>lr1,lrr2           | IXT,IW                        | 3.4<br>LD<br>r1,r2,X                      | 3.2<br>PUSHX<br>ER2               |                              |                            |                          |                           |                           |                         | 1.2<br>RCF               |

| D | 2.2<br>SRA<br>R1               | 2.3<br>SRA<br>IR1                | 2.5<br>LDC<br>r2,Irr1                | 2.9<br>LDCI<br>lr2,lrr1      | 2.6                            | 2.2<br>BSWAP<br>R1               | 3.3<br>CALL<br>DA             | 3.4<br>LD<br>r2,r1,X                      | 3.2<br><b>POPX</b><br>ER1         |                              |                            |                          |                           |                           |                         | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1         | 2.3<br><b>RR</b><br>IR1          | 2.2<br>BIT<br>p,b,r1                 | 2.3<br>LD<br>r1,lr2          | 3.2<br>LD<br>R2,R1             | 3.3<br>LD<br>IR2,R1              | 3.2<br>LD<br>R1,IM            | 3.3<br>LD<br>IR1,IM                       | 4.2<br>LDX<br>ER2,ER1             | 4.2<br>LDX<br>IM,ER1         |                            |                          |                           |                           |                         | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1              | 2.3<br>SWAP<br>IR1               | 2.6<br>TRAP<br>Vector                | 2.3<br>LD<br>lr1,r2          | 2.8<br>MULT<br>RR1             | 3.3<br>LD<br>R2,IR1              | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X            |                                   |                              | V                          | ┥                        | V                         | ▼                         | V                       |                          |

Figure 27. First Opcode Map

|                           |                                                         | VD                   | <sub>D</sub> = 2.7V to 3         | 8.6V                             |    |                                                                   |  |

|---------------------------|---------------------------------------------------------|----------------------|----------------------------------|----------------------------------|----|-------------------------------------------------------------------|--|

| Symbol                    | Parameter                                               | Typical <sup>1</sup> | Maximum <sup>2</sup><br>Std Temp | Maximum <sup>3</sup><br>Ext Temp |    | Conditions                                                        |  |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                          | 0.1                  | 2                                | 7.5                              | μA | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}$ . |  |

| I <sub>DD</sub> Halt      | Supply Current in HALT                                  | 35                   | 55                               | 65                               | μA | 32kHz.                                                            |  |

|                           | Mode (with all peripher-<br>als disabled)               | 520                  | 630                              | 700                              | μA | 5.5MHz.                                                           |  |

| I <sub>DD</sub>           | Supply Current in                                       | 2.8                  | 4.5                              | 4.8                              | mA | 32kHz.                                                            |  |

|                           | ACTIVE Mode (with all peripherals disabled)             | 4.5                  | 5.2                              | 5.2                              | mA | 5.5MHz.                                                           |  |

| I <sub>DD</sub> WDT       | Watchdog Timer Sup-<br>ply Current                      | 0.9                  | 1.0                              | 1.1                              | μA |                                                                   |  |

| I <sub>DD</sub> IPO       | Internal Precision Oscil-<br>lator Supply Current       | 350                  | 500                              | 550                              | μA |                                                                   |  |

| I <sub>DD</sub> VBO       | Voltage Brown-Out Sup-<br>ply Current                   | 50                   |                                  |                                  | μA | For 20-/28-pin devices (VBO only). <sup>4</sup>                   |  |

|                           | -                                                       |                      |                                  |                                  |    | For 8-pin devices. <sup>4</sup>                                   |  |

| I <sub>DD</sub> ADC       | Analog-to-Digital Con-                                  | 2.8                  | 3.1                              | 3.2                              | mA | 32kHz.                                                            |  |

|                           | verter Supply Current<br>(with External Refer-<br>ence) | 3.1                  | 3.6                              | 3.7                              | mA | 5.5MHz.                                                           |  |

|                           |                                                         | 3.3                  | 3.7                              | 3.8                              | mA | 10MHz.                                                            |  |

|                           | ,                                                       | 3.7                  | 4.2                              | 4.3                              | mA | 20MHz.                                                            |  |

| I <sub>DD</sub><br>ADCRef | ADC Internal Refer-<br>ence Supply Current              | 0                    |                                  |                                  | μA | See Note 4.                                                       |  |

| I <sub>DD</sub> CMP       | Comparator supply Cur-<br>rent                          | 150                  | 180                              | 190                              | μA | See Note 4.                                                       |  |

| I <sub>DD</sub> BG        | Band Gap Supply Cur-                                    | 320                  | 480                              | 500                              | μA | For 20-/28-pin devices.                                           |  |

#### **Table 122. Power Consumption**

Notes:

1. Typical conditions are defined as  $V_{DD}$  = 3.3 V and +30°C.

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

ilog Embedded in Life An IXYS Company 202

|                                               | $T_A = -$ | = 2.7V to<br>-40°C to +<br>otherwise | 105°C   |        |                                                                                                                                                                  |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  | Notes                                                                                                                                                            |

| Flash Byte Read Time                          | 100       | _                                    | _       | ns     |                                                                                                                                                                  |

| Flash Byte Program Time                       | 20        | _                                    | 40      | μs     |                                                                                                                                                                  |

| Flash Page Erase Time                         | 10        | _                                    | _       | ms     |                                                                                                                                                                  |

| Flash Mass Erase Time                         | 200       | _                                    | _       | ms     |                                                                                                                                                                  |

| Writes to Single Address<br>Before Next Erase | -         | -                                    | 2       |        |                                                                                                                                                                  |

| Flash Row Program Time                        | -         | _                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This param-<br>eter is only an issue when<br>bypassing the Flash Controller. |

| Data Retention                                | 100       | _                                    | _       | years  | 25°C                                                                                                                                                             |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                             |

#### Table 126. Flash Memory Electrical Characteristics and Timing

#### Table 127. Watchdog Timer Electrical Characteristics and Timing

|                          |                          | T <sub>A</sub> = -      | = 2.7V to<br>-40°C to +<br>otherwise | 105°C       |            |                                                                                              |

|--------------------------|--------------------------|-------------------------|--------------------------------------|-------------|------------|----------------------------------------------------------------------------------------------|

| Symbol Parameter         |                          | Minimum Typical Maximum |                                      | Units       | Conditions |                                                                                              |

| F <sub>WDT</sub>         | WDT Oscillator Frequency |                         | 10                                   |             | kHz        |                                                                                              |

| F <sub>WDT</sub>         | WDT Oscillator Error     |                         |                                      | <u>+</u> 50 | %          |                                                                                              |

| T <sub>WDT-</sub><br>CAL | WDT Calibrated Timeout   | 0.98                    | 1                                    | 1.02        | S          | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30°C                                            |

|                          |                          | 0.70                    | 1                                    | 1.30        | S          | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = 0^{\circ} C \text{ to } 70^{\circ} C$           |

|                          |                          | 0.50                    | 1                                    | 1.50        | S          | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = -40^{\circ} \text{C to } +105^{\circ} \text{C}$ |

224