Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | ·                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | · .                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113sb005eg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ilog° Embedded in Life An∎IXYS Company 88

|         |     |      |            |      | <b>U</b> ( | ,   |       |     |  |  |

|---------|-----|------|------------|------|------------|-----|-------|-----|--|--|

| Bit     | 7   | 6    | 5          | 4    | 3          | 2   | 1     | 0   |  |  |

| Field   | TEN | TPOL |            | PRES |            |     | TMODE |     |  |  |

| RESET   | 0   | 0    | 0          | 0    | 0          | 0   | 0     | 0   |  |  |

| R/W     | R/W | R/W  | R/W        | R/W  | R/W        | R/W | R/W   | R/W |  |  |

| Address |     |      | F07H, F0FH |      |            |     |       |     |  |  |

#### Table 58. Timer 0–1 Control Register 1 (TxCTL1)

| Audress     |                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Description                                                                                                                                                                                                                                                                                                                    |

| [7]<br>TEN  | Timer Enable0 = Timer is disabled.1 = Timer enabled to count.                                                                                                                                                                                                                                                                  |

| [6]<br>TPOL | <b>Timer Input/Output Polarity</b><br>Operation of this bit is a function of the current operating mode of the timer.<br><b>ONE-SHOT Mode</b><br>When the timer is disabled, the Timer Output signal is set to the value of this bit. When the<br>timer is enabled, the Timer Output signal is complemented upon timer reload. |

|             | <b>CONTINUOUS Mode</b><br>When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer reload.                                                                                                                           |

#### Bit **Description (Continued)**

#### [6] COUNTER Mode

- TPOL If the timer is enabled the Timer Output signal is complemented after timer reload. (cont'd.)

- 0 =Count occurs on the rising edge of the Timer Input signal.

- 1 = Count occurs on the falling edge of the Timer Input signal.

#### **PWM SINGLE OUTPUT Mode**

- 0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon reload.

- 1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon reload.

#### **CAPTURE Mode**

- 0 = Count is captured on the rising edge of the Timer Input signal.

- 1 = Count is captured on the falling edge of the Timer Input signal.

#### COMPARE Mode

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer reload.

#### GATED Mode

- 0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

- 1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

#### CAPTURE/COMPARE Mode

- 0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

- 1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### **PWM DUAL OUTPUT Mode**

- 0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

- 1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

#### **CAPTURE RESTART Mode**

- 0 = Count is captured on the rising edge of the Timer Input signal.

- 1 = Count is captured on the falling edge of the Timer Input signal.

## Embedded in Life IXYS Company 92

## Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information about programming of the WDT\_RES Flash Option Bit, see **the** <u>Flash Option Bits</u> chapter on page 146.

#### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see the <u>Reset Status Register</u> section on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and F0823 Series are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. For more information about Stop Mode Recovery, see **the** <u>Reset and Stop Mode Recovery</u> chapter on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

nbedded in Life

100

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled,.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

#### Transmitting Data Using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

#### ILOG Embedded in Life IXYS Company 104

scheme is enabled, the UART Address Compare register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR Mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes

- Interrupt on matched address bytes and correctly framed data bytes

- Interrupt only on correctly framed data bytes

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare register. This mode introduces additional hard-ware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second

105

scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

### **External Driver Enable**

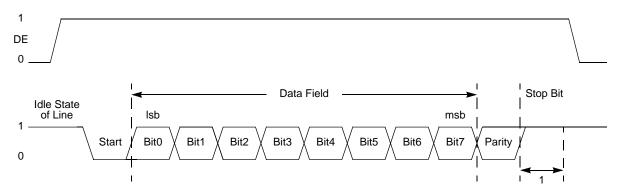

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data Register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

Figure 14. UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity)

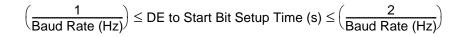

The Driver Enable to Start bit setup time is calculated as follows:

### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

#### ilog° Embedded in Life An∎IXYS Company 106

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error

dded in Life

118

passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

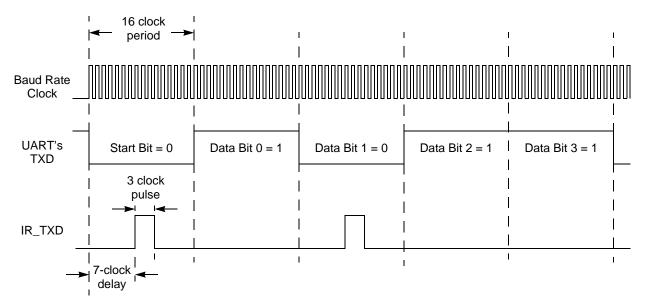

The baud rate is set by the UART's baud rate generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the infrared endec is enabled, the UART's TXD signal is internal to Z8 Encore! XP F0823 Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

ilog Embedded in Life An IXYS Company 172

### Table 105. Oscillator Control Register (OSCCTL)

| Bit             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6                                                                                                                                      | 5              | 4             | 3             | 2   | 1      | 0   |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|---------------|-----|--------|-----|--|--|--|--|

| Field           | INTEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reserved                                                                                                                               | WDTEN          | POFEN         | WDFEN         |     | SCKSEL |     |  |  |  |  |

| RESET           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                      | 1              | 0             | 0             | 0   | 0      | 0   |  |  |  |  |

| R/W             | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W                                                                                                                                    | R/W            | R/W           | R/W           | R/W | R/W    | R/W |  |  |  |  |

| Address         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | F86H                                                                                                                                   |                |               |               |     |        |     |  |  |  |  |

| Bit             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |                |               |               |     |        |     |  |  |  |  |

| [7]<br>INTEN    | 1 = Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nternal Precision Oscillator Enable<br>1 = Internal precision oscillator is enabled.<br>0 = Internal precision oscillator is disabled. |                |               |               |     |        |     |  |  |  |  |

| [6]             | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                        |                |               |               |     |        |     |  |  |  |  |

| [5]<br>WDTEN    | 1 = Watchd                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Timer Osci<br>og Timer os<br>og Timer os                                                                                               | cillator is en | abled.        |               |     |        |     |  |  |  |  |

| [4]<br>POFEN    | 1 = Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | scillator Fai<br>detection ar<br>detection ar                                                                                          | d recovery     | of primary o  |               |     |        |     |  |  |  |  |

| [3]<br>WDFEN    | 1 = Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Timer Osci<br>detection of<br>detection of                                                                                             | Watchdog 7     | Fimer oscilla | tor is enable |     |        |     |  |  |  |  |

| [2:0]<br>SCKSEL | 0 = Failure detection of Watchdog Timer oscillator is disabled.<br><b>System Clock Oscillator Select</b><br>000 = Internal precision oscillator functions as system clock at 5.53MHz.<br>001 = Internal precision oscillator functions as system clock at 32kHz.<br>010 = Reserved.<br>011 = Watchdog Timer oscillator functions as system clock.<br>100 = External clock signal on PB3 functions as system clock.<br>101 = Reserved.<br>110 = Reserved.<br>111 = Reserved. |                                                                                                                                        |                |               |               |     |        |     |  |  |  |  |

# eZ8 CPU Instruction Set

This chapter describes the following features of the eZ8 CPU instruction set: <u>Assembly Language Programming Introduction</u>: see page 174 <u>Assembly Language Syntax</u>: see page 175

eZ8 CPU Instruction Notation: see page 176

eZ8 CPU Instruction Classes: see page 178

eZ8 CPU Instruction Summary: see page 182

# **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called *statements*. Each statement can contain labels, operations, operands, and comments.

Labels are assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

ilog Embedded in Life An IXYS Company

187

| Assembly        |                                     |       | ress<br>ode | _ Opcode(s) |   |   | Fla  | ıgs |   |   | Fetch  | Instr. |

|-----------------|-------------------------------------|-------|-------------|-------------|---|---|------|-----|---|---|--------|--------|

| Mnemonic        | Symbolic Operation                  | dst   | src         | (Hex)       | С | Ζ | SVDH |     |   |   | Cycles |        |

| LDX dst, src    | dst ← src                           | r     | ER          | 84          | _ | _ | _    | _   | _ | _ | 3      | 2      |

|                 |                                     | lr    | ER          | 85          | - |   |      |     |   |   | 3      | 3      |

|                 |                                     | R     | IRR         | 86          | - |   |      |     |   |   | 3      | 4      |

|                 |                                     | IR    | IRR         | 87          | - |   |      |     |   |   | 3      | 5      |

|                 |                                     | r     | X(rr)       | 88          | - |   |      |     |   |   | 3      | 4      |

|                 |                                     | X(rr) | r           | 89          | - |   |      |     |   |   | 3      | 4      |

|                 |                                     | ER    | r           | 94          | - |   |      |     |   |   | 3      | 2      |

|                 |                                     | ER    | lr          | 95          | - |   |      |     |   |   | 3      | 3      |

|                 |                                     | IRR   | R           | 96          | - |   |      |     |   |   | 3      | 4      |

|                 |                                     | IRR   | IR          | 97          | - |   |      |     |   |   | 3      | 5      |

|                 |                                     | ER    | ER          | E8          | - |   |      |     |   |   | 4      | 2      |

|                 |                                     | ER    | IM          | E9          | - |   |      |     |   |   | 4      | 2      |

| LEA dst, X(src) | $dst \gets src + X$                 | r     | X(r)        | 98          | _ | _ | _    | -   | _ | _ | 3      | 3      |

|                 |                                     | rr    | X(rr)       | 99          | - |   |      |     |   |   | 3      | 5      |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR    |             | F4          | - | _ | _    | -   | _ | _ | 2      | 8      |

| NOP             | No operation                        |       |             | 0F          | _ | _ | _    | -   | _ | _ | 1      | 2      |

| OR dst, src     | $dst \gets dst \ OR \ src$          | r     | r           | 42          | _ | * | *    | 0   | _ | _ | 2      | 3      |

|                 |                                     | r     | lr          | 43          | - |   |      |     |   |   | 2      | 4      |

|                 |                                     | R     | R           | 44          | - |   |      |     |   |   | 3      | 3      |

|                 |                                     | R     | IR          | 45          | - |   |      |     |   |   | 3      | 4      |

|                 |                                     | R     | IM          | 46          | - |   |      |     |   |   | 3      | 3      |

|                 |                                     | IR    | IM          | 47          | - |   |      |     |   |   | 3      | 4      |

| ORX dst, src    | $dst \gets dst \ OR \ src$          | ER    | ER          | 48          | _ | * | *    | 0   | _ | _ | 4      | 3      |

|                 |                                     | ER    | IM          | 49          | - |   |      |     |   |   | 4      | 3      |

| POP dst         | $dst \leftarrow @SP$                | R     |             | 50          | _ | - | _    | -   | _ | _ | 2      | 2      |

|                 | $SP \leftarrow SP + 1$              | IR    |             | 51          | - |   |      |     |   |   | 2      | 3      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

ilog<sup>®</sup> Embedded in Life 191 An∎IXYS Company

| Assembly      |                             |     | Address<br>ModeOpcode(s) _ |       | Flags |   |   |   |   | _ Fetch | Instr. |   |

|---------------|-----------------------------|-----|----------------------------|-------|-------|---|---|---|---|---------|--------|---|

| Mnemonic      | Symbolic Operation          | dst | src                        | (Hex) | С     | Ζ | S | ۷ | D | Н       | Cycles |   |

| XOR dst, src  | $dst \gets dst \ XOR \ src$ | r   | r                          | B2    | _     | * | * | 0 | _ | _       | 2      | 3 |

|               |                             | r   | lr                         | B3    |       |   |   |   |   |         | 2      | 4 |

|               |                             | R   | R                          | B4    |       |   |   |   |   |         | 3      | 3 |

|               |                             | R   | IR                         | B5    |       |   |   |   |   |         | 3      | 4 |

|               |                             | R   | IM                         | B6    |       |   |   |   |   |         | 3      | 3 |

|               |                             | IR  | IM                         | B7    |       |   |   |   |   |         | 3      | 4 |

| XORX dst, src | $dst \gets dst \ XOR \ src$ | ER  | ER                         | B8    | _     | * | * | 0 | _ | _       | 4      | 3 |

|               |                             | ER  | IM                         | B9    |       |   |   |   |   |         | 4      | 3 |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

PS024315-1011

# Embedded in Life An IXYS Company

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F0823 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 120 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                       | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                  | -40     | +105    | °C    |       |

| Storage temperature                                             | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>              | -0.3    | +5.5    | V     | 1     |

|                                                                 | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$                | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin             | -5      | +5      | μA    |       |

| Maximum output current from active output pin                   | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0°C to 70°C                   |         |         |       |       |

| Total power dissipation                                         |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                  |         |         |       |       |

| Total power dissipation                                         |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                  |         |         |       |       |

| Total power dissipation                                         |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 125     | mA    |       |

| Natas, Operating temperature is enceified in DC Characteristics |         |         |       |       |

| Table 1 | 20. Ab | solute N | laximum | Ratings |

|---------|--------|----------|---------|---------|

|---------|--------|----------|---------|---------|

Notes: Operating temperature is specified in DC Characteristics.

This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

2. This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

## Embedded in Life An IXYS Company 197

# **DC Characteristics**

Table 121 lists the DC characteristics of the Z8 Encore! XP F0823 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

|                  |                              |                     | -40°C to -<br>otherwise | ⊦105°C<br>specified) |       |                                                                                                                                                                |

|------------------|------------------------------|---------------------|-------------------------|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                    | Minimum             | Typical                 | Maximum              | Units | Conditions                                                                                                                                                     |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                       | 3.6                  | V     |                                                                                                                                                                |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -                       | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                                |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                       | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all sig-<br>nal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                       | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when pro-<br>grammable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | -                       | 0.4                  | V     | I <sub>OL</sub> = 2mA; V <sub>DD</sub> = 3.0V<br>High Output Drive disabled.                                                                                   |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | -                       | -                    | V     | $I_{OH} = -2mA; V_{DD} = 3.0V$<br>High Output Drive disabled.                                                                                                  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -                       | 0.6                  | V     | $I_{OL}$ = 20mA; $V_{DD}$ = 3.3 V<br>High Output Drive enabled.                                                                                                |

| V <sub>OH2</sub> | High Level Output<br>Voltage | 2.4                 | -                       | -                    | V     | I <sub>OH</sub> = -20mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                                 |

| I <sub>IH</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.002          | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>IL</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.007          | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>TL</sub>  | Tristate Leakage<br>Current  | -                   | -                       | <u>+</u> 5           | μA    |                                                                                                                                                                |

| Table 121. | DC | Characteristics |

|------------|----|-----------------|

|            |    | •               |

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

ilog nbedded in Life

# **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 125 tabulates the electrical characteristics of the POR and VBO blocks.

#### Table 125. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                   |                                                                                  | <b>T</b> <sub>A</sub> = - | –40°C to +′     |         |       |                                                                                           |

|-------------------|----------------------------------------------------------------------------------|---------------------------|-----------------|---------|-------|-------------------------------------------------------------------------------------------|

| Symbol            | Parameter                                                                        | Minimum                   | Typical*        | Maximum | Units | Conditions                                                                                |

| V <sub>POR</sub>  | Power-On Reset Voltage<br>Threshold                                              | 2.20                      | 2.45            | 2.70    | V     | $V_{DD} = V_{POR}$                                                                        |

| V <sub>VBO</sub>  | Voltage Brown-Out Reset Volt-<br>age Threshold                                   | 2.15                      | 2.40            | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                        |

|                   | $V_{\mbox{POR}}$ to $V_{\mbox{VBO}}$ hysteresis                                  |                           | 50              | 75      | mV    |                                                                                           |

|                   | Starting V <sub>DD</sub> voltage to ensure valid Power-On Reset.                 | -                         | V <sub>SS</sub> | _       | V     |                                                                                           |

| T <sub>ANA</sub>  | Power-On Reset Analog Delay                                                      | -                         | 70              | -       | μs    | $V_{DD} > V_{POR};$<br>$T_{POR}$ Digital<br>Reset delay fol-<br>lows $T_{ANA}$            |

| T <sub>POR</sub>  | Power-On Reset Digital Delay                                                     |                           | 16              |         | μs    | 66 Internal Precision Oscillator<br>cycles + IPO<br>startup time<br>(T <sub>IPOST</sub> ) |

| T <sub>SMR</sub>  | Stop Mode Recovery                                                               |                           | 16              |         | μs    | 66 Internal Precision Oscillator cycles                                                   |

| T <sub>VBO</sub>  | Voltage Brown-Out Pulse<br>Rejection Period                                      | _                         | 10              | _       | μs    | Period of time in<br>which $V_{DD} < V_{VBO}$ without<br>generating a<br>Reset.           |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to transition from $V_{SS}$ to $V_{POR}$ to ensure valid Reset | 0.10                      | -               | 100     | ms    |                                                                                           |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                    |                           | 20              |         | ns    | For any SMR pin<br>or for the Reset<br>pin when it is<br>asserted in STOF<br>Mode.        |

guidance only and are not tested in production.

Embedded in Life

|                          |                                                    | $T_A =$    | = 3.0V to<br>= 0°C to +7<br>otherwise | ′0°C       |                                |                                                                                                |  |

|--------------------------|----------------------------------------------------|------------|---------------------------------------|------------|--------------------------------|------------------------------------------------------------------------------------------------|--|

| Symbol                   | Parameter                                          | Minimum    | Typical Maximum                       |            | Units                          | Conditions                                                                                     |  |

|                          | Resolution                                         | 10         |                                       | -          | bits                           |                                                                                                |  |

|                          | Differential Nonlinearity (DNL)                    | -1.0       | -                                     | 1.0        | LSB <sup>3</sup>               | External V <sub>REF</sub> = 2.0V;<br>R <sub>S</sub> $\leftarrow$ 3.0 kΩ                        |  |

|                          | Integral Nonlinearity (INL)                        | -3.0       | -                                     | 3.0        | LSB <sup>3</sup>               | External V <sub>REF</sub> = 2.0V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$                |  |

|                          | Offset Error with Calibration                      |            | <u>+</u> 1                            |            | LSB <sup>3</sup>               |                                                                                                |  |

|                          | Absolute Accuracy with Calibration                 |            | <u>+</u> 3                            |            | LSB <sup>3</sup>               |                                                                                                |  |

| V <sub>REF</sub>         | Internal Reference Voltage                         | 1.0<br>2.0 | 1.1<br>2.2                            | 1.2<br>2.4 | V                              | REFSEL=01<br>REFSEL=10                                                                         |  |

| V <sub>REF</sub>         | Internal Reference Varia-<br>tion with Temperature |            | <u>+</u> 1.0                          |            | %                              | Temperature variation with $V_{DD} = 3.0$                                                      |  |

| V <sub>REF</sub>         | Internal Reference Voltage Variation with $V_{DD}$ |            | <u>+</u> 0.5                          |            | %                              | Supply voltage varia-<br>tion with $T_A = 30^{\circ}C$                                         |  |

| R <sub>RE-</sub><br>FOUT | Reference Buffer Output<br>Impedance               |            | 850                                   |            | W                              | When the internal ref-<br>erence is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |  |

|                          | Single-Shot Conversion<br>Time                     | _          | 5129                                  | _          | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                        |  |

|                          |                                                    |            | 10258                                 |            |                                | Temperature sensor measurement                                                                 |  |

|                          | Continuous Conversion<br>Time                      | -          | 256                                   | -          | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                        |  |

|                          |                                                    |            | 512                                   |            |                                | Temperature sensor measurement                                                                 |  |

#### Table 128. Analog-to-Digital Converter Electrical Characteristics and Timing

Notes:

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- Devices are factory calibrated at V<sub>DD</sub> = 3.3 V and T<sub>A</sub> = +30°C, so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

An∎IXYS Company

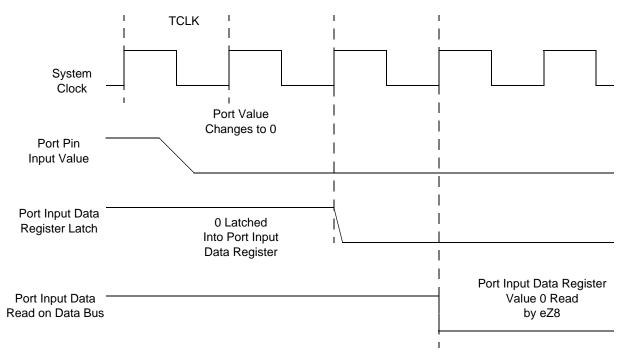

| Table 130. GPIO Port Input Timing |  |

|-----------------------------------|--|

|                                   |  |

|                     |                                                                                                    | Delay (ns) |         |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (Not pictured)                            | 5          | _       |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (Not pictured)                             | 0          | _       |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO Port Pins enabled as SMR sources) | 1 μs       |         |  |

> ilog Embedded in Life An IXYS Company 213

| Part Number                                                                    | Flash<br>RAM |      | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|--------------------------------------------------------------------------------|--------------|------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP F0823 Series with 4 KB Flash, 10-Bit Analog-to-Digital Converter |              |      |            |                        |                     |                |                     |

| Standard Temperature: 0°C to 70°C                                              |              |      |            |                        |                     |                |                     |

| Z8F0423PB005SG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005SG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005SG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005SG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005SG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005SG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005SG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005SG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005SG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: –40°C to 105°C                                           |              |      |            |                        |                     |                |                     |

| Z8F0423PB005EG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005EG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005EG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005EG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005EG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005EG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005EG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005EG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005EG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

> ilog Embedded in Life An IXYS Company 214

|                                            |              |           |            |                        |                     | -              |                     |

|--------------------------------------------|--------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                                | Flash<br>RAM | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 Series with 4 KB Flash |              |           |            |                        |                     |                |                     |

| Standard Temperature: 0°C to 70°C          |              |           |            |                        |                     |                |                     |

| Z8F0413PB005SG                             | 4 KB 1 KB    | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005SG                             | 4 KB 1 KB    | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005SG                             | 4 KB 1 KB    | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005SG                             | 4 KB 1 KB    | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005SG                             | 4 KB 1 KB    | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005SG                             | 4 KB 1 KB    | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005SG                             | 4 KB 1 KB    | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005SG                             | 4 KB 1 KB    | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005SG                             | 4 KB 1 KB    | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperature: –40°C to 105°C       |              |           |            |                        |                     |                |                     |

| Z8F0413PB005EG                             | 4 KB 1 KB    | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005EG                             | 4 KB 1 KB    | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005EG                             | 4 KB 1 KB    | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005EG                             | 4 KB 1 KB    | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005EG                             | 4 KB 1 KB    | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005EG                             | 4 KB 1 KB    | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005EG                             | 4 KB 1 KB    | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005EG                             | 4 KB 1 KB    | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005EG                             | 4 KB 1 KB    | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.