Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 5MHz                                                      |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 6                                                         |  |

| Program Memory Size        | 1KB (1K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 256 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113sb005sg |  |

Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2011 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

### Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| OCD Status Register                                     | 168 |

|---------------------------------------------------------|-----|

| Oscillator Control                                      | 169 |

| Operation                                               |     |

| System Clock Selection                                  |     |

| Clock Failure Detection and Recovery                    |     |

| Oscillator Control Register Definitions                 | 171 |

| Internal Precision Oscillator                           |     |

| Operation                                               | 173 |

| eZ8 CPU Instruction Set                                 | 174 |

| Assembly Language Programming Introduction              | 174 |

| Assembly Language Syntax                                | 175 |

| eZ8 CPU Instruction Notation                            |     |

| eZ8 CPU Instruction Classes                             |     |

| eZ8 CPU Instruction Summary                             | 182 |

| Opcode Maps                                             | 192 |

| Electrical Characteristics                              | 196 |

| Absolute Maximum Ratings                                | 196 |

| DC Characteristics                                      | 197 |

| AC Characteristics                                      |     |

| On-Chip Peripheral AC and DC Electrical Characteristics |     |

| General Purpose I/O Port Input Data Sample Timing       |     |

| General Purpose I/O Port Output Timing                  |     |

| On-Chip Debugger Timing                                 |     |

| UART Timing                                             | 208 |

| Packaging                                               | 210 |

| Ordering Information                                    | 211 |

| Part Number Suffix Designations                         | 220 |

| Index                                                   | 221 |

| Customer Support                                        | 230 |

| Customer Support                                        |     |

# Z8 Encore! XP® F0823 Series Product Specification

| Table 34. | LED Drive Level Low Register (LEDLVLL)           | 53  |

|-----------|--------------------------------------------------|-----|

| Table 35. | Trap and Interrupt Vectors in Order of Priority  | 55  |

| Table 36. | Interrupt Request 0 Register (IRQ0)              | 59  |

| Table 37. | Interrupt Request 1 Register (IRQ1)              | 60  |

| Table 38. | Interrupt Request 2 Register (IRQ2)              | 61  |

| Table 39. | IRQ0 Enable and Priority Encoding                | 61  |

| Table 40. | IRQ0 Enable High Bit Register (IRQ0ENH)          | 62  |

| Table 41. | IRQ0 Enable Low Bit Register (IRQ0ENL)           | 62  |

| Table 42. | IRQ1 Enable and Priority Encoding                | 63  |

| Table 43. | IRQ1 Enable Low Bit Register (IRQ1ENL)           | 64  |

| Table 44. | IRQ1 Enable High Bit Register (IRQ1ENH)          | 64  |

| Table 45. | IRQ2 Enable and Priority Encoding                | 65  |

| Table 46. | IRQ2 Enable High Bit Register (IRQ2ENH)          | 65  |

| Table 47. | IRQ2 Enable Low Bit Register (IRQ2ENL)           | 66  |

| Table 48. | Interrupt Edge Select Register (IRQES)           | 66  |

| Table 49. | Shared Interrupt Select Register (IRQSS)         | 67  |

| Table 50. | Interrupt Control Register (IRQCTL)              | 68  |

| Table 51. | Timer 0–1 High Byte Register (TxH)               | 84  |

| Table 52. | Timer 0–1 Low Byte Register (TxL)                | 84  |

| Table 53. | Timer 0–1 Reload High Byte Register (TxRH)       | 85  |

| Table 54. | Timer 0–1 Reload Low Byte Register (TxRL)        | 85  |

| Table 55. | Timer 0–1 PWM High Byte Register (TxPWMH)        | 86  |

| Table 56. | Timer 0–1 PWM Low Byte Register (TxPWML)         | 86  |

| Table 57. | Timer 0–1 Control Register 0 (TxCTL0)            | 87  |

| Table 58. | Timer 0–1 Control Register 1 (TxCTL1)            | 88  |

| Table 59. | Watchdog Timer Approximate Time-Out Delays       | 91  |

| Table 60. | Watchdog Timer Control Register (WDTCTL)         | 94  |

| Table 61. | Watchdog Timer Reload Upper Byte Register (WDTU) | 95  |

| Table 62. | Watchdog Timer Reload High Byte Register (WDTH)  |     |

| Table 63. | Watchdog Timer Reload Low Byte Register (WDTL)   | 95  |

| Table 64. | UART Transmit Data Register (U0TXD)              | 109 |

| Table 65. | UART Receive Data Register (U0RXD)               | 109 |

| Table 66. | UART Status 0 Register (U0STAT0)                 | 110 |

| Table 67. | UART Status 1 Register (U0STAT1)                 | 111 |

| Table 68. | UART Control 0 Register (U0CTL0)                 | 112 |

| Table 69. | UART Control 1 Register (U0CTL1)                 |     |

|           |                                                  |     |

6

#### **On-Chip Debugger**

F0823 Series products feature an integrated On-Chip Debugger. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

## Reset and Stop Mode Recovery

The Reset Controller within the Z8 Encore! XP F0823 Series controls Reset and Stop Mode Recovery operation and provides indication of low supply voltage conditions. In typical operation, the following events cause a Reset:

- Power-On Reset (POR)

- Voltage Brown-Out (VBO)

- Watchdog Timer time-out (when configured by the WDT\_RES Flash Option Bit to initiate a reset)

- External RESET pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the device is in STOP Mode, a Stop Mode Recovery is initiated by either of the following:

- Watchdog Timer time-out

- GPIO port input pin transition on an enabled Stop Mode Recovery source

The VBO circuitry on the device performs the following function:

Generates the VBO reset when the supply voltage drops below a minimum safe level

#### **Reset Types**

F0823 Series MCUs provide several different types of Reset operations. Stop Mode Recovery is considered a form of Reset. Table 9 lists the types of Reset and their operating characteristics. The duration of a System Reset is longer if the external crystal oscillator is enabled by the Flash option bits; this configuration allows additional time for oscillator startup.

Table 9. Reset and Stop Mode Recovery Characteristics and Latency

|                       | Reset Characteristics and Latency                |         |                                                               |  |  |  |

|-----------------------|--------------------------------------------------|---------|---------------------------------------------------------------|--|--|--|

| Reset Type            | Control Registers                                | eZ8 CPU | Reset Latency (Delay)                                         |  |  |  |

| System Reset          | Reset (as applicable)                            | Reset   | 66 Internal Precision Oscillator Cycles                       |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except WDT_CTL and OSC_CTL registers | Reset   | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |

# General-Purpose Input/Output

Z8 Encore! XP F0823 Series products support a maximum of 24 port pins (Ports A–C) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality, and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

#### **GPIO Port Availability By Device**

Table 15 lists the port pins available with each device and package type.

Table 15. Port Availability by Device and Package Type

| Devices                                                                                      | Package | 10-Bit ADC | Port A | Port B | Port C | Total I/O |

|----------------------------------------------------------------------------------------------|---------|------------|--------|--------|--------|-----------|

| Z8F0823SB, Z8F0823PB<br>Z8F0423SB, Z8F0423PB<br>Z8F0223SB, Z8F0223PB<br>Z8F0123SB, Z8F0123PB | 8-pin   | Yes        | [5:0]  | No     | No     | 6         |

| Z8F0813SB, Z8F0813PB<br>Z8F0413SB, Z8F0413PB<br>Z8F0213SB, Z8F0213PB<br>Z8F0113SB, Z8F011vPB | 8-pin   | No         | [5:0]  | No     | No     | 6         |

| Z8F0823PH, Z8F0823HH<br>Z8F0423PH, Z8F0423HH<br>Z8F0223PH, Z8F0223HH<br>Z8F0123PH, Z8F0123HH | 20-pin  | Yes        | [7:0]  | [3:0]  | [3:0]  | 16        |

| Z8F0813PH, Z8F0813HH<br>Z8F0413PH, Z8F0413HH<br>Z8F0213PH, Z8F0213HH<br>Z8F0113PH, Z8F0113HH | 20-pin  | No         | [7:0]  | [3:0]  | [3:0]  | 16        |

| Z8F0823PJ, Z8F0823SJ<br>Z8F0423PJ, Z8F0423SJ<br>Z8F0223PJ, Z8F0223SJ<br>Z8F0123PJ, Z8F0123SJ | 28-pin  | Yes        | [7:0]  | [5:0]  | [7:0]  | 22        |

| Z8F0813PJ, Z8F0813SJ<br>Z8F0413PJ, Z8F0413SJ<br>Z8F0213PJ, Z8F0213SJ<br>Z8F0113PJ, Z8F0113SJ | 28-pin  | No         | [7:0]  | [7:0]  | [7:0]  | 24        |

PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{\rm DD}$  even with the pull-ups enabled.

## **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see the <u>Oscillator Control Register Definitions</u> section on page 171) such that the external oscillator is selected as the system clock. For 8-pin devices, use PA1 instead of PB3.

## **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see the <a href="Interrupt Controller">Interrupt Controller</a> chapter on page 54.

#### **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data, and output data. Table 18 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

Table 18. GPIO Port Registers and Subregisters

| Port Register    |                                                              |

|------------------|--------------------------------------------------------------|

| Mnemonic         | Port Register Name                                           |

| P <i>x</i> ADDR  | Port A–C Address Register (Selects subregisters).            |

| P <i>x</i> CTL   | Port A–C Control Register (Provides access to subregisters). |

| PxIN             | Port A–C Input Data Register.                                |

| P <i>x</i> OUT   | Port A–C Output Data Register.                               |

| Port Subregister |                                                              |

| Mnemonic         | Port Register Name                                           |

| P <i>x</i> DD    | Data Direction.                                              |

| P <i>x</i> AF    | Alternate Function.                                          |

| P <i>x</i> OC    | Output Control (Open-Drain).                                 |

Table 43. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|---------|---------|--------|--------|--------|--------|--------|--------|

| Field   | PA7VENH | PA6CENH | PA5ENH | PA4ENH | PA3ENH | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address |         | FC4H    |        |        |        |        |        |        |

| Bit             | Description                                                                                                                                                   |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VENH  | Port A Bit[7] Interrupt Request Enable High Bit                                                                                                               |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit                                                                                                 |

| [5:0]<br>PAxENH | Port A Bit[x] Interrupt Request Enable High Bit For selection of Port A as the interrupt source, see the Shared Interrupt Select Register section on page 67. |

| Note: x indic   | cates the specific GPIO Port A pin number (5–0).                                                                                                              |

Table 44. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|---------|---------|--------|--------|--------|--------|--------|--------|

| Field   | PA7VENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |

| RESET   | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address |         | FC5H    |        |        |        |        |        |        |

| Bit             | Description                                                  |  |

|-----------------|--------------------------------------------------------------|--|

| [7]<br>PA7VENL  | Port A Bit[7] Interrupt Request Enable Low Bit               |  |

| [6]<br>PA6CENL  | Port A Bit[7] or Comparator Interrupt Request Enable Low Bit |  |

| [5:0]<br>PAxENL | Port A Bit[x] Interrupt Request Enable Low Bit               |  |

| Note: x indi    | icates the specific GPIO Port A pin number (5–0)             |  |

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | Transmitter Data Register Empty This bit indicates that the UART Transmit Data Register is empty and ready for additional data. Writing to the UART Transmit Data Register resets this bit.  0 = Do not write to the UART Transmit Data Register.  1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted. |

| [1]<br>TXE  | Transmitter Empty This bit indicates that the transmit shift register is empty and character transmission is finished.  0 = Data is currently transmitting.  1 = Transmission is complete.                                                                                                                                                       |

| [0]<br>CTS  | CTS Signal When this bit is read, it returns the level of the CTS signal. This signal is active Low.                                                                                                                                                                                                                                             |

## **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 67. UART Status 1 Register (U0STAT1)

| Bit     | 7 | 6    | 5    | 4     | 3   | 2   | 1      | 0    |

|---------|---|------|------|-------|-----|-----|--------|------|

| Field   |   |      | Rese | erved |     |     | NEWFRM | MPRX |

| RESET   | 0 | 0    | 0    | 0     | 0   | 0   | 0      | 0    |

| R/W     | R | R    | R    | R     | R/W | R/W | R      | R    |

| Address |   | F44H |      |       |     |     |        |      |

| Bit           | Description                                                                                                                                                                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | Reserved These bits are reserved; R/W bits must be programmed to 000000 during writes and 000000 when read.                                                                                                                                          |

| [1]<br>NEWFRM | New Frame A status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.  0 = The current byte is not the first data byte of a new frame.  1 = The current byte is the first data byte of a new frame. |

| [0]<br>MPRX   | Multiprocessor Receive Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data Register resets this bit to 0.                                                                                           |

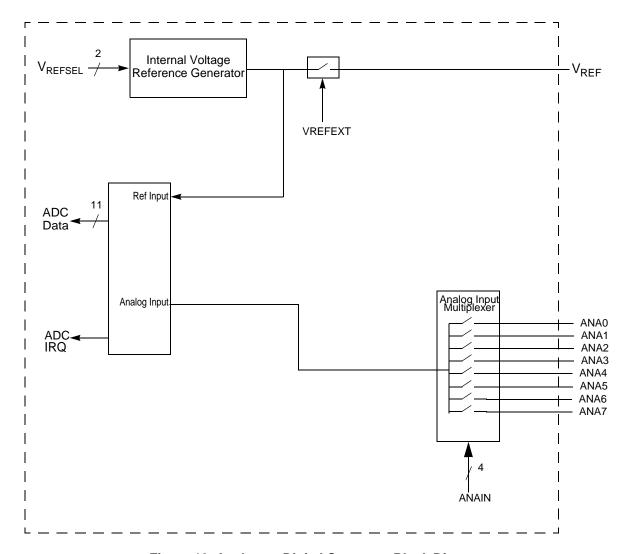

Figure 19. Analog-to-Digital Converter Block Diagram

## **Operation**

The output of the ADC is an 11-bit, signed, two's-complement digital value. The output generally ranges from 0 to  $\pm 1023$ , but offset errors can cause small negative values.

The ADC registers return 13 bits of data, but the two LSBs are intended for compensation use only. When the compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

136

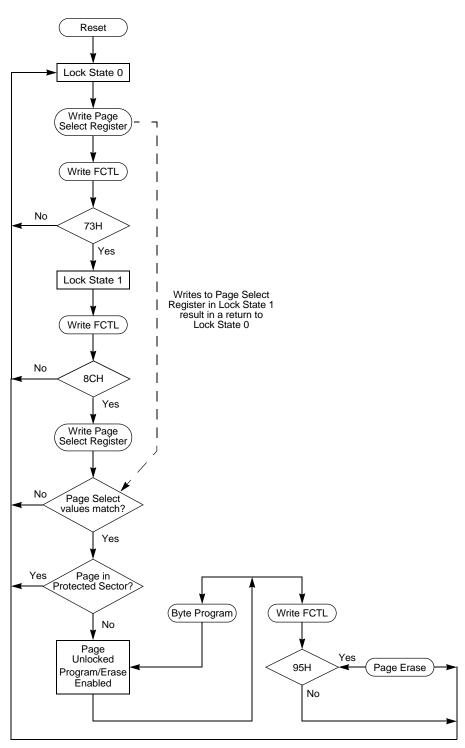

Figure 21. Flash Controller Operation Flowchart

#### Flash Sector Protect Register

The Flash Sector Protect (FPROT) Register is shared with the Flash Page Select Register. When the Flash Control Register is written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

Table 84. Flash Sector Protect Register (FPROT)

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address |        | FF9H   |        |        |        |        |        |        |

#### Bit Description

#### [7] Sector Protection

SPROT*n* Each bit corresponds to a 1024-byte Flash sector on devices in the 8K range, while the remaining devices correspond to a 512-byte Flash sector. To determine the appropriate Flash memory sector address range and sector number for your Z8F0823 Series product, please refer to <u>Table 79</u> on page 134 and to Figure 20, which follows the table.

- For Z8F08x3 and Z8F04x3 devices, all bits are used.

- For Z8F02x3 devices, the upper 4 bits are unused.

- For Z8F01x3 devices, the upper 6 bits are unused.

Note: n indicates the specific Flash sector (7–0).

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$

#### Table 92. Trim Option Bits at 0001H

| Bit                                             | 7                             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field                                           | Reserved                      |     |     |     |     |     |     |     |

| RESET                                           | U                             | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 0021H |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |     |     |     |     |     |     |     |

| Bit   | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                  |

|       | These bits are reserved. Altering this register may result in incorrect device operation. |

#### Table 93. Trim Option Bits at 0002H (TIPO)

| Bit       | 7                                               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|-------------------------------------------------|---|---|---|---|---|---|---|

| Field     | IPO_TRIM                                        |   |   |   |   |   |   |   |

| RESET     | U                                               |   |   |   |   |   |   |   |

| R/W       | R/W                                             |   |   |   |   |   |   |   |

| Address   | Information Page Memory 0022H                   |   |   |   |   |   |   |   |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |   |   |   |   |   |   |   |

| Bit      | Description                                                   |

|----------|---------------------------------------------------------------|

| [7:0]    | Internal Precision Oscillator Trim Byte                       |

| IPO_TRIM | Contains trimming bits for the Internal Precision Oscillator. |

## **Zilog Calibration Data**

This section briefly describes the features of the following Flash Option Bit calibration registers.

ADC Calibration Data: see page 153

Serialization Data: see page 154

Randomized Lot Identifier: see page 154

## **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of Z8 Encore! XP F0823 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 101 is a summary of the OCD commands. Each OCD command is described in further detail in the pages that follow this table. <u>Table 102</u> on page 167 also indicates those commands that operate when the device is not in DEBUG Mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

**Table 101. OCD Commands**

| Debug Command              | Command<br>Byte | Enabled when not in DEBUG Mode? | Disabled by Flash Read Protect Option Bit                                                                                                                        |

|----------------------------|-----------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                             | -                                                                                                                                                                |

| Reserved                   | 01H             | _                               | _                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                             | _                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                               | _                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                             | Cannot clear DBGMODE bit.                                                                                                                                        |

| Read OCD Control Register  | 05H             | Yes                             | _                                                                                                                                                                |

| Write Program Counter      | 06H             | _                               | Disabled.                                                                                                                                                        |

| Read Program Counter       | 07H             | _                               | Disabled.                                                                                                                                                        |

| Write Register             | 08H             | -                               | Only writes of the Flash Memory Control registers are allowed. Additionally, only the Mass Erase command is allowed to be written to the Flash Control Register. |

| Read Register              | 09H             | _                               | Disabled.                                                                                                                                                        |

| Write Program Memory       | 0AH             | -                               | Disabled.                                                                                                                                                        |

| Read Program Memory        | 0BH             | _                               | Disabled.                                                                                                                                                        |

| Write Data Memory          | 0CH             | _                               | Yes.                                                                                                                                                             |

| Read Data Memory           | 0DH             | -                               | _                                                                                                                                                                |

| Read Program Memory CRC    | 0EH             | _                               | _                                                                                                                                                                |

| Reserved                   | 0FH             | _                               | _                                                                                                                                                                |

| Step Instruction           | 10H             | _                               | Disabled.                                                                                                                                                        |

| Stuff Instruction          | 11H             |                                 | Disabled.                                                                                                                                                        |

| Execute Instruction        | 12H             | _                               | Disabled.                                                                                                                                                        |

| Reserved                   | 13H-FFH         | _                               | _                                                                                                                                                                |

Table 107. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Z8 Encore! XP Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

#### **eZ8 CPU Instruction Notation**

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is noted in Table 108.

**Table 108. Notational Shorthand**

| Notation | Description                    | Operand | Range                                                                             |

|----------|--------------------------------|---------|-----------------------------------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                  |

| CC       | Condition Code                 | _       | See the Condition Codes overview in the <u>eZ8 CPU</u> Core User Manual (UM0128). |

| DA       | Direct Address                 | Addrs   | Addrs represents a number in the range of 0000H to FFFFH.                         |

| ER       | Extended Addressing Register   | Reg     | Reg represents a number in the range of 000H to FFFH.                             |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH.                                              |

| Ir       | Indirect Working Register      | @Rn     | n = 0–15.                                                                         |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH.                              |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                 |

| IRR      | Indirect Register Pair         | @Reg    | Reg represents an even number in the range 00H to FEH                             |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                         |

| r        | Working Register               | Rn      | n = 0–15.                                                                         |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH.                              |

**Table 115. Logical Instructions**

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| COM      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

**Table 116. Program Control Instructions**

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

**Table 117. Rotate and Shift Instructions**

| Mnemonic | Operands | Instruction               |

|----------|----------|---------------------------|

| BSWAP    | dst      | Bit Swap                  |

| RL       | dst      | Rotate Left               |

| RLC      | dst      | Rotate Left through Carry |

Table 118. eZ8 CPU Instruction Summary (Continued)

| Assembly         |                                                                                  | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   |   | Fetch | Instr. |

|------------------|----------------------------------------------------------------------------------|-----------------|-----|-------------|-------|---|---|---|---|---|-------|--------|

| Mnemonic         | Symbolic Operation                                                               | dst             | src | (Hex)       | С     | Z | S | ٧ | D | Н |       | Cycles |

| ADD dst, src     | dst ← dst + src                                                                  | r               | r   | 02          | *     | * | * | * | 0 | * | 2     | 3      |

|                  |                                                                                  | r               | lr  | 03          |       |   |   |   |   |   | 2     | 4      |

|                  |                                                                                  | R               | R   | 04          | •     |   |   |   |   |   | 3     | 3      |

|                  |                                                                                  | R               | IR  | 05          | •     |   |   |   |   |   | 3     | 4      |

|                  |                                                                                  | R               | IM  | 06          | •     |   |   |   |   |   | 3     | 3      |

|                  |                                                                                  | IR              | IM  | 07          | •     |   |   |   |   |   | 3     | 4      |

| ADDX dst, src    | dst ← dst + src                                                                  | ER              | ER  | 08          | *     | * | * | * | 0 | * | 4     | 3      |

|                  |                                                                                  | ER              | IM  | 09          | •     |   |   |   |   |   | 4     | 3      |

| AND dst, src     | dst ← dst AND src                                                                | r               | r   | 52          | -     | * | * | 0 | - | - | 2     | 3      |

|                  |                                                                                  | r               | lr  | 53          | •     |   |   |   |   |   | 2     | 4      |

|                  |                                                                                  | R               | R   | 54          | •     |   |   |   |   |   | 3     | 3      |

|                  |                                                                                  | R               | IR  | 55          | •     |   |   |   |   |   | 3     | 4      |

|                  |                                                                                  | R               | IM  | 56          |       |   |   |   |   |   | 3     | 3      |

|                  |                                                                                  | IR              | IM  | 57          | •     |   |   |   |   |   | 3     | 4      |

| ANDX dst, src    | dst ← dst AND src                                                                | ER              | ER  | 58          | -     | * | * | 0 | - | - | 4     | 3      |

|                  |                                                                                  | ER              | IM  | 59          | •     |   |   |   |   |   | 4     | 3      |

| ATM              | Block all interrupt and DMA requests during execution of the next 3 instructions |                 |     | 2F          | _     | _ | _ | - | _ | - | 1     | 2      |

| BCLR bit, dst    | dst[bit] ← 0                                                                     | r               |     | E2          | _     | - | _ | _ | _ | _ | 2     | 2      |

| BIT p, bit, dst  | dst[bit] ← p                                                                     | r               |     | E2          | -     | - | _ | 0 | _ | _ | 2     | 2      |

| BRK              | Debugger Break                                                                   |                 |     | 00          | _     | - | _ | _ | _ | _ | 1     | 1      |

| BSET bit, dst    | dst[bit] ← 1                                                                     | r               |     | E2          | -     | - | - | 0 | - | - | 2     | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                              | R               |     | D5          | Χ     | * | * | 0 | - | - | 2     | 2      |

| BTJ p, bit, src, | if src[bit] = p                                                                  |                 | r   | F6          | _     | - | - | - | _ | - | 3     | 3      |

| dst              | PC ← PC + X                                                                      |                 | lr  | F7          | •     |   |   |   |   |   | 3     | 4      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

#### **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

**Table 123. AC Characteristics**

|                                            |                        | T <sub>A</sub> = -40°C<br>(unless o | V to 3.6V<br>to +105°C<br>otherwise<br>ted) |       |                                            |  |

|--------------------------------------------|------------------------|-------------------------------------|---------------------------------------------|-------|--------------------------------------------|--|

| Symbol Parameter                           |                        | Minimum                             | Maximum                                     | Units | Conditions                                 |  |

| F <sub>SYSCLK</sub> System Clock Frequency |                        | _                                   | 20.0*                                       | MHz   | Read-only from Flash memory                |  |

|                                            |                        | 0.032768                            | 20.0 <sup>1</sup>                           | MHz   | Program or erasure of the Flash memory.    |  |

| T <sub>XIN</sub>                           | System Clock Period    | 50                                  | _                                           | ns    | T <sub>CLK</sub> = 1/F <sub>SYSCLK</sub> . |  |

| T <sub>XINH</sub>                          | System Clock High Time | 20                                  | 30                                          | ns    | T <sub>CLK</sub> = 50ns.                   |  |

| T <sub>XINL</sub>                          | System Clock Low Time  | 20                                  | 30                                          | ns    | T <sub>CLK</sub> = 50ns.                   |  |

| T <sub>XINR</sub>                          | System Clock Rise Time | _                                   | 3                                           | ns    | T <sub>CLK</sub> = 50ns.                   |  |

| T <sub>XINF</sub>                          | System Clock Fall Time | _                                   | 3                                           | ns    | $T_{CLK} = 50$ ns.                         |  |

**Table 124. Internal Precision Oscillator Electrical Characteristics**

$V_{DD}$  = 2.7V to 3.6V  $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$ (unless otherwise stated) **Symbol Parameter Minimum Maximum Units Conditions Typical** Internal Precision Oscillator 5.53 MHz  $V_{DD} = 3.3V$  $F_{IPO}$  $T_A = 30$ °C Frequency (High Speed)  $F_{IPO}$ Internal Precision Oscillator 32.7 kHz  $V_{DD} = 3.3 V$ Frequency (Low Speed)  $T_A = 30$ °C Internal Precision Oscillator  $F_{IPO}$ % <u>+</u>1 <u>+</u>4 Error  $T_{IPOST}$ Internal Precision Oscillator 3 μs Startup Time

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

|                                            |       |        |          |            |                        |                     | 5              | (                       |

|--------------------------------------------|-------|--------|----------|------------|------------------------|---------------------|----------------|-------------------------|

| Part Number                                | Flash | RAM    | VO Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description             |

| Z8 Encore! XP F0823 Series Development Kit |       |        |          |            |                        |                     |                |                         |

| Z8F08A28100KITG                            |       | Z8 En  | core! X  | P F08      | 2A Serie               | es Dev              | elopme         | nt Kit (20- and 28-Pin) |

| Z8F04A28100KITG                            |       | Z8 En  | core! X  | P F04      | 2A Serie               | es Dev              | elopme         | nt Kit (20- and 28-Pin) |

| Z8F04A08100KITG                            |       | Z8 En  | core! X  | P F04      | 2A Serie               | es Dev              | elopme         | nt Kit (8-Pin)          |

| ZUSBSC00100ZACG                            |       | USB S  | Smart C  | Cable A    | Accesso                | ry Kit              |                |                         |

| ZUSBOPTSC01ZACG                            |       | Opto-l | Isolated | d USB      | Smart C                | Cable A             | Accesso        | ry Kit                  |

| ZENETSC0100ZACG                            |       | Etherr | net Sm   | art Cal    | ole Acce               | essory              | Kit            |                         |

| compare with carry - extended addressing 178 | Watchdog Timer 202, 204                   |

|----------------------------------------------|-------------------------------------------|

| complement 181                               | enable interrupt 180                      |

| complement carry flag 179, 180               | ER 176                                    |

| condition code 176                           | extended addressing register 176          |

| continuous conversion (ADC) 124              | external pin reset 25                     |

| CONTINUOUS mode 88                           | eZ8 CPU features 4                        |

| control register definition, UART 108        | eZ8 CPU instruction classes 178           |

| Control Registers 13, 16                     | eZ8 CPU instruction notation 176          |

| COUNTER modes 89                             | eZ8 CPU instruction set 174               |

| CP 178                                       | eZ8 CPU instruction summary 182           |

| CPC 178                                      |                                           |

| CPCX 178                                     |                                           |

| CPU and peripheral overview 4                | F                                         |

| CPU control instructions 180                 | FCTL register 141, 148, 149               |

| CPX 178                                      | features, Z8 Encore! 1                    |

| Customer Support 230                         | first opcode map 194                      |

|                                              | FLAGS 177                                 |

|                                              | flags register 177                        |

| D                                            | flash                                     |

| DA 176, 178                                  | controller 4                              |

| data memory 15                               | option bit address space 149              |

| DC characteristics 197                       | option bit configuration - reset 146      |

| debugger, on-chip 156                        | program memory address 0000H 149          |

| DEC 178                                      | program memory address 0001H 150          |

| decimal adjust 178                           | flash memory 134                          |

| decrement 178                                | arrangement 135                           |

| decrement and jump non-zero 181              | byte programming 139                      |

| decrement word 178                           | code protection 137                       |

| DECW 178                                     | configurations 134                        |

| destination operand 177                      | control register definitions 141, 148     |

| device, port availability 33                 | controller bypass 140                     |

| DI 180                                       | electrical characteristics and timing 202 |

| direct address 176                           | flash control register 141, 148, 149      |

| disable interrupts 180                       | flash option bits 138                     |

| DJNZ 181                                     | flash status register 142                 |

| dst 177                                      | flow chart 136                            |

|                                              | frequency high and low byte registers 144 |

|                                              | mass erase 139                            |

| E                                            | operation 135                             |

| EI 180                                       | operation timing 137                      |

| electrical characteristics 196               | page erase 139                            |

| ADC 203                                      | page select register 142, 144             |

| flash memory and timing 202                  | FPS register 142, 144                     |

| GPIO input data sample timing 204            | FSTAT register 142                        |

| or roughly and sample anning 201             | $\mathcal{E}$                             |