## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113sh005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 2.7V to 3.6V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 8-, 20-, and 28-pin packages

- $0^{\circ}$ C to +70°C and -40°C to +105°C for operating temperature ranges

### **Part Selection Guide**

Table 1 lists the basic features and package styles available for each device within the Z8 Encore!  $XP^{\text{®}}$  F0823 Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | I/O  | ADC<br>Inputs | Packages             |

|----------------|---------------|------------|------|---------------|----------------------|

| Z8F0823        | 8             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0813        | 8             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0423        | 4             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0413        | 4             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0223        | 2             | 512        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0213        | 2             | 512        | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0123        | 1             | 256        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0113        | 1             | 256        | 6–24 | 0             | 8-, 20-, and 28-pins |

Table 1. F0823 Series Family Part Selection Guide

9

IXYS Company

**Note:** \*Analog input alternate functions (ANA) are not available on Z8F0x13 devices.

#### **Signal Descriptions**

>

Table 3 lists the Z8 Encore! XP F0823 Series signals. To determine the signals available for the specific package styles, see the Pin Configurations section on page 7.

| Signal Mnemonic      | I/O     | Description                                                                                                                                                                                                                                                                                             |

|----------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/   | O Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]              | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0] <sup>1</sup> | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]              | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| UART Controllers     |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                 | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                 | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                 | I       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                   | Ο       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 Register. The DE signal can be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers               |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT          | 0       | Timer Output 0–1. These signals are output from the timers.                                                                                                                                                                                                                                             |

| T0OUT/T1OUT          | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM DUAL OUTPUT Mode.                                                                                                                                                                                                          |

| T0IN/T1IN            | I       | Timer Input 0–1. These signals are used as the capture, gating and counter inputs. The T0IN signal is multiplexed T0OUT signals.                                                                                                                                                                        |

| Comparator           |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN            | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| Notes:               |         |                                                                                                                                                                                                                                                                                                         |

#### **Table 3. Signal Descriptions**

1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see **the** <u>Port A–C Control Registers</u> **section on page 42**), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overrightarrow{\text{RESET}}$  pin Low. The  $\overrightarrow{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

#### **Stop Mode Recovery**

The device enters into STOP Mode when eZ8 CPU executes a STOP instruction. For more details about STOP Mode, see **the** Low-Power Modes **section on page 30**. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

iloa 39

dded in Life

For correct operation, the LED anode must be connected to V<sub>DD</sub> and the cathode must be connected to the GPIO pin. Using all Port C pins in LED Drive Mode with maximum current can result in excessive total current. For the maximum total current for the applicable package, see the Electrical Characteristics chapter on page 196.

#### Shared Reset Pin

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO Mode.

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, ensure that no external stimulus 1 drives the pin Low during any reset sequence. Because PA2 returns to its RESET alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

#### Shared Debug Pin

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer functions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see the On-Chip Debugger chapter on page 156.

#### **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see the Oscillator Control Register Definitions section on page 171), the GPIO settings are overridden and PA0 and PA1 are disabled.

#### **5V Tolerance**

All six I/O pins on the 8-pin devices are 5V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5V-tolerant, including PA[1:0], PB[5:0], and

#### Bit 7 5 4 3 2 1 6 0 AF7 AF6 AF5 AF4 AF3 AF2 AF1 AF0 Field 00H (Ports A–C); 04H (Port A of 8-pin device) RESET R/W R/W If 02H in Port A–C Address Register, accessible through the Port A–C Control Register Address

#### Table 23. Port A–C Alternate Function Subregisters (PxAF)

| Bit   | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Alternate Function enabled                                                                                                                                                      |

| AFx   | 0 = The port pin is in NORMAL Mode and the DDx bit in the Port A–C Data Direction Subregister determines the direction of the pin.                                                   |

|       | <ul> <li>1 = The alternate function selected through Alternate Function Set subregisters is enabled.</li> <li>Port pin operation is controlled by the alternate function.</li> </ul> |

Note: x indicates the specific GPIO port pin number (7–0).

#### Port A–C Output Control Subregisters

The Port A–C Output Control Subregister (Table 24) is accessed through the Port A–C Control Register by writing 03H to the Port A–C Address Register. Setting the bits in the Port A–C Output Control subregisters to 1 configures the specified port pins for opendrain operation. These subregisters affect the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7         | 6                                                                                     | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|-----------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|--|

| Field   | POC7      | POC6                                                                                  | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |  |

| RESET   | 0         | 0                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    |  |

| R/W     | R/W       | R/W                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |

| Address | If 03H ir | If 03H in Port A–C Address Register, accessible through the Port A–C Control Register |      |      |      |      |      |      |  |

Table 24. Port A–C Output Control Subregisters (PxOC)

| Bit       | Description                                                                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]     | Port Output Control                                                                                                                                                                        |

| POCx      | These bits function independently of the alternate function bit and always disable the drains if set to 1.                                                                                 |

|           | <ul><li>0 = The drains are enabled for any output mode (unless overridden by the alternate function).</li><li>1 = The drain of the associated pin is disabled (open-drain mode).</li></ul> |

| Note: x i | ndicates the specific GPIO port pin number (7–0).                                                                                                                                          |

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### ilog° Embedded in Life An TXYS Company

61

#### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 38) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit           | 7                                 | 6                                                                          | 5              | 4           | 3    | 2    | 1    | 0    |  |

|---------------|-----------------------------------|----------------------------------------------------------------------------|----------------|-------------|------|------|------|------|--|

| Field         |                                   | Rese                                                                       | erved          |             | PC3I | PC2I | PC1I | PC0I |  |

| RESET         | 0 0 0 0 0 0                       |                                                                            |                |             |      |      | 0    | 0    |  |

| R/W           | R/W                               | R/W                                                                        | R/W            | R/W         | R/W  | R/W  | R/W  | R/W  |  |

| Address       |                                   | FC6H                                                                       |                |             |      |      |      |      |  |

| Bit           | Description                       |                                                                            |                |             |      |      |      |      |  |

| [7:4]         | Reserved<br>These bits            | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000. |                |             |      |      |      |      |  |

| [3:0]<br>PCxI | 0] Port C Pin x Interrupt Request |                                                                            |                |             |      |      |      |      |  |

| Note: x in    | dicates the sp                    | ecific GPIO F                                                              | Port C pin nun | nber (3–0). |      |      |      |      |  |

#### Table 38. Interrupt Request 2 Register (IRQ2)

#### **IRQ0 Enable High and Low Bit Registers**

Table 39 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 40 and Table 41) form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register. Priority is generated by setting bits in each register.

| Table 39. IRQ0 Enable and Priority Encoding |

|---------------------------------------------|

|---------------------------------------------|

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Note: where x indicates the register bits from 0–7.

Observe the following steps to configure a timer for PWM DUAL OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode. Setting the mode also involves writing to the TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H); this write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) =  $\frac{\text{Reload Value } \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

Iloa 84

ded in Life

causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TxL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

| Bit     | 7   | 7         6         5         4         3         2         1         0 |     |     |     |     |     |     |  |

|---------|-----|-------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | TH                                                                      |     |     |     |     |     |     |  |

| RESET   | 0   | 0                                                                       | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W                                                                     | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F00H, F08H                                                              |     |     |     |     |     |     |  |

Table 51. Timer 0–1 High Byte Register (TxH)

#### Table 52. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   | TL         |     |     |     |     |     |     |     |  |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 1   |  |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F01H, F09H |     |     |     |     |     |     |     |  |

| F- 01 |       |       |     |       |

|-------|-------|-------|-----|-------|

| [7:0] | Timer | Lindh | and | LV+AC |

|       |       |       |     |       |

|       |       |       |     |       |

TH. TL These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value.

#### **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers (Table 53 and Table 54) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer reload value. In COMPARE Mode, the Timer Reload High and Low Byte registers store the 16-bit compare value.

#### Embedded in Life IXYS Company 92

#### Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

#### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information about programming of the WDT\_RES Flash Option Bit, see **the** <u>Flash Option Bits</u> chapter on page 146.

#### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see the <u>Reset Status Register</u> section on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and F0823 Series are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. For more information about Stop Mode Recovery, see **the** <u>Reset and Stop Mode Recovery</u> chapter on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

#### WDT Reset in NORMAL Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Watchdog Timer Control Register is set to 1. For more information about System Reset, see **the** <u>Reset and Stop</u> <u>Mode Recovery</u> chapter on page 21.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following WDT time-out in STOP Mode. For more information, see **the** <u>Reset and Stop Mode Recovery</u> chapter on page 21.

#### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer Control Register (WDTCTL) address unlocks the three Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. The following sequence is required to unlock the Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

#### Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register (WDTCTL): see page 94

Watchdog Timer Reload Upper Byte Register (WDTU): see page 95

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Embedded in Life

#### **UART Transmit Data Register**

Data bytes written to the UART Transmit Data Register (Table 64) are shifted out on the TXDx pin. The Write-only UART Transmit Data Register shares a Register File address with the read-only UART Receive Data Register.

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------|---|---|---|---|---|---|---|--|--|--|

| Field   | TXD  |   |   |   |   |   |   |   |  |  |  |

| RESET   | Х    | Х | Х | Х | Х | Х | Х | Х |  |  |  |

| R/W     | W    | W | W | W | W | W | W | W |  |  |  |

| Address | F40H |   |   |   |   |   |   |   |  |  |  |

#### Table 64. UART Transmit Data Register (U0TXD)

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

#### **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data Register (Table 65). The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------|---|---|---|---|---|---|---|--|--|--|

| Field   | RXD  |   |   |   |   |   |   |   |  |  |  |

| RESET   | Х    | Х | Х | Х | Х | Х | Х | Х |  |  |  |

| R/W     | R    | R | R | R | R | R | R | R |  |  |  |

| Address | F40H |   |   |   |   |   |   |   |  |  |  |

| Bit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

nbedded in Life

124

- CEN resets to 0 to indicate the conversion is complete

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

#### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS Mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Observe the following steps for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

#### ilog Embedded in Life An LIXYS Company 128

| Bit            | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3:0]<br>ANAIN | <ul> <li>Analog Input Select</li> <li>These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore! XP F0823 Series. For information about the port pins available with each package style, see the Pin Description section on page 7. Do not enable unavail able analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.</li> <li>For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.</li> </ul> |

|                | Single-Ended: $0000 = ANA0.$ $0001 = ANA1.$ $0010 = ANA2.$ $0011 = ANA3.$ $0100 = ANA4.$ $0101 = ANA5.$ $0110 = ANA6.$ $0111 = ANA7.$ $1000 = Reserved.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | 1001 = Reserved.<br>1010 = Reserved.<br>1011 = Reserved.<br>1100 = Reserved.<br>1101 = Reserved.<br>1110 = Reserved.<br>1111 = Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### ilog<sup>\*</sup> Embedded in Life An∎IXYS Company 129

#### ADC Control/Status Register 1

The second ADC Control Register contains the voltage reference level selection bit.

#### Table 75. ADC Control/Status Register 1 (ADCCTL1)

| Bit            | 7                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5           | 4            | 3           | 2      | 1   | 0   |  |  |  |

|----------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-------------|--------|-----|-----|--|--|--|

| Field          | REFSELH                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reserved    |              |             |        |     |     |  |  |  |

| RESET          | 1                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 0 0 0 0   |              |             |        |     |     |  |  |  |

| R/W            | R/W                                                        | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W         | R/W          | R/W         | R/W    | R/W | R/W |  |  |  |

| Address        | F71H                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |              |             |        |     |     |  |  |  |

| Bit            | Description                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |              |             |        |     |     |  |  |  |

| [7]<br>REFSELH | In conjun<br>the level<br>REFSEL<br>00 = Inte<br>01 = Inte | Voltage Reference Level Select High Bit<br>In conjunction with the Low bit (REFSELL) in ADC Control Register 0, this bit determines<br>the level of the internal voltage reference; the following details the effects of {REFSELH,<br>REFSELL}; this reference is independent of the Comparator reference.<br>00 = Internal Reference Disabled, reference comes from external pin.<br>01 = Internal Reference set to 1.0V.<br>10 = Internal Reference set to 2.0V (default). |             |              |             |        |     |     |  |  |  |

| [6:0]          | Reserve<br>These bit                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ved and mus | st be progra | nmed to 000 | 00000. |     |     |  |  |  |

nbedded in Life

134

### Flash Memory

The products in Z8 Encore! XP F0823 Series features either 8KB (8192), 4KB (4096), 2KB (2048) or 1KB (1024) of nonvolatile Flash memory with read/write/erase capability. Flash Memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash Memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program/data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F0823 Series, these sectors are either 1024 bytes (in the 8KB devices) or 512 bytes in size (all other memory sizes); each sector maps to a page. Page and sector sizes are not generally equal.

The first two bytes of the Flash program memory are used as Flash Option bits. For more information about their operation, see the <u>Flash Option Bits</u> chapter on page 146.

Table 79 describes the Flash memory configuration for each device in the Z8 Encore! XP F0823 Series. Figure 20 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F08x3     | 8 (8192)                 | 16          | 0000H–1FFFH                    | 1024                         |

| Z8F04x3     | 4 (4096)                 | 8           | 0000H–0FFFH                    | 512                          |

| Z8F02x3     | 2 (2048)                 | 4           | 0000H-07FFH                    | 512                          |

| Z8F01x3     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

#### Table 79. Z8 Encore! XP F0823 Series Flash Memory Configurations

ilog Ibedded in Life

156

### **On-Chip Debugger**

Z8 Encore! XP F0823 Series devices contain an integrated On-Chip Debugger (OCD) which provides advanced debugging features that include:

- Single pin interface

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

- Debug pin sharing with general-purpose input-output function to maximize the pins available

#### Architecture

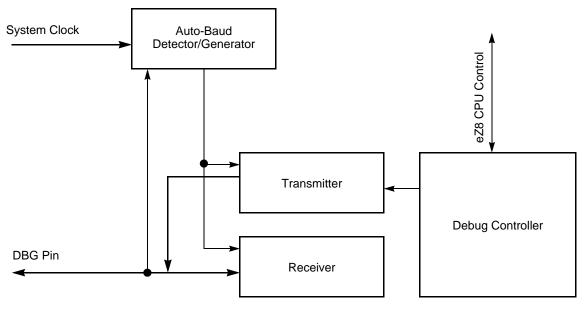

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator, and debug controller. Figure 22 displays the architecture of the OCD.

Figure 22. On-Chip Debugger Block Diagram

ilog° Embedded in Life An∎IXYS Company

188

| Assembly  |                                                |     | lress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch  | Instr. |

|-----------|------------------------------------------------|-----|--------------|-------------|---|---|-----|-----|---|---|--------|--------|

| Mnemonic  | Symbolic Operation                             | dst | src          | (Hex)       | С | Ζ | S   | ۷   | D | Н | Cycles |        |

| POPX dst  | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1 | ER  |              | D8          | - | - | -   | -   | _ | _ | 3      | 2      |

| PUSH src  | $SP \leftarrow SP - 1$                         | R   |              | 70          | - | - | _   | _   | _ | - | 2      | 2      |

|           | $@SP \leftarrow src$                           | IR  |              | 71          | • |   |     |     |   |   | 2      | 3      |

|           | -                                              | IM  |              | IF70        |   |   |     |     |   |   | 3      | 2      |

| PUSHX src | $SP \leftarrow SP - 1$<br>@SP ← src            | ER  |              | C8          | _ | _ | _   | _   | _ | - | 3      | 2      |

| RCF       | C ← 0                                          |     |              | CF          | 0 | _ | -   | _   | _ | - | 1      | 2      |

| RET       | $PC \leftarrow @SP \\ SP \leftarrow SP + 2$    |     |              | AF          | _ | - | -   | _   | _ | _ | 1      | 4      |

| RL dst    |                                                | R   |              | 90          | * | * | *   | *   | _ | - | 2      | 2      |

|           | C                                              | IR  |              | 91          | • |   |     |     |   |   | 2      | 3      |

| RLC dst   |                                                | R   |              | 10          | * | * | *   | *   | _ | _ | 2      | 2      |

|           | C ← D7 D6 D5 D4 D3 D2 D1 D0 ← dst              | IR  |              | 11          |   |   |     |     |   |   | 2      | 3      |

| RR dst    |                                                | R   |              | E0          | * | * | *   | *   | - | _ | 2      | 2      |

|           | ► <u>D7D6D5D4D3D2D1D0</u> C<br>dst             | IR  |              | E1          |   |   |     |     |   |   | 2      | 3      |

| RRC dst   |                                                | R   |              | C0          | * | * | *   | *   | _ | _ | 2      | 2      |

|           | ► D7 D6 D5 D4 D3 D2 D1 D0 - C dst              | IR  |              | C1          | • |   |     |     |   |   | 2      | 3      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

|                   |                                       |         | -40°C to -<br>otherwise | ⊦105°C<br>specified) |       |                                                                               |  |  |

|-------------------|---------------------------------------|---------|-------------------------|----------------------|-------|-------------------------------------------------------------------------------|--|--|

| Symbol            | Parameter                             | Minimum | Typical                 | Maximum              | Units | Conditions                                                                    |  |  |

| I <sub>LED</sub>  | Controlled Current                    | 1.8     | 3                       | 4.5                  | mA    | {AFS2,AFS1} = {0,0}.                                                          |  |  |

|                   | Drive                                 | 2.8     | 7                       | 10.5                 | mA    | {AFS2,AFS1} = {0,1}.                                                          |  |  |

|                   |                                       | 7.8     | 13                      | 19.5                 | mA    | {AFS2,AFS1} = {1,0}.                                                          |  |  |

|                   |                                       | 12      | 20                      | 30                   | mA    | ${AFS2,AFS1} = {1,1}.$                                                        |  |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance          | -       | 8.0 <sup>2</sup>        | -                    | pF    |                                                                               |  |  |

| C <sub>XIN</sub>  | X <sub>IN</sub> Pad Capaci-<br>tance  | -       | 8.0 <sup>2</sup>        | -                    | pF    |                                                                               |  |  |

| C <sub>XOUT</sub> | X <sub>OUT</sub> Pad Capaci-<br>tance | -       | 9.5 <sup>2</sup>        | -                    | pF    |                                                                               |  |  |

| I <sub>PU</sub>   | Weak Pull-up Cur-<br>rent             | 30      | 100                     | 350                  | μA    | V <sub>DD</sub> = 3.0V–3.6V.                                                  |  |  |

| V <sub>RAM</sub>  | RAM Data Reten-<br>tion Voltage       | TBD     |                         |                      | V     | Voltage at which RAM retains static values; no reading or writing is allowed. |  |  |

#### Table 121. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

208

#### UART Timing

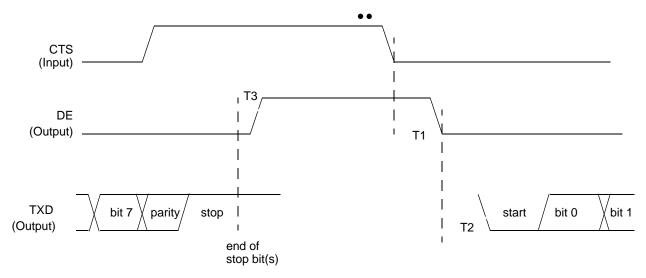

Figure 32 and Table 133 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

Figure 32. UART Timing With CTS

|                |                                                    | Delay (ns)                 |                                            |  |  |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|--|--|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |  |  |  |

| UART           |                                                    |                            |                                            |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | Ŧ                          | = 5                                        |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ÷                          | - 5                                        |  |  |  |

| Table | 133  | UART | Timing  | With   | CTS |

|-------|------|------|---------|--------|-----|

| Table | 155. |      | rinning | WWILII | 010 |

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

228

ONE-SHOT mode 70, 88 operating mode 70 PWM mode 75, 76, 89 reading the timer count values 83 reload high and low byte registers 84 timer control register definitions 83 timer output signal operation 83 timers 0-3 control registers 86, 87 high and low byte registers 83, 86 TM 179 **TMX 179** tools, hardware and software 220 transmit IrDA data 118 transmitting UART data-polled method 99 transmitting UART dat-interrupt-driven method 100 **TRAP 181**

#### U

UART 4 architecture 97 baud rate generator 108 control register definitions 108 controller signals 9 interrupts 105 MULTIPROCESSOR mode 103 receiving data using interrupt-driven method 102 receiving data using the polled method 101 transmitting data using the interrupt-driven method 100 transmitting data using the polled method 99 x baud rate high and low registers 115 x control 0 and control 1 registers 112 x status 0 and status 1 registers 110, 111 UxBRH register 115 **UxBRL** register 115 UxCTL0 register 112, 115 UxCTL1 register 113 UxRXD register 109 UxSTAT0 register 110

UxSTAT1 register 111 UxTXD register 109

#### V

vector 177 Voltage Brownout reset (VBR) 24

#### W

Watchdog Timer approximate time-out delay 91 CNTL 24 control register 94, 171 electrical characteristics and timing 202, 204 interrupt in normal operation 92 interrupt in STOP mode 92 refresh 92, 180 reload unlock sequence 93 reload upper, high and low registers 94 reset 25 reset in normal operation 93 reset in STOP mode 93 time-out response 92 Watchdog Timer Control Register (WDTCTL) 94 WDTCTL register 94, 133, 172 WDTH register 95 WDTL register 95 WDTU register 95 working register 176 working register pair 177

#### Χ

X 177 XOR 181 XORX 181

#### Ζ

Z8 Encore! block diagram 3 features 1