Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0123ph005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| OCD Status Register                                                                                                                                                                             | 168                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Oscillator Control                                                                                                                                                                              | 169<br>169<br>170                             |

| Internal Precision Oscillator Operation                                                                                                                                                         | 173                                           |

| eZ8 CPU Instruction Set<br>Assembly Language Programming Introduction<br>Assembly Language Syntax<br>eZ8 CPU Instruction Notation<br>eZ8 CPU Instruction Classes<br>eZ8 CPU Instruction Summary | 174<br>175<br>176<br>178                      |

| Opcode Maps                                                                                                                                                                                     | 192                                           |

| Electrical Characteristics                                                                                                                                                                      | 196<br>197<br>200<br>201<br>204<br>206<br>207 |

| Packaging                                                                                                                                                                                       | 210                                           |

| Ordering Information                                                                                                                                                                            |                                               |

| Index                                                                                                                                                                                           | 221                                           |

| Customer Support                                                                                                                                                                                | 230                                           |

# List of Figures

| Figure 1.  | Z8 Encore! XP F0823 Series Block Diagram 3                                           |

|------------|--------------------------------------------------------------------------------------|

| Figure 2.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package        |

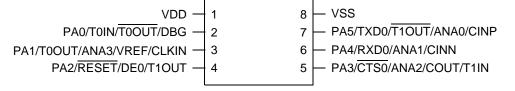

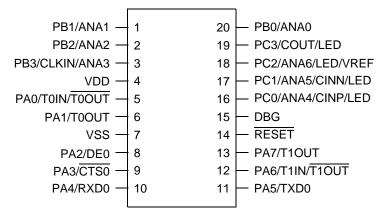

| Figure 3.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package             |

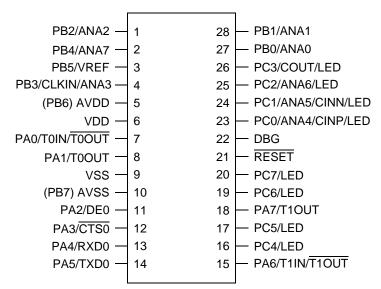

| Figure 4.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package             |

| Figure 5.  | Power-On Reset Operation                                                             |

| Figure 6.  | Voltage Brown-Out Reset Operation                                                    |

| Figure 7.  | GPIO Port Pin Block Diagram                                                          |

| Figure 8.  | Interrupt Controller Block Diagram                                                   |

| Figure 9.  | Timer Block Diagram                                                                  |

| Figure 10. | UART Block Diagram                                                                   |

| Figure 11. | UART Asynchronous Data Format without Parity                                         |

| Figure 12. | UART Asynchronous Data Format with Parity                                            |

| Figure 13. | UART Asynchronous MULTIPROCESSOR Mode Data Format 103                                |

| Figure 14. | UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity) 105              |

| Figure 15. | UART Receiver Interrupt Service Routine Flow                                         |

| Figure 16. | Infrared Data Communication System Block Diagram 117                                 |

| Figure 17. | Infrared Data Transmission                                                           |

| Figure 18. | IrDA Data Reception                                                                  |

| Figure 19. | Analog-to-Digital Converter Block Diagram 122                                        |

| Figure 20. | Flash Memory Arrangement 135                                                         |

| Figure 21. | Flash Controller Operation Flowchart                                                 |

| Figure 22. | On-Chip Debugger Block Diagram 156                                                   |

| Figure 23. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface,<br># 1 of 2 157 |

| Figure 24. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface,<br># 2 of 2     |

| Figure 25. | OCD Data Format                                                                      |

| Figure 26. | Opcode Map Cell Description 192                                                      |

| Figure 27. | First Opcode Map                                                                     |

| Figure 28. | Second Opcode Map after 1FH 195                                                      |

| Figure 29. | Port Input Sample Timing 205                                                         |

| Z8 Encore! XP <sup>®</sup> F0823 Series<br>Product Specification |  |

|------------------------------------------------------------------|--|

| Embedded in Llfe                                                 |  |

3

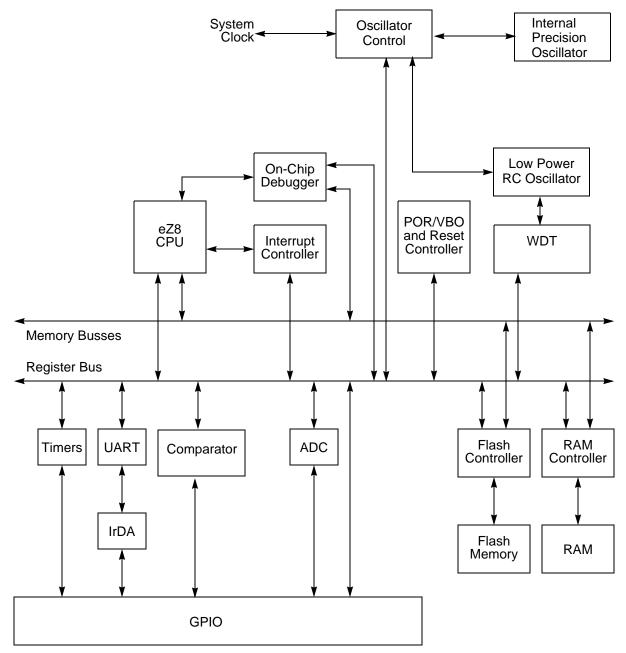

# **Block Diagram**

Figure 1 displays a block diagram of the F0823 Series architecture.

Figure 1. Z8 Encore! XP F0823 Series Block Diagram

8

Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

#### ILOG<sup>°</sup> Embedded in Life

# HALT Mode

Executing the eZ8 CPU's HALT instruction places the device into HALT Mode, which powers down the CPU but leaves all other peripherals active. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

# **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F0823 Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

The following sections describe the power control registers.

#### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

#### ilog Embedded in Life An IXYS Company 45

#### Port A–C High Drive Enable Subregisters

The Port A–C High Drive Enable Subregister (Table 25) is accessed through the Port A–C Control Register by writing 04H to the Port A–C Address Register. Setting the bits in the Port A–C High Drive Enable subregisters to 1 configures the specified port pins for high-current output drive operation. The Port A–C High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

| Table 25. Port A–C High Drive Enable Subregiste | ers (PHDEx) |

|-------------------------------------------------|-------------|

|-------------------------------------------------|-------------|

| Bit     | 7                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Field   | PHDE7                                                                                 | PHDE6 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | If 04H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |       |

#### Bit Description

[7:0] **Port High Drive Enabled.**

PHDEx 0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

Note: x indicates the specific GPIO port pin number (7–0).

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

Iloa 84

ded in Life

causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TxL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|--|

| Field   | ТН  |            |     |     |     |     |     |     |  |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F00H, F08H |     |     |     |     |     |     |  |

Table 51. Timer 0–1 High Byte Register (TxH)

#### Table 52. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   |            |     |     | Т   | Ľ   |     |     |     |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F01H, F09H |     |     |     |     |     |     |     |

| <b>F----1</b> |       |       |     |       |

|---------------|-------|-------|-----|-------|

| [7:0]         | Timer | Lindh | and | LV+AC |

|               |       |       |     |       |

|               |       |       |     |       |

TH. TL These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value.

## **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers (Table 53 and Table 54) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer reload value. In COMPARE Mode, the Timer Reload High and Low Byte registers store the 16-bit compare value.

# **Analog-to-Digital Converter**

The Analog-to-Digital Converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 10-bit resolution

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Bandgap generated internal voltage reference generator with two selectable levels

- Factory offset and gain calibration

# Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

nbedded in Life

124

- CEN resets to 0 to indicate the conversion is complete

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

## **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS Mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Observe the following steps for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

#### ilog Embedded in Life An LIXYS Company 128

| Bit            | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3:0]<br>ANAIN | <ul> <li>Analog Input Select</li> <li>These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore! XP F0823 Series. For information about the port pins available with each package style, see the Pin Description section on page 7. Do not enable unavail able analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.</li> <li>For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.</li> </ul> |

|                | Single-Ended: $0000 = ANA0.$ $0001 = ANA1.$ $0010 = ANA2.$ $0011 = ANA3.$ $0100 = ANA4.$ $0101 = ANA5.$ $0110 = ANA6.$ $0111 = ANA7.$ $1000 = Reserved.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | 1000 = Reserved.<br>1001 = Reserved.<br>1010 = Reserved.<br>1011 = Reserved.<br>1100 = Reserved.<br>1101 = Reserved.<br>1110 = Reserved.<br>1111 = Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### ILOG Embedded in Life An IXYS Company 140

## Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

## **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

# **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the Zilog application note titled, <u>Third-Party Flash Programming Support for Z8 Encore! MCUs (AN0117)</u>, available for download at <u>www.zilog.com</u>.

# Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

ilog<sup>®</sup>

143

# **Flash Status Register**

The Flash Status Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

| Bit     | 7          | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|---------|------------|-------|-------|---|---|---|---|---|

| Field   | Rese       | erved | FSTAT |   |   |   |   |   |

| RESET   | 0          | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

| R/W     | R          | R     | R     | R | R | R | R | R |

| Address |            | FF8H  |       |   |   |   |   |   |

| Bit     | Descriptio | n     |       |   |   |   |   |   |

| Table 82 | . Flash | Status | Register | (FSTAT) |

|----------|---------|--------|----------|---------|

|----------|---------|--------|----------|---------|

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 0 when read.                                                                                                                                                                                                                                                                                           |

| [5:0]<br>FSTAT | Flash Controller Status000000 = Flash Controller locked.000001 = First unlock command received (73H written).000010 = Second unlock command received (8CH written).000011 = Flash Controller unlocked.000100 = Sector protect register selected.001xxx = Program operation in progress.010xxx = Page erase operation in progress.100xxx = Mass erase operation in progress. |

## Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

## **OCD Unlock Sequence (8-Pin Devices Only)**

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5 ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

\begin{array}{l} \text{DBG} \leftarrow 80\text{H} \text{ (autobaud)} \\ \\ \text{DBG} \leftarrow \text{EBH} \\ \\ \text{DBG} \leftarrow 5\text{AH} \\ \\ \\ \text{DBG} \leftarrow 70\text{H} \\ \\ \\ \\ \text{DBG} \leftarrow \text{CDH} \text{ (32-bit unlock key)} \end{array}

```

Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20- or 28-pin device. To enter DEBUG Mode, reautobaud and write 80H to the OCD Control Register (see the <u>On-Chip Debugger Commands</u> section on page 162).

## **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

## **Runtime Counter**

The OCD contains a 16-bit Runtime Counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

ILOG<sup>®</sup> Ibedded in Life IXYS Company 164

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

**Read Register (09H).** The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

Write Program Memory (0AH). The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

ILO O hbedded in Life IXYS Company

166

**Stuff Instruction (11H).** The Stuff command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0–4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

**Execute Instruction (12H).** The Execute command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

## **OCD Control Register**

The OCD Control Register controls the state of the OCD. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It also resets Z8 Encore! XP F0823 Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

nbedded in Life

171

conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control Register.

#### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

ilog<sup>®</sup> Embedded in Life 191 An∎IXYS Company

| Assembly      |                             |     | ress<br>ode | _ Opcode(s)<br>(Hex) | Flags |   |   |   |   |   | Fetch  | Instr. |

|---------------|-----------------------------|-----|-------------|----------------------|-------|---|---|---|---|---|--------|--------|

| Mnemonic      | Symbolic Operation          | dst | src         |                      | С     | Ζ | S | ۷ | D | Н | Cycles | Cycles |

| XOR dst, src  | $dst \gets dst \ XOR \ src$ | r   | r           | B2                   | _     | * | * | 0 | _ | _ | 2      | 3      |

|               |                             | r   | lr          | B3                   |       |   |   |   |   |   | 2      | 4      |

|               |                             | R   | R           | B4                   |       |   |   |   |   |   | 3      | 3      |

|               |                             | R   | IR          | B5                   |       |   |   |   |   |   | 3      | 4      |

|               |                             | R   | IM          | B6                   |       |   |   |   |   |   | 3      | 3      |

|               |                             | IR  | IM          | B7                   |       |   |   |   |   |   | 3      | 4      |

| XORX dst, src | $dst \gets dst \ XOR \ src$ | ER  | ER          | B8                   | _     | * | * | 0 | _ | _ | 4      | 3      |

|               |                             | ER  | IM          | B9                   |       |   |   |   |   |   | 4      | 3      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

PS024315-1011

> ilog Embedded in Life An IXYS Company 214

|                                      |               |           |            |                        |                     | -              |                     |  |  |  |

|--------------------------------------|---------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|--|--|

| Part Number                          | Flash<br>RAM  | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |  |

| Z8 Encore! XP F0823                  | Series with 4 | KB Fla    | ash        |                        |                     |                |                     |  |  |  |

| Standard Temperature: 0°C to 70°C    |               |           |            |                        |                     |                |                     |  |  |  |

| Z8F0413PB005SG                       | 4 KB 1 KB     | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0413QB005SG                       | 4 KB 1 KB     | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0413SB005SG                       | 4 KB 1 KB     | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0413SH005SG                       | 4 KB 1 KB     | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0413HH005SG                       | 4 KB 1 KB     | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0413PH005SG                       | 4 KB 1 KB     | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0413SJ005SG                       | 4 KB 1 KB     | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0413HJ005SG                       | 4 KB 1 KB     | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0413PJ005SG                       | 4 KB 1 KB     | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |  |

| Extended Temperature: –40°C to 105°C |               |           |            |                        |                     |                |                     |  |  |  |

| Z8F0413PB005EG                       | 4 KB 1 KB     | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0413QB005EG                       | 4 KB 1 KB     | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0413SB005EG                       | 4 KB 1 KB     | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0413SH005EG                       | 4 KB 1 KB     | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0413HH005EG                       | 4 KB 1 KB     | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0413PH005EG                       | 4 KB 1 KB     | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0413SJ005EG                       | 4 KB 1 KB     | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0413HJ005EG                       | 4 KB 1 KB     | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0413PJ005EG                       | 4 KB 1 KB     | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |  |

### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

> ilog Embedded in Life An IXYS Company 216

| Part Number                       | Flash    | RAM      | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |

|-----------------------------------|----------|----------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|

| Z8 Encore! XP F0823               | Series   | with 2 k | KB Fla    | ash        |                        |                     |                |                     |  |

| Standard Temperature: 0°C to 70°C |          |          |           |            |                        |                     |                |                     |  |

| Z8F0213PB005SG                    | 2 KB     | 512 B    | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |

| Z8F0213QB005SG                    | 2 KB     | 512 B    | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |

| Z8F0213SB005SG                    | 2 KB     | 512 B    | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |

| Z8F0213SH005SG                    | 2 KB     | 512 B    | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |

| Z8F0213HH005SG                    | 2 KB     | 512 B    | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |

| Z8F0213PH005SG                    | 2 KB     | 512 B    | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |

| Z8F0213SJ005SG                    | 2 KB     | 512 B    | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |

| Z8F0213HJ005SG                    | 2 KB     | 512 B    | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |

| Z8F0213PJ005SG                    | 2 KB     | 512 B    | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |

| Extended Temperatu                | re: -40° | C to 10  | 5°C       |            |                        |                     |                |                     |  |

| Z8F0213PB005EG                    | 2 KB     | 512 B    | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |

| Z8F0213QB005EG                    | 2 KB     | 512 B    | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |

| Z8F0213SB005EG                    | 2 KB     | 512 B    | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |

| Z8F0213SH005EG                    | 2 KB     | 512 B    | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |

| Z8F0213HH005EG                    | 2 KB     | 512 B    | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |

| Z8F0213PH005EG                    | 2 KB     | 512 B    | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |

| Z8F0213SJ005EG                    | 2 KB     | 512 B    | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |

| Z8F0213HJ005EG                    |          | 512 B    | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |

| Z8F0213PJ005EG                    | 2 KB     | 512 B    | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |

### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)