Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K × 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0123sb005eg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Embedded in Life An TXYS Company

## **Table of Contents**

| Revision History                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures x                                                                                                                                                                                                                                                                                                   |

| List of Tables xii                                                                                                                                                                                                                                                                                                  |

| Overview1Features1Part Selection Guide2Block Diagram3CPU and Peripheral Overview4General-Purpose I/O4Flash Controller4Internal Precision Oscillator510-Bit Analog-to-Digital Converter5Analog Comparator5Universal Asynchronous Receiver/Transmitter5Timers5Interrupt Controller5Reset Controller5On-Chip Debugger6 |

| Pin Description7Available Packages7Pin Configurations7Signal Descriptions9Pin Characteristics11Address Space13Register File13Program Memory13                                                                                                                                                                       |

| Data Memory15Flash Information Area15                                                                                                                                                                                                                                                                               |

| Register Map                                                                                                                                                                                                                                                                                                        |

| Reset and Stop Mode Recovery21Reset Types21Reset Sources23Power-On Reset23Voltage Brown-Out Reset24Watchdog Timer Reset25                                                                                                                                                                                           |

## **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit central processing unit (CPU), meets the continuing demand for faster and code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access of up to 4 KB

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>) available for download at <u>www.zilog.com</u>.

### **General-Purpose I/O**

F0823 Series features 6 to 24 port pins (Ports A–C) for general-purpose I/O (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable. 5 V-tolerant input pins are available on all I/Os on 8-pin devices, most I/Os on other package types.

## **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports protection against accidental program and erasure, as well as factory serialization and read protection.

returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the Z8 Encore! XP F0823 Series products.

| Program Memory Address (Hex) | Function                 |

|------------------------------|--------------------------|

| Z8F0823 and Z8F0813 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0423 and Z8F0413 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0223 and Z8F0213 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-07FF                    | Program Memory           |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps

Note: \*See the <u>Trap and Interrupt Vectors in Order of Priority section on page 55</u> for a list of the interrupt vectors and traps.

Embedded in Life An IXYS Company

ilog<sup>®</sup> Embedded in Life

ilog Embedded in Life An IXYS Company 17

| Address (Hex)    | Register Description      | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------|----------|-------------|-------------|

| Timer 1 (cont'd) |                           |          |             |             |

| F0A              | Timer 1 Reload High Byte  | T1RH     | FF          | <u>85</u>   |

| F0B              | Timer 1 Reload Low Byte   | T1RL     | FF          | <u>85</u>   |

| F0C              | Timer 1 PWM High Byte     | T1PWMH   | 00          | <u>86</u>   |

| F0D              | Timer 1 PWM Low Byte      | T1PWML   | 00          | <u>86</u>   |

| F0E              | Timer 1 Control 0         | T1CTL0   | 00          | <u>87</u>   |

| F0F              | Timer 1 Control 1         | T1CTL1   | 00          | <u>84</u>   |

| F10–F3F          | Reserved                  | —        | XX          |             |

| UART             |                           |          |             |             |

| F40              | UART0 Transmit Data       | U0TXD    | XX          | <u>109</u>  |

|                  | UART0 Receive Data        | U0RXD    | XX          | <u>109</u>  |

| F41              | UART0 Status 0            | U0STAT0  | 0000011Xb   | <u>110</u>  |

| F42              | UART0 Control 0           | U0CTL0   | 00          | <u>112</u>  |

| F43              | UART0 Control 1           | U0CTL1   | 00          | <u>112</u>  |

| F44              | UART0 Status 1            | U0STAT1  | 00          | <u>111</u>  |

| F45              | UART0 Address Compare     | U0ADDR   | 00          | <u>115</u>  |

| F46              | UART0 Baud Rate High Byte | U0BRH    | FF          | <u>115</u>  |

| F47              | UART0 Baud Rate Low Byte  | U0BRL    | FF          | <u>115</u>  |

| F48–F6F          | Reserved                  | —        | XX          |             |

| Analog-to-Digita | al Converter (ADC)        |          |             |             |

| F70              | ADC Control 0             | ADCCTL0  | 00          | <u>127</u>  |

| F71              | ADC Control 1             | ADCCTL1  | 80          | <u>127</u>  |

| F72              | ADC Data High Byte        | ADCD_H   | XX          | <u>130</u>  |

| F73              | ADC Data Low Bits         | ADCD_L   | XX          | <u>130</u>  |

| F74–F7F          | Reserved                  | —        | XX          |             |

| Low Power Con    | trol                      |          |             |             |

| F80              | Power Control 0           | PWRCTL0  | 80          | <u>32</u>   |

| F81              | Reserved                  | _        | XX          |             |

| LED Controller   |                           |          |             |             |

| F82              | LED Drive Enable          | LEDEN    | 00          | <u>51</u>   |

| F83              | LED Drive Level High Byte | LEDLVLH  | 00          | <u>52</u>   |

| Note: XX=Undefi  |                           |          |             |             |

#### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

#### ilog Embedded in Life An ∎IXYS Company 21

## **Reset and Stop Mode Recovery**

The Reset Controller within the Z8 Encore! XP F0823 Series controls Reset and Stop Mode Recovery operation and provides indication of low supply voltage conditions. In typical operation, the following events cause a Reset:

- Power-On Reset (POR)

- Voltage Brown-Out (VBO)

- Watchdog Timer time-out (when configured by the WDT\_RES Flash Option Bit to initiate a reset)

- External RESET pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the device is in STOP Mode, a Stop Mode Recovery is initiated by either of the following:

- Watchdog Timer time-out

- GPIO port input pin transition on an enabled Stop Mode Recovery source

The VBO circuitry on the device performs the following function:

• Generates the VBO reset when the supply voltage drops below a minimum safe level

## **Reset Types**

F0823 Series MCUs provide several different types of Reset operations. Stop Mode Recovery is considered a form of Reset. Table 9 lists the types of Reset and their operating characteristics. The duration of a System Reset is longer if the external crystal oscillator is enabled by the Flash option bits; this configuration allows additional time for oscillator startup.

|                       | Reset Characteristics and Latency                |         |                                                               |  |  |  |

|-----------------------|--------------------------------------------------|---------|---------------------------------------------------------------|--|--|--|

| Reset Type            | Control Registers                                | eZ8 CPU | Reset Latency (Delay)                                         |  |  |  |

| System Reset          | Reset (as applicable)                            | Reset   | 66 Internal Precision Oscillator Cycles                       |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except WDT_CTL and OSC_CTL registers | Reset   | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |

Table 9. Reset and Stop Mode Recovery Characteristics and Latency

bedded in Life

40

PC[2:0]. All other signal pins are 5V-tolerant, and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

## **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see the <u>Oscillator Control Register Definitions</u> section on page 171) such that the external oscillator is selected as the system clock. For 8-pin devices, use PA1 instead of PB3.

## **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see the <u>Interrupt Controller</u> chapter on page 54.

## **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data, and output data. Table 18 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register<br>Mnemonic    | Port Register Name                                           |

|------------------------------|--------------------------------------------------------------|

| P <i>x</i> ADDR              | Port A–C Address Register (Selects subregisters).            |

| P <i>x</i> CTL               | Port A-C Control Register (Provides access to subregisters). |

| PxIN                         | Port A–C Input Data Register.                                |

| P <i>x</i> OUT               | Port A–C Output Data Register.                               |

| Port Subregister<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                | Data Direction.                                              |

| P <i>x</i> AF                | Alternate Function.                                          |

| P <i>x</i> OC                | Output Control (Open-Drain).                                 |

|                              |                                                              |

**Table 18. GPIO Port Registers and Subregisters**

#### ilog Embedded in Life An∎IXYSCompany 42

#### Table 20. PADDR[7:0] Subregister Functions

| PADDR[7:0] | Port Control Subregister Accessible Using the Port A–C Control Registers |

|------------|--------------------------------------------------------------------------|

| 05H        | Stop Mode Recovery Source Enable.                                        |

| 06H        | Pull-up Enable.                                                          |

| 07H        | Alternate Function Set 1.                                                |

| 08H        | Alternate Function Set 2.                                                |

| 09H–FFH    | No function.                                                             |

## **Port A–C Control Registers**

The Port A–C Control registers set the GPIO port operation. The value in the corresponding Port A–C Address Register determines which subregister is read from or written to by a Port A–C Control Register transaction; see Table 21.

| Bit           | 7          | 6                                                                                                          | 5   | 4        | 3        | 2   | 1   | 0   |  |  |  |

|---------------|------------|------------------------------------------------------------------------------------------------------------|-----|----------|----------|-----|-----|-----|--|--|--|

| Field         |            | PCTL                                                                                                       |     |          |          |     |     |     |  |  |  |

| RESET         |            | 00H                                                                                                        |     |          |          |     |     |     |  |  |  |

| R/W           | R/W        | R/W                                                                                                        | R/W | R/W      | R/W      | R/W | R/W | R/W |  |  |  |

| Address       |            | L                                                                                                          | L   | FD1H, FD | 5H, FD9H |     |     |     |  |  |  |

| Bit           | Descriptio | n                                                                                                          |     |          |          |     |     |     |  |  |  |

| [7:0]<br>PCTL |            | Port Control<br>The Port Control Register provides access to all subregisters that configure the GPIO Port |     |          |          |     |     |     |  |  |  |

Table 21. Port A–C Control Registers (PxCTL)

#### Port A–C Alternate Function Set 1 Subregisters

The Port A–C Alternate Function Set1 Subregister (Table 28) is accessed through the Port A–C Control Register by writing 07H to the Port A–C Address Register. The Alternate Function Set 1 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in "GPIO Alternate Functions" on page 34.

**Note:** Alternate function selection on port pins must also be enabled as described in the <u>Port A</u>–<u>C Alternate Function Subregisters</u> section on page 43.

| Bit     | 7         | 6                                                                  | 5           | 4             | 3            | 2            | 1            | 0        |  |

|---------|-----------|--------------------------------------------------------------------|-------------|---------------|--------------|--------------|--------------|----------|--|

| Field   | PAFS17    | PAFS16                                                             | PAFS15      | PAFS14        | PAFS13       | PAFS12       | PAFS11       | PAFS10   |  |

| RESET   |           | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |             |               |              |              |              |          |  |

| R/W     | R/W       | R/W                                                                | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |  |

| Address | If 07H ir | n Port A–C A                                                       | Address Reg | jister, acces | sible throug | h the Port A | -C Control F | Register |  |

#### Table 28. Port A–C Alternate Function Set 1 Subregisters (PAFS1x)

#### Bit Description

#### [7:0] Port Alternate Function Set to 1

PAFS1x 0 = Port Alternate Function selected as defined in Table 15 (see the <u>GPIO Alternate Functions</u> section on page 34).

1 = Port Alternate Function selected as defined in Table 15 (see the <u>GPIO Alternate Functions</u> section on page 34).

Note: x indicates the specific GPIO port pin number (7–0).

# Embedded in Life

## **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) register (Table 49) determines the source of the PADxS interrupts. The Shared Interrupt Select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit     | 7        | 6     | 5           | 4   | 3   | 2   | 1   | 0   |

|---------|----------|-------|-------------|-----|-----|-----|-----|-----|

| Field   | Reserved | PA6CS | Reserved    |     |     |     |     |     |

| RESET   | 0        | 0     | 0 0 0 0 0 0 |     |     |     |     |     |

| R/W     | R/W      | R/W   | R/W         | R/W | R/W | R/W | R/W | R/W |

| Address |          | FCEH  |             |     |     |     |     |     |

#### Table 49. Shared Interrupt Select Register (IRQSS)

| Bit          | Description                                                                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]          | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                   |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The comparator is used as an interrupt for PA6CS interrupt requests.</li> </ul> |

| [5:0]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                           |

ILO<u>G</u> abedded in Life

74

## **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps to configure a timer for COMPARATOR COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer reload in COMPARATOR COUNTER Mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions since the timer start is computed via the following equation:

Comparator Output Transitions = Current Count Value – Start Value

#### WDT Reset in NORMAL Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Watchdog Timer Control Register is set to 1. For more information about System Reset, see **the** <u>Reset and Stop</u> <u>Mode Recovery</u> chapter on page 21.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following WDT time-out in STOP Mode. For more information, see **the** <u>Reset and Stop Mode Recovery</u> chapter on page 21.

### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer Control Register (WDTCTL) address unlocks the three Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. The following sequence is required to unlock the Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register (WDTCTL): see page 94

Watchdog Timer Reload Upper Byte Register (WDTU): see page 95

#### ILOG Embedded in Life IXYS Company 104

scheme is enabled, the UART Address Compare register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR Mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes

- Interrupt on matched address bytes and correctly framed data bytes

- Interrupt only on correctly framed data bytes

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare register. This mode introduces additional hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second

#### **Baud Rate Generator Interrupts**

If the Baud Rate Generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Observe the following steps to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) × BRG[15:0]

## **UART Control Register Definitions**

The UART control registers support the UART and the associated infrared encoder/decoders. For more information about the infrared operation, see the <u>Infrared Encoder/Decoder</u> chapter on page 117.

# Embedded in Life

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data Register (Table 64) are shifted out on the TXDx pin. The Write-only UART Transmit Data Register shares a Register File address with the read-only UART Receive Data Register.

| Bit     | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|------|---|---|----|----|---|---|---|

| Field   |      |   |   | Tک | (D |   |   |   |

| RESET   | Х    | Х | Х | Х  | Х  | Х | Х | Х |

| R/W     | W    | W | W | W  | W  | W | W | W |

| Address | F40H |   |   |    |    |   |   |   |

#### Table 64. UART Transmit Data Register (U0TXD)

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

## **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data Register (Table 65). The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Bit     | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|------|---|---|----|----|---|---|---|

| Field   |      |   |   | RX | (D |   |   |   |

| RESET   | Х    | Х | Х | Х  | Х  | Х | Х | Х |

| R/W     | R    | R | R | R  | R  | R | R | R |

| Address | F40H |   |   |    |    |   |   |   |

| Bit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

116

dded in Life

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 73 provides information about data rate errors for a 5.5296MHz System Clock.

|                          | 5.5296MHz S              | ystem Clock          |           |

|--------------------------|--------------------------|----------------------|-----------|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |

| 1250.0                   | N/A                      | N/A                  | N/A       |

| 625.0                    | N/A                      | N/A                  | N/A       |

| 250.0                    | 1                        | 345.6                | 38.24     |

| 115.2                    | 3                        | 115.2                | 0.00      |

| 57.6                     | 6                        | 57.6                 | 0.00      |

| 38.4                     | 9                        | 38.4                 | 0.00      |

| 19.2                     | 18                       | 19.2                 | 0.00      |

| 9.60                     | 36                       | 9.60                 | 0.00      |

| 4.80                     | 72                       | 4.80                 | 0.00      |

| 2.40                     | 144                      | 2.40                 | 0.00      |

| 1.20                     | 288                      | 1.20                 | 0.00      |

| 0.60                     | 576                      | 0.60                 | 0.00      |

| 0.30                     | 1152                     | 0.30                 | 0.00      |

#### Table 73. UART Baud Rates

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20kHz or above 20MHz.

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   |      |     |     | FFR | EQH |     |     |     |

| RESET   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FFAH |     |     |     |     |     |     |     |

#### Table 85. Flash Frequency High Byte Register (FFREQH)

| Bit    | Description                                    |

|--------|------------------------------------------------|

| [7:0]  | Flash Frequency High Byte                      |

| FFREQH | High byte of the 16-bit Flash Frequency value. |

#### Table 86. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7      | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|--------|------|---|---|---|---|---|---|

| Field   | FFREQL |      |   |   |   |   |   |   |

| RESET   |        | 0    |   |   |   |   |   |   |

| R/W     | R/W    |      |   |   |   |   |   |   |

| Address |        | FFBH |   |   |   |   |   |   |

| Bit    | Description                                   |

|--------|-----------------------------------------------|

| [7:0]  | Flash Frequency Low Byte                      |

| FFREQL | Low byte of the 16-bit Flash Frequency value. |

> ilog Embedded in Life An IXYS Company 152

#### Table 92. Trim Option Bits at 0001H

| Bit       | 7                                             | 6   | 5   | 4    | 3     | 2   | 1   | 0   |  |

|-----------|-----------------------------------------------|-----|-----|------|-------|-----|-----|-----|--|

| Field     |                                               |     |     | Rese | erved |     |     |     |  |

| RESET     | U                                             | U   | U   | U    | U     | U   | U   | U   |  |

| R/W       | R/W                                           | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |  |

| Address   | Information Page Memory 0021H                 |     |     |      |       |     |     |     |  |

| Note: U = | te: U = Unchanged by Reset. R/W = Read/Write. |     |     |      |       |     |     |     |  |

| Bit   | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                  |

|       | These bits are reserved. Altering this register may result in incorrect device operation. |

#### Table 93. Trim Option Bits at 0002H (TIPO)

| Bit       | 7                                               | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|-------------------------------------------------|----------|---|---|---|---|---|---|--|

| Field     |                                                 | IPO_TRIM |   |   |   |   |   |   |  |

| RESET     |                                                 | U        |   |   |   |   |   |   |  |

| R/W       |                                                 | R/W      |   |   |   |   |   |   |  |

| Address   | Information Page Memory 0022H                   |          |   |   |   |   |   |   |  |

| Note: U = | lote: U = Unchanged by Reset. R/W = Read/Write. |          |   |   |   |   |   |   |  |

| Bit      | Description                                                   |

|----------|---------------------------------------------------------------|

| [7:0]    | Internal Precision Oscillator Trim Byte                       |

| IPO_TRIM | Contains trimming bits for the Internal Precision Oscillator. |

## **Zilog Calibration Data**

This section briefly describes the features of the following Flash Option Bit calibration registers.

ADC Calibration Data: see page 153

Serialization Data: see page 154

Randomized Lot Identifier: see page 154

#### ilog<sup>°</sup> Embedded in Life An TIXYS Company 158

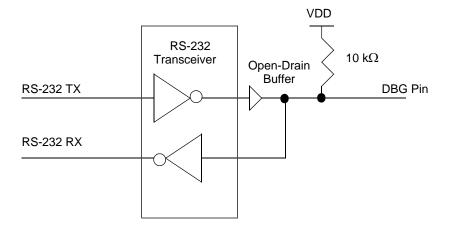

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 2 of 2

## **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The device enters DEBUG Mode following the operations below:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (breakpoint) instruction

- If the DBG pin is held Low during the most recent clock cycle of System Reset, the part enters DEBUG Mode upon exiting System Reset

• Note: Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an autobaud sequence (see the <u>OCD Autobaud Detector/</u><u>Generator section on page 159</u>).

#### $V_{DD} = 3.0 V \text{ to } 3.6 V$ $T_A = 0^{\circ}C$ to +70°C (unless otherwise stated) Symbol Parameter **Maximum Units Conditions** Minimum Typical As defined by -3 dB Signal Input Bandwidth 10 kHz \_ point Analog Source Impedance<sup>4</sup> kW In unbuffered mode $R_S$ 10 \_ \_ Zin kW In unbuffered mode at Input Impedance 150 20MHz<sup>5</sup> Vin Input Voltage Range 0 $V_{DD}$ V **Unbuffered Mode**

Table 128. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

| V <sub>DD</sub> = 2.7V to 3.6V<br>T <sub>A</sub> = -40°C to +105°C |                                            |                 |            |                    |       |                    |  |  |

|--------------------------------------------------------------------|--------------------------------------------|-----------------|------------|--------------------|-------|--------------------|--|--|

| Symbol                                                             | Parameter                                  | Minimum         | Typical    | Maximum            | Units | Conditions         |  |  |

| V <sub>OS</sub>                                                    | Input DC Offset                            |                 | 5          |                    | mV    |                    |  |  |

| V <sub>CREF</sub>                                                  | Programmable Internal<br>Reference Voltage |                 | <u>+</u> 5 |                    | %     | 20-/28-pin devices |  |  |

|                                                                    |                                            |                 | <u>+</u> 3 |                    | %     | 8-pin devices      |  |  |

| T <sub>PROP</sub>                                                  | Propagation Delay                          |                 | 200        |                    | ns    |                    |  |  |

| V <sub>HYS</sub>                                                   | Input Hysteresis                           |                 | 4          |                    | mV    |                    |  |  |

| V <sub>IN</sub>                                                    | Input Voltage Range                        | V <sub>SS</sub> |            | V <sub>DD</sub> -1 | V     |                    |  |  |

#### Table 129. Comparator Electrical Characteristics

## General Purpose I/O Port Input Data Sample Timing

Figure 29 displays a timing sequence for the GPIO port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The port value is

221

## Index

## **Numerics**

10-bit ADC 4

## Α

absolute maximum ratings 196 AC characteristics 200 ADC 178 architecture 121 block diagram 122 continuous conversion 124 control register 126, 129 control register definitions 126 data high byte register 130 data low bits register 131 electrical characteristics and timing 203 operation 122 single-shot conversion 123 ADCCTL register 126, 129 ADCDH register 130 ADCDL register 131 **ADCX 178** ADD 178 add - extended addressing 178 add with carry 178 add with carry - extended addressing 178 additional symbols 177 address space 13 **ADDX 178** analog signals 10 analog-to-digital converter (ADC) 121 AND 181 **ANDX 181** arithmetic instructions 178 assembly language programming 174 assembly language syntax 175

## В

B 177

b 176 baud rate generator, UART 108 **BCLR 179** binary number suffix 177 **BIT 179** bit 176 clear 179 manipulation instructions 179 set 179 set or clear 179 swap 179 test and jump 181 test and jump if non-zero 181 test and jump if zero 181 bit jump and test if non-zero 181 bit swap 181 block diagram 3 block transfer instructions 179 **BRK 181 BSET 179** BSWAP 179, 181 BTJ 181 **BTJNZ 181 BTJZ 181**

## С

CALL procedure 181 CAPTURE mode 89 CAPTURE/COMPARE mode 89 cc 176 CCF 180 characteristics, electrical 196 clear 180 CLR 180 COM 181 COMPARE 89 compare - extended addressing 178 COMPARE mode 89 compare with carry 178