Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0123sj005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Z8 Encore! XP <sup>®</sup> F0823 Series<br>Product Specification |  |

|------------------------------------------------------------------|--|

| Embedded in Llfe                                                 |  |

3

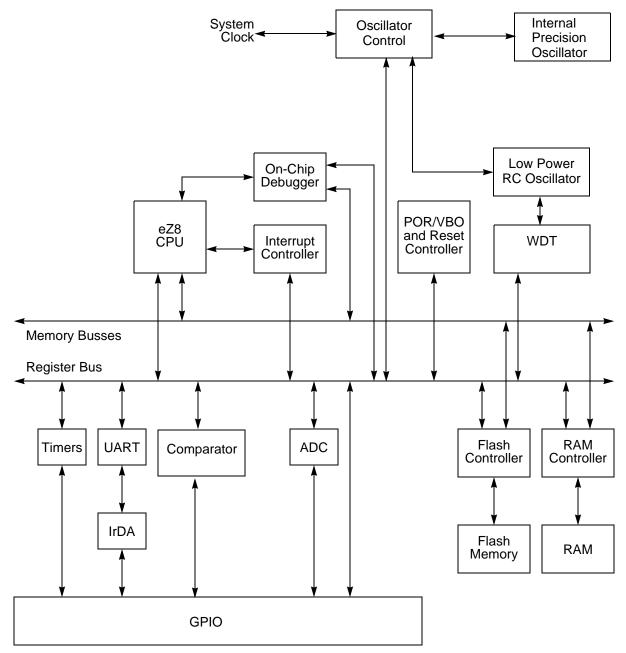

# **Block Diagram**

Figure 1 displays a block diagram of the F0823 Series architecture.

Figure 1. Z8 Encore! XP F0823 Series Block Diagram

#### ilog Embedded in Life An 🛙 IXYS Company

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 8-pin devices.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                         | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up<br>or Pull-<br>down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                    |

|--------------------|-----------|----------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if<br>key<br>sequence<br>detected) | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O<br>(defaults<br><u>to</u><br>RESET)                                    | N/A                                   | Yes                | Program-<br>mable for<br>PA2;<br>always<br>on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

| VSS                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

#### Table 5. Pin Characteristics (8-Pin Devices)

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see **the** <u>Port A–C Control Registers</u> **section on page 42**), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overrightarrow{\text{RESET}}$  pin Low. The  $\overrightarrow{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

## **Stop Mode Recovery**

The device enters into STOP Mode when eZ8 CPU executes a STOP instruction. For more details about STOP Mode, see **the** Low-Power Modes **section on page 30**. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

ILO G Embedded in Life

■IXYS Company

53

# LED Drive Level Low Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 34). These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit     | 7   | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|---------|-----|-----|-----|

| Field   |     |     |     | LEDLV | LL[7:0] |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Address |     |     |     | F8    | 4H      |     |     |     |

#### Table 34. LED Drive Level Low Register (LEDLVLL)

Bit

Description

[7:0]

LED Level High Bit

LEDLVLL

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3mA.

01 = 7mA.

10 = 13mA.

11 = 20mA.

#### Table 40. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit           | 7                          | 6                                                                 | 5           | 4             | 3       | 2    | 1     | 0      |  |  |

|---------------|----------------------------|-------------------------------------------------------------------|-------------|---------------|---------|------|-------|--------|--|--|

| Field         | Reserved                   | T1ENH                                                             | T0ENH       | <b>U0RENH</b> | U0TENH  | Rese | erved | ADCENH |  |  |

| RESET         | 0                          | 0 0 0 0 0 0                                                       |             |               |         |      |       |        |  |  |

| R/W           | R/W                        | R/W                                                               | R/W         | R/W           | R/W     | R/   | W     | R/W    |  |  |

| Address       |                            |                                                                   |             | FC            | 1H      |      |       |        |  |  |

| Bit           | Description                | escription                                                        |             |               |         |      |       |        |  |  |

| [7]           | Reserved<br>This bit is re | Reserved<br>This bit is reserved and must be programmed to 0.     |             |               |         |      |       |        |  |  |

| [6]<br>T1ENH  | Timer 1 Int                | errupt Req                                                        | uest Enable | e High Bit    |         |      |       |        |  |  |

| [5]<br>T0ENH  | Timer 0 Int                | errupt Req                                                        | uest Enable | e High Bit    |         |      |       |        |  |  |

| [4]<br>U0RENH | UART 0 Re                  | ceive Inter                                                       | rupt Reque  | st Enable H   | igh Bit |      |       |        |  |  |

| [3]<br>U0TENH | UART 0 Tra                 | JART 0 Transmit Interrupt Request Enable High Bit                 |             |               |         |      |       |        |  |  |

| [2:1]         | Reserved<br>These bits a   | Reserved<br>These bits are reserved and must be programmed to 00. |             |               |         |      |       |        |  |  |

| [0]           | ADC Interr                 | upt Reques                                                        | t Enable Hi | igh Bit       |         |      |       |        |  |  |

[0] ADCENH

#### Table 41. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5            | 4             | 3             | 2    | 1     | 0      |

|---------|----------|-------|--------------|---------------|---------------|------|-------|--------|

| Field   | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Rese | erved | ADCENL |

| RESET   | 0        | 0     | 0            | 0             | 0             | (    | )     | 0      |

| R/W     | R        | R/W   | R/W          | R/W           | R/W           | F    | २     | R/W    |

| Address |          |       |              | FC            | 2H            |      |       |        |

| Bit          | Description                                                             |

|--------------|-------------------------------------------------------------------------|

| [7]          | Reserved<br>This bit is reserved and must be programmed to 0 when read. |

| [6]<br>T1ENL | Timer 1 Interrupt Request Enable Low Bit                                |

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the capture occurs on a rising edge or a falling edge of the Timer Input signal. When the capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL1 Register clears indicating the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture or a reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

> ilog Embedded in Life An IXYS Company 85

|         |     | -   | -   | -     |      |     | -   |     |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

| Field   |     |     |     | TF    | RH   |     |     |     |

| RESET   | 1   | 1   | 1   | 1     | 1    | 1   | 1   | 1   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F02H, | F0AH |     |     |     |

#### Table 53. Timer 0–1 Reload High Byte Register (TxRH)

#### Table 54. Timer 0–1 Reload Low Byte Register (TxRL)

| Bit     | 7          | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|------------|-----|-----|-------|------|-----|-----|-----|

| Field   |            |     |     | TF    | RL   |     |     |     |

| RESET   | 1          | 1   | 1   | 1     | 1    | 1   | 1   | 1   |

| R/W     | R/W        | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |            |     |     | F03H, | F0BH |     |     |     |

| Bit     | Descriptio | n   |     |       |      |     |     |     |

| [7]     |            |     |     |       |      |     |     |     |

| [6]     |            |     |     |       |      |     |     |     |

| [5]     |            |     |     |       |      |     |     |     |

| [4]     |            |     |     |       |      |     |     |     |

| [3]     |            |     |     |       |      |     |     |     |

| [2]     |            |     |     |       |      |     |     |     |

| [1]     |            |     |     |       |      |     |     |     |

| [0]     |            |     |     |       |      |     |     |     |

TRH and TRL—Timer Reload Register High and Low

These two bytes form the 16-bit reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE Mode, these two bytes form the 16-bit compare value.

ilog<sup>°</sup> Embedded in Life An∎IXYS Company **88**

|         |     |            |            |     | <b>U</b> ( | ,   |     |     |

|---------|-----|------------|------------|-----|------------|-----|-----|-----|

| Bit     | 7   | 6          | 5          | 4   | 3          | 2   | 1   | 0   |

| Field   | TEN | TPOL       | PRES TMODE |     |            |     |     |     |

| RESET   | 0   | 0          | 0          | 0   | 0          | 0   | 0   | 0   |

| R/W     | R/W | R/W        | R/W        | R/W | R/W        | R/W | R/W | R/W |

| Address |     | F07H, F0FH |            |     |            |     |     |     |

#### Table 58. Timer 0–1 Control Register 1 (TxCTL1)

| Audress     |                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Description                                                                                                                                                                                                                                                                                                                    |

| [7]<br>TEN  | Timer Enable0 = Timer is disabled.1 = Timer enabled to count.                                                                                                                                                                                                                                                                  |

| [6]<br>TPOL | <b>Timer Input/Output Polarity</b><br>Operation of this bit is a function of the current operating mode of the timer.<br><b>ONE-SHOT Mode</b><br>When the timer is disabled, the Timer Output signal is set to the value of this bit. When the<br>timer is enabled, the Timer Output signal is complemented upon timer reload. |

|             | <b>CONTINUOUS Mode</b><br>When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer reload.                                                                                                                           |

# Embedded in Life An IXYS Company 97

# Universal Asynchronous Receiver/ Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. The features of UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) Mode with three configurable interrupt schemes

- BRG can be configured and used as a basic 16-bit timer

- Driver Enable output for external bus transceivers

## Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

edded in Life

IXYS Company

119

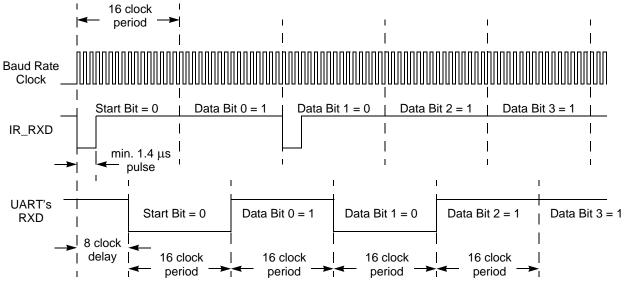

### **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the infrared endec and passed to the UART. The UART's baud rate clock is used by the infrared endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the infrared endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP F0823 Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0MHz to ensure proper reception of the 1.4µs minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens.

#### ilog<sup>\*</sup> Embedded in Life An IXYS Company 133

# **Comparator Control Register Definition**

The Comparator Control Register (CMPCTL) configures the comparator inputs and sets the value of the internal voltage reference.

| Bit             | 7                                                                                                                                                                                                                                                          | 6                                                | 5             | 4            | 3             | 2           | 1              | 0       |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------|--------------|---------------|-------------|----------------|---------|--|--|--|

| Field           | INPSEL                                                                                                                                                                                                                                                     | INNSEL                                           |               | REF          | LVL           | I           | Rese           | erved   |  |  |  |

| RESET           | 0                                                                                                                                                                                                                                                          | 0                                                | 0             | 1            | 0             | 1           | 0              | 0       |  |  |  |

| R/W             | R/W                                                                                                                                                                                                                                                        | R/W                                              | R/W           | R/W          | R/W           | R/W         | R/W            | R/W     |  |  |  |

| Address         |                                                                                                                                                                                                                                                            | F90H                                             |               |              |               |             |                |         |  |  |  |

| Bit             | Descriptio                                                                                                                                                                                                                                                 | Description                                      |               |              |               |             |                |         |  |  |  |

| [7]<br>INPSEL   | 0 = GPIO p                                                                                                                                                                                                                                                 | ect for Posi<br>in used as p<br>ature sensor     | ositive com   |              |               |             |                |         |  |  |  |

| [6]<br>INNSEL   | Signal Select for Negative Input<br>0 = internal reference disabled, GPIO pin used as negative comparator input.<br>1 = internal reference enabled as negative comparator input.                                                                           |                                                  |               |              |               |             |                |         |  |  |  |

| [5:2]<br>REFLVL | $\begin{array}{l} 0000 = 0.0^{\circ}\\ 0001 = 0.2^{\circ}\\ 0010 = 0.4^{\circ}\\ 0011 = 0.6^{\circ}\\ 0100 = 0.8^{\circ}\\ 0101 = 1.0^{\circ}\\ 0110 = 1.2^{\circ}\\ 0111 = 1.4^{\circ}\\ 1000 = 1.6^{\circ}\\ 1001 = 1.8^{\circ}\\ 1010-1111 \end{array}$ | V.<br>V.<br>V.<br>V.<br>V (Default).<br>V.<br>V. |               |              | C voltage ref | ference.    |                |         |  |  |  |

| [1:0]           | Reserved<br>These bits a<br>read.                                                                                                                                                                                                                          | are reserved                                     | l; R/W bits r | nust be prog | rammed to     | 00 during w | rites and to ( | 00 when |  |  |  |

#### Table 78. Comparator Control Register (CMP0)

Figure 20. Flash Memory Arrangement

### **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

### Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

Figure 21 displays a basic Flash Controller flow. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

ILO<u>G</u> nbedded in Life

141

- Programming operations are not limited to the page selected in the Page Select register

- Bits in the Flash Sector Protect register can be written to one or zero

- The second write of the Page Select register to unlock the Flash Controller is not necessary

- The Page Select register can be written when the Flash Controller is unlocked

- The Mass Erase command is enabled through the Flash Control Register

**Caution:** For security reasons, the Flash Controller allows only a single page to be opened for write/erase. When writing multiple Flash pages, the Flash controller must repeat the unlock sequence to select another page.

### **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 141

Flash Status Register: see page 143

Flash Page Select Register: see page 143

Flash Sector Protect Register: see page 145

Flash Frequency High and Low Byte Registers: see page 145

### **Flash Control Register**

٠

The Flash Controller must be unlocked using the Flash Control (FTCTL) Register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select register. Mass Erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

#### ILO 9<sup>°</sup> Inbedded in Life IIXYS Company 147

### **Option Bit Types**

This section describes the five types of Flash option bits offered in the F083A Series.

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 in program memory is erased.

### **Trim Option Bits**

The trim option bits are contained in a Flash memory information page. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

**Note:** The trim address range is from information address 20–3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in the <u>Flash Information Area</u> section on page 15.

#### **Serialization Bits**

As an optional feature, Zilog is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

ILOG<sup>®</sup> Ibedded in Life IXYS Company 164

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

**Read Register (09H).** The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

Write Program Memory (0AH). The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

Table 102. OCD Control Register (OCDCTL)

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                                                                     | 6                                                                                                                                                                                                                                                                                                                                                                                               | 5      | 4 | 3    | 2     | 1 | 0   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---|------|-------|---|-----|

| Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DBGMODE                                                               | BRKEN                                                                                                                                                                                                                                                                                                                                                                                           | DBGACK |   | Rese | erved | l | RST |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                               | 0      | 0 | 0    | 0     | 0 | 0   |

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                                                             | R/W    | R | R    | R     | R | R/W |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit Description                                                       |                                                                                                                                                                                                                                                                                                                                                                                                 |        |   |      |       |   |     |

| <ul> <li>[7] DEBUG Mode</li> <li>DBGMODE The device enters DEBUG Mode when this bit is 1. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.</li> <li>0 = F0823 Series device is operating in NORMAL Mode.</li> <li>1 = F0823 Series device is in DEBUG Mode.</li> </ul> |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                 |        |   |      |       |   |     |

| [6]<br>BRKEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | This bit co<br>are disable<br>when a BR<br>cally set to<br>0 = Breakp | Breakpoint Enable<br>This bit controls the behavior of the BRK instruction (opcode 00H). By default, breakpoints<br>are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1,<br>when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automati-<br>cally set to 1.<br>0 = Breakpoints are disabled.<br>1 = Breakpoints are enabled. |        |   |      |       |   |     |

| [5]<br>DBGACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | This bit en<br>Debug Acł<br>0 = Debug                                 | <ul> <li>Debug Acknowledge</li> <li>This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.</li> <li>0 = Debug Acknowledge is disabled.</li> <li>1 = Debug Acknowledge is enabled.</li> </ul>                                                                                          |        |   |      |       |   |     |

| [4:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reserved<br>These bits                                                | <b>Reserved</b><br>These bits are reserved and must be 00000 when read.                                                                                                                                                                                                                                                                                                                         |        |   |      |       |   |     |

| [0]<br>RST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Power-On<br>ically clear<br>0 = No effe                               | <ul> <li>Reset</li> <li>Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal Power-On Reset sequence with the exception that the OCD is not reset. This bit is automatically cleared to 0 at the end of reset.</li> <li>0 = No effect.</li> <li>1 = Reset the Flash Read Protect Option Bit device.</li> </ul>                                              |        |   |      |       |   |     |

| Mnemonic | Operands | Instruction            |  |  |

|----------|----------|------------------------|--|--|

| ATM      | _        | Atomic Execution       |  |  |

| CCF      | —        | Complement Carry Flag  |  |  |

| DI       | —        | Disable Interrupts     |  |  |

| EI       | _        | Enable Interrupts      |  |  |

| HALT     | _        | HALT Mode              |  |  |

| NOP      | —        | No Operation           |  |  |

| RCF      | —        | Reset Carry Flag       |  |  |

| SCF      | —        | Set Carry Flag         |  |  |

| SRP      | src      | Set Register Pointer   |  |  |

| STOP     | —        | STOP Mode              |  |  |

| WDT      | _        | Watchdog Timer Refresh |  |  |

#### Table 113. CPU Control Instructions

#### Table 114. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

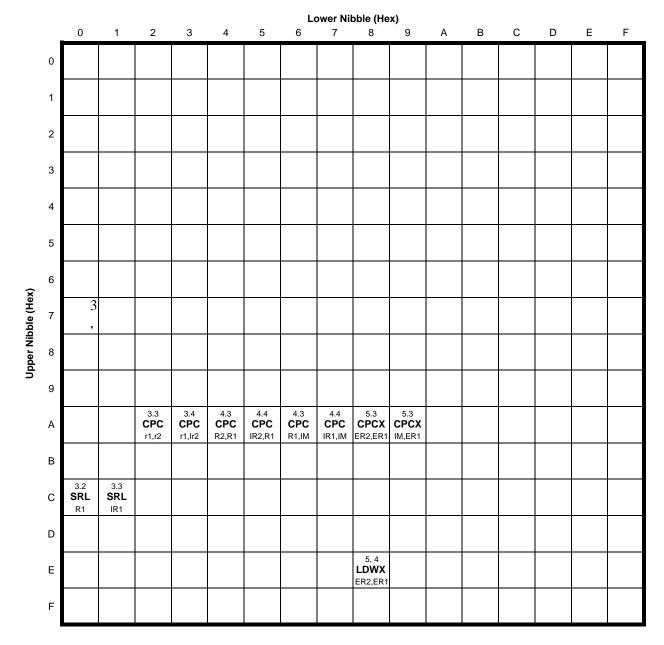

Figure 28. Second Opcode Map after 1FH

# Embedded in Life An IXYS Company 197

# **DC Characteristics**

Table 121 lists the DC characteristics of the Z8 Encore! XP F0823 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

|                  | T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise specified) |                     |                |                      |       |                                                                                                                                                                |

|------------------|------------------------------------------------------------------|---------------------|----------------|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                                        | Minimum             | Typical        | Maximum              | Units | Conditions                                                                                                                                                     |

| V <sub>DD</sub>  | Supply Voltage                                                   | 2.7                 | -              | 3.6                  | V     |                                                                                                                                                                |

| V <sub>IL1</sub> | Low Level Input<br>Voltage                                       | -0.3                | -              | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                                |

| V <sub>IH1</sub> | High Level Input<br>Voltage                                      | 0.7*V <sub>DD</sub> | -              | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all sig-<br>nal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage                                      | 0.7*V <sub>DD</sub> | -              | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when pro-<br>grammable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage                                      | -                   | _              | 0.4                  | V     | I <sub>OL</sub> = 2mA; V <sub>DD</sub> = 3.0V<br>High Output Drive disabled.                                                                                   |

| V <sub>OH1</sub> | High Level Output<br>Voltage                                     | 2.4                 | _              | _                    | V     | $I_{OH} = -2mA; V_{DD} = 3.0V$<br>High Output Drive disabled.                                                                                                  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage                                      | -                   | -              | 0.6                  | V     | I <sub>OL</sub> = 20mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                                  |

| V <sub>OH2</sub> | High Level Output<br>Voltage                                     | 2.4                 | -              | -                    | V     | I <sub>OH</sub> = -20mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                                 |

| I <sub>IH</sub>  | Input Leakage Cur-<br>rent                                       | -                   | <u>+</u> 0.002 | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>IL</sub>  | Input Leakage Cur-<br>rent                                       | -                   | <u>+</u> 0.007 | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>TL</sub>  | Tristate Leakage<br>Current                                      | -                   | -              | <u>+</u> 5           | μA    |                                                                                                                                                                |

| Table 121. | DC | Characteristics |

|------------|----|-----------------|

|            |    | •               |

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.