Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213hh005eg |

# Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| Flash Code Protection Against Accidental Program and Erasure | 137 |

|--------------------------------------------------------------|-----|

| Byte Programming                                             | 139 |

| Page Erase                                                   | 139 |

| Mass Erase                                                   | 139 |

| Flash Controller Bypass                                      | 140 |

| Flash Controller Behavior in DEBUG Mode                      | 140 |

| Flash Control Register Definitions                           | 141 |

| Flash Control Register                                       | 141 |

| Flash Status Register                                        | 142 |

| Flash Page Select Register                                   | 142 |

| Flash Sector Protect Register                                | 144 |

| Flash Frequency High and Low Byte Registers                  | 144 |

| Flash Option Bits                                            | 146 |

| Operation                                                    |     |

| Option Bit Configuration By Reset                            |     |

| Option Bit Types                                             |     |

| Reading the Flash Information Page                           |     |

| Flash Option Bit Control Register Definitions                |     |

| Trim Bit Address Register                                    |     |

| Trim Bit Data Register                                       |     |

| Flash Option Bit Address Space                               |     |

| Trim Bit Address Space                                       |     |

| Zilog Calibration Data                                       |     |

| ADC Calibration Data                                         |     |

| Serialization Data                                           |     |

| Randomized Lot Identifier                                    |     |

|                                                              |     |

| On-Chip Debugger                                             |     |

| Architecture                                                 |     |

| Operation                                                    |     |

| OCD Interface                                                |     |

| DEBUG Mode                                                   |     |

| OCD Data Format                                              |     |

| OCD Autobaud Detector/Generator                              |     |

| OCD Serial Errors                                            |     |

| OCD Unlock Sequence (8-Pin Devices Only)                     |     |

| Breakpoints                                                  |     |

| Runtime Counter                                              |     |

| On-Chip Debugger Commands                                    |     |

| On-Chip Debugger Control Register Definitions                |     |

| OCD Control Register                                         | 166 |

**Table 3. Signal Descriptions (Continued)**

| Signal Mnemonic               | I/O | Description                                                                                                                                                                                                           |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COUT                          | 0   | Comparator Output. This is the output of the comparator.                                                                                                                                                              |

| Analog                        |     |                                                                                                                                                                                                                       |

| ANA[7:0]                      | I   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                          | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                   |     |                                                                                                                                                                                                                       |

| CLKIN                         | I   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                   |     |                                                                                                                                                                                                                       |

| LED                           | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                           |

| On-Chip Debugger              |     |                                                                                                                                                                                                                       |

| DBG                           | I/O | Debug. This signal is the control and data input and output to and from the OCD.  Caution: The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                            |

| Reset                         |     |                                                                                                                                                                                                                       |

| RESET                         | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                  |     |                                                                                                                                                                                                                       |

| $V_{DD}$                      | ļ   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> <sup>2</sup> | I   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>               | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>              | I   | Analog Ground.                                                                                                                                                                                                        |

| Notos:                        |     |                                                                                                                                                                                                                       |

- 1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are

- replaced by AV<sub>DD</sub> and AV<sub>SS</sub>.

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 8-pin devices.

**Table 5. Pin Characteristics (8-Pin Devices)**

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                         | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up<br>or Pull-<br>down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                    |

|--------------------|-----------|----------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if<br>key<br>sequence<br>detected) | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | I                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O<br>(defaults<br>to<br>RESET)                                           | N/A                                   | Yes                | Program-<br>mable for<br>PA2;<br>always<br>on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

| VSS                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

>

**Note:** This register is only reset during a Power-On Reset sequence. Other System Reset events do not affect it.

Table 14. Power Control Register 0 (PWRCTL0)

| Bit     | 7        | 6        | 5   | 4   | 3        | 2   | 1    | 0        |

|---------|----------|----------|-----|-----|----------|-----|------|----------|

| Field   | Reserved | Reserved |     | VBO | Reserved | ADC | COMP | Reserved |

| RESET   | 1        | 0        | 0   | 0   | 0        | 0   | 0    | 0        |

| R/W     | R/W      | R/W      | R/W | R/W | R/W      | R/W | R/W  | R/W      |

| Address | F80H     |          |     |     | 0H       |     |      |          |

| Bit         | Description                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]         | Reserved This bit is reserved and must be programmed to 1.                                                                                                          |

| [6:5]       | Reserved These bits are reserved and must be programmed to 00.                                                                                                      |

| [4]<br>VBO  | Voltage Brown-Out Detector Disable This bit and the VBO_AO Flash option bit must both enable the VBO for the VBO to be active.  0 = VBO enabled.  1 = VBO disabled. |

| [3]         | Reserved This bit is reserved and must be programmed to 0.                                                                                                          |

| [2]<br>ADC  | Analog-to-Digital Converter Disable  0 = Analog-to-Digital Converter enabled.  1 = Analog-to-Digital Converter disabled.                                            |

| [1]<br>COMP | Comparator Disable 0 = Comparator is enabled. 1 = Comparator is disabled.                                                                                           |

| [0]         | Reserved This bit is reserved and must be programmed to 0.                                                                                                          |

Table 18. GPIO Port Registers and Subregisters (Continued)

| Port Register<br>Mnemonic | Port Register Name                |

|---------------------------|-----------------------------------|

| P <i>x</i> HDE            | High Drive Enable.                |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable. |

| P <i>x</i> PUE            | Pull-up Enable.                   |

| PxAFS1                    | Alternate Function Set 1.         |

| PxAFS2                    | Alternate Function Set 2.         |

# Port A-C Address Registers

The Port A–C Address registers select the GPIO port functionality accessible through the Port A–C Control registers. The Port A–C Address and Control registers combine to provide access to all GPIO port controls (Table 19).

Table 19. Port A–C GPIO Address Registers (PxADDR)

| Bit     | 7   | 6                | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------------|-----|-----|-----|-----|-----|-----|

| Field   |     | PADDR[7:0]       |     |     |     |     |     |     |

| RESET   |     | 00H              |     |     |     |     |     |     |

| R/W     | R/W | R/W              | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | FD0H, FD4H, FD8H |     |     |     |     |     |     |

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The Port Address selects one of the subregisters accessible through the Port Control Register. |

|       | See Table 20 for each subregister function.                                                    |

Table 20. PADDR[7:0] Subregister Functions

|   | PADDR[7:0] | Port Control Subregister Accessible Using the Port A–C Control Registers       |

|---|------------|--------------------------------------------------------------------------------|

| - | 00H        | No function. Provides some protection against accidental Port reconfiguration. |

| - | 01H        | Data Direction.                                                                |

| - | 02H        | Alternate Function.                                                            |

|   | 03H        | Output Control (Open-Drain).                                                   |

| - | 04H        | High Drive Enable                                                              |

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 38) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

Table 38. Interrupt Request 2 Register (IRQ2)

| Bit     | 7   | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|---------|-----|------|-------|-----|------|------|------|------|

| Field   |     | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0   | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| Address |     | FC6H |       |     |      |      |      |      |

| Bit   | Description                                                          |  |

|-------|----------------------------------------------------------------------|--|

| [7:4] | Reserved                                                             |  |

|       | These bits are reserved and must be programmed to 0000.              |  |

| [3:0] | Port C Pin x Interrupt Request                                       |  |

| PCxI  | 0 = No interrupt request is pending for GPIO Port C pin x.           |  |

|       | 1 = An interrupt request from GPIO Port C pin x is awaiting service. |  |

| Note: | x indicates the specific GPIO Port C pin number (3–0).               |  |

# IRQ0 Enable High and Low Bit Registers

Table 39 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 40 and Table 41) form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register. Priority is generated by setting bits in each register.

Table 39. IRQ0 Enable and Priority Encoding

| IRQ0ENL[x] | Priority         | Description                    |

|------------|------------------|--------------------------------|

| 0          | Disabled         | Disabled                       |

| 1          | Level 1          | Low                            |

| 0          | Level 2          | Nominal                        |

| 1          | Level 3          | High                           |

|            | 0<br>1<br>0<br>1 | 0 Disabled 1 Level 1 0 Level 2 |

Note: where *x* indicates the register bits from 0–7.

causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TxL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

Table 51. Timer 0–1 High Byte Register (TxH)

| Bit     | 7   | 6                       | 5 | 4     | 3    | 2 | 1 | 0 |  |

|---------|-----|-------------------------|---|-------|------|---|---|---|--|

| Field   |     | TH                      |   |       |      |   |   |   |  |

| RESET   | 0   | 0                       | 0 | 0     | 0    | 0 | 0 | 0 |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W |   |       |      |   |   |   |  |

| Address |     |                         |   | F00H, | F08H |   |   |   |  |

Table 52. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Field   |     | TL  |     |       |      |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 1   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F01H, | F09H |     |     |     |

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

# **Timer Reload High and Low Byte Registers**

The Timer 0-1 Reload High and Low Byte (TxRH and TxRL) registers (Table 53 and Table 54) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer reload value. In COMPARE Mode, the Timer Reload High and Low Byte registers store the 16-bit compare value.

# Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers (Table 55 and Table 56) control pulse-width modulator (PWM) operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

Table 55. Timer 0–1 PWM High Byte Register (TxPWMH)

| Bit     | 7   | 7 6 5 4 3 2 1 0         |   |       |      |   |   |   |  |

|---------|-----|-------------------------|---|-------|------|---|---|---|--|

| Field   |     | PWMH                    |   |       |      |   |   |   |  |

| RESET   | 0   | 0                       | 0 | 0     | 0    | 0 | 0 | 0 |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W |   |       |      |   |   |   |  |

| Address |     |                         |   | F04H, | F0CH |   |   |   |  |

Table 56. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7   | 6                           | 5 | 4     | 3    | 2 | 1 | 0 |

|---------|-----|-----------------------------|---|-------|------|---|---|---|

| Field   |     | PWML                        |   |       |      |   |   |   |

| RESET   | 0   | 0 0 0 0 0 0 0               |   |       |      |   |   |   |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |       |      |   |   |   |

| Address |     |                             |   | F05H, | F0DH |   |   |   |

| Bit                    | Description                                                                                                                                                                                                                                                                                               |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>PWMH,<br>PWML | Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register. |

|                        | These TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.                                                                                                                                                                          |

# Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

#### Timer 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode. It also includes a programmable PWM deadband delay,

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled,.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

### Transmitting Data Using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

occurred, this byte cannot contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data Register must be read again to clear the error bits is the UART Status 0 Register. Updates to the Receive Data Register occur only when the next data word is received.

#### **UART Data and Error Handling Procedure**

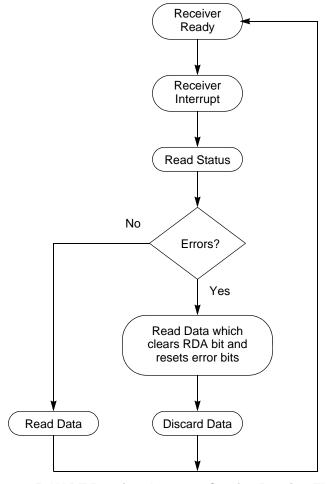

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

Figure 15. UART Receiver Interrupt Service Routine Flow

# **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 66 and Table 67) identify the current UART operating configuration and status.

Table 66. UART Status 0 Register (U0STAT0)

| Bit     | 7   | 6           | 5  | 4  | 3    | 2    | 1   | 0   |

|---------|-----|-------------|----|----|------|------|-----|-----|

| Field   | RDA | PE          | OE | FE | BRKD | TDRE | TXE | CTS |

| RESET   | 0   | 0           | 0  | 0  | 0    | 1    | 1   | Х   |

| R/W     | R   | R R R R R R |    |    |      |      |     |     |

| Address |     |             |    | F4 | 1H   |      |     |     |

| Bit         | Description                                                                                                                                                                                                                                                                                                                  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>RDA  | Receive Data Available This bit indicates that the UART Receive Data Register has received data. Reading the UART Receive Data Register clears this bit.  0 = The UART Receive Data Register is empty.  1 = There is a byte in the UART Receive Data Register.                                                               |

| [6]<br>PE   | Parity Error This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.  0 = No parity error has occurred.  1 = A parity error has occurred.                                                                                                                               |

| [5]<br>OE   | Overrun Error This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data Register has not been read. If the RDA bit is reset to 0, reading the UART Receive Data Register clears this bit.  0 = No overrun error occurred.  1 = An overrun error occurred. |

| [4]<br>FE   | Framing Error This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data Register clears this bit.  0 = No framing error occurred.  1 = A framing error occurred.                                                                                            |

| [3]<br>BRKD | Break Detect This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data Register clears this bit. 0 = No break occurred. 1 = A break occurred.                                                                    |

Table 81. Flash Control Register (FCTL)

| Bit     | 7 | 6             | 5 | 4  | 3  | 2 | 1 | 0 |  |

|---------|---|---------------|---|----|----|---|---|---|--|

| Field   |   | FCMD          |   |    |    |   |   |   |  |

| RESET   | 0 | 0 0 0 0 0 0 0 |   |    |    |   |   |   |  |

| R/W     | W | w w w w w w   |   |    |    |   |   |   |  |

| Address |   |               |   | FF | 8H |   |   |   |  |

| Bit   | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| [7:0] | Flash Command                                                                        |

| FCMD  | 73H = First unlock command.                                                          |

|       | 8CH = Second unlock command.                                                         |

|       | 95H = Page Erase command (must be third command in sequence to initiate Page Erase). |

|       | 63H = Mass Erase command (must be third command in sequence to initiate Mass Erase). |

|       | 5EH = Enable Flash Sector Protect Register Access.                                   |

**Table 110. Arithmetic Instructions (Continued)**

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

**Table 111. Bit Manipulation Instructions**

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| TCM      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| TM       | dst, src    | Test Under Mask                                      |

| TMX      | dst, src    | Test Under Mask using Extended Addressing            |

**Table 112. Block Transfer Instructions**

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

Table 118. eZ8 CPU Instruction Summary (Continued)

| Assembly        |                        |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|-----------------|------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic        | Symbolic Operation     | dst | src         | (Hex)       | С | Z | S   | ٧   | D | Н |         | Cycles |

| BTJNZ bit, src, | if src[bit] = 1        |     | r           | F6          | - | _ | _   | -   | _ | _ | 3       | 3      |

| dst             | $PC \leftarrow PC + X$ |     | lr          | F7          | • |   |     |     |   |   | 3       | 4      |

| BTJZ bit, src,  | if src[bit] = 0        |     | r           | F6          | - | - | _   | -   | _ | _ | 3       | 3      |

| dst             | $PC \leftarrow PC + X$ |     | lr          | F7          | • |   |     |     |   |   | 3       | 4      |

| CALL dst        | SP ← SP <b>–</b> 2     | IRR |             | D4          | - | - | _   | -   | _ | _ | 2       | 6      |

|                 | @SP ← PC<br>PC ← dst   | DA  |             | D6          | - |   |     |     |   |   | 3       | 3      |

| CCF             | C ← ~C                 |     |             | EF          | * | - | _   | -   | _ |   | 1       | 2      |

| CLR dst         | dst ← 00H              | R   |             | В0          | - | - | _   | -   | _ | _ | 2       | 2      |

|                 |                        | IR  |             | B1          |   |   |     |     |   |   | 2       | 3      |

| COM dst         | dst ← ~dst             | R   |             | 60          | - | * | *   | 0   | _ | _ | 2       | 2      |

|                 |                        | IR  |             | 61          | - |   |     |     |   |   | 2       | 3      |

| CP dst, src     | dst - src              | r   | r           | A2          | * | * | *   | *   | _ | _ | 2       | 3      |

|                 |                        | r   | Ir          | A3          | - |   |     |     |   |   | 2       | 4      |

|                 |                        | R   | R           | A4          | - |   |     |     |   |   | 3       | 3      |

|                 |                        | R   | IR          | A5          |   |   |     |     |   |   | 3       | 4      |

|                 |                        | R   | IM          | A6          | - |   |     |     |   |   | 3       | 3      |

|                 |                        | IR  | IM          | A7          | - |   |     |     |   |   | 3       | 4      |

| CPC dst, src    | dst - src - C          | r   | r           | 1F A2       | * | * | *   | *   | _ | _ | 3       | 3      |

|                 |                        | r   | lr          | 1F A3       |   |   |     |     |   |   | 3       | 4      |

|                 |                        | R   | R           | 1F A4       | - |   |     |     |   |   | 4       | 3      |

|                 |                        | R   | IR          | 1F A5       |   |   |     |     |   |   | 4       | 4      |

|                 |                        | R   | IM          | 1F A6       |   |   |     |     |   |   | 4       | 3      |

|                 |                        | IR  | IM          | 1F A7       |   |   |     |     |   |   | 4       | 4      |

| CPCX dst, src   | dst - src - C          | ER  | ER          | 1F A8       | * | * | *   | *   | _ | _ | 5       | 3      |

|                 |                        | ER  | IM          | 1F A9       | • |   |     |     |   |   | 5       | 3      |

| CPX dst, src    | dst - src              | ER  | ER          | A8          | * | * | *   | *   | - | _ | 4       | 3      |

|                 |                        | ER  | IM          | A9          | - |   |     |     |   |   | 4       | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

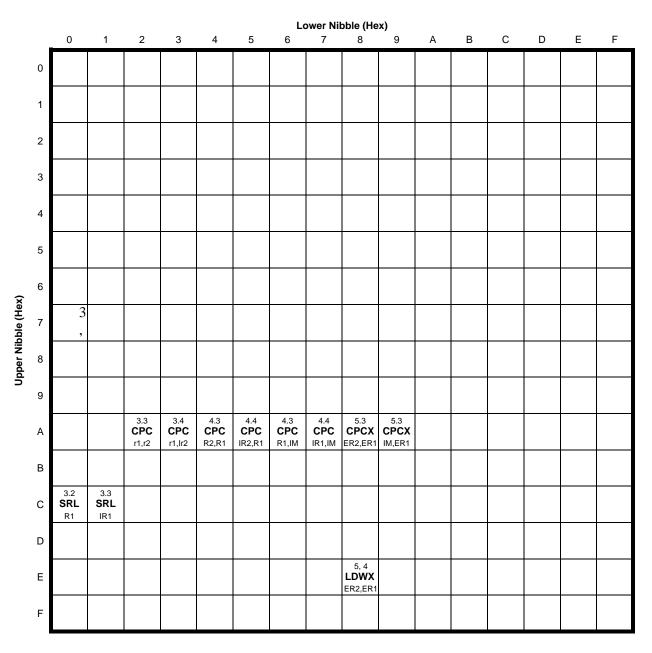

Figure 28. Second Opcode Map after 1FH

**Table 126. Flash Memory Electrical Characteristics and Timing**

$V_{DD}$  = 2.7V to 3.6V  $T_A$  = -40°C to +105°C (unless otherwise stated)

|                                               | •       |         | ,       |        |                                                                                                                                                    |

|-----------------------------------------------|---------|---------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum | Typical | Maximum | Units  | Notes                                                                                                                                              |

| Flash Byte Read Time                          | 100     | -       | _       | ns     |                                                                                                                                                    |

| Flash Byte Program Time                       | 20      | _       | 40      | μs     |                                                                                                                                                    |

| Flash Page Erase Time                         | 10      | _       | _       | ms     |                                                                                                                                                    |

| Flash Mass Erase Time                         | 200     | -       | _       | ms     |                                                                                                                                                    |

| Writes to Single Address<br>Before Next Erase | -       | -       | 2       |        |                                                                                                                                                    |

| Flash Row Program Time                        | -       | -       | 8       | ms     | Cumulative program time for single row cannot exceed limit before next erase. This parameter is only an issue when bypassing the Flash Controller. |

| Data Retention                                | 100     | -       | -       | years  | 25°C                                                                                                                                               |

| Endurance                                     | 10,000  | _       |         | cycles | Program/erase cycles                                                                                                                               |

|                                               |         |         |         |        |                                                                                                                                                    |

**Table 127. Watchdog Timer Electrical Characteristics and Timing**

$V_{DD}$  = 2.7V to 3.6V  $T_A$  = -40°C to +105°C (unless otherwise stated)

|                    |                          | -       |         | -           |       |                                                                                                    |

|--------------------|--------------------------|---------|---------|-------------|-------|----------------------------------------------------------------------------------------------------|

| Symbol             | Parameter                | Minimum | Typical | Maximum     | Units | Conditions                                                                                         |

| F <sub>WDT</sub>   | WDT Oscillator Frequency |         | 10      |             | kHz   |                                                                                                    |

| F <sub>WDT</sub>   | WDT Oscillator Error     |         |         | <u>+</u> 50 | %     |                                                                                                    |

| T <sub>WDT</sub> - | WDT Calibrated Timeout   | 0.98    | 1       | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30°C                                                  |

|                    |                          | 0.70    | 1       | 1.30        | S     | $V_{DD} = 2.7 \text{V to } 3.6 \text{V}$<br>$T_A = 0^{\circ}\text{C to } 70^{\circ}\text{C}$       |

|                    |                          | 0.50    | 1       | 1.50        | S     | $V_{DD} = 2.7 \text{V to } 3.6 \text{V}$<br>$T_A = -40 ^{\circ}\text{C to } +105 ^{\circ}\text{C}$ |

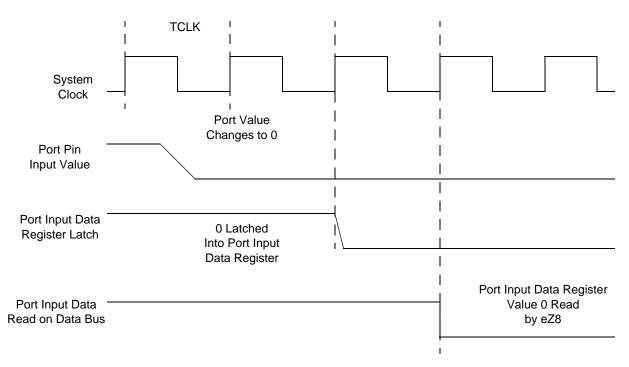

available to the eZ8 CPU on the second rising clock edge following the change of the port value.

Figure 29. Port Input Sample Timing

**Table 130. GPIO Port Input Timing**

|                     |                                                                                                    | Delay (ns) |         |  |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |  |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (Not pictured)                            | 5          | _       |  |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (Not pictured)                             | 0          | _       |  |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO Port Pins enabled as SMR sources) | 1 μs       |         |  |  |

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

|                                   |               |           |            |                        |                     |                | (                   |  |

|-----------------------------------|---------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|

| Part Number                       | Flash<br>RAM  | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |

| Z8 Encore! XP F0823               | Series with   | 4 KB FI   | lash       |                        |                     |                |                     |  |

| Standard Temperature: 0°C to 70°C |               |           |            |                        |                     |                |                     |  |

| Z8F0413PB005SG                    | 4 KB 1 K      | B 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |

| Z8F0413QB005SG                    | 4 KB 1 K      | B 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |

| Z8F0413SB005SG                    | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |

| Z8F0413SH005SG                    | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |

| Z8F0413HH005SG                    | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |

| Z8F0413PH005SG                    | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |

| Z8F0413SJ005SG                    | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |

| Z8F0413HJ005SG                    | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |

| Z8F0413PJ005SG                    | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |

| Extended Temperatu                | ıre: –40°C to | 105°C     |            |                        |                     |                |                     |  |

| Z8F0413PB005EG                    | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |

| Z8F0413QB005EG                    | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |

| Z8F0413SB005EG                    | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |

| Z8F0413SH005EG                    | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |

| Z8F0413HH005EG                    | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |

| Z8F0413PH005EG                    | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |

| Z8F0413SJ005EG                    | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |

| Z8F0413HJ005EG                    | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |

| Z8F0413PJ005EG                    | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |

| LD 180                           | Interrupt Controller 54                               |

|----------------------------------|-------------------------------------------------------|

| LDC 180                          | interrupt controller                                  |

| LDCI 179, 180                    | architecture 54                                       |

| LDE 180                          | interrupt assertion types 57                          |

| LDEI 179                         | interrupt vectors and priority 57                     |

| LDX 180                          | operation 56                                          |

| LEA 180                          | register definitions 59                               |

| load 180                         | software interrupt assertion 58                       |

| logical 181                      | interrupt edge select register 66                     |

| MULT 179                         | interrupt request 0 register 59                       |

| NOP 180                          | interrupt request 1 register 60                       |

| OR 181                           | interrupt request 2 register 61                       |

| ORX 181                          | interrupt return 181                                  |

| POP 180                          | interrupt vector listing 54                           |

| POPX 180                         | interrupts                                            |

| program control 181              | UART 105                                              |

| PUSH 180                         | IR 176                                                |

| PUSHX 180                        | Ir 176                                                |

| RCF 179, 180                     | IrDA                                                  |

| RET 181                          | architecture 117                                      |

| RL 181                           | block diagram 117                                     |

| RLC 181                          | control register definitions 120                      |

| rotate and shift 181             | operation 117                                         |

| RR 182                           | receiving data 119                                    |

| RRC 182                          | transmitting data 118                                 |

| SBC 179                          | IRET 181                                              |

| SCF 179, 180                     | IRQ0 enable high and low bit registers 61             |

| SRA 182                          | IRQ1 enable high and low bit registers 63             |

| SRL 182                          | IRQ2 enable high and low bit registers 65             |

| SRP 180                          | IRR 176                                               |

| STOP 180                         | Irr 176                                               |

| SUB 179                          |                                                       |

| SUBX 179                         |                                                       |

| SWAP 182                         | J                                                     |

| TCM 179                          | JP 181                                                |

| TCMX 179                         | jump, conditional, relative, and relative conditional |

| TM 179                           | 181                                                   |

| TMX 179                          |                                                       |

| TRAP 181                         |                                                       |

| Watchdog Timer refresh 180       | L                                                     |

| XOR 181                          | LD 180                                                |

| XORX 181                         | LDC 180                                               |

| instructions, eZ8 classes of 178 | LDCI 179, 180                                         |

| interrupt control register 68    | LDE 180                                               |

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <a href="http://zilog.com/forum">http://zilog.com/forum</a>. <a href="http://zilog.com/forum">zilog.com/forum</a>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <a href="http://www.zilog.com">http://www.zilog.com</a>.

PS024315-1011 PRELIMINARY Customer Support