Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213ph005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ilog Embedded in Life An IXYS Company 17

| Address (Hex)    | Register Description      | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------|----------|-------------|-------------|

| Timer 1 (cont'd) |                           |          |             |             |

| F0A              | Timer 1 Reload High Byte  | T1RH     | FF          | <u>85</u>   |

| F0B              | Timer 1 Reload Low Byte   | T1RL     | FF          | <u>85</u>   |

| F0C              | Timer 1 PWM High Byte     | T1PWMH   | 00          | <u>86</u>   |

| F0D              | Timer 1 PWM Low Byte      | T1PWML   | 00          | <u>86</u>   |

| F0E              | Timer 1 Control 0         | T1CTL0   | 00          | <u>87</u>   |

| F0F              | Timer 1 Control 1         | T1CTL1   | 00          | <u>84</u>   |

| F10–F3F          | Reserved                  | —        | XX          |             |

| UART             |                           |          |             |             |

| F40              | UART0 Transmit Data       | U0TXD    | XX          | <u>109</u>  |

|                  | UART0 Receive Data        | U0RXD    | XX          | <u>109</u>  |

| F41              | UART0 Status 0            | U0STAT0  | 0000011Xb   | <u>110</u>  |

| F42              | UART0 Control 0           | U0CTL0   | 00          | <u>112</u>  |

| F43              | UART0 Control 1           | U0CTL1   | 00          | <u>112</u>  |

| F44              | UART0 Status 1            | U0STAT1  | 00          | <u>111</u>  |

| F45              | UART0 Address Compare     | U0ADDR   | 00          | <u>115</u>  |

| F46              | UART0 Baud Rate High Byte | U0BRH    | FF          | <u>115</u>  |

| F47              | UART0 Baud Rate Low Byte  | U0BRL    | FF          | <u>115</u>  |

| F48–F6F          | Reserved                  | —        | XX          |             |

| Analog-to-Digita | al Converter (ADC)        |          |             |             |

| F70              | ADC Control 0             | ADCCTL0  | 00          | <u>127</u>  |

| F71              | ADC Control 1             | ADCCTL1  | 80          | <u>127</u>  |

| F72              | ADC Data High Byte        | ADCD_H   | XX          | <u>130</u>  |

| F73              | ADC Data Low Bits         | ADCD_L   | XX          | <u>130</u>  |

| F74–F7F          | Reserved                  | —        | XX          |             |

| Low Power Con    | trol                      |          |             |             |

| F80              | Power Control 0           | PWRCTL0  | 80          | <u>32</u>   |

| F81              | Reserved                  | _        | XX          |             |

| LED Controller   |                           |          |             |             |

| F82              | LED Drive Enable          | LEDEN    | 00          | <u>51</u>   |

| F83              | LED Drive Level High Byte | LEDLVLH  | 00          | <u>52</u>   |

| Note: XX=Undefi  |                           |          |             |             |

### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

#### ilog° Embedded in Life An∎IXYS Company

#### 29

| Bit        | Description (Continued)                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>EXT | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset<br>or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register |

|            | resets this bit. For POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                               |

| [3:0]      | Reserved                                                                                                                                                                                                                    |

These bits are reserved and must be programmed to 0000 when read.

#### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

Embedded in Life An TXYS Company

| Port                     | Pin        | Mnemonic                      | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------------------------|------------|-------------------------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1</sup>      | PA0        | T0IN/T0OUT                    | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|                          |            | Reserved                      |                                         | -                                       |

|                          | PA1        | T0OUT                         | Timer 0 Output                          | -                                       |

|                          |            | Reserved                      |                                         | -                                       |

|                          | PA2        | DE0                           | UART 0 Driver Enable                    | -                                       |

| PA3<br>PA4<br>PA5<br>PA6 |            | Reserved                      |                                         | _                                       |

|                          | CTS0       | UART 0 Clear to Send          | _                                       |                                         |

|                          |            | Reserved                      |                                         | _                                       |

|                          | PA4        | RXD0/IRRX0                    | UART 0 / IrDA 0 Receive Data            | _                                       |

|                          |            | Reserved                      |                                         | _                                       |

|                          | TXD0/IRTX0 | UART 0 / IrDA 0 Transmit Data | _                                       |                                         |

|                          | Reserved   |                               | _                                       |                                         |

|                          | PA6        | T1IN/T1OUT <sup>2</sup>       | Timer 1 Input/Timer 1 Output Complement | _                                       |

|                          |            | Reserved                      |                                         | _                                       |

|                          | PA7        | T1OUT                         | Timer 1 Output                          | _                                       |

|                          |            | Reserved                      |                                         | _                                       |

#### Table 17. Port Alternate Function Mapping (Non 8-Pin Parts)

Notes:

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in the <u>Port A–C Alternate Function</u> <u>Subregisters</u> section on page 43 automatically enables the associated alternate function.

2. Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in the <u>Timer Pin Signal Operation</u> section on page 83.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, alternate function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

4. V<sub>REF</sub> is available on PB5 in 28-pin products only.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

6. V<sub>REF</sub> is available on PC2 in 20-pin parts only.

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### Port A–C Alternate Function Set 1 Subregisters

The Port A–C Alternate Function Set1 Subregister (Table 28) is accessed through the Port A–C Control Register by writing 07H to the Port A–C Address Register. The Alternate Function Set 1 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in "GPIO Alternate Functions" on page 34.

**Note:** Alternate function selection on port pins must also be enabled as described in the <u>Port A</u>–<u>C Alternate Function Subregisters</u> section on page 43.

| Bit     | 7         | 6                                                                  | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------------------------------------------------------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | PAFS17    | PAFS16                                                             | PAFS15      | PAFS14        | PAFS13       | PAFS12       | PAFS11       | PAFS10   |

| RESET   |           | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |             |               |              |              |              |          |

| R/W     | R/W       | R/W                                                                | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | If 07H ir | n Port A–C A                                                       | Address Reg | jister, acces | sible throug | h the Port A | -C Control F | Register |

#### Table 28. Port A–C Alternate Function Set 1 Subregisters (PAFS1x)

#### Bit Description

#### [7:0] Port Alternate Function Set to 1

PAFS1x 0 = Port Alternate Function selected as defined in Table 15 (see the <u>GPIO Alternate Functions</u> section on page 34).

1 = Port Alternate Function selected as defined in Table 15 (see the <u>GPIO Alternate Functions</u> section on page 34).

Note: x indicates the specific GPIO port pin number (7–0).

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

| -        | 0004H                               | Watchdog Timer (see the Watchdog Timer section on page 91)                 |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          | 0036H                               | Port C Pin 0, both input edges                                             |

| Lowest   | 0038H                               | Reserved                                                                   |

#### Table 35. Trap and Interrupt Vectors in Order of Priority

# Embedded in Life

63

| Bit           | Description (Continued)                                           |

|---------------|-------------------------------------------------------------------|

| [5]<br>T0ENL  | Timer 0 Interrupt Request Enable Low Bit                          |

| [4]<br>U0RENL | UART 0 Receive Interrupt Request Enable Low Bit                   |

| [3]<br>U0TENL | UART 0 Transmit Interrupt Request Enable Low Bit                  |

| [2:1]         | Reserved<br>These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                              |

# **IRQ1 Enable High and Low Bit Registers**

Table 42 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 43 and Table 44) form a priority-encoded enabling for interrupts in the Interrupt Request 1 Register. Priority is generated by setting bits in each register.

| IRQ1ENL[ <i>x</i> ] | Priority                            | Description               |

|---------------------|-------------------------------------|---------------------------|

| 0                   | Disabled                            | Disabled                  |

| 1                   | Level 1                             | Low                       |

| 0                   | Level 2                             | Nominal                   |

| 1                   | Level 3                             | High                      |

|                     | IRQ1ENL[x]<br>0<br>1<br>0<br>1<br>1 | 0Disabled1Level 10Level 2 |

Table 42. IRQ1 Enable and Priority Encoding

# **Timers**

Z8 Encore! XP F0823 Series products contain up to two 16-bit reloadable timers that are used for timing, event counting or generation of PWM signals. The timers' features include:

- 16-bit reload counter

- Programmable prescaler with prescale values from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating, or capture signal; external input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

In addition to the timers described in this chapter, the baud rate generator of the UART (if unused) also provides basic timing functionality. For information about using the baud rate generator as an additional timer, see the <u>Universal Asynchronous Receiver/Transmitter</u> chapter on page 97.

# Embedded in Life

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a PWM output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps to configure a timer for PWM Single Output mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H); this write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

# Embedded in Life

two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

Table 57. Timer 0–1 Control Register 0 (TxCTL0)

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 5                                                                                                                                                                                                                                                                                                                                                 | 57. Timer 0- | -1 Control R | egister 0 ( | TxCTL0) |     |        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|-------------|---------|-----|--------|

| Bit               | 7                                                                                                                                                                                                                                                                                                                                                                                                                        | 6                                                                                                                                                                                                                                                                                                                                                       | 5            | 4            | 3           | 2       | 1   | 0      |

| Field             | TMODEHI                                                                                                                                                                                                                                                                                                                                                                                                                  | TICO                                                                                                                                                                                                                                                                                                                                                    | NFIG         | Reserved     |             | PWMD    |     | INPCAP |

| RESET             | 0                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                       | 0            | 0            | 0           | 0       | 0   | 0      |

| R/W               | R/W                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W                                                                                                                                                                                                                                                                                                                                                     | R/W          | R/W          | R/W         | R/W     | R/W | R/W    |

| Address           |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                         |              | F06H,        | F0EH        | ·       |     |        |

| Bit               | Descript                                                                                                                                                                                                                                                                                                                                                                                                                 | tion                                                                                                                                                                                                                                                                                                                                                    |              |              |             |         |     |        |

| [7]<br>TMODEHI    | This bit a                                                                                                                                                                                                                                                                                                                                                                                                               | <b>Timer Mode High Bit</b><br>This bit along with the TMODE field in TxCTL1 Register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value.                                                                                                                                                    |              |              |             |         |     |        |

| [6:5]<br>TICONFIG | 6 This field<br>0x = Tim<br>10 = Tim                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined reload, compare and input events.</li> <li>10 = Timer Interrupt only on defined input capture/deassertion events.</li> <li>11 = Timer Interrupt only on defined reload/compare events.</li> </ul> |              |              |             |         |     |        |

| [4]               | <b>Reserve</b><br>This bit is                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                         | and must be  | programme    | d to 0.     |         |     |        |

| [3:1]<br>PWMD     | <b>PWMD—PWM Delay value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>110 = 64 cycles delay.<br>111 = 128 cycles delay. |                                                                                                                                                                                                                                                                                                                                                         |              |              |             |         |     |        |

| [0]<br>INPCAP     | This bit i<br>0 = Previ                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>Input Capture Event</li> <li>This bit indicates if the most recent timer interrupt is caused by a Timer Input capture event.</li> <li>0 = Previous timer interrupt is not a result of Timer Input capture event.</li> <li>1 = Previous timer interrupt is a result of Timer Input capture event.</li> </ul>                                    |              |              |             |         |     |        |

## Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

ilog<sup>°</sup> Embedded in Life An∎IXYS Company 95

#### Table 61. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit       | 7           | 6             | 5            | 4              | 3             | 2             | 1         | 0    |

|-----------|-------------|---------------|--------------|----------------|---------------|---------------|-----------|------|

| Field     |             | WDTU          |              |                |               |               |           |      |

| RESET     | 00H         |               |              |                |               |               |           |      |

| R/W       | R/W*        | R/W*          | R/W*         | R/W*           | R/W*          | R/W*          | R/W*      | R/W* |

| Address   | FF1H        |               |              |                |               |               |           |      |

| Note: R/W | *—Read retu | rns the curre | nt WDT count | t value. Write | sets the appr | opriate Reloa | id Value. |      |

|           |             |               |              |                |               |               |           |      |

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

#### Table 62. Watchdog Timer Reload High Byte Register (WDTH)

| Bit       | 7                                                                                           | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-----------|---------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| Field     | WDTH                                                                                        |      |      |      |      |      |      |      |  |  |

| RESET     | 04H                                                                                         |      |      |      |      |      |      |      |  |  |

| R/W       | R/W*                                                                                        | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |

| Address   | FF2H                                                                                        |      |      |      |      |      |      |      |  |  |

| Note: R/W | te: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |  |  |

| Bit   | Description                                              |

|-------|----------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                     |

| WDTH  | Middle byte, Bits[15:8], of the 24-bit WDT reload value. |

#### Table 63. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit       | 7           | 6             | 5                                                                                             | 4    | 3    | 2    | 1    | 0    |  |  |  |

|-----------|-------------|---------------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|--|--|--|

| Field     | WDTL        |               |                                                                                               |      |      |      |      |      |  |  |  |

| RESET     | 00H         |               |                                                                                               |      |      |      |      |      |  |  |  |

| R/W       | R/W*        | R/W*          | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |  |

| Address   | FF3H        |               |                                                                                               |      |      |      |      |      |  |  |  |

| Note: R/W | *—Read retu | rns the curre | Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |  |  |  |

| Bit   | Description                                                              |

|-------|--------------------------------------------------------------------------|

| [7:0] | WDT Reload Low                                                           |

| WDTL  | Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value. |

00

105

scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

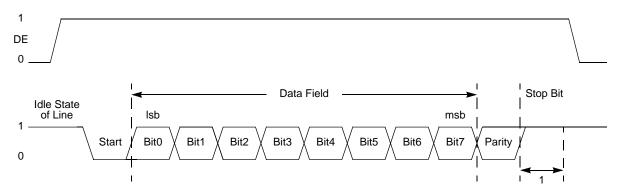

## **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data Register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

Figure 14. UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity)

The Driver Enable to Start bit setup time is calculated as follows:

## **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### ilog Embedded in Life An∎IXYS Company 110

# **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 66 and Table 67) identify the current UART operating configuration and status.

| Bit         | 7                                                                                                                                                                                                                                                                         | 6                          | 5                                         | 4           | 3                                          | 2           | 1            | 0        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------|-------------|--------------------------------------------|-------------|--------------|----------|

| Field       | RDA                                                                                                                                                                                                                                                                       | PE                         | OE                                        | FE          | BRKD                                       | TDRE        | TXE          | CTS      |

| RESET       | 0                                                                                                                                                                                                                                                                         | 0                          | 0                                         | 0           | 0                                          | 1           | 1            | Х        |

| R/W         | R                                                                                                                                                                                                                                                                         | R                          | R                                         | R           | R                                          | R           | R            | R        |

| Address     |                                                                                                                                                                                                                                                                           |                            |                                           | F4          | 1H                                         |             |              |          |

| Bit         | Descriptio                                                                                                                                                                                                                                                                | n                          |                                           |             |                                            |             |              |          |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA                                                                                                                                                                                                                                 | ita Register<br>RT Receive | he UART Re<br>clears this b<br>Data Regis |             |                                            | received da | ata. Reading | the UART |

| [6]<br>PE   | register clea<br>0 = No parit                                                                                                                                                                                                                                             | cates that a               | occurred.                                 | has occurre | d. Reading t                               | the UART R  | eceive Data  |          |

| [5]<br>OE   | received an<br>reading the<br>0 = No over                                                                                                                                                                                                                                 | cates that a<br>d the UART | Receive Da<br>eive Data Re<br>curred.     |             | urred. An ov<br>has not bee<br>s this bit. |             |              |          |

| [4]<br>FE   | Framing Error<br>This bit indicates that a framing error (no Stop bit following data reception) was detected.<br>Reading the UART Receive Data Register clears this bit.<br>0 = No framing error occurred.<br>1 = A framing error occurred.                               |                            |                                           |             |                                            |             |              |          |

| [3]<br>BRKD | <b>Break Detect</b><br>This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data Register clears this bit.<br>0 = No break occurred.<br>1 = A break occurred. |                            |                                           |             |                                            |             |              |          |

ILO O hbedded in Life IXYS Company

120

The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the endec clock counter is reset, resynchronizing the endec to the incoming signal, allowing the endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART control registers as defined in the <u>Universal Asynchronous Receiver/Transmitter</u> chapter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the endec before enabling the GPIO port alternate function for the corresponding pin.

#### ilog<sup>\*</sup> Embedded in Life An∎IXYS Company 154

# **Serialization Data**

#### Table 96. Serial Number at 001C–001F (S\_NUM)

| Bit       | 7                                 | 6            | 5              | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-----------------------------------|--------------|----------------|-----|-----|-----|-----|-----|--|--|

| Field     | S_NUM                             |              |                |     |     |     |     |     |  |  |

| RESET     | U                                 | U            | U              | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                               | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |  |

| Address   | Information Page Memory 001C–001F |              |                |     |     |     |     |     |  |  |

| Note: U = | Unchanged b                       | y Reset. R/W | / = Read/Write | е.  |     |     |     |     |  |  |

# Bit Description [7:0] Serial Number Byte S\_NUM The serial number is a unique four-byte binary value; see Table 97.

#### **Table 97. Serialization Data Locations**

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

# **Randomized Lot Identifier**

#### Table 98. Lot Identification Number (RAND\_LOT)

| Bit       | 7                                               | 6            | 5              | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|--------------|----------------|-----|-----|-----|-----|-----|--|--|

| Field     | RAND_LOT                                        |              |                |     |     |     |     |     |  |  |

| RESET     | U                                               | U            | U              | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                                             | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |  |

| Address   | Interspersed throughout Information Page Memory |              |                |     |     |     |     |     |  |  |

| Note: U = | Unchanged b                                     | y Reset. R/M | / = Read/Write | ə.  |     |     |     |     |  |  |

| Bit             | Description                                                                                                                        |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>RAND_LOT | <b>Randomized Lot ID</b><br>The randomized lot ID is a 32-byte binary value that changes for each production lot; see<br>Table 99. |

ilog° Embedded in Life An∎IXYS Company

189

| Assembly      |                                            | Address<br><u>Mode</u> Opcode(s) _ |     | Flags |   |   |   |   | Fetch Instr. |   |        |   |

|---------------|--------------------------------------------|------------------------------------|-----|-------|---|---|---|---|--------------|---|--------|---|

| Mnemonic      | Symbolic Operation                         | dst                                | src | (Hex) |   | Ζ | S | ۷ | D            | Н | Cycles |   |

| SBC dst, src  | $dst \gets dst - src - C$                  | r                                  | r   | 32    | * | * | * | * | 1            | * | 2      | 3 |

|               |                                            | r                                  | lr  | 33    | - |   |   |   |              |   | 2      | 4 |

|               | -                                          | R                                  | R   | 34    | - |   |   |   |              |   | 3      | 3 |

|               | -                                          | R                                  | IR  | 35    | - |   |   |   |              |   | 3      | 4 |

|               |                                            | R                                  | IM  | 36    | _ |   |   |   |              |   | 3      | 3 |

|               | -                                          | IR                                 | IM  | 37    | - |   |   |   |              |   | 3      | 4 |

| SBCX dst, src | $dst \gets dst - src - C$                  | ER                                 | ER  | 38    | * | * | * | * | 1            | * | 4      | 3 |

|               | -                                          | ER                                 | IM  | 39    | - |   |   |   |              |   | 4      | 3 |

| SCF           | C ← 1                                      |                                    |     | DF    | 1 | _ | _ | - | _            | - | 1      | 2 |

| SRA dst       | **                                         | R                                  |     | D0    | * | * | * | 0 | _            | - | 2      | 2 |

|               | D7_D6_D5_D4_D3_D2_D1_D0 ► C<br>dst         | IR                                 |     | D1    | - |   |   |   |              |   | 2      | 3 |

| SRL dst       | 0 - <b>▶</b> D7 D6 D5 D4 D3 D2 D1 D0 - ▶ C | R                                  |     | 1F C0 | * | * | 0 | * | _            | _ | 3      | 2 |

|               | dst                                        | IR                                 |     | 1F C1 | - |   |   |   |              |   | 3      | 3 |

| SRP src       | $RP \leftarrow src$                        |                                    | IM  | 01    | _ | _ | _ | _ | _            | _ | 2      | 2 |

| STOP          | STOP Mode                                  |                                    |     | 6F    | - | - | _ | - | _            | _ | 1      | 2 |

| SUB dst, src  | $dst \leftarrow dst - src$                 | r                                  | r   | 22    | * | * | * | * | 1            | * | 2      | 3 |

|               | -                                          | r                                  | lr  | 23    | - |   |   |   |              |   | 2      | 4 |

|               | -                                          | R                                  | R   | 24    | - |   |   |   |              |   | 3      | 3 |

|               |                                            | R                                  | IR  | 25    | - |   |   |   |              |   | 3      | 4 |

|               |                                            | R                                  | IM  | 26    | - |   |   |   |              |   | 3      | 3 |

|               |                                            | IR                                 | IM  | 27    | - |   |   |   |              |   | 3      | 4 |

| SUBX dst, src | $dst \leftarrow dst - src$                 | ER                                 | ER  | 28    | * | * | * | * | 1            | * | 4      | 3 |

|               |                                            | ER                                 | IM  | 29    | - |   |   |   |              |   | 4      | 3 |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$        | R                                  |     | F0    | Х | * | * | Х | -            | _ | 2      | 2 |

|               | -                                          | IR                                 |     | F1    | - |   |   |   |              |   | 2      | 3 |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

| Abbreviation | Description                             | Abbreviation                                   | Description            |

|--------------|-----------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                            | IRR                                            | Indirect Register Pair |

| СС           | Condition code                          | р                                              | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displace-<br>ment | r                                              | 4-bit Working Register |

| DA           | Destination address                     | R                                              | 8-bit register         |

| ER           | Extended Addressing register            | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                    | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| lr           | Indirect Working Register               | RA                                             | Relative               |

| IR           | Indirect register                       | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair          | RR                                             | Register Pair          |

#### Table 119. Opcode Map Abbreviations

#### ILOG<sup>°</sup> Inbedded in Life IXYS Company **210**

# Packaging

Zilog's F0823 Series of MCUs includes the Z8F0113, Z8F0123, Z8F0213, Z8F0223, Z8F0413, Z8F0423, Z8F0813 and Z8F0823 devices, which are available in the following packages:

- 8-pin Plastic Dual Inline Package (PDIP)

- 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S<sup>1</sup>

- 20-pin Plastic Dual-Inline Package (PDIP)

- 20-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Small Shrink Outline Package (SSOP)

- 28-pin Plastic Dual-Inline Package (PDIP)

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Small Shrink Outline Package (SSOP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

<sup>1.</sup> The footprint of the QFN)/MLF-S package is identical to that of the 8-pin SOIC package, but with a lower profile.

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

> ilog Embedded in Life An IXYS Company 215

|                                                                                |              |           |            |                        |                     | U              | · · · ·             |

|--------------------------------------------------------------------------------|--------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                                                                    | Flash<br>RAM | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 Series with 2 KB Flash, 10-Bit Analog-to-Digital Converter |              |           |            |                        |                     |                |                     |

| Standard Temperature: 0°C to 70°C                                              |              |           |            |                        |                     |                |                     |

| Z8F0223PB005SG                                                                 | 2 KB 512     | B 6       | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005SG                                                                 | 2 KB 512     | B 6       | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005SG                                                                 | 2 KB 512     | B 6       | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005SG                                                                 | 2 KB 512     | B 16      | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005SG                                                                 | 2 KB 512     | B 16      | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005SG                                                                 | 2 KB 512     | B 16      | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005SG                                                                 | 2 KB 512     | B 22      | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005SG                                                                 | 2 KB 512     | B 22      | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005SG                                                                 | 2 KB 512     | B 22      | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: –40°C to 105°C                                           |              |           |            |                        |                     |                |                     |

| Z8F0223PB005EG                                                                 | 2 KB 512     | B 6       | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005EG                                                                 | 2 KB 512     | B 6       | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005EG                                                                 | 2 KB 512     | B 6       | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005EG                                                                 | 2 KB 512     | B 16      | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005EG                                                                 | 2 KB 512     | B 16      | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005EG                                                                 | 2 KB 512     | B 16      | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005EG                                                                 | 2 KB 512     | B 22      | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005EG                                                                 | 2 KB 512     | B 22      | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005EG                                                                 | 2 KB 512     | B 22      | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

230

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.