Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213qb005eg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ilog<sup>®</sup>

ii

#### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2011 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

#### ilog<sup>°</sup> Embedded in Life An ∎IXYS Company

5

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

# **10-Bit Analog-to-Digital Converter**

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

# **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

## Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

# **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

# **Reset Controller**

Z8 Encore!  $XP^{\text{(B)}}$  F0823 Series products can be reset using the RESET pin, POR, WDT time-out, STOP Mode exit, or Voltage Brown-Out warning signal. The RESET pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

8

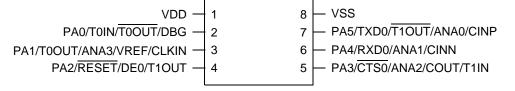

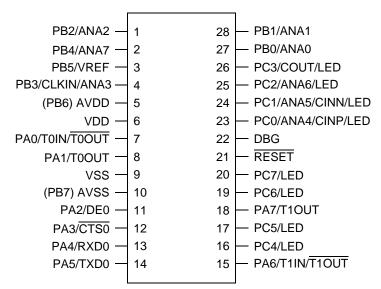

Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

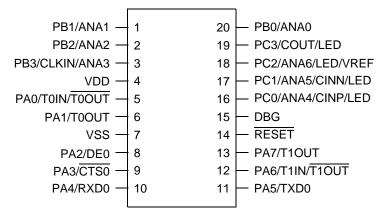

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

nbedded in Life

13

# Address Space

The eZ8 CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O Port Control Registers

- The Program Memory contains addresses for all memory locations having executable code and/or data

- The Data Memory contains addresses for all memory locations that contain data only

These three address spaces are covered briefly in the following subsections. For more detailed information regarding the eZ8 CPU and its address space, refer to the <u>eZ8 CPU</u> <u>Core User Manual (UM0128)</u>, available for download at <u>www.zilog.com</u>.

# **Register File**

The Register File address space in the Z8 Encore! XP<sup>™</sup> MCU is 4KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. Z8 Encore! XP F0823 Series devices contain 256B–1KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

# **Program Memory**

The eZ8 CPU supports 64KB of Program Memory address space. F0823 Series devices contain 1KB to 8KB of on-chip Flash memory in the Program Memory address space. Reading from Program Memory addresses outside the available Flash memory addresses

#### ilog° Embedded in Life An∎IXYS Company

#### 29

| Bit        | Description (Continued)                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>EXT | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset<br>or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register |

|            | resets this bit. For POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                               |

| [3:0]      | Reserved                                                                                                                                                                                                                    |

These bits are reserved and must be programmed to 0000 when read.

#### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

# Embedded in Life

# **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) register (Table 49) determines the source of the PADxS interrupts. The Shared Interrupt Select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit     | 7        | 6     | 5        | 4   | 3   | 2   | 1   | 0   |

|---------|----------|-------|----------|-----|-----|-----|-----|-----|

| Field   | Reserved | PA6CS | Reserved |     |     |     |     |     |

| RESET   | 0        | 0     | 0        | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W      | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |

| Address |          | FCEH  |          |     |     |     |     |     |

#### Table 49. Shared Interrupt Select Register (IRQSS)

| Bit          | Description                                                                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]          | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                   |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The comparator is used as an interrupt for PA6CS interrupt requests.</li> </ul> |

| [5:0]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                           |

# Embedded in Life An IXYS Company 97

# Universal Asynchronous Receiver/ Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. The features of UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) Mode with three configurable interrupt schemes

- BRG can be configured and used as a basic 16-bit timer

- Driver Enable output for external bus transceivers

# Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

nbedded in Life

100

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled,.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

### Transmitting Data Using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

nbedded in Life

102

# **Receiving Data Using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Observe the following steps to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR Mode

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

#### **Baud Rate Generator Interrupts**

If the Baud Rate Generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Observe the following steps to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) × BRG[15:0]

# **UART Control Register Definitions**

The UART control registers support the UART and the associated infrared encoder/decoders. For more information about the infrared operation, see the <u>Infrared Encoder/Decoder</u> chapter on page 117.

#### ilog<sup>\*</sup> Embedded in Life An∎IXYS Company 154

# **Serialization Data**

#### Table 96. Serial Number at 001C–001F (S\_NUM)

| Bit       | 7                                               | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------------------------|-------|-----|-----|-----|-----|-----|-----|

| Field     |                                                 | S_NUM |     |     |     |     |     |     |

| RESET     | U                                               | U     | U   | U   | U   | U   | U   | U   |

| R/W       | R/W                                             | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Address   | Information Page Memory 001C–001F               |       |     |     |     |     |     |     |

| Note: U = | lote: U = Unchanged by Reset. R/W = Read/Write. |       |     |     |     |     |     |     |

# Bit Description [7:0] Serial Number Byte S\_NUM The serial number is a unique four-byte binary value; see Table 97.

#### **Table 97. Serialization Data Locations**

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

# **Randomized Lot Identifier**

#### Table 98. Lot Identification Number (RAND\_LOT)

| Bit       | 7                                                 | 6        | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|---------------------------------------------------|----------|-----|-----|-----|-----|-----|-----|

| Field     |                                                   | RAND_LOT |     |     |     |     |     |     |

| RESET     | U                                                 | U        | U   | U   | U   | U   | U   | U   |

| R/W       | R/W                                               | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |

| Address   | s Interspersed throughout Information Page Memory |          |     |     |     |     |     |     |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write.   |          |     |     |     |     |     |     |

| Bit      | Description                                                                                         |

|----------|-----------------------------------------------------------------------------------------------------|

| [7]      | Randomized Lot ID                                                                                   |

| RAND_LOT | The randomized lot ID is a 32-byte binary value that changes for each production lot; see Table 99. |

ILOG abedded in Life

169

# **Oscillator Control**

Z8 Encore! XP F0823 Series devices uses three possible clocking schemes, each userselectable. These three schemes are:

- On-chip precision trimmed RC oscillator

- External clock drive

- On-chip low power Watchdog Timer oscillator

In addition, F0823 Series devices contain clock failure detection and recovery circuitry, which allow continued operation despite a failure of the primary oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document.

# **System Clock Selection**

The oscillator control block selects from the available clocks. Table 104 details each clock source and its usage.

| Clock Source                          | Characteristics                                                                                                                | Required Setup                                                                                                                                                                                                  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8kHz or 5.53MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>            | <ul> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator at either 5.53MHz or<br/>32.8kHz</li> </ul>                                                              |

| External Clock<br>Drive               | <ul> <li>0 to 20MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul> |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Very Low power consumption</li> </ul> | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>            |

Table 104. Oscillator Configuration and Selection

177

#### Table 108. Notational Shorthand (Continued)

| Notation | Description           | Operand | Range                                                                                                                     |

|----------|-----------------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| RA       | Relative Address      | Х       | X represents an index in the range of $+127$ to $-128$ which is an offset relative to the address of the next instruction |

| rr       | Working Register Pair | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                         |

| RR       | Register Pair         | Reg     | Reg. represents an even number in the range of 00H to FEH.                                                                |

| Vector   | Vector Address        | Vector  | Vector represents a number in the range of 00H to FFH.                                                                    |

| X        | Indexed               | #Index  | The register or register pair to be indexed is offset<br>by the signed Index value (#Index) in a +127 to<br>-128 range.   |

Table 109 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol             | Definition                |

|--------------------|---------------------------|

| dst                | Destination Operand       |

| src Source Operand |                           |

| @                  | Indirect Address Prefix   |

| SP                 | Stack Pointer             |

| PC                 | Program Counter           |

| FLAGS              | Flags Register            |

| RP                 | Register Pointer          |

| #                  | Immediate Operand Prefix  |

| В                  | Binary Number Suffix      |

| %                  | Hexadecimal Number Prefix |

| Н                  | Hexadecimal Number Suffix |

#### Table 109. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.

$dst \leftarrow dst + src$

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

ilog° Embedded in Life An∎IXYS Company

190

| Assembly      |                                                                                                                        | Address<br>Opcode(s |        |       | Flags |   |   |   |   |   | _ Fetch | Instr. |

|---------------|------------------------------------------------------------------------------------------------------------------------|---------------------|--------|-------|-------|---|---|---|---|---|---------|--------|

| Mnemonic      | Symbolic Operation                                                                                                     | dst src             |        | (Hex) | С     | Ζ | S | ۷ | D | Н | Cycles  |        |

| TCM dst, src  | (NOT dst) AND src                                                                                                      | r                   | r      | 62    | -     | * | * | 0 | - | _ | 2       | 3      |

|               |                                                                                                                        | r                   | lr     | 63    | -     |   |   |   |   |   | 2       | 4      |

|               |                                                                                                                        | R                   | R      | 64    | -     |   |   |   |   |   | 3       | 3      |

|               |                                                                                                                        | R                   | IR     | 65    | -     |   |   |   |   |   | 3       | 4      |

|               |                                                                                                                        | R                   | IM     | 66    | -     |   |   |   |   |   | 3       | 3      |

|               |                                                                                                                        | IR                  | IM     | 67    | -     |   |   |   |   |   | 3       | 4      |

| TCMX dst, src | (NOT dst) AND src                                                                                                      | ER                  | ER     | 68    | -     | * | * | 0 | - | _ | 4       | 3      |

|               |                                                                                                                        | ER                  | IM     | 69    | -     |   |   |   |   |   | 4       | 3      |

| TM dst, src   | dst AND src                                                                                                            | r                   | r      | 72    | -     | * | * | 0 | - | _ | 2       | 3      |

|               |                                                                                                                        | r                   | lr     | 73    | -     |   |   |   |   |   | 2       | 4      |

|               |                                                                                                                        | R                   | R      | 74    | -     |   |   |   |   |   | 3       | 3      |

|               |                                                                                                                        | R                   | IR     | 75    | -     |   |   |   |   |   | 3       | 4      |

|               |                                                                                                                        | R                   | IM     | 76    | -     |   |   |   |   |   | 3       | 3      |

|               |                                                                                                                        | IR                  | IM     | 77    | -     |   |   |   |   |   | 3       | 4      |

| TMX dst, src  | dst AND src                                                                                                            | ER                  | ER     | 78    | -     | * | * | 0 | _ | _ | 4       | 3      |

|               |                                                                                                                        | ER                  | IM     | 79    | -     |   |   |   |   |   | 4       | 3      |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |                     | Vector | F2    | -     | _ | - | - | - | _ | 2       | 6      |

| WDT           |                                                                                                                        |                     |        | 5F    | _     | _ | _ | _ | _ | _ | 1       | 2      |

### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

|   |                                |                                  |                                      |                              |                                |                                  | Lo                            | ower Nil                                  | bble (He                          | x)                           |                            |                          |                           |                           |                         |                          |

|---|--------------------------------|----------------------------------|--------------------------------------|------------------------------|--------------------------------|----------------------------------|-------------------------------|-------------------------------------------|-----------------------------------|------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|--------------------------|

|   | 0                              | 1                                | 2                                    | 3                            | 4                              | 5                                | 6                             | 7                                         | 8                                 | 9                            | Α                          | В                        | С                         | D                         | Е                       | F                        |

| 0 | 1.1<br>BRK                     | 2.2<br>SRP<br>IM                 | 2.3<br><b>ADD</b><br>r1,r2           | 2.4<br><b>ADD</b><br>r1,lr2  | 3.3<br><b>ADD</b><br>R2,R1     | 3.4<br><b>ADD</b><br>IR2,R1      | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM                      | 4.3<br>ADDX<br>ER2,ER1            | 4.3<br>ADDX<br>IM,ER1        | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1        | 2.3<br><b>RLC</b><br>IR1         | 2.3<br>ADC<br>r1,r2                  | 2.4<br>ADC<br>r1,lr2         | 3.3<br>ADC<br>R2,R1            | 3.4<br>ADC<br>IR2,R1             | 3.3<br>ADC<br>R1,IM           | 3.4<br>ADC<br>IR1,IM                      | 4.3<br>ADCX<br>ER2,ER1            | 4.3<br>ADCX<br>IM,ER1        |                            |                          |                           |                           |                         | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1               | 2.3<br>INC<br>IR1                | 2.3<br><b>SUB</b><br>r1,r2           | 2.4<br>SUB<br>r1,lr2         | 3.3<br><b>SUB</b><br>R2,R1     | 3.4<br>SUB<br>IR2,R1             | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br>SUB<br>IR1,IM                      | 4.3<br><b>SUBX</b><br>ER2,ER1     | 4.3<br><b>SUBX</b><br>IM,ER1 |                            |                          |                           |                           |                         | 1                        |

| 3 | 2.2<br>DEC<br>R1               | 2.3<br>DEC<br>IR1                | 2.3<br>SBC<br>r1,r2                  | 2.4<br>SBC<br>r1,lr2         | 3.3<br>SBC<br>R2,R1            | 3.4<br>SBC<br>IR2,R1             | 3.3<br>SBC<br>R1,IM           | 3.4<br>SBC<br>IR1,IM                      | 4.3<br><b>SBCX</b><br>ER2,ER1     | 4.3<br>SBCX                  |                            |                          |                           |                           |                         |                          |

| 4 | 2.2<br>DA<br>R1                | 2.3<br>DA<br>IR1                 | 2.3<br><b>OR</b>                     | 2.4<br>OR                    | 3.3<br>OR<br>R2,R1             | 3.4<br><b>OR</b>                 | 3.3<br><b>OR</b>              | 3.4<br><b>OR</b>                          | 4.3<br>ORX<br>ER2,ER1             | 4.3<br>ORX                   |                            |                          |                           |                           |                         |                          |

| 5 | 2.2<br><b>POP</b><br>R1        | 2.3<br><b>POP</b>                | r1,r2<br>2.3<br>AND                  | r1,lr2<br>2.4<br>AND         | 3.3<br>AND<br>R2,R1            | 3.4<br>AND                       | 81,IM<br>3.3<br><b>AND</b>    | 3.4<br>AND                                | 4.3<br>ANDX                       | 4.3<br>ANDX                  |                            |                          |                           |                           |                         | 1.2<br>WDT               |

| 6 | 2.2<br>COM                     | IR1<br>2.3<br>COM                | r1,r2<br>2.3<br>TCM                  | r1,lr2<br>2.4<br>TCM         | 3.3<br>TCM                     | 3.4<br>TCM                       | 81,IM<br>3.3<br><b>TCM</b>    | 3.4<br>TCM                                | 4.3<br><b>TCMX</b>                | 4.3<br><b>TCMX</b>           |                            |                          |                           |                           |                         | 1.2<br>STOP              |

| 7 | R1<br>2.2<br><b>PUSH</b><br>R2 | IR1<br>2.3<br><b>PUSH</b><br>IR2 | r1,r2<br>2.3<br><b>TM</b>            | r1,lr2<br>2.4<br><b>TM</b>   | R2,R1<br>3.3<br><b>TM</b>      | IR2,R1<br>3.4<br><b>TM</b>       | R1,IM<br>3.3<br><b>TM</b>     | IR1,IM<br>3.4<br><b>TM</b>                | ER2,ER1<br>4.3<br><b>TMX</b>      | 4.3<br><b>TMX</b>            |                            |                          |                           |                           |                         | 1.2<br>HALT              |

| 8 | 2.5<br>DECW<br>RR1             | 2.6<br>DECW<br>IRR1              | r1,r2<br>2.5<br>LDE                  | r1,lr2<br>2.9<br><b>LDEI</b> | R2,R1<br>3.2<br>LDX            | IR2,R1<br>3.3<br>LDX             | R1,IM<br>3.4<br>LDX           | IR1,IM<br>3.5<br><b>LDX</b>               | 3.4<br>LDX                        | IM,ER1<br>3.4<br>LDX         |                            |                          |                           |                           |                         | 1.2<br><b>DI</b>         |

| 9 | 2.2<br>RL<br>R1                | 2.3<br>RL<br>IR1                 | r1,Irr2<br>2.5<br>LDE                | 2.9<br>LDEI<br>Ir2,Irr1      | r1,ER2<br>3.2<br>LDX<br>r2,ER1 | Ir1,ER2<br>3.3<br>LDX<br>Ir2,ER1 | 3.4<br>LDX<br>R2,IRR1         | IRR2,IR1<br>3.5<br><b>LDX</b><br>IR2,IRR1 | r1,rr2,X<br>3.3<br>LEA<br>r1,r2,X | 3.5<br><b>LEA</b>            |                            |                          |                           |                           |                         | 1.2<br>El                |

| A | 2.5<br>INCW<br>RR1             | 2.6<br>INCW                      | r2,Irr1<br>2.3<br><b>CP</b><br>r1,r2 | 2.4<br><b>CP</b><br>r1,lr2   | 3.3<br><b>CP</b><br>R2,R1      | 3.4<br><b>CP</b><br>IR2,R1       | 3.3<br>CP<br>R1,IM            | 3.4<br>CP<br>IR1,IM                       | 4.3<br>CPX<br>ER2,ER1             | 4.3<br>CPX<br>IM,ER1         |                            |                          |                           |                           |                         | 1.4<br>RET               |

| в | 2.2<br>CLR<br>R1               | 2.3<br>CLR<br>IR1                | 2.3<br>XOR<br>r1,r2                  | 2.4<br>XOR<br>r1,lr2         | 3.3<br>XOR<br>R2,R1            | 3.4<br>XOR<br>IR2,R1             | 3.3<br>XOR<br>R1,IM           | 3.4<br>XOR<br>IR1,IM                      | 4.3<br><b>XORX</b><br>ER2,ER1     | 4.3<br><b>XORX</b><br>IM,ER1 |                            |                          |                           |                           |                         | 1.5<br>IRET              |

| С | 2.2<br>RRC<br>R1               | 2.3<br>RRC<br>IR1                | 2.5<br>LDC<br>r1,lrr2                | 2.9<br>LDCI<br>lr1,lrr2      | 2.3<br>JP<br>IRR1              | 2.9<br>LDC<br>lr1,lrr2           | IXT,IW                        | 3.4<br>LD<br>r1,r2,X                      | 3.2<br>PUSHX<br>ER2               |                              |                            |                          |                           |                           |                         | 1.2<br>RCF               |

| D | 2.2<br>SRA<br>R1               | 2.3<br>SRA<br>IR1                | 2.5<br>LDC<br>r2,Irr1                | 2.9<br>LDCI<br>lr2,lrr1      | 2.6                            | 2.2<br>BSWAP<br>R1               | 3.3<br>CALL<br>DA             | 3.4<br>LD<br>r2,r1,X                      | 3.2<br><b>POPX</b><br>ER1         |                              |                            |                          |                           |                           |                         | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1         | 2.3<br><b>RR</b><br>IR1          | 2.2<br>BIT<br>p,b,r1                 | 2.3<br>LD<br>r1,lr2          | 3.2<br>LD<br>R2,R1             | 3.3<br>LD<br>IR2,R1              | 3.2<br>LD<br>R1,IM            | 3.3<br>LD<br>IR1,IM                       | 4.2<br>LDX<br>ER2,ER1             | 4.2<br>LDX<br>IM,ER1         |                            |                          |                           |                           |                         | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1              | 2.3<br>SWAP<br>IR1               | 2.6<br>TRAP<br>Vector                | 2.3<br>LD<br>lr1,r2          | 2.8<br>MULT<br>RR1             | 3.3<br>LD<br>R2,IR1              | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X            |                                   |                              | V                          | ┥                        | V                         | ▼                         | V                       |                          |

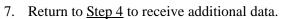

Figure 27. First Opcode Map

Figure 28. Second Opcode Map after 1FH

# Embedded in Life An IXYS Company

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                   |                        | T <sub>A</sub> = -40°C<br>(unless o | 'V to 3.6V<br>C to +105°C<br>otherwise<br>ted) |       |                                         |  |

|-------------------|------------------------|-------------------------------------|------------------------------------------------|-------|-----------------------------------------|--|

| Symbol            | Parameter              | Minimum                             | Maximum                                        | Units | Conditions                              |  |

| FSYSCLK           | System Clock Frequency | _                                   | 20.0*                                          | MHz   | Read-only from Flash memory.            |  |

|                   |                        | 0.032768                            | 20.0 <sup>1</sup>                              | MHz   | Program or erasure of the Flash memory. |  |

| T <sub>XIN</sub>  | System Clock Period    | 50                                  | -                                              | ns    | $T_{CLK} = 1/F_{SYSCLK}$ .              |  |

| T <sub>XINH</sub> | System Clock High Time | 20                                  | 30                                             | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINL</sub> | System Clock Low Time  | 20                                  | 30                                             | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINR</sub> | System Clock Rise Time | _                                   | 3                                              | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINF</sub> | System Clock Fall Time | _                                   | 3                                              | ns    | Т <sub>СІ К</sub> = 50ns.               |  |

| Table ' | 123. AC | Characteristics |

|---------|---------|-----------------|

|---------|---------|-----------------|

#### Table 124. Internal Precision Oscillator Electrical Characteristics

|                    |                                                         | $T_A = -$ | = 2.7V to<br>-40°C to +<br>otherwise |            |       |                                                 |

|--------------------|---------------------------------------------------------|-----------|--------------------------------------|------------|-------|-------------------------------------------------|

| Symbol             | Parameter                                               | Minimum   | Typical                              | Maximum    | Units | Conditions                                      |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |           | 5.53                                 |            | MHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |           | 32.7                                 |            | kHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |           | <u>+</u> 1                           | <u>+</u> 4 | %     |                                                 |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |           | 3                                    |            | μs    |                                                 |

edded in Life

An∎IXYS Company

207

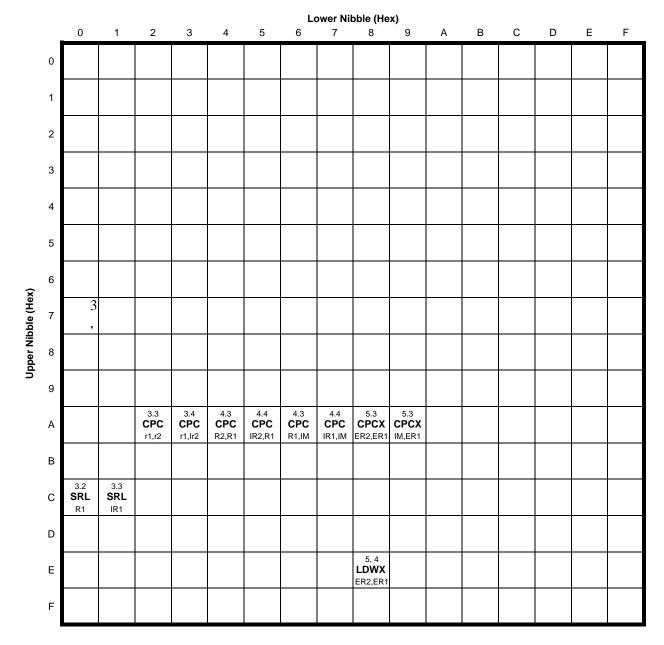

# **On-Chip Debugger Timing**

Figure 31 and Table 132 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

|                |                                              | Delay (ns) |         |  |  |  |

|----------------|----------------------------------------------|------------|---------|--|--|--|

| Parameter      | Abbreviation                                 | Minimum    | Maximum |  |  |  |

| DBG            |                                              |            |         |  |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | _          | 15      |  |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2          | -       |  |  |  |

| T <sub>3</sub> | DBG to X <sub>IN</sub> Rise Input Setup Time | 5          | _       |  |  |  |

| T <sub>4</sub> | DBG to X <sub>IN</sub> Rise Input Hold Time  | 5          | _       |  |  |  |

#### Table 132. On-Chip Debugger Timing

> ilog Embedded in Life An IXYS Company 218

| Part Number                                | sh          | Σ       | /O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |

|--------------------------------------------|-------------|---------|----------|------------|------------------------|---------------------|----------------|---------------------|--|--|

|                                            | Flash       | RAM     |          | _          | 16-<br>w/P             | 10-                 | NA             | Des                 |  |  |

| Z8 Encore! XP F0823 Series with 1 KB Flash |             |         |          |            |                        |                     |                |                     |  |  |

| Standard Temperatu                         | ire: 0°C to | o 70°C  |          |            |                        |                     |                |                     |  |  |

| Z8F0113PB005SG                             | 1 KB        | 256 B   | 6        | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0113QB005SG                             | 1 KB        | 256 B   | 6        | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |

| Z8F0113SB005SG                             | 1 KB        | 256 B   | 6        | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0113SH005SG                             | 1 KB        | 256 B   | 16       | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |

| Z8F0113HH005SG                             | 1 KB        | 256 B   | 16       | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |

| Z8F0113PH005SG                             | 1 KB        | 256 B   | 16       | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |

| Z8F0113SJ005SG                             | 1 KB        | 256 B   | 24       | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |

| Z8F0113HJ005SG                             | 1 KB        | 256 B   | 24       | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |

| Z8F0113PJ005SG                             | 1 KB        | 256 B   | 24       | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |

| Extended Temperatu                         | ure: –40°0  | C to 10 | 5°C      |            |                        |                     |                |                     |  |  |

| Z8F0113PB005EG                             | 1 KB        | 256 B   | 6        | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0113QB005EG                             | 1 KB        | 256 B   | 6        | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |

| Z8F0113SB005EG                             | 1 KB        | 256 B   | 6        | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0113SH005EG                             | 1 KB        | 256 B   | 16       | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |

| Z8F0113HH005EG                             | 1 KB        | 256 B   | 16       | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |

| Z8F0113PH005EG                             | 1 KB        | 256 B   | 16       | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |

| Z8F0113SJ005EG                             | 1 KB        | 256 B   | 24       | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |

| Z8F0113HJ005EG                             | 1 KB        | 256 B   | 24       | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |

| Z8F0113PJ005EG                             | 1 KB        | 256 B   | 24       | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |

## Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

219

ilog<sup>®</sup> Embedded in Life

An∎IXYS Company

| Part Number            | Flash | RAM    | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description             |

|------------------------|-------|--------|-----------|------------|------------------------|---------------------|----------------|-------------------------|

| Z8 Encore! XP F0823 Se | eries | Develo | pment     | t Kit      |                        |                     |                |                         |

| Z8F08A28100KITG        |       | Z8 En  | core! X   | P F08      | 2A Seri                | es Dev              | elopme         | nt Kit (20- and 28-Pin) |

| Z8F04A28100KITG        |       | Z8 En  | core! X   | P F04      | 2A Seri                | es Dev              | velopme        | nt Kit (20- and 28-Pin) |

| Z8F04A08100KITG        |       | Z8 En  | core! X   | P F04      | 2A Seri                | es Dev              | velopme        | nt Kit (8-Pin)          |

| ZUSBSC00100ZACG        |       | USB S  | Smart C   | Cable A    | Accesso                | ry Kit              |                |                         |

| ZUSBOPTSC01ZACG        |       | Opto-I | solated   | USB        | Smart (                | Cable A             | Accesso        | ry Kit                  |

| ZENETSC0100ZACG        |       | Etherr | net Sma   | art Cal    | ble Acce               | essory              | Kit            |                         |

## Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)