# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213sh005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

7

# **Pin Description**

Z8 Encore! XP F0823 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and pin configurations available for each of the package styles. For information about physical package specifications, see the Packaging chapter on page 210.

# **Available Packages**

Table 2 lists the package styles that are available for each device in the F0823 Series product line.

| Part<br>Number | ADC | 8-pin<br>PDIP | 8-pin<br>SOIC | 20-pin<br>PDIP | 20-pin<br>SOIC | 20-pin<br>SSOP | 28-pin<br>PDIP | 28-pin<br>SOIC | 28-pin<br>SSOP | 8-pin QFN/<br>MLF-S |

|----------------|-----|---------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------|

| Z8F0823        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0813        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0423        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0413        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0223        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0213        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0123        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0113        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

Table 2. F0823 Series Package Options

# **Pin Configurations**

Figures 2 through 4 display the pin configurations for all packages available in the F0823 Series. For description of signals, see Table 3. The analog input alternate functions (ANAx) are not available on the Z8F0x13 devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all pins of Ports A, B, and C default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general-purpose input ports until programmed otherwise.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

ilog<sup>®</sup> Embedded in Life An∎IXYS Company 19

| Address (Hex)    | Register Description                  | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------------------|----------|-------------|-------------|

| GPIO Port B (co  | nt'd)                                 |          |             |             |

| FD6              | Port B Input Data                     | PBIN     | XX          | <u>43</u>   |

| FD7              | Port B Output Data                    | PBOUT    | 00          | <u>43</u>   |

| GPIO Port C      |                                       |          |             |             |

| FD8              | Port C Address                        | PCADDR   | 00          | <u>40</u>   |

| FD9              | Port C Control                        | PCCTL    | 00          | <u>42</u>   |

| FDA              | Port C Input Data                     | PCIN     | XX          | <u>43</u>   |

| FDB              | Port C Output Data                    | PCOUT    | 00          | <u>43</u>   |

| FDC-FEF          | Reserved                              |          | XX          |             |

| Watchdog Time    | r (WDT)                               |          |             |             |

| FF0              | Reset Status                          | RSTSTAT  | XX          | <u>94</u>   |

|                  | Watchdog Timer Control                | WDTCTL   | XX          | <u>94</u>   |

| FF1              | Watchdog Timer Reload Upper Byte      | WDTU     | FF          | <u>95</u>   |

| FF2              | Watchdog Timer Reload High Byte       | WDTH     | FF          | <u>95</u>   |

| FF3              | Watchdog Timer Reload Low Byte        | WDTL     | FF          | <u>95</u>   |

| FF4–FF5          | Reserved                              | _        | XX          |             |

| Trim Bit Control | l                                     |          |             |             |

| FF6              | Trim Bit Address                      | TRMADR   | 00          | 148         |

| FF7              | Trim Data                             | TRMDR    | XX          | 149         |

| Flash Memory C   | Controller                            |          |             |             |

| FF8              | Flash Control                         | FCTL     | 00          | 141         |

| FF8              | Flash Status                          | FSTAT    | 00          | 142         |

| FF9              | Flash Page Select                     | FPS      | 00          | <u>143</u>  |

|                  | Flash Sector Protect                  | FPROT    | 00          | <u>144</u>  |

| FFA              | Flash Programming Frequency High Byte | FFREQH   | 00          | <u>145</u>  |

| FFB              | Flash Programming Frequency Low Byte  | FFREQL   | 00          | <u>145</u>  |

### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

Embedded in Life An TXYS Company

| Port                | Pin | Mnemonic                | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-------------------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1</sup> | PA0 | T0IN/T0OUT              | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|                     |     | Reserved                |                                         | -                                       |

|                     | PA1 | T0OUT                   | Timer 0 Output                          | -                                       |

|                     |     | Reserved                |                                         | -                                       |

|                     | PA2 | DE0                     | UART 0 Driver Enable                    | -                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA3 | CTS0                    | UART 0 Clear to Send                    | _                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA4 | RXD0/IRRX0              | UART 0 / IrDA 0 Receive Data            | _                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA5 | TXD0/IRTX0              | UART 0 / IrDA 0 Transmit Data           | _                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA6 | T1IN/T1OUT <sup>2</sup> | Timer 1 Input/Timer 1 Output Complement | _                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA7 | T1OUT                   | Timer 1 Output                          | _                                       |

|                     |     | Reserved                |                                         | _                                       |

### Table 17. Port Alternate Function Mapping (Non 8-Pin Parts)

Notes:

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in the <u>Port A–C Alternate Function</u> <u>Subregisters</u> section on page 43 automatically enables the associated alternate function.

2. Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in the <u>Timer Pin Signal Operation</u> section on page 83.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, alternate function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

4. V<sub>REF</sub> is available on PB5 in 28-pin products only.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

6. V<sub>REF</sub> is available on PC2 in 20-pin parts only.

# Embedded in Life

| Port Register   |                                   |

|-----------------|-----------------------------------|

| Mnemonic        | Port Register Name                |

| P <i>x</i> HDE  | High Drive Enable.                |

| P <i>x</i> SMRE | Stop Mode Recovery Source Enable. |

| P <i>x</i> PUE  | Pull-up Enable.                   |

| PxAFS1          | Alternate Function Set 1.         |

| PxAFS2          | Alternate Function Set 2.         |

### Table 18. GPIO Port Registers and Subregisters (Continued)

## **Port A–C Address Registers**

The Port A–C Address registers select the GPIO port functionality accessible through the Port A–C Control registers. The Port A–C Address and Control registers combine to provide access to all GPIO port controls (Table 19).

| Table 19. Port | A-C GPIO | Address R | egisters ( | (P <i>x</i> ADDR) |

|----------------|----------|-----------|------------|-------------------|

|----------------|----------|-----------|------------|-------------------|

| Bit     | 7          | 6                | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------------|------------------|-----|-----|-----|-----|-----|-----|--|

| Field   | PADDR[7:0] |                  |     |     |     |     |     |     |  |

| RESET   | 00H        |                  |     |     |     |     |     |     |  |

| R/W     | R/W        | R/W              | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |            | FD0H, FD4H, FD8H |     |     |     |     |     |     |  |

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The Port Address selects one of the subregisters accessible through the Port Control Register. |

|       | See Table 20 for each subregister function.                                                    |

### Table 20. PADDR[7:0] Subregister Functions

| PADDR[7:0] | Port Control Subregister Accessible Using the Port A–C Control Registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental Port reconfiguration. |

| 01H        | Data Direction.                                                                |

| 02H        | Alternate Function.                                                            |

| 03H        | Output Control (Open-Drain).                                                   |

| 04H        | High Drive Enable.                                                             |

### ilog Embedded in Life An IXYS Company 45

### Port A–C High Drive Enable Subregisters

The Port A–C High Drive Enable Subregister (Table 25) is accessed through the Port A–C Control Register by writing 04H to the Port A–C Address Register. Setting the bits in the Port A–C High Drive Enable subregisters to 1 configures the specified port pins for high-current output drive operation. The Port A–C High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

| Table 25. Port A–C High Drive Enable Subregiste | ers (PHDEx) |

|-------------------------------------------------|-------------|

|-------------------------------------------------|-------------|

| Bit     | 7                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| Field   | PHDE7                                                                                 | PHDE6 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |  |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address | If 04H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |       |  |

#### Bit Description

[7:0] **Port High Drive Enabled.**

PHDEx 0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

Note: x indicates the specific GPIO port pin number (7–0).

nbedded in Life

46

## Port A–C Stop Mode Recovery Source Enable Subregisters

The Port A–C Stop Mode Recovery Source Enable Subregister (Table 26) is accessed through the Port A–C Control Register by writing 05H to the Port A–C Address Register. Setting the bits in the Port A–C Stop Mode Recovery Source Enable subregisters to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

Table 26. Port A–C Stop Mode Recovery Source Enable Subregisters (PSMREx)

| Bit     | 7         | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|-----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | PSMRE7    | PSMRE6                                                                                | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |  |

| RESET   | 0         | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W       | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address | If 05H ir | If 05H in Port A–C Address Register, accessible through the Port A–C Control Register |        |        |        |        |        |        |  |  |

#### Bit Description

| [7:0] | Port Stop Mode Recovery Source Enabled. |

|-------|-----------------------------------------|

|-------|-----------------------------------------|

PSMREx 0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7–0).

| <b>Z</b> 8 | Encore! XP <sup>®</sup> | F0823  | Series  |

|------------|-------------------------|--------|---------|

|            | Product                 | Specif | ication |

|            |                         |        |         |

nbedded in Life

n 🗖 IXYS Company

56

# Architecture

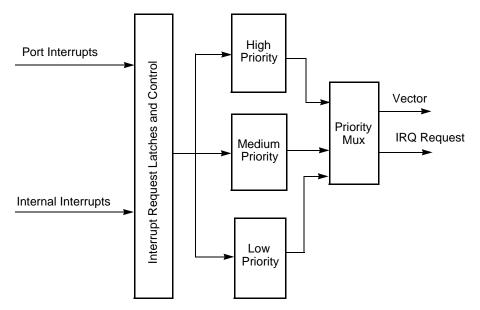

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

# Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 56

Interrupt Vectors and Priority: see page 57

Interrupt Assertion: see page 57

Software Interrupt Assertion: see page 58

Watchdog Timer Interrupt Assertion: see page 58

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

• Execution of an Enable Interrupt (EI) instruction

### Table 47. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|---------|-----|------|-------|-----|-------|-------|-------|-------|

| Field   |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| Address |     | FC8H |       |     |       |       |       |       |

| Bit          | Description                                                                |

|--------------|----------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENL | Port C3 Interrupt Request Enable Low Bit                                   |

| [2]<br>C2ENL | Port C2 Interrupt Request Enable Low Bit                                   |

| [1]<br>C1ENL | Port C1 Interrupt Request Enable Low Bit                                   |

| [0]<br>C0ENL | Port C0 Interrupt Request Enable High Low                                  |

# Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) Register (Table 48) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | FCDH |      |      |      |      |      |      |      |

| Table 48. | Interrupt | Edae | Select | Register | (IRQES) |

|-----------|-----------|------|--------|----------|---------|

|           |           |      |        |          |         |

| Bit         | Description                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IESx | <b>Interrupt Edge Select</b> $x$<br>0 = An interrupt request is generated on the falling edge of the PA $x$ input or PD $x$ .<br>1 = An interrupt request is generated on the rising edge of the PA $x$ input PD $x$ . |

Note: x indicates the specific GPIO port pin number (7–0).

### WDT Reset in NORMAL Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Watchdog Timer Control Register is set to 1. For more information about System Reset, see **the** <u>Reset and Stop</u> <u>Mode Recovery</u> chapter on page 21.

### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following WDT time-out in STOP Mode. For more information, see **the** <u>Reset and Stop Mode Recovery</u> chapter on page 21.

## Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer Control Register (WDTCTL) address unlocks the three Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. The following sequence is required to unlock the Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register (WDTCTL): see page 94

Watchdog Timer Reload Upper Byte Register (WDTU): see page 95

#### ilog Embedded in Life An IXYS Company 110

## **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 66 and Table 67) identify the current UART operating configuration and status.

| Bit         | 7                                                                                                                                                                                                                                                                                                                                         | 6                                                                                                                                                                                                                                                                               | 5  | 4  | 3    | 2    | 1   | 0   |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|------|------|-----|-----|--|

| Field       | RDA                                                                                                                                                                                                                                                                                                                                       | PE                                                                                                                                                                                                                                                                              | OE | FE | BRKD | TDRE | TXE | CTS |  |

| RESET       | 0                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                               | 0  | 0  | 0    | 1    | 1   | Х   |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                               | R  | R  | R    | R    | R   | R   |  |

| Address     |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                 |    | F4 | 1H   |      |     |     |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                | n                                                                                                                                                                                                                                                                               |    |    |      |      |     |     |  |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA                                                                                                                                                                                                                                                                                                 | <b>Receive Data Available</b><br>This bit indicates that the UART Receive Data Register has received data. Reading the UART<br>Receive Data Register clears this bit.<br>0 = The UART Receive Data Register is empty.<br>1 = There is a byte in the UART Receive Data Register. |    |    |      |      |     |     |  |

| [6]<br>PE   | Parity Error<br>This bit indicates that a parity error has occurred. Reading the UART Receive Data<br>register clears this bit.<br>0 = No parity error has occurred.<br>1 = A parity error has occurred.                                                                                                                                  |                                                                                                                                                                                                                                                                                 |    |    |      |      |     |     |  |

| [5]<br>OE   | Overrun Error<br>This bit indicates that an overrun error has occurred. An overrun occurs when new data is<br>received and the UART Receive Data Register has not been read. If the RDA bit is reset to 0,<br>reading the UART Receive Data Register clears this bit.<br>0 = No overrun error occurred.<br>1 = An overrun error occurred. |                                                                                                                                                                                                                                                                                 |    |    |      |      |     |     |  |

| [4]<br>FE   | Framing Error<br>This bit indicates that a framing error (no Stop bit following data reception) was detected.<br>Reading the UART Receive Data Register clears this bit.<br>0 = No framing error occurred.<br>1 = A framing error occurred.                                                                                               |                                                                                                                                                                                                                                                                                 |    |    |      |      |     |     |  |

| [3]<br>BRKD | <b>Break Detect</b><br>This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data Register clears this bit.<br>0 = No break occurred.<br>1 = A break occurred.                                                                 |                                                                                                                                                                                                                                                                                 |    |    |      |      |     |     |  |

ILO O hbedded in Life IXYS Company

120

The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the endec clock counter is reset, resynchronizing the endec to the incoming signal, allowing the endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART control registers as defined in the <u>Universal Asynchronous Receiver/Transmitter</u> chapter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the endec before enabling the GPIO port alternate function for the corresponding pin.

nbedded in Life

125

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 11-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:5]}

- An interrupt request to the Interrupt Controller denoting conversion complete

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

### Interrupts

The ADC is able to interrupt the CPU whenever a conversion has been completed and the ADC is enabled.

When the ADC is disabled, an interrupt is not asserted; however, an interrupt pending when the ADC is disabled is not cleared.

### **Calibration and Compensation**

Z8 Encore! XP F0823 Series ADC can be factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, user code can perform its own calibration, storing the values into Flash themselves.

### **Factory Calibration**

Devices that have been factory calibrated contain nine bytes of calibration data in the Flash option bit space. This data consists of three bytes for each reference type. For a list of input modes for which calibration data exists, see the <u>Zilog Calibration Data</u> section on page 152. There is 1 byte for offset, and there are 2 bytes for gain correction.

### User Calibration

If you have precision references available, its own external calibration can be performed, storing the values into Flash themselves.

#### ilog<sup>\*</sup> Embedded in Life An IXYS Company 133

# **Comparator Control Register Definition**

The Comparator Control Register (CMPCTL) configures the comparator inputs and sets the value of the internal voltage reference.

| Bit             | 7                                                                                                                                                                                                                                       | 6      | 5   | 4   | 3   | 2   | 1    | 0     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|------|-------|

| Field           | INPSEL                                                                                                                                                                                                                                  | INNSEL |     | REF | LVL | I   | Rese | erved |

| RESET           | 0                                                                                                                                                                                                                                       | 0      | 0   | 1   | 0   | 1   | 0    | 0     |

| R/W             | R/W                                                                                                                                                                                                                                     | R/W    | R/W | R/W | R/W | R/W | R/W  | R/W   |

| Address         |                                                                                                                                                                                                                                         |        |     | F9  | 0H  |     |      |       |

| Bit             | Descriptio                                                                                                                                                                                                                              | n      |     |     |     |     |      |       |

| [7]<br>INPSEL   | Signal Select for Positive Input<br>0 = GPIO pin used as positive comparator input.<br>1 = temperature sensor used as positive comparator input.                                                                                        |        |     |     |     |     |      |       |

| [6]<br>INNSEL   | Signal Select for Negative Input<br>0 = internal reference disabled, GPIO pin used as negative comparator input.<br>1 = internal reference enabled as negative comparator input.                                                        |        |     |     |     |     |      |       |

| [5:2]<br>REFLVL | Internal Reference Voltage Level $0000 = 0.0V.$ $0001 = 0.2V.$ $0010 = 0.4V.$ $0011 = 0.6V.$ $0100 = 0.8V.$ $0101 = 1.0V$ (Default). $0110 = 1.2V.$ $0111 = 1.4V.$ $1000 = 1.6V.$ $1001 = 1.8V.$ $1001 = 1.8V.$ $1010-1111 = Reserved.$ |        |     |     |     |     |      |       |

| [1:0]           | Note: This reference is independent of the ADC voltage reference.<br>Reserved<br>These bits are reserved; R/W bits must be programmed to 00 during writes and to 00 when<br>read.                                                       |        |     |     |     |     |      |       |

### Table 78. Comparator Control Register (CMP0)

# bits), framed between High bits. The auto-baud detector measures this period and sets the OCD baud rate generator accordingly.

The auto-baud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by eight. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by four, but this theoretical maximum is possible only for low noise designs with clean signals. Table 100 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended<br>Maximum Baud Rate<br>(kbps) | Recommended<br>Standard PC Baud<br>Rate (bps) | Minimum Baud Rate<br>(kbps) |

|---------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|

| 5.5296                          | 1382.4                                     | 691,200                                       | 1.08                        |

| 0.032768 (32kHz)                | 4.096                                      | 2400                                          | 0.064                       |

If the OCD receives a Serial Break (nine or more continuous bits Low) the auto-baud detector/generator resets. Reconfigure the auto-baud detector/generator by sending 80H.

## **OCD Serial Errors**

The OCD detects any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the auto-baud detector/generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the F0823 Series devices or when recovering from an error. A Serial Break from the host resets the autobaud generator/detector but does not reset the OCD Control Register. A Serial Break leaves the device in DEBUG Mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the opendrain nature of the DBG pin, the host sends a Serial Break to the OCD even if the OCD is transmitting a character. 160

nbedded in Life

DBG  $\leftarrow$  0BH DBG  $\leftarrow$  Program Memory Address[15:8] DBG  $\leftarrow$  Program Memory Address[7:0] DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\rightarrow$  1-65536 data bytes

Write Data Memory (0CH). The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option Bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Data Memory (0DH).** The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Read Program Memory CRC (0EH).** The Read Program Memory Cyclic Redundancy Check (CRC) command computes and returns the CRC of Program Memory using the 16bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

**Step Instruction (10H).** The Step Instruction steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG ← 10H

#### Table 110. Arithmetic Instructions (Continued)

| MULTdstMultiplySBCdst, srcSubtract with CarrySBCXdst, srcSubtract with Carry using Extended AddressingSUBdst, srcSubtractSUBXdst, srcSubtract using Extended Addressing | Mnemonic | Operands | Instruction                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-----------------------------------------------|

| SBCXdst, srcSubtract with Carry using Extended AddressingSUBdst, srcSubtract                                                                                            | MULT     | dst      | Multiply                                      |

| SUB     dst, src     Subtract                                                                                                                                           | SBC      | dst, src | Subtract with Carry                           |

|                                                                                                                                                                         | SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUBX dst, src Subtract using Extended Addressing                                                                                                                        | SUB      | dst, src | Subtract                                      |

|                                                                                                                                                                         | SUBX     | dst, src | Subtract using Extended Addressing            |

### Table 111. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                             |

|----------|-------------|---------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                               |

| BIT      | p, bit, dst | Bit Set or Clear                                        |

| BSET     | bit, dst    | Bit Set                                                 |

| BSWAP    | dst         | Bit Swap                                                |

| CCF      | —           | Complement Carry Flag                                   |

| RCF      | —           | Reset Carry Flag                                        |

| SCF      | —           | Set Carry Flag                                          |

| ТСМ      | dst, src    | Test Complement Under Mask                              |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended<br>Addressing |

| ТМ       | dst, src    | Test Under Mask                                         |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing               |

|          |             |                                                         |

### Table 112. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

ilog Embedded in Life An IXYS Company

187

| Assembly        |                                     | Address<br>Mode |       | _ Opcode(s) | Flags |        |   |   |        | Fetch | Instr. |   |

|-----------------|-------------------------------------|-----------------|-------|-------------|-------|--------|---|---|--------|-------|--------|---|

| Mnemonic        | Symbolic Operation                  | dst             | src   | (Hex)       | С     | CZSVDH |   |   | Cycles |       |        |   |

| LDX dst, src    | dst ← src                           | r               | ER    | 84          | _     | _      | _ | _ | _      | _     | 3      | 2 |

|                 |                                     | lr              | ER    | 85          | -     |        |   |   |        |       | 3      | 3 |

|                 |                                     | R               | IRR   | 86          | -     |        |   |   |        |       | 3      | 4 |

|                 |                                     | IR              | IRR   | 87          | -     |        |   |   |        |       | 3      | 5 |

|                 |                                     | r               | X(rr) | 88          | -     |        |   |   |        |       | 3      | 4 |

|                 |                                     | X(rr)           | r     | 89          | -     |        |   |   |        |       | 3      | 4 |

|                 |                                     | ER              | r     | 94          | -     |        |   |   |        |       | 3      | 2 |

|                 |                                     | ER              | lr    | 95          | -     |        |   |   |        |       | 3      | 3 |

|                 |                                     | IRR             | R     | 96          | -     |        |   |   |        |       | 3      | 4 |

|                 |                                     | IRR             | IR    | 97          | -     |        |   |   |        |       | 3      | 5 |

|                 |                                     | ER              | ER    | E8          | -     |        |   |   |        |       | 4      | 2 |

|                 |                                     | ER              | IM    | E9          | -     |        |   |   |        |       | 4      | 2 |

| LEA dst, X(src) | $dst \gets src + X$                 | r               | X(r)  | 98          | _     | _      | _ | - | _      | _     | 3      | 3 |

|                 |                                     | rr              | X(rr) | 99          | -     |        |   |   |        |       | 3      | 5 |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR              |       | F4          | _     | _      | _ | - | _      | _     | 2      | 8 |

| NOP             | No operation                        |                 |       | 0F          | _     | _      | _ | - | _      | _     | 1      | 2 |

| OR dst, src     | $dst \gets dst \ OR \ src$          | r               | r     | 42          | _     | *      | * | 0 | _      | _     | 2      | 3 |

|                 |                                     | r               | lr    | 43          | -     |        |   |   |        |       | 2      | 4 |

|                 |                                     | R               | R     | 44          | -     |        |   |   |        |       | 3      | 3 |

|                 |                                     | R               | IR    | 45          | -     |        |   |   |        |       | 3      | 4 |

|                 |                                     | R               | IM    | 46          | -     |        |   |   |        |       | 3      | 3 |

|                 |                                     | IR              | IM    | 47          | -     |        |   |   |        |       | 3      | 4 |

| ORX dst, src    | $dst \gets dst \ OR \ src$          | ER              | ER    | 48          | _     | *      | * | 0 | _      | _     | 4      | 3 |

|                 |                                     | ER              | IM    | 49          | -     |        |   |   |        |       | 4      | 3 |

| POP dst         | $dst \leftarrow @SP$                | R               |       | 50          | _     | -      | _ | - | _      | _     | 2      | 2 |

|                 | $SP \leftarrow SP + 1$              | IR              |       | 51          | -     |        |   |   |        |       | 2      | 3 |

### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

# Embedded in Life An IXYS Company 197

# **DC Characteristics**

Table 121 lists the DC characteristics of the Z8 Encore! XP F0823 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

| Symbol           | Parameter                    | Minimum             | Typical        | Maximum              | Units | Conditions                                                                                                                                                     |

|------------------|------------------------------|---------------------|----------------|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _              | 3.6                  | V     |                                                                                                                                                                |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -              | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                                |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -              | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all sig-<br>nal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -              | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when pro-<br>grammable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | -              | 0.4                  | V     | I <sub>OL</sub> = 2mA; V <sub>DD</sub> = 3.0V<br>High Output Drive disabled.                                                                                   |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | -              | -                    | V     | $I_{OH} = -2mA; V_{DD} = 3.0V$<br>High Output Drive disabled.                                                                                                  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -              | 0.6                  | V     | $I_{OL}$ = 20mA; $V_{DD}$ = 3.3 V<br>High Output Drive enabled.                                                                                                |

| V <sub>OH2</sub> | High Level Output<br>Voltage | 2.4                 | -              | -                    | V     | I <sub>OH</sub> = -20mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                                 |

| I <sub>IH</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.002 | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>IL</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.007 | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>TL</sub>  | Tristate Leakage<br>Current  | -                   | -              | <u>+</u> 5           | μA    |                                                                                                                                                                |

| Table 121. | DC | Characteristics |

|------------|----|-----------------|

|            |    | •               |

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

> ilog<sup>®</sup> Embedded in Life

■IXYS Company

211

# **Ordering Information**

Order your F0823 Series products from Zilog using the part numbers shown in Table 135. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

|                     | Table 155. 20    | LIICO     |            | 1 0025 (               |                     | Oraci          |                     |

|---------------------|------------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number         | Flash<br>RAM     | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 |                  |           | ash, 10    | -Bit An                | alog-1              | o-Digi         | ital Converter      |

| Standard Temperatu  |                  |           |            |                        |                     |                |                     |

| Z8F0823PB005SG      | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005SG      | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005SG      | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005SG      | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005SG      | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005SG      | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005SG      | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005SG      | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005SG      | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatu  | ıre: –40°C to 10 | )5°C      |            |                        |                     |                |                     |

| Z8F0823PB005EG      | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005EG      | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005EG      | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005EG      | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005EG      | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005EG      | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005EG      | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005EG      | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005EG      | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

#### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix

> ilog Embedded in Life An IXYS Company 215

|                                   |                |           |            |                        |                     | U              | · · · ·             |  |  |  |

|-----------------------------------|----------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|--|--|

| Part Number                       | Flash<br>RAM   | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |  |

| Z8 Encore! XP F0823               | Series with 2  | 2 KB FI   | ash, 10    | )-Bit An               | alog-1              | o-Digi         | tal Converter       |  |  |  |

| Standard Temperature: 0°C to 70°C |                |           |            |                        |                     |                |                     |  |  |  |

| Z8F0223PB005SG                    | 2 KB 512 I     | 36        | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0223QB005SG                    | 2 KB 512 I     | 36        | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0223SB005SG                    | 2 KB 512 I     | 36        | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0223SH005SG                    | 2 KB 512 I     | 3 16      | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0223HH005SG                    | 2 KB 512 I     | 3 16      | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0223PH005SG                    | 2 KB 512 B     | 3 16      | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0223SJ005SG                    | 2 KB 512 I     | 3 22      | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0223HJ005SG                    | 2 KB 512 I     | 3 22      | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0223PJ005SG                    | 2 KB 512 I     | 3 22      | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |

| Extended Temperatu                | re: -40°C to ' | 05°C      |            |                        |                     |                |                     |  |  |  |

| Z8F0223PB005EG                    | 2 KB 512 I     | 36        | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0223QB005EG                    | 2 KB 512 I     | 36        | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0223SB005EG                    | 2 KB 512 I     | 36        | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0223SH005EG                    | 2 KB 512 I     | 3 16      | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0223HH005EG                    | 2 KB 512 I     | 3 16      | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0223PH005EG                    | 2 KB 512 B     | 3 16      | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0223SJ005EG                    | 2 KB 512 I     | 3 22      | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0223HJ005EG                    | 2 KB 512 I     | 3 22      | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0223PJ005EG                    | 2 KB 512 B     | 3 22      | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |

### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)