Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213sj005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Interrupt Assertion                                      | . 57 |

|----------------------------------------------------------|------|

| Software Interrupt Assertion                             | . 58 |

| Watchdog Timer Interrupt Assertion                       | . 58 |

| Interrupt Control Register Definitions                   | . 59 |

| Interrupt Request 0 Register                             | . 59 |

| Interrupt Request 1 Register                             | 60   |

| Interrupt Request 2 Register                             | 61   |

| IRQ0 Enable High and Low Bit Registers                   | 61   |

| IRQ1 Enable High and Low Bit Registers                   | . 63 |

| IRQ2 Enable High and Low Bit Registers                   | . 65 |

| Interrupt Edge Select Register                           | . 66 |

| Shared Interrupt Select Register                         | . 67 |

| Interrupt Control Register                               | . 68 |

| Timers                                                   | . 69 |

| Architecture                                             |      |

| Operation                                                |      |

| Timer Operating Modes                                    |      |

| Reading the Timer Count Values                           |      |

| Timer Pin Signal Operation                               |      |

| Timer Control Register Definitions                       | . 83 |

| Timer 0–1 High and Low Byte Registers                    | . 83 |

| Timer Reload High and Low Byte Registers                 |      |

| Timer 0–1 PWM High and Low Byte Registers                |      |

| Timer 0–1 Control Registers                              |      |

| Watchdog Timer                                           | 91   |

| Operation                                                |      |

| Watchdog Timer Refresh                                   |      |

| Watchdog Timer Time-Out Response                         |      |

| Watchdog Timer Reload Unlock Sequence                    |      |

| Watchdog Timer Control Register Definitions              |      |

| Watchdog Timer Control Register                          |      |

| Watchdog Timer Reload Upper, High and Low Byte Registers |      |

| Universal Asynchronous Receiver/Transmitter              |      |

| Architecture                                             |      |

| Operation                                                |      |

| Transmitting Data Using the Polled Method                |      |

| Transmitting Data Using the Interrupt-Driven Method      |      |

| Receiving Data Using the Polled Method                   |      |

| Receiving Data Using the Interrupt-Driven Method         |      |

| Clear To Send (CTS) Operation                            |      |

| Ciem 10 Dena (01D) Operation                             | -05  |

returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the Z8 Encore! XP F0823 Series products.

| Program Memory Address (Hex) | Function                 |

|------------------------------|--------------------------|

| Z8F0823 and Z8F0813 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0423 and Z8F0413 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0223 and Z8F0213 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-07FF                    | Program Memory           |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps

Note: \*See the <u>Trap and Interrupt Vectors in Order of Priority section on page 55</u> for a list of the interrupt vectors and traps.

Embedded in Life An IXYS Company

ilog<sup>®</sup> Embedded in Life

| Address (Hex) | Register Description    | Mnemonic | Reset (Hex) | Page<br>No.                                                                   |

|---------------|-------------------------|----------|-------------|-------------------------------------------------------------------------------|

| eZ8 CPU       |                         |          |             |                                                                               |

| FFC           | Flags                   | _        | XX          | Refe                                                                          |

| FFD           | Register Pointer        | RP       | XX          | to the                                                                        |

| FFE           | Stack Pointer High Byte | SPH      | XX          | - <u>eZ8</u><br>CPU                                                           |

| FFF           | Stack Pointer Low Byte  | SPL      | XX          | <u>Core</u><br><u>User</u><br><u>Man-</u><br><u>ual</u><br>(UM0<br><u>28)</u> |

#### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

# Embedded in Life

23

## **Reset Sources**

Table 10 lists the possible sources of a System Reset.

| Operating Mode       | Reset Source                                       | Special Conditions                                                                                                                 |

|----------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-<br>Out.              | Reset delay begins after supply voltage exceeds POR level.                                                                         |

|                      | Watchdog Timer time-out when configured for Reset. | None.                                                                                                                              |

|                      | RESET pin assertion.                               | All reset pulses less than three system clocks in width are ignored.                                                               |

|                      | OCD initiated Reset (OCDCTL[0] set to 1).          | System Reset, except the OCD is unaffected by the reset.                                                                           |

| STOP Mode            | Power-On Reset/Voltage Brown-<br>Out.              | Reset delay begins after supply voltage exceeds POR level.                                                                         |

|                      | RESET pin assertion.                               | All reset pulses less than the specified analog delay are ignored. See the <u>Electrical Characteris</u> tics chapter on page 196. |

|                      | DBG pin driven Low.                                | None.                                                                                                                              |

#### Table 10. Reset Sources and Resulting Reset Type

## **Power-On Reset**

Each device in the Z8 Encore! XP F0823 Series contains an internal POR circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F0823 Series device exits the POR state, the eZ8 CPU fetches the Reset vector. Following the POR, the POR status bit in Watchdog Timer Control (WDTCTL) Register is set to 1.

Figure 5 displays POR operation. For the POR threshold voltage ( $V_{POR}$ ), see the <u>Electrical Characteristics</u> chapter on page 196.

#### ilog° Embedded in Life An∎IXYS Company

#### 29

| Bit        | Description (Continued)                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>EXT | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset<br>or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register |

|            | resets this bit. For POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                               |

| [3:0]      | Reserved                                                                                                                                                                                                                    |

These bits are reserved and must be programmed to 0000 when read.

#### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

bedded in Life

40

PC[2:0]. All other signal pins are 5V-tolerant, and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

## **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see the <u>Oscillator Control Register Definitions</u> section on page 171) such that the external oscillator is selected as the system clock. For 8-pin devices, use PA1 instead of PB3.

## **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see the <u>Interrupt Controller</u> chapter on page 54.

## **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data, and output data. Table 18 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register<br>Mnemonic    | Port Register Name                                           |

|------------------------------|--------------------------------------------------------------|

| P <i>x</i> ADDR              | Port A–C Address Register (Selects subregisters).            |

| P <i>x</i> CTL               | Port A-C Control Register (Provides access to subregisters). |

| PxIN                         | Port A–C Input Data Register.                                |

| P <i>x</i> OUT               | Port A–C Output Data Register.                               |

| Port Subregister<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                | Data Direction.                                              |

| P <i>x</i> AF                | Alternate Function.                                          |

| P <i>x</i> OC                | Output Control (Open-Drain).                                 |

|                              |                                                              |

**Table 18. GPIO Port Registers and Subregisters**

#### ilog Embedded in Life An∎IXYSCompany 42

#### Table 20. PADDR[7:0] Subregister Functions

| PADDR[7:0] | Port Control Subregister Accessible Using the Port A–C Control Registers |

|------------|--------------------------------------------------------------------------|

| 05H        | Stop Mode Recovery Source Enable.                                        |

| 06H        | Pull-up Enable.                                                          |

| 07H        | Alternate Function Set 1.                                                |

| 08H        | Alternate Function Set 2.                                                |

| 09H–FFH    | No function.                                                             |

## **Port A–C Control Registers**

The Port A–C Control registers set the GPIO port operation. The value in the corresponding Port A–C Address Register determines which subregister is read from or written to by a Port A–C Control Register transaction; see Table 21.

| Bit           | 7          | 6                                                                                                          | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------------|------------|------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|

| Field         |            | PCTL                                                                                                       |     |     |     |     |     |     |  |

| RESET         |            |                                                                                                            |     | 00  | )H  |     |     |     |  |

| R/W           | R/W        | R/W                                                                                                        | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address       |            | FD1H, FD5H, FD9H                                                                                           |     |     |     |     |     |     |  |

| Bit           | Descriptio | Description                                                                                                |     |     |     |     |     |     |  |

| [7:0]<br>PCTL |            | Port Control<br>The Port Control Register provides access to all subregisters that configure the GPIO Port |     |     |     |     |     |     |  |

Table 21. Port A–C Control Registers (PxCTL)

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

| -        | 0004H                               | Watchdog Timer (see the Watchdog Timer section on page 91)                 |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          | 0036H                               | Port C Pin 0, both input edges                                             |

| Lowest   | 0038H                               | Reserved                                                                   |

#### Table 35. Trap and Interrupt Vectors in Order of Priority

**Caution:** To avoid retriggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, Zilog recommends that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as shown in the following example.

```

CLEARWDT:

LDX r0, RSTSTAT ; read reset status register to clear wdt bit

BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

```

## **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Timer Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 36) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 register to determine if any interrupt requests are pending.

| Bit     | 7        | 6   | 5   | 4     | 3     | 2        | 1 | 0    |

|---------|----------|-----|-----|-------|-------|----------|---|------|

| Field   | Reserved | T1I | тоі | U0RXI | U0TXI | Reserved |   | ADCI |

| RESET   | 0        | 0   | 0   | 0     | 0     | 0        |   | 0    |

| R/W     | R/W      | R/W | R/W | R/W   | R/W   | R/W      |   | R/W  |

| Address |          |     |     | FC    | 0H    |          |   |      |

| Bit        | Description                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]        | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                               |

| [6]<br>T1I | <b>Timer 1 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 1.<br>1 = An interrupt request from Timer 1 is awaiting service. |

| [5]<br>T0I | <b>Timer 0 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 0.<br>1 = An interrupt request from Timer 0 is awaiting service. |

#### Table 43. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address | FC4H    |         |        |        |               |        |        |        |

| Bit             | Description                                                                                                                                                                         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VENH  | Port A Bit[7] Interrupt Request Enable High Bit                                                                                                                                     |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit                                                                                                                       |

| [5:0]<br>PAxENH | <b>Port A Bit[x] Interrupt Request Enable High Bit</b><br>For selection of Port A as the interrupt source, see the <u>Shared Interrupt Select Register</u> sec-<br>tion on page 67. |

Note: x indicates the specific GPIO Port A pin number (5–0).

#### Table 44. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|---------|---------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | PA7VENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |  |  |

| RESET   | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address |         | FC5H    |        |        |        |        |        |        |  |  |

| Description                                                  |                                                                                                                |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Port A Bit[7] Interrupt Request Enable Low Bit               |                                                                                                                |

| Port A Bit[7] or Comparator Interrupt Request Enable Low Bit |                                                                                                                |

| Port A Bit[x] Interrupt Request Enable Low Bit               |                                                                                                                |

| _                                                            | Port A Bit[7] Interrupt Request Enable Low Bit<br>Port A Bit[7] or Comparator Interrupt Request Enable Low Bit |

Note: x indicates the specific GPIO Port A pin number (5–0).

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period. If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### **PWM Dual Output Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a PWM output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the capture occurs on a rising edge or a falling edge of the Timer Input signal. When the capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL1 Register clears indicating the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture or a reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both

#### ilog° Embedded in Life An∎IXYS Company 99

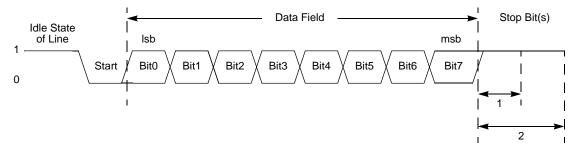

Figure 11. UART Asynchronous Data Format without Parity

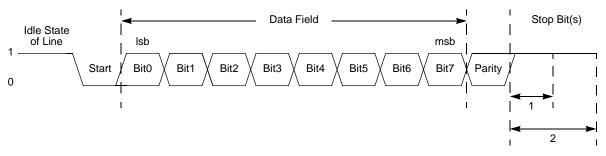

Figure 12. UART Asynchronous Data Format with Parity

## **Transmitting Data Using the Polled Method**

Observe the following steps to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register, if MULTIPROCESSOR Mode is appropriate, to enable MULTIPROCESSOR (9-bit) Mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR Mode.

- 5. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR Mode is not enabled, and select either even or odd parity (PSEL)

116

dded in Life

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 73 provides information about data rate errors for a 5.5296MHz System Clock.

| 5.5296MHz System Clock   |                          |                      |           |  |  |  |  |

|--------------------------|--------------------------|----------------------|-----------|--|--|--|--|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |  |  |  |  |

| 1250.0                   | N/A                      | N/A                  | N/A       |  |  |  |  |

| 625.0                    | N/A                      | N/A                  | N/A       |  |  |  |  |

| 250.0                    | 1                        | 345.6                | 38.24     |  |  |  |  |

| 115.2                    | 3                        | 115.2                | 0.00      |  |  |  |  |

| 57.6                     | 6                        | 57.6                 | 0.00      |  |  |  |  |

| 38.4                     | 9                        | 38.4                 | 0.00      |  |  |  |  |

| 19.2                     | 18                       | 19.2                 | 0.00      |  |  |  |  |

| 9.60                     | 36                       | 9.60                 | 0.00      |  |  |  |  |

| 4.80                     | 72                       | 4.80                 | 0.00      |  |  |  |  |

| 2.40                     | 144                      | 2.40                 | 0.00      |  |  |  |  |

| 1.20                     | 288                      | 1.20                 | 0.00      |  |  |  |  |

| 0.60                     | 576                      | 0.60                 | 0.00      |  |  |  |  |

| 0.30                     | 1152                     | 0.30                 | 0.00      |  |  |  |  |

#### Table 73. UART Baud Rates

nbedded in Life

134

## Flash Memory

The products in Z8 Encore! XP F0823 Series features either 8KB (8192), 4KB (4096), 2KB (2048) or 1KB (1024) of nonvolatile Flash memory with read/write/erase capability. Flash Memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash Memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program/data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F0823 Series, these sectors are either 1024 bytes (in the 8KB devices) or 512 bytes in size (all other memory sizes); each sector maps to a page. Page and sector sizes are not generally equal.

The first two bytes of the Flash program memory are used as Flash Option bits. For more information about their operation, see the <u>Flash Option Bits</u> chapter on page 146.

Table 79 describes the Flash memory configuration for each device in the Z8 Encore! XP F0823 Series. Figure 20 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F08x3     | 8 (8192)                 | 16          | 0000H–1FFFH                    | 1024                         |

| Z8F04x3     | 4 (4096)                 | 8           | 0000H–0FFFH                    | 512                          |

| Z8F02x3     | 2 (2048)                 | 4           | 0000H-07FFH                    | 512                          |

| Z8F01x3     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

#### Table 79. Z8 Encore! XP F0823 Series Flash Memory Configurations

## **OCD Unlock Sequence (8-Pin Devices Only)**

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5 ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

\begin{array}{l} \text{DBG} \leftarrow 80\text{H} \text{ (autobaud)} \\ \\ \text{DBG} \leftarrow \text{EBH} \\ \\ \text{DBG} \leftarrow 5\text{AH} \\ \\ \\ \text{DBG} \leftarrow 70\text{H} \\ \\ \\ \\ \text{DBG} \leftarrow \text{CDH} \text{ (32-bit unlock key)} \end{array}

```

Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20- or 28-pin device. To enter DEBUG Mode, reautobaud and write 80H to the OCD Control Register (see the <u>On-Chip Debugger Commands</u> section on page 162).

## **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

## **Runtime Counter**

The OCD contains a 16-bit Runtime Counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

## Embedded in Life An IXYS Company

## **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

| Table 103. OCD Status | Register (OCDSTAT) |

|-----------------------|--------------------|

|-----------------------|--------------------|

| Bit   | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |

|-------|-----|------|--------|----------|---|---|---|---|--|

| Field | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |

|       |     |      | I      |          |   | I |   |   |  |

| Bit           | Description                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBG    | Debug Status<br>0 = NORMAL Mode.<br>1 = DEBUG Mode.                                                                                |

| [6]<br>HALT   | HALT Mode<br>0 = Not in HALT Mode.<br>1 = In HALT Mode.                                                                            |

| [5]<br>FRPENB | Flash Read Protect Option Bit Enable<br>0 = FRP bit enabled to allow disabling of many OCD commands.<br>1 = FRP bit has no effect. |

| [4:0]         | Reserved<br>These bits are reserved and must be 00000 when read.                                                                   |

> ilog Embedded in Life An IXYS Company 214

|                     |                 |           |            |                        |                     | -              |                     |

|---------------------|-----------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number         | Flash<br>RAM    | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 | Series with 4   | KB Fla    | ash        |                        |                     |                |                     |

| Standard Temperatu  | re: 0°C to 70°C | ;         |            |                        |                     |                |                     |

| Z8F0413PB005SG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005SG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005SG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005SG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005SG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005SG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005SG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005SG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005SG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu  | re: -40°C to 1  | 05°C      |            |                        |                     |                |                     |

| Z8F0413PB005EG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005EG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005EG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005EG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005EG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005EG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005EG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005EG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005EG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

#### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

part selection guide 2