Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213sj005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| External Reset Input                                | . 25 |

|-----------------------------------------------------|------|

| External Reset Indicator                            | . 26 |

| On-Chip Debugger Initiated Reset                    | . 26 |

| Stop Mode Recovery                                  | . 26 |

| Stop Mode Recovery Using Watchdog Timer Time-Out    | . 27 |

| Stop Mode Recovery Using a GPIO Port Pin Transition | . 27 |

| Stop Mode Recovery Using the External RESET Pin     | . 28 |

| Reset Register Definitions                          | . 28 |

| Low-Power Modes                                     | . 30 |

| STOP Mode                                           | . 30 |

| HALT Mode                                           | . 31 |

| Peripheral-Level Power Control                      | . 31 |

| Power Control Register Definitions                  | . 31 |

| General-Purpose Input/Output                        | 33   |

| GPIO Port Availability By Device                    |      |

| Architecture                                        |      |

| GPIO Alternate Functions                            |      |

| Direct LED Drive                                    |      |

| Shared Reset Pin                                    |      |

| Shared Debug Pin                                    |      |

| Crystal Oscillator Override                         |      |

| 5V Tolerance                                        |      |

| External Clock Setup                                |      |

| GPIO Interrupts                                     |      |

| GPIO Control Register Definitions                   |      |

| Port A–C Address Registers                          |      |

| Port A–C Control Registers                          |      |

| Port A–C Data Direction Subregisters                |      |

| Port A–C Alternate Function Subregisters            | . 43 |

| Port A–C Input Data Registers                       | . 50 |

| Port A–C Output Data Register                       | . 51 |

| LED Drive Enable Register                           | . 51 |

| LED Drive Level High Register                       |      |

| LED Drive Level Low Register                        |      |

| Interrupt Controller                                | . 54 |

| Interrupt Vector Listing                            |      |

| Architecture                                        |      |

| Operation                                           | . 56 |

| Master Interrupt Enable                             |      |

| Interrupt Vectors and Priority                      | . 57 |

|                                                     |      |

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

## **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see **the** <u>Port A–C Control Registers</u> **section on page 42**), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overrightarrow{\text{RESET}}$  pin Low. The  $\overrightarrow{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

## **Stop Mode Recovery**

The device enters into STOP Mode when eZ8 CPU executes a STOP instruction. For more details about STOP Mode, see **the** Low-Power Modes **section on page 30**. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

## 28

nbedded in Life

## Stop Mode Recovery Using the External RESET Pin

When a Z8 Encore! XP F0823 Series device is in STOP Mode and the external  $\overline{\text{RESET}}$  pin is driven Low, a system reset occurs. Because of a glitch filter operating on the  $\overline{\text{RESET}}$  pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For more details, see the <u>Electrical Characteristics</u> chapter on page 196.

## **Reset Register Definitions**

The following sections define the Reset registers.

#### **Reset Status Register**

The Reset Status (RSTSTAT) Register is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer Control Register, which is writeonly; see Table 12.

| Bit     | 7       | 6            | 5        | 4   | 3        | 2 | 1 | 0 |  |  |

|---------|---------|--------------|----------|-----|----------|---|---|---|--|--|

| Field   | POR     | STOP         | WDT      | EXT | Reserved |   |   |   |  |  |

| RESET   | See des | criptions in | Table 13 | 0   | 0        | 0 | 0 | 0 |  |  |

| R/W     | R       | R            | R        | R   | R        | R | R | R |  |  |

| Address |         | FFOH         |          |     |          |   |   |   |  |  |

Table 12. Reset Status Register (RSTSTAT)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [7]<br>POR  | <b>Power-On Reset Indicator</b><br>If this bit is set to 1, a Power-On Reset event has occurred. This bit is reset to 0 if a WDT time-<br>out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read. For<br>POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                                                                                                   |  |  |  |  |  |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery is occurred. If the STOP and WDT bits are both set<br>to 1, the Stop Mode Recovery occurred because of a WDT time-out. If the STOP bit is 1 and<br>the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset<br>by a POR or a WDT time-out that occurred while not in STOP Mode. Reading this register also<br>resets this bit. For POR/Stop Mode Recover event values, please see Table 13. |  |  |  |  |  |

| [5]<br>WDT  | <b>Watchdog Timer Time-Out Indicator</b><br>If this bit is set to 1, a WDT time-out has occurred. A POR resets this pin. A Stop Mode Recov-<br>ery from a change in an input pin also resets this bit. Reading this register resets this bit; this<br>read must occur before clearing the WDT interrupt. For POR/Stop Mode Recover event values,<br>please see Table 13.                                                                                                                                             |  |  |  |  |  |

34

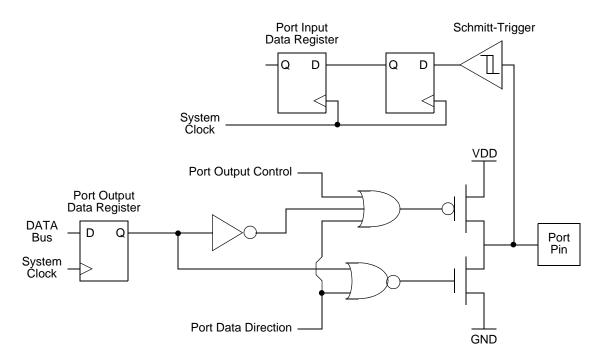

## Architecture

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

# **GPIO Alternate Functions**

Many of the GPIO port pins are used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The port A–D Alternate Function subregisters configure these pins for either GPIO or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Tables 16 and 17 list the alternate functions possible with each port pin for 8-pin and non-8-pin parts, respectively. The alternate function associated at a pin is defined through Alternate Function Sets subregisters AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

- Execution of an Return from Interrupt (IRET) instruction

- Writing a 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Timer Oscillator Fail Trap

## **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all interrupts are enabled with identical interrupt priority (for example, all as Level 2 interrupts), the interrupt priority is assigned from highest to lowest as specified in <u>Table 35</u> on page 55. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2 or Level 3), priority is assigned as specified in Table 35. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Timer Oscillator Fail Trap, and Illegal Instruction Trap always have highest (Level 3) priority.

### **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request register likewise clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

#### Table 40. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit           | 7                                                                        | 6           | 5          | 4           | 3       | 2        | 1 | 0      |  |  |

|---------------|--------------------------------------------------------------------------|-------------|------------|-------------|---------|----------|---|--------|--|--|

| Field         | Reserved                                                                 | T1ENH       | T0ENH      | U0RENH      | U0TENH  | Reserved |   | ADCENH |  |  |

| RESET         | 0                                                                        | 0           | 0          | 0           | 0       | (        | ) | 0      |  |  |

| R/W           | R/W                                                                      | R/W         | R/W        | R/W         | R/W     | R/       | W | R/W    |  |  |

| Address       | FC1H                                                                     |             |            |             |         |          |   |        |  |  |

| Bit           | Description                                                              |             |            |             |         |          |   |        |  |  |

| [7]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.     |             |            |             |         |          |   |        |  |  |

| [6]<br>T1ENH  | Timer 1 Interrupt Request Enable High Bit                                |             |            |             |         |          |   |        |  |  |

| [5]<br>T0ENH  | Timer 0 Interrupt Request Enable High Bit                                |             |            |             |         |          |   |        |  |  |

| [4]<br>U0RENH | UART 0 Re                                                                | ceive Inter | rupt Reque | st Enable H | igh Bit |          |   |        |  |  |

| [3]<br>U0TENH | UART 0 Transmit Interrupt Request Enable High Bit                        |             |            |             |         |          |   |        |  |  |

| [2:1]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |             |            |             |         |          |   |        |  |  |

| [0]           | ADC Interrupt Request Enable High Bit                                    |             |            |             |         |          |   |        |  |  |

[0] ADCENH

#### Table 41. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5            | 4             | 3             | 2        | 1 | 0      |  |  |

|---------|----------|-------|--------------|---------------|---------------|----------|---|--------|--|--|

| Field   | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved |   | ADCENL |  |  |

| RESET   | 0        | 0     | 0            | 0             | 0             | 0        |   | 0      |  |  |

| R/W     | R        | R/W   | R/W          | R/W           | R/W           | R        |   | R/W    |  |  |

| Address |          | FC2H  |              |               |               |          |   |        |  |  |

| Bit          | Description                                                             |

|--------------|-------------------------------------------------------------------------|

| [7]          | Reserved<br>This bit is reserved and must be programmed to 0 when read. |

| [6]<br>T1ENL | Timer 1 Interrupt Request Enable Low Bit                                |

## Embedded in Life IXYS Company 92

## Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

## Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information about programming of the WDT\_RES Flash Option Bit, see **the** <u>Flash Option Bits</u> chapter on page 146.

#### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see the <u>Reset Status Register</u> section on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and F0823 Series are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. For more information about Stop Mode Recovery, see **the** <u>Reset and Stop Mode Recovery</u> chapter on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

#### ilog<sup>®</sup> Embedded in Life An∎IXYS Company 94

<u>Watchdog Timer Reload High Byte Register (WDTH)</u>: see page 95 <u>Watchdog Timer Reload Low Byte Register (WDTL)</u>: see page 95

## Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status Register.

| Bit              | 7           | 6                                                                                                                     | 5 | 4   | 3    | 2 | 1 | 0 |  |  |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|---|-----|------|---|---|---|--|--|

| Field            |             |                                                                                                                       |   | WDT | UNLK |   |   |   |  |  |

| RESET            | Х           | Х                                                                                                                     | Х | Х   | Х    | Х | Х | Х |  |  |

| R/W              | W           | W                                                                                                                     | W | W   | W    | W | W | W |  |  |

| Address          |             | FF0H                                                                                                                  |   |     |      |   |   |   |  |  |

| Bit              | Description |                                                                                                                       |   |     |      |   |   |   |  |  |

| [7:0]<br>WDTUNLK |             | Watchdog Timer Unlock<br>The software must write the correct unlocking sequence to this register before it is allowed |   |     |      |   |   |   |  |  |

Table 60. Watchdog Timer Control Register (WDTCTL)

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 61 through 63, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT Reload Value must not be set to a value less than 000004H.

to modify the contents of the Watchdog Timer reload registers.

nbedded in Life

100

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled,.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

#### Transmitting Data Using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

nbedded in Life

101

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) performs the following:

1. Write the UART Control 1 Register to select the multiprocessor bit for the byte to be transmitted:

Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 3. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 4. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data Register to again become empty.

#### **Receiving Data Using the Polled Method**

Observe the following steps to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set an acceptable baud rate for the incoming data stream.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable MULTIPROCESSOR Mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if Multiprocessor mode is not enabled, and select either even or odd parity

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to <u>Step 6</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

- 6. Read data from the UART Receive Data Register. If operating in MULTIPROCES-SOR (9-bit) Mode, further actions may be required depending on the MULTIPRO-CESSOR Mode bits MPMD[1:0].

nbedded in Life

102

## **Receiving Data Using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Observe the following steps to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR Mode

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

# Embedded in Life

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data Register (Table 64) are shifted out on the TXDx pin. The Write-only UART Transmit Data Register shares a Register File address with the read-only UART Receive Data Register.

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|---|---|---|---|---|---|---|--|

| Field   | TXD  |   |   |   |   |   |   |   |  |

| RESET   | Х    | Х | Х | Х | Х | Х | Х | Х |  |

| R/W     | W    | W | W | W | W | W | W | W |  |

| Address | F40H |   |   |   |   |   |   |   |  |

#### Table 64. UART Transmit Data Register (U0TXD)

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

## **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data Register (Table 65). The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|---|---|---|---|---|---|---|--|

| Field   | RXD  |   |   |   |   |   |   |   |  |

| RESET   | Х    | Х | Х | Х | Х | Х | Х | Х |  |

| R/W     | R    | R | R | R | R | R | R | R |  |

| Address | F40H |   |   |   |   |   |   |   |  |

| Bit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control</li> <li>This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.</li> <li>When the UART receiver is not enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0.</li> <li>Reads from the Baud Rate High and Low Byte registers return the current BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the High Byte is read.</li> </ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared encoder/decoder is disabled. UART operates normally.</li> <li>1 = Infrared encoder/decoder is enabled. The UART transmits and receives data through the infrared encoder/decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### illog<sup>®</sup> Ibedded in Life IXYS Company 138

# Table 80. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code program-<br>ming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-<br>Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                    |

#### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

#### **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F0823 Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 79</u> on page 134.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

> ILO <u>G</u> Embedded in Life An **D**IXYS Company 142

| Bit     | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-----------------|---|---|---|---|---|---|---|

| Field   | FCMD            |   |   |   |   |   |   |   |

| RESET   | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

| R/W     | W               | W | W | W | W | W | W | W |

| Address | FF8H            |   |   |   |   |   |   |   |

#### Table 81. Flash Control Register (FCTL)

Bit

Description

[7:0]

Flash Command

FCMD

73H = First unlock command.

8CH = Second unlock command.

95H = Page Erase command (must be third command in sequence to initiate Page Erase).

63H = Mass Erase command (must be third command in sequence to initiate Mass Erase).

5EH = Enable Flash Sector Protect Register Access.

163

ilog Ibedded in Life

In the following list of OCD Commands, data and commands sent from the host to the OCD are identified by 'DBG  $\leftarrow$  Command/Data'. Data sent from the OCD back to the host is identified by 'DBG  $\rightarrow$  Data'.

**Read OCD Revision (00H).** The Read OCD Revision command determines the version of the OCD. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The Read OCD Status Register command reads the OCDSTAT Register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

**Read Runtime Counter (03H).** The Runtime Counter counts system clock cycles in between breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory, Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction, and Execute Instruction commands.

```

DBG \leftarrow 03H

DBG \rightarrow RuntimeCounter[15:8]

DBG \rightarrow RuntimeCounter[7:0]

```

Write OCD Control Register (04H). The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of returning the device to normal operating mode is to reset the device.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

**Read OCD Control Register (05H).** The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

**Write Program Counter (06H).** The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53MHz frequency. The features of IPO include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimming possible through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

# Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30°C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

Power down this block for minimum system power. By default, the oscillator is configured through the Flash Option bits. However, the user code can override these trim values, as described in the <u>Trim Bit Address Space</u> section on page 151.

Select one of the two frequencies for the oscillator: 5.53MHz and 32.8kHz, using the OSCSEL bits in the <u>Oscillator Control</u> chapter on page 169.

## Embedded in Life An IXYS Company

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                   |                        | T <sub>A</sub> = -40°C<br>(unless o | 'V to 3.6V<br>C to +105°C<br>otherwise<br>ted) |       |                                         |

|-------------------|------------------------|-------------------------------------|------------------------------------------------|-------|-----------------------------------------|

| Symbol            | Parameter              | Minimum Maximum                     |                                                | Units | Conditions                              |

| FSYSCLK           | System Clock Frequency | _                                   | 20.0*                                          | MHz   | Read-only from Flash memory.            |

|                   |                        | 0.032768                            | 20.0 <sup>1</sup>                              | MHz   | Program or erasure of the Flash memory. |

| T <sub>XIN</sub>  | System Clock Period    | 50                                  | -                                              | ns    | $T_{CLK} = 1/F_{SYSCLK}$ .              |

| T <sub>XINH</sub> | System Clock High Time | 20                                  | 30                                             | ns    | T <sub>CLK</sub> = 50ns.                |

| T <sub>XINL</sub> | System Clock Low Time  | 20                                  | 30                                             | ns    | T <sub>CLK</sub> = 50ns.                |

| T <sub>XINR</sub> | System Clock Rise Time | _                                   | 3                                              | ns    | T <sub>CLK</sub> = 50ns.                |

| T <sub>XINF</sub> | System Clock Fall Time | _                                   | 3                                              | ns    | Т <sub>СІ К</sub> = 50ns.               |

| Table ' | 123. AC | Characteristics |

|---------|---------|-----------------|

|---------|---------|-----------------|

#### Table 124. Internal Precision Oscillator Electrical Characteristics

|                    |                                                         | $T_A = -$ | = 2.7V to<br>-40°C to +<br>otherwise |            |       |                                                 |

|--------------------|---------------------------------------------------------|-----------|--------------------------------------|------------|-------|-------------------------------------------------|

| Symbol             | Parameter                                               | Minimum   | Typical                              | Maximum    | Units | Conditions                                      |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |           | 5.53                                 |            | MHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |           | 32.7                                 |            | kHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |           | <u>+</u> 1                           | <u>+</u> 4 | %     |                                                 |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |           | 3                                    |            | μs    |                                                 |

> ilog Embedded in Life An IXYS Company 213

| Part Number         | Flash<br>RAM   | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|---------------------|----------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP F0823 | Series with 4  | KB FI     | ash, 10    | )-Bit An               | alog-t              | o-Digi         | tal Converter       |

| Standard Temperatur | re: 0°C to 70° | C         |            |                        |                     |                |                     |

| Z8F0423PB005SG      | 4 KB 1 KB      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005SG      | 4 KB 1 KB      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005SG      | 4 KB 1 KB      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005SG      | 4 KB 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005SG      | 4 KB 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005SG      | 4 KB 1 KB      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005SG      | 4 KB 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005SG      | 4 KB 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005SG      | 4 KB 1 KB      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatu  | re: -40°C to 1 | 05°C      |            |                        |                     |                |                     |

| Z8F0423PB005EG      | 4 KB 1 KB      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005EG      | 4 KB 1 KB      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005EG      | 4 KB 1 KB      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005EG      | 4 KB 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005EG      | 4 KB 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005EG      | 4 KB 1 KB      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005EG      | 4 KB 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005EG      | 4 KB 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005EG      | 4 KB 1 KB      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

#### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

part selection guide 2