Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Obsolete                                                  |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 5MHz                                                      |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 16                                                        |  |

| Program Memory Size        | 2KB (2K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 512 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | A/D 7x10b                                                 |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223hh005sg |  |

# **Table of Contents**

| Revision History                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                                                                                                                                    |

| List of Tables                                                                                                                                                                                                                                                                                                     |

| Overview Features Part Selection Guide Block Diagram CPU and Peripheral Overview General-Purpose I/O Flash Controller Internal Precision Oscillator 10-Bit Analog-to-Digital Converter Analog Comparator Universal Asynchronous Receiver/Transmitter Timers Interrupt Controller Reset Controller On-Chip Debugger |

| Pin Description                                                                                                                                                                                                                                                                                                    |

| Address Space 13 Register File 13 Program Memory 13 Data Memory 15 Flash Information Area 15                                                                                                                                                                                                                       |

| Register Map                                                                                                                                                                                                                                                                                                       |

| Reset and Stop Mode Recovery 21 Reset Types 21 Reset Sources 23 Power-On Reset 23                                                                                                                                                                                                                                  |

| Voltage Brown-Out Reset                                                                                                                                                                                                                                                                                            |

### Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| MULTIPROCESSOR (9-Bit) Mode                                | 103 |

|------------------------------------------------------------|-----|

| External Driver Enable                                     | 105 |

| UART Interrupts                                            | 105 |

| UART Baud Rate Generator                                   | 108 |

| UART Control Register Definitions                          | 108 |

| UART Transmit Data Register                                | 109 |

| UART Receive Data Register                                 | 109 |

| UART Status 0 Register                                     | 110 |

| UART Status 1 Register                                     | 111 |

| UART Control 0 and Control 1 Registers                     | 112 |

| UART Address Compare Register                              | 115 |

| UART Baud Rate High and Low Byte Registers                 | 115 |

| Infrared Encoder/Decoder                                   | 117 |

| Architecture                                               |     |

| Operation                                                  | 117 |

| Transmitting IrDA Data                                     |     |

| Receiving IrDA Data                                        |     |

| Infrared Encoder/Decoder Control Register Definitions      |     |

| Analog-to-Digital Converter                                | 121 |

| Architecture                                               |     |

| Operation                                                  | 122 |

| Automatic Powerdown                                        |     |

| Single-Shot Conversion                                     | 123 |

| Continuous Conversion                                      | 124 |

| Interrupts                                                 | 125 |

| Calibration and Compensation                               | 125 |

| ADC Control Register Definitions                           | 126 |

| ADC Control Register 0                                     | 126 |

| ADC Control/Status Register 1                              | 129 |

| ADC Data High Byte Register                                | 130 |

| ADC Data Low Bits Register                                 | 131 |

| Comparator                                                 | 132 |

| Operation                                                  | 132 |

| Comparator Control Register Definition                     | 133 |

| Flash Memory                                               | 134 |

| Flash Information Area                                     | 135 |

| Operation                                                  | 135 |

| Flash Operation Timing Using the Flash Frequency Registers |     |

| Flash Code Protection Against External Access              | 137 |

## Embedded in Life An IXYS Company

## **Block Diagram**

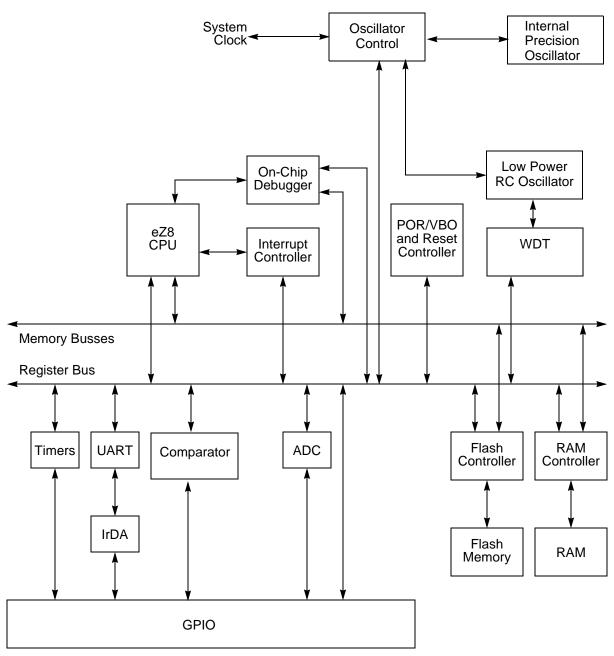

Figure 1 displays a block diagram of the F0823 Series architecture.

Figure 1. Z8 Encore! XP F0823 Series Block Diagram

Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

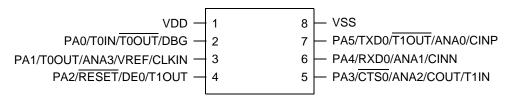

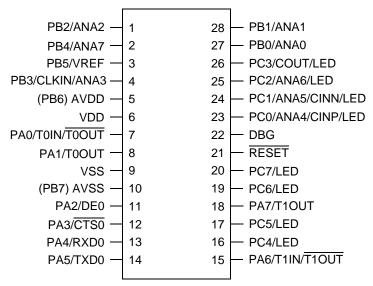

Figure 3. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package\*

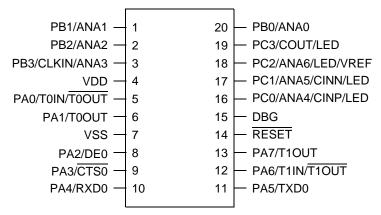

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

# Address Space

The eZ8 CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O Port Control Registers

- The Program Memory contains addresses for all memory locations having executable code and/or data

- The Data Memory contains addresses for all memory locations that contain data only

These three address spaces are covered briefly in the following subsections. For more detailed information regarding the eZ8 CPU and its address space, refer to the eZ8 CPU Core User Manual (UM0128), available for download at www.zilog.com.

## **Register File**

The Register File address space in the Z8 Encore! XP<sup>TM</sup> MCU is 4KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address <code>000H</code> in the Register File address space. Z8 Encore! XP F0823 Series devices contain 256B–1KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

## **Program Memory**

The eZ8 CPU supports 64KB of Program Memory address space. F0823 Series devices contain 1KB to 8KB of on-chip Flash memory in the Program Memory address space. Reading from Program Memory addresses outside the available Flash memory addresses

Table 8. Register File Address Map (Continued)

| Address (Hex)      | Register Description     | Mnemonic | Reset (Hex) | Page<br>No. |

|--------------------|--------------------------|----------|-------------|-------------|

| LED Controller (   | (cont'd)                 |          |             |             |

| F84                | LED Drive Level Low Byte | LEDLVLL  | 00          | <u>53</u>   |

| F85                | Reserved                 | _        | XX          |             |

| Oscillator Contr   | ol                       |          |             |             |

| F86                | Oscillator Control       | OSCCTL   | A0          | <u>172</u>  |

| F87–F8F            | Reserved                 | _        | XX          |             |

| Comparator 0       |                          |          |             |             |

| F90                | Comparator 0 Control     | CMP0     | 14          | 133         |

| F91–FBF            | Reserved                 | _        | XX          |             |

| Interrupt Contro   | ller                     |          |             |             |

| FC0                | Interrupt Request 0      | IRQ0     | 00          | <u>59</u>   |

| FC1                | IRQ0 Enable High Bit     | IRQ0ENH  | 00          | <u>62</u>   |

| FC2                | IRQ0 Enable Low Bit      | IRQ0ENL  | 00          | <u>62</u>   |

| FC3                | Interrupt Request 1      | IRQ1     | 00          | <u>60</u>   |

| FC4                | IRQ1 Enable High Bit     | IRQ1ENH  | 00          | <u>64</u>   |

| FC5                | IRQ1 Enable Low Bit      | IRQ1ENL  | 00          | <u>64</u>   |

| FC6                | Interrupt Request 2      | IRQ2     | 00          | <u>61</u>   |

| FC7                | IRQ2 Enable High Bit     | IRQ2ENH  | 00          | <u>65</u>   |

| FC8                | IRQ2 Enable Low Bit      | IRQ2ENL  | 00          | <u>66</u>   |

| FC9-FCC            | Reserved                 | _        | XX          |             |

| FCD                | Interrupt Edge Select    | IRQES    | 00          | <u>67</u>   |

| FCE                | Shared Interrupt Select  | IRQSS    | 00          | <u>67</u>   |

| FCF                | Interrupt Control        | IRQCTL   | 00          | <u>68</u>   |

| <b>GPIO Port A</b> |                          |          |             |             |

| FD0                | Port A Address           | PAADDR   | 00          | 40          |

| FD1                | Port A Control           | PACTL    | 00          | <u>42</u>   |

| FD2                | Port A Input Data        | PAIN     | XX          | <u>43</u>   |

| FD3                | Port A Output Data       | PAOUT    | 00          | <u>43</u>   |

| GPIO Port B        |                          |          |             | _           |

| FD4                | Port B Address           | PBADDR   | 00          | <u>40</u>   |

| FD5                | Port B Control           | PBCTL    | 00          | <u>42</u>   |

Note: XX=Undefined.

# General-Purpose Input/Output

Z8 Encore! XP F0823 Series products support a maximum of 24 port pins (Ports A–C) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality, and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

## **GPIO Port Availability By Device**

Table 15 lists the port pins available with each device and package type.

Table 15. Port Availability by Device and Package Type

| Devices                                                                                      | Package | 10-Bit ADC | Port A | Port B | Port C | Total I/O |

|----------------------------------------------------------------------------------------------|---------|------------|--------|--------|--------|-----------|

| Z8F0823SB, Z8F0823PB<br>Z8F0423SB, Z8F0423PB<br>Z8F0223SB, Z8F0223PB<br>Z8F0123SB, Z8F0123PB | 8-pin   | Yes        | [5:0]  | No     | No     | 6         |

| Z8F0813SB, Z8F0813PB<br>Z8F0413SB, Z8F0413PB<br>Z8F0213SB, Z8F0213PB<br>Z8F0113SB, Z8F011vPB | 8-pin   | No         | [5:0]  | No     | No     | 6         |

| Z8F0823PH, Z8F0823HH<br>Z8F0423PH, Z8F0423HH<br>Z8F0223PH, Z8F0223HH<br>Z8F0123PH, Z8F0123HH | 20-pin  | Yes        | [7:0]  | [3:0]  | [3:0]  | 16        |

| Z8F0813PH, Z8F0813HH<br>Z8F0413PH, Z8F0413HH<br>Z8F0213PH, Z8F0213HH<br>Z8F0113PH, Z8F0113HH | 20-pin  | No         | [7:0]  | [3:0]  | [3:0]  | 16        |

| Z8F0823PJ, Z8F0823SJ<br>Z8F0423PJ, Z8F0423SJ<br>Z8F0223PJ, Z8F0223SJ<br>Z8F0123PJ, Z8F0123SJ | 28-pin  | Yes        | [7:0]  | [5:0]  | [7:0]  | 22        |

| Z8F0813PJ, Z8F0813SJ<br>Z8F0413PJ, Z8F0413SJ<br>Z8F0213PJ, Z8F0213SJ<br>Z8F0113PJ, Z8F0113SJ | 28-pin  | No         | [7:0]  | [7:0]  | [7:0]  | 24        |

PAO and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. For more details, see the <u>Timers</u> chapter on page 69.

Caution: For pins with multiple alternate functions, Zilog recommends writing to the AFS1 and AFS2 subregisters before enabling the alternate function via the AF Subregister. This prevents spurious transitions through unwanted alternate function modes.

**Table 16. Port Alternate Function Mapping (8-Pin Parts)**

| Port   | Pin | Mnemonic          | Alternate Function Description    | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select<br>Register<br>AFS2 |

|--------|-----|-------------------|-----------------------------------|-----------------------------------------------|-----------------------------------------------------|

| Port A | PA0 | TOIN              | Timer 0 Input                     | AFS1[0]: 0                                    | AFS2[0]: 0                                          |

|        |     | Reserved          |                                   | AFS1[0]: 0                                    | AFS2[0]: 1                                          |

|        |     | Reserved          |                                   | AFS1[0]: 1                                    | AFS2[0]: 0                                          |

|        |     | T0OUT             | Timer 0 Output Complement         | AFS1[0]: 1                                    | AFS2[0]: 1                                          |

|        | PA1 | T0OUT             | Timer 0 Output                    | AFS1[1]: 0                                    | AFS2[1]: 0                                          |

|        |     | Reserved          |                                   | AFS1[1]: 0                                    | AFS2[1]: 1                                          |

|        |     | CLKIN             | External Clock Input              | AFS1[1]: 1                                    | AFS2[1]: 0                                          |

|        |     | Analog Functions* | ADC Analog Input/V <sub>REF</sub> | AFS1[1]: 1                                    | AFS2[1]: 1                                          |

|        | PA2 | DE0               | UART 0 Driver Enable              | AFS1[2]: 0                                    | AFS2[2]: 0                                          |

|        |     | RESET             | External Reset                    | AFS1[2]: 0                                    | AFS2[2]: 1                                          |

|        |     | T1OUT             | Timer 1 Output                    | AFS1[2]: 1                                    | AFS2[2]: 0                                          |

|        |     | Reserved          |                                   | AFS1[2]: 1                                    | AFS2[2]: 1                                          |

|        | PA3 | CTS0              | UART 0 Clear to Send              | AFS1[3]: 0                                    | AFS2[3]: 0                                          |

|        |     | COUT              | Comparator Output                 | AFS1[3]: 0                                    | AFS2[3]: 1                                          |

|        |     | T1IN              | Timer 1 Input                     | AFS1[3]: 1                                    | AFS2[3]: 0                                          |

|        |     | Analog Functions* | ADC Analog Input                  | AFS1[3]: 1                                    | AFS2[3]: 1                                          |

|        | PA4 | RXD0              | UART 0 Receive Data               | AFS1[4]: 0                                    | AFS2[4]: 0                                          |

|        |     | Reserved          |                                   | AFS1[4]: 0                                    | AFS2[4]: 1                                          |

|        |     | Reserved          |                                   | AFS1[4]: 1                                    | AFS2[4]: 0                                          |

|        |     | Analog Functions* | ADC/Comparator Input (N)          | AFS1[4]: 1                                    | AFS2[4]: 1                                          |

|        | PA5 | TXD0              | UART 0 Transmit Data              | AFS1[5]: 0                                    | AFS2[5]: 0                                          |

|        |     | T1OUT             | Timer 1 Output Complement         | AFS1[5]: 0                                    | AFS2[5]: 1                                          |

|        |     | Reserved          |                                   | AFS1[5]: 1                                    | AFS2[5]: 0                                          |

|        |     | Analog Functions* | ADC/Comparator Input (P)          | AFS1[5]: 1                                    | AFS2[5]: 1                                          |

Note: \*Analog Functions include ADC inputs, ADC reference and comparator inputs. Also, alternate function selection as described in the Port A-C Alternate Function Subregisters section on page 43 must be enabled.

- Execution of an Return from Interrupt (IRET) instruction

- Writing a 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Timer Oscillator Fail Trap

### **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all interrupts are enabled with identical interrupt priority (for example, all as Level 2 interrupts), the interrupt priority is assigned from highest to lowest as specified in <u>Table 35</u> on page 55. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2 or Level 3), priority is assigned as specified in Table 35. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Timer Oscillator Fail Trap, and Illegal Instruction Trap always have highest (Level 3) priority.

## Interrupt Assertion

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request register likewise clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

Table 40. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit     | 7        | 6     | 5     | 4      | 3      | 2    | 1     | 0      |

|---------|----------|-------|-------|--------|--------|------|-------|--------|

| Field   | Reserved | T1ENH | T0ENH | U0RENH | U0TENH | Rese | erved | ADCENH |

| RESET   | 0        | 0     | 0     | 0      | 0      | (    | )     | 0      |

| R/W     | R/W      | R/W   | R/W   | R/W    | R/W    | R/   | W     | R/W    |

| Address |          |       |       | FC     | 1H     |      |       |        |

| Bit           | Description                                           |

|---------------|-------------------------------------------------------|

| [7]           | Reserved                                              |

|               | This bit is reserved and must be programmed to 0.     |

| [6]<br>T1ENH  | Timer 1 Interrupt Request Enable High Bit             |

| [5]<br>T0ENH  | Timer 0 Interrupt Request Enable High Bit             |

| [4]<br>U0RENH | UART 0 Receive Interrupt Request Enable High Bit      |

| [3]<br>U0TENH | UART 0 Transmit Interrupt Request Enable High Bit     |

| [2:1]         | Reserved                                              |

|               | These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENH | ADC Interrupt Request Enable High Bit                 |

Table 41. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5     | 4      | 3      | 2    | 1     | 0      |

|---------|----------|-------|-------|--------|--------|------|-------|--------|

| Field   | Reserved | T1ENL | T0ENL | U0RENL | U0TENL | Rese | erved | ADCENL |

| RESET   | 0        | 0     | 0     | 0      | 0      | (    | )     | 0      |

| R/W     | R        | R/W   | R/W   | R/W    | R/W    | F    | ₹     | R/W    |

| Address |          | FC2H  |       |        |        |      |       |        |

| Bit          | Description                                                          |

|--------------|----------------------------------------------------------------------|

| [7]          | Reserved This bit is reserved and must be programmed to 0 when read. |

| [6]<br>T1ENL | Timer 1 Interrupt Request Enable Low Bit                             |

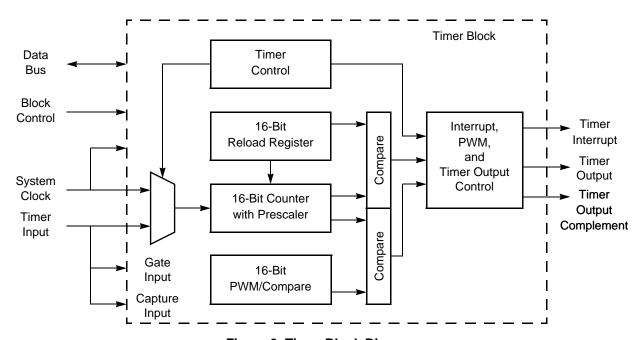

### **Architecture**

Figure 9 displays the architecture of the timers.

Figure 9. Timer Block Diagram

## **Operation**

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer reload. If it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps to configure a timer for ONE-SHOT Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode

- Set the prescale value

- Set the initial output level (High or Low) if using the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps to configure a timer for CONTINUOUS Mode and to initiate the count:

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture or a reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =

$$\frac{(Capture\ Value - Start\ Value) \times Prescale}{System\ Clock\ Frequency\ (Hz)}$$

#### **COMPARE Mode**

In COMPARE Mode, the timer counts up to the 16-bit maximum compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting. Observe the following steps to configure a timer for COMPARE Mode and to initiate the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

- 1. Checks the UART Status 0 Register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data Register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) Mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

## Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 Register, performs flow control on the outgoing transmit datastream. The Clear To Send (CTS) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert CTS at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If CTS deasserts in the middle of a character transmission, the current character is sent completely.

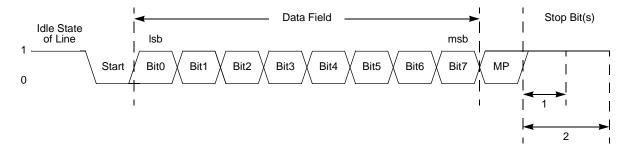

## **MULTIPROCESSOR (9-Bit) Mode**

The UART has a MULTIPROCESSOR (9-bit) Mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTI-PROCESSOR Mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is given below:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) Mode, the parity bit location (9<sup>th</sup> bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPRO-CESSOR (9-bit) Mode control and status information. If an automatic address matching

140

### **Page Erase**

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

## Flash Controller Bypass

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the Zilog application note titled, <u>Third-Party Flash Programming Support for Z8 Encore! MCUs (AN0117)</u>, available for download at <u>www.zilog.com</u>.

#### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

Table 81. Flash Control Register (FCTL)

| Bit     | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|---|---|----|----|---|---|---|

| Field   |   |   |   | FC | MD |   |   |   |

| RESET   | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W     | W | W | W | W  | W  | W | W | W |

| Address |   |   |   | FF | 8H |   |   |   |

| Bit   | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| [7:0] | Flash Command                                                                        |

| FCMD  | 73H = First unlock command.                                                          |

|       | 8CH = Second unlock command.                                                         |

|       | 95H = Page Erase command (must be third command in sequence to initiate Page Erase). |

|       | 63H = Mass Erase command (must be third command in sequence to initiate Mass Erase). |

|       | 5EH = Enable Flash Sector Protect Register Access.                                   |

Table 118. eZ8 CPU Instruction Summary (Continued)

| Assembly  |                           |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|-----------|---------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic  | Symbolic Operation        | dst | src         | (Hex)       |   | Z | S   | ٧   | D | Н | Cycles  |        |

| POPX dst  | dst ← @SP<br>SP ← SP + 1  | ER  |             | D8          | _ | - | _   | -   | - | - | 3       | 2      |

| PUSH src  | SP ← SP – 1               | R   |             | 70          | - | - | -   | -   | - | - | 2       | 2      |

|           | @SP ← src                 | IR  |             | 71          | • |   |     |     |   |   | 2       | 3      |

|           |                           | IM  |             | IF70        |   |   |     |     |   |   | 3       | 2      |

| PUSHX src | SP ← SP − 1<br>@SP ← src  | ER  |             | C8          | _ | _ | _   | _   | _ | _ | 3       | 2      |

| RCF       | C ← 0                     |     |             | CF          | 0 | _ | _   | _   | _ | _ | 1       | 2      |

| RET       | PC ← @SP<br>SP ← SP + 2   |     |             | AF          | - | - | -   | -   | - | - | 1       | 4      |

| RL dst    |                           | R   |             | 90          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 91          | - |   |     |     |   |   | 2       | 3      |

| RLC dst   | <u> </u>                  | R   |             | 10          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 11          | - |   |     |     |   |   | 2       | 3      |

| RR dst    |                           | R   |             | E0          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  |             | E1          | - |   |     |     |   |   | 2       | 3      |

| RRC dst   |                           | R   |             | C0          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  |             | C1          | • |   |     |     |   |   | 2       | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

### **DC Characteristics**

Table 121 lists the DC characteristics of the Z8 Encore! XP F0823 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

**Table 121. DC Characteristics**

|                  |                              | T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise specified) |                |                      |       |                                                                                                                                                  |

|------------------|------------------------------|------------------------------------------------------------------|----------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                    | Minimum                                                          | Typical        | Maximum              | Units | Conditions                                                                                                                                       |

| $V_{DD}$         | Supply Voltage               | 2.7                                                              | _              | 3.6                  | V     |                                                                                                                                                  |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                                                             | _              | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                  |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub>                                              | -              | 5.5                  | V     | For all input pins without analog or oscillator function. For all signal pins on the 8-pin devices. Programmable pull-ups must also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub>                                              | -              | V <sub>DD</sub> +0.3 | V     | For those pins with analog or oscillator function (20-/28-pin devices only), or when programmable pull-ups are enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | _                                                                | _              | 0.4                  | V     | I <sub>OL</sub> = 2mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                    |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                                                              | _              | _                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | _                                                                | _              | 0.6                  | V     | I <sub>OL</sub> = 20mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                    |

| V <sub>OH2</sub> | High Level Output<br>Voltage | 2.4                                                              | _              | -                    | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                  |

| I <sub>IH</sub>  | Input Leakage Cur-<br>rent   | _                                                                | <u>+</u> 0.002 | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 \text{ V}$                                                                                                    |

| I <sub>IL</sub>  | Input Leakage Cur-<br>rent   | _                                                                | <u>+</u> 0.007 | <u>+</u> 5           | μΑ    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 \text{ V}$                                                                                                    |

| I <sub>TL</sub>  | Tristate Leakage<br>Current  | _                                                                | -              | <u>+</u> 5           | μΑ    |                                                                                                                                                  |

#### Notes:

- 1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

- 2. These values are provided for design guidance only and are not tested in production.

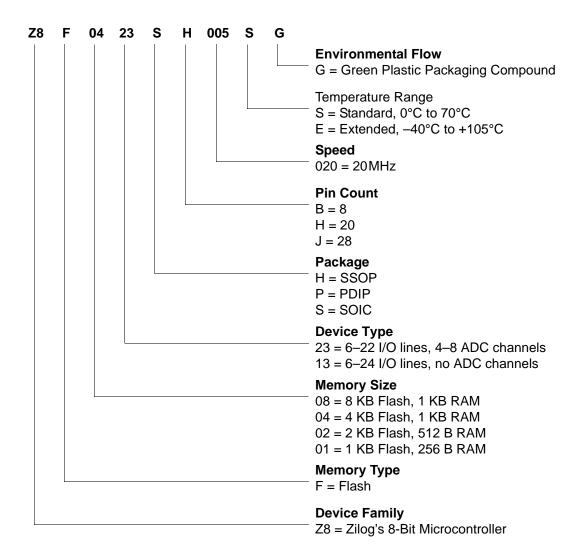

## **Part Number Suffix Designations**

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0423SH005SG is an 8-bit 20MHz Flash MCU with 4KB of Program Memory and equipped with 6–22 I/O lines and 4–8 ADC channels in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

# Index

| Numerics                                                                                                                                                                                                                                                                                             | b 176                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-bit ADC 4                                                                                                                                                                                                                                                                                         | baud rate generator, UART 108<br>BCLR 179                                                                                                                                                                                         |

| A absolute maximum ratings 196 AC characteristics 200 ADC 178 architecture 121 block diagram 122 continuous conversion 124 control register 126, 129 control register definitions 126 data high byte register 130 data low bits register 131 electrical characteristics and timing 203 operation 122 | binary number suffix 177 BIT 179 bit 176 clear 179 manipulation instructions 179 set 179 set or clear 179 swap 179 test and jump 181 test and jump if non-zero 181 bit jump and test if non-zero 181 bit swap 181 block diagram 3 |

| single-shot conversion 123 ADCCTL register 126, 129 ADCDH register 130 ADCDL register 131 ADCX 178 ADD 178 add - extended addressing 178 add with carry 178                                                                                                                                          | block transfer instructions 179<br>BRK 181<br>BSET 179<br>BSWAP 179, 181<br>BTJ 181<br>BTJNZ 181<br>BTJZ 181                                                                                                                      |

| add with carry - extended addressing 178 additional symbols 177 address space 13 ADDX 178 analog signals 10 analog-to-digital converter (ADC) 121 AND 181 ANDX 181 arithmetic instructions 178 assembly language programming 174 assembly language syntax 175                                        | CALL procedure 181 CAPTURE mode 89 CAPTURE/COMPARE mode 89 cc 176 CCF 180 characteristics, electrical 196 clear 180 CLR 180 COM 181 COMPARE 89 compare - extended addressing 178                                                  |

| <b>B</b> B 177                                                                                                                                                                                                                                                                                       | COMPARE mode 89 compare with carry 178                                                                                                                                                                                            |