Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223hj005eg |

#### Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| Flash Code Protection Against Accidental Program and Erasure | 137 |

|--------------------------------------------------------------|-----|

| Byte Programming                                             | 139 |

| Page Erase                                                   | 139 |

| Mass Erase                                                   | 139 |

| Flash Controller Bypass                                      | 140 |

| Flash Controller Behavior in DEBUG Mode                      | 140 |

| Flash Control Register Definitions                           | 141 |

| Flash Control Register                                       | 141 |

| Flash Status Register                                        | 142 |

| Flash Page Select Register                                   | 142 |

| Flash Sector Protect Register                                | 144 |

| Flash Frequency High and Low Byte Registers                  | 144 |

| Flash Option Bits                                            | 146 |

| Operation                                                    |     |

| Option Bit Configuration By Reset                            |     |

| Option Bit Types                                             |     |

| Reading the Flash Information Page                           |     |

| Flash Option Bit Control Register Definitions                |     |

| Trim Bit Address Register                                    |     |

| Trim Bit Data Register                                       |     |

| Flash Option Bit Address Space                               |     |

| Trim Bit Address Space                                       |     |

| Zilog Calibration Data                                       |     |

| ADC Calibration Data                                         |     |

| Serialization Data                                           |     |

| Randomized Lot Identifier                                    |     |

|                                                              |     |

| On-Chip Debugger                                             |     |

| Architecture                                                 |     |

| Operation                                                    |     |

| OCD Interface                                                |     |

| DEBUG Mode                                                   |     |

| OCD Data Format                                              |     |

| OCD Autobaud Detector/Generator                              |     |

| OCD Serial Errors                                            |     |

| OCD Unlock Sequence (8-Pin Devices Only)                     |     |

| Breakpoints                                                  |     |

| Runtime Counter                                              |     |

| On-Chip Debugger Commands                                    |     |

| On-Chip Debugger Control Register Definitions                |     |

| OCD Control Register                                         | 166 |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Table 70.  | UART Address Compare Register (U0ADDR)                 | 115 |

|------------|--------------------------------------------------------|-----|

| Table 71.  | UART Baud Rate High Byte Register (U0BRH)              | 115 |

| Table 72.  | UART Baud Rate Low Byte Register (U0BRL)               | 115 |

| Table 73.  | UART Baud Rates                                        | 116 |

| Table 74.  | ADC Control Register 0 (ADCCTL0)                       | 127 |

| Table 75.  | ADC Control/Status Register 1 (ADCCTL1)                | 129 |

| Table 76.  | ADC Data High Byte Register (ADCD_H)                   | 130 |

| Table 77.  | ADC Data Low Bits Register (ADCD_L)                    | 131 |

| Table 78.  | Comparator Control Register (CMP0)                     | 133 |

| Table 79.  | Z8 Encore! XP F0823 Series Flash Memory Configurations | 134 |

| Table 80.  | Flash Code Protection Using the Flash Option Bits      | 138 |

| Table 81.  | Flash Control Register (FCTL)                          | 141 |

| Table 82.  | Flash Status Register (FSTAT)                          | 142 |

| Table 83.  | Flash Page Select Register (FPS)                       | 143 |

| Table 84.  | Flash Sector Protect Register (FPROT)                  | 144 |

| Table 85.  | Flash Frequency High Byte Register (FFREQH)            | 145 |

| Table 86.  | Flash Frequency Low Byte Register (FFREQL)             |     |

| Table 87.  | Trim Bit Address Register (TRMADR)                     | 148 |

| Table 88.  | Trim Bit Data Register (TRMDR)                         | 149 |

| Table 89.  | Flash Option Bits at Program Memory Address 0000H      | 149 |

| Table 90.  | Flash Options Bits at Program Memory Address 0001H     | 150 |

| Table 91.  | Trim Options Bits at Address 0000H                     | 151 |

| Table 92.  | Trim Option Bits at 0001H                              | 152 |

| Table 93.  | Trim Option Bits at 0002H (TIPO)                       | 152 |

| Table 94.  | ADC Calibration Bits                                   | 153 |

| Table 95.  | ADC Calibration Data Location                          | 153 |

| Table 96.  | Serial Number at 001C-001F (S_NUM)                     | 154 |

| Table 97.  | Serialization Data Locations                           | 154 |

| Table 98.  | Lot Identification Number (RAND_LOT)                   | 154 |

| Table 99.  | Randomized Lot ID Locations                            | 155 |

| Table 100. | OCD Baud-Rate Limits                                   | 160 |

| Table 101. | OCD Commands                                           | 162 |

| Table 102. | OCD Control Register (OCDCTL)                          | 167 |

| Table 103. | OCD Status Register (OCDSTAT)                          | 168 |

|            | Oscillator Configuration and Selection                 |     |

| Table 105. | Oscillator Control Register (OSCCTL)                   | 172 |

|            |                                                        |     |

#### **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit central processing unit (CPU), meets the continuing demand for faster and code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access of up to 4 KB

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the eZ8 CPU Core User Manual (UM0128) available for download at www.zilog.com.

#### General-Purpose I/O

F0823 Series features 6 to 24 port pins (Ports A-C) for general-purpose I/O (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable. 5 V-tolerant input pins are available on all I/Os on 8-pin devices, most I/Os on other package types.

#### Flash Controller

The Flash Controller programs and erases Flash memory. The Flash Controller supports protection against accidental program and erasure, as well as factory serialization and read protection.

## Pin Description

Z8 Encore! XP F0823 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and pin configurations available for each of the package styles. For information about physical package specifications, see the Packaging chapter on page 210.

#### **Available Packages**

Table 2 lists the package styles that are available for each device in the F0823 Series product line.

Part 8-pin 8-pin 20-pin 20-pin 20-pin 28-pin 28-pin 28-pin 8-pin QFN/ Number **ADC PDIP** SOIC **PDIP** SOIC **SSOP PDIP** SOIC **SSOP** MLF-S Z8F0823 Yes Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Z8F0813 No Z8F0423 Yes Χ Χ Χ Χ Χ Χ Χ Χ Χ Z8F0413 Χ Χ Χ Χ Χ Χ Χ Χ Χ No Z8F0223 Yes Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Χ Z8F0213 Χ Χ Χ No Χ Z8F0123 Yes Χ Χ Χ Χ Χ Χ Χ Χ Z8F0113 Χ Χ Χ Χ Χ Χ Χ Χ Χ No

**Table 2. F0823 Series Package Options**

#### **Pin Configurations**

Figures 2 through 4 display the pin configurations for all packages available in the F0823 Series. For description of signals, see Table 3. The analog input alternate functions (ANAx) are not available on the Z8F0x13 devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all pins of Ports A, B, and C default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general-purpose input ports until programmed otherwise.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

**Table 3. Signal Descriptions (Continued)**

| Signal Mnemonic               | I/O | Description                                                                                                                                                                                                           |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COUT                          | 0   | Comparator Output. This is the output of the comparator.                                                                                                                                                              |

| Analog                        |     |                                                                                                                                                                                                                       |

| ANA[7:0]                      | I   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                          | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                   |     |                                                                                                                                                                                                                       |

| CLKIN                         | I   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                   |     |                                                                                                                                                                                                                       |

| LED                           | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                           |

| On-Chip Debugger              |     |                                                                                                                                                                                                                       |

| DBG                           | I/O | Debug. This signal is the control and data input and output to and from the OCD.  Caution: The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                            |

| Reset                         |     |                                                                                                                                                                                                                       |

| RESET                         | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                  |     |                                                                                                                                                                                                                       |

| $V_{DD}$                      | ļ   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> <sup>2</sup> | I   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>               | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>              | I   | Analog Ground.                                                                                                                                                                                                        |

| Notos:                        |     |                                                                                                                                                                                                                       |

- 1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are

- replaced by AV<sub>DD</sub> and AV<sub>SS</sub>.

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

### Reset and Stop Mode Recovery

The Reset Controller within the Z8 Encore! XP F0823 Series controls Reset and Stop Mode Recovery operation and provides indication of low supply voltage conditions. In typical operation, the following events cause a Reset:

- Power-On Reset (POR)

- Voltage Brown-Out (VBO)

- Watchdog Timer time-out (when configured by the WDT\_RES Flash Option Bit to initiate a reset)

- External RESET pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the device is in STOP Mode, a Stop Mode Recovery is initiated by either of the following:

- Watchdog Timer time-out

- GPIO port input pin transition on an enabled Stop Mode Recovery source

The VBO circuitry on the device performs the following function:

Generates the VBO reset when the supply voltage drops below a minimum safe level

#### **Reset Types**

F0823 Series MCUs provide several different types of Reset operations. Stop Mode Recovery is considered a form of Reset. Table 9 lists the types of Reset and their operating characteristics. The duration of a System Reset is longer if the external crystal oscillator is enabled by the Flash option bits; this configuration allows additional time for oscillator startup.

Table 9. Reset and Stop Mode Recovery Characteristics and Latency

|                       | Reset Characteristics and Latency                |         |                                                               |  |  |  |

|-----------------------|--------------------------------------------------|---------|---------------------------------------------------------------|--|--|--|

| Reset Type            | Control Registers                                | eZ8 CPU | Reset Latency (Delay)                                         |  |  |  |

| System Reset          | Reset (as applicable)                            | Reset   | 66 Internal Precision Oscillator Cycles                       |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except WDT_CTL and OSC_CTL registers | Reset   | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |

Table 17. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>4</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

|                     |     | ANA6/V <sub>REF</sub> <sup>6</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

#### Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in the <u>Port A–C Alternate Function</u> Subregisters section on page 43 automatically enables the associated alternate function.

- 2. Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in the <u>Timer Pin Signal Operation</u> section on page 83.

- 3. Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, alternate function selection as described in the <a href="Port A-C Alternate Function Subregisters">Port A-C Alternate Function Subregisters</a> section on page 43 must also be enabled.

- 4. V<sub>REE</sub> is available on PB5 in 28-pin products only.

- 5. Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in the <a href="Port A-C Alternate Function Subregisters">Port A-C Alternate Function Subregisters</a> section on page 43 must also be enabled.

- 6. V<sub>REF</sub> is available on PC2 in 20-pin parts only.

#### **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3mA, 7mA, 13mA, and 20mA. This mode is enabled through the LED control registers. The LED Drive Enable (LEDEN) register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

#### Port A-C Alternate Function Set 1 Subregisters

The Port A–C Alternate Function Set1 Subregister (Table 28) is accessed through the Port A–C Control Register by writing 07H to the Port A–C Address Register. The Alternate Function Set 1 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in "GPIO Alternate Functions" on page 34.

**Note:** Alternate function selection on port pins must also be enabled as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43.

Table 28. Port A–C Alternate Function Set 1 Subregisters (PAFS1x)

| Bit     | 7         | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|-----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Field   | PAFS17    | PAFS16                                                                                | PAFS15 | PAFS14 | PAFS13 | PAFS12 | PAFS11 | PAFS10 |

| RESET   |           | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device)                    |        |        |        |        |        |        |

| R/W     | R/W       | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | If 07H ir | If 07H in Port A–C Address Register, accessible through the Port A–C Control Register |        |        |        |        |        |        |

| Bit    | Description                                                                                                               |

|--------|---------------------------------------------------------------------------------------------------------------------------|

| [7:0]  | Port Alternate Function Set to 1                                                                                          |

| PAFS1x | 0 = Port Alternate Function selected as defined in Table 15 (see the <u>GPIO Alternate Functions</u> section on page 34). |

|        | 1 = Port Alternate Function selected as defined in Table 15 (see the <u>GPIO Alternate Functions</u> section on page 34). |

Note: x indicates the specific GPIO port pin number (7–0).

#### Port A-C Input Data Registers

Reading from the Port A–C Input Data registers (Table 30) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

Table 30. Port A-C Input Data Registers (PxIN)

| Bit     | 7    | 6                | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------------------|------|------|------|------|------|------|

| Field   | PIN7 | PIN6             | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET   | Х    | Х                | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W     | R    | R                | R    | R    | R    | R    | R    | R    |

| Address |      | FD2H, FD6H, FDAH |      |      |      |      |      |      |

| Bit   | Description                                          |

|-------|------------------------------------------------------|

| [7:0] | Port Input Data                                      |

| PxIN  | Sampled data from the corresponding port pin input.  |

|       | 0 = Input data is logical 0 (Low).                   |

|       | 1 = Input data is logical 1 (High).                  |

| Note: | x indicates the specific GPIO port pin number (7–0). |

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{CTS}$  pin.

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Write the UART Control 1 Register to select the multiprocessor bit for the byte to be transmitted:

- Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 3. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 4. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data Register to again become empty.

#### **Receiving Data Using the Polled Method**

Observe the following steps to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set an acceptable baud rate for the incoming data stream.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable MULTIPROCESSOR Mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if Multiprocessor mode is not enabled, and select either even or odd parity

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to <a href="Step 6">Step 6</a>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

- 6. Read data from the UART Receive Data Register. If operating in MULTIPROCESSOR (9-bit) Mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 1. Checks the UART Status 0 Register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data Register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) Mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

### Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 Register, performs flow control on the outgoing transmit datastream. The Clear To Send (CTS) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert CTS at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If CTS deasserts in the middle of a character transmission, the current character is sent completely.

#### **MULTIPROCESSOR (9-Bit) Mode**

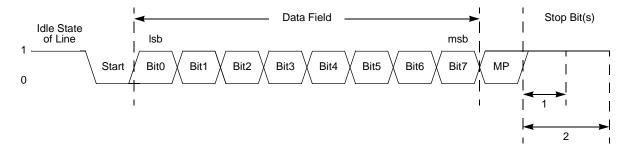

The UART has a MULTIPROCESSOR (9-bit) Mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTI-PROCESSOR Mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is given below:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) Mode, the parity bit location (9<sup>th</sup> bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPRO-CESSOR (9-bit) Mode control and status information. If an automatic address matching

### Analog-to-Digital Converter

The Analog-to-Digital Converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 10-bit resolution

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Bandgap generated internal voltage reference generator with two selectable levels

- Factory offset and gain calibration

#### **Architecture**

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

#### **Automatic Powerdown**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to powerup. The ADC powers up when a conversion is requested by the ADC Control Register.

#### **Single-Shot Conversion**

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the acceptable analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}

#### **ADC Data High Byte Register**

The ADC Data High Byte Register contains the upper eight bits of the ADC output. The output is an 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

Table 76. ADC Data High Byte Register (ADCD\_H)

| Bit     | 7 | 6     | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|-------|---|----|----|---|---|---|

| Field   |   | ADCDH |   |    |    |   |   |   |

| RESET   | Х | X     | Х | X  | X  | X | X | Х |

| R/W     | R | R     | R | R  | R  | R | R | R |

| Address |   |       |   | F7 | 2H |   |   |   |

| Bit   | Description                                                                                       |

|-------|---------------------------------------------------------------------------------------------------|

| [7:0] | ADC Data High Byte                                                                                |

| ADCDH | This byte contains the upper eight bits of the ADC output. These bits are not valid during a sin- |

|       | gle-shot conversion. During a continuous conversion, the most recent conversion output is         |

|       | held in this register. These bits are undefined after a Reset.                                    |

#### **Page Erase**

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

#### Flash Controller Bypass

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the Zilog application note titled, <u>Third-Party Flash Programming Support for Z8 Encore! MCUs (AN0117)</u>, available for download at <u>www.zilog.com</u>.

#### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

Table 81. Flash Control Register (FCTL)

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|---|---|---|---|---|---|---|

| Field   | FCMD |   |   |   |   |   |   |   |

| RESET   | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W     | W    | W | W | W | W | W | W | W |

| Address | FF8H |   |   |   |   |   |   |   |

| Bit   | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| [7:0] | Flash Command                                                                        |

| FCMD  | 73H = First unlock command.                                                          |

|       | 8CH = Second unlock command.                                                         |

|       | 95H = Page Erase command (must be third command in sequence to initiate Page Erase). |

|       | 63H = Mass Erase command (must be third command in sequence to initiate Mass Erase). |

|       | 5EH = Enable Flash Sector Protect Register Access.                                   |

Table 107. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Z8 Encore! XP Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

#### **eZ8 CPU Instruction Notation**

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is noted in Table 108.

**Table 108. Notational Shorthand**

| Notation | Description                    | Operand | Range                                                                             |

|----------|--------------------------------|---------|-----------------------------------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                  |

| CC       | Condition Code                 | _       | See the Condition Codes overview in the <u>eZ8 CPU</u> Core User Manual (UM0128). |

| DA       | Direct Address                 | Addrs   | Addrs represents a number in the range of 0000H to FFFFH.                         |

| ER       | Extended Addressing Register   | Reg     | Reg represents a number in the range of 000H to FFFH.                             |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH.                                              |

| Ir       | Indirect Working Register      | @Rn     | n = 0–15.                                                                         |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH.                              |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                 |

| IRR      | Indirect Register Pair         | @Reg    | Reg represents an even number in the range 00H to FEH                             |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                         |

| r        | Working Register               | Rn      | n = 0–15.                                                                         |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH.                              |

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

|                                            |               |           |            |                        |                     |                | (                   |

|--------------------------------------------|---------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                                | Flash<br>RAM  | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 Series with 4 KB Flash |               |           |            |                        |                     |                |                     |

| Standard Temperatu                         | re: 0°C to 70 | °C        |            |                        |                     |                |                     |

| Z8F0413PB005SG                             | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005SG                             | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005SG                             | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005SG                             | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005SG                             | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005SG                             | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005SG                             | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005SG                             | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005SG                             | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperature: -40°C to 105°C       |               |           |            |                        |                     |                |                     |

| Z8F0413PB005EG                             | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005EG                             | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005EG                             | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005EG                             | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005EG                             | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005EG                             | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005EG                             | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005EG                             | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005EG                             | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| G                                                | indirect register pair 176          |

|--------------------------------------------------|-------------------------------------|

| GATED mode 89                                    | indirect working register 176       |

| general-purpose I/O 33                           | indirect working register pair 176  |

| GPIO 4, 33                                       | infrared encoder/decoder (IrDA) 117 |

| alternate functions 34                           | Instruction Set 174                 |

| architecture 34                                  | instruction set, eZ8 CPU 174        |

| control register definitions 40                  | instructions                        |

| input data sample timing 204                     | ADC 178                             |

| interrupts 40                                    | ADCX 178                            |

| port A-C pull-up enable sub-registers 47, 48, 49 | ADD 178                             |

| port A-H address registers 41                    | ADDX 178                            |

| port A-H alternate function sub-registers 43     | AND 181                             |

| port A-H control registers 42                    | ANDX 181                            |

| port A-H data direction sub-registers 43         | arithmetic 178                      |

| port A-H high drive enable sub-registers 45      | BCLR 179                            |

| port A-H input data registers 50                 | BIT 179                             |

| port A-H output control sub-registers 44         | bit manipulation 179                |

| port A-H output data registers 51                | block transfer 179                  |

| port A-H stop mode recovery sub-registers 46     | BRK 181                             |

| port availability by device 33                   | BSET 179                            |

| port input timing 205                            | BSWAP 179, 181                      |

| port output timing 206                           | BTJ 181                             |

|                                                  | BTJNZ 181                           |

|                                                  | BTJZ 181                            |

| Н                                                | CALL 181                            |

| H 177                                            | CCF 179, 180                        |

| HALT 180                                         | CLR 180                             |

| halt mode 31, 180                                | COM 181                             |

| hexadecimal number prefix/suffix 177             | CP 178                              |

|                                                  | CPC 178                             |

|                                                  | CPCX 178                            |

| I                                                | CPU control 180                     |

| I2C 4                                            | CPX 178                             |

| IM 176                                           | DA 178                              |

| immediate data 176                               | DEC 178                             |

| immediate operand prefix 177                     | DECW 178                            |

| INC 178                                          | DI 180                              |

| increment 178                                    | DJNZ 181                            |

| increment word 178                               | EI 180                              |

| INCW 178                                         | HALT 180                            |

| indexed 177                                      | INC 178                             |

| indirect address prefix 177                      | INCW 178                            |

| indirect register 176                            | IRET 181                            |

| mancet register 170                              | JP 181                              |

| read OCD revision (00H) 163                          | power supply signals 10                          |

|------------------------------------------------------|--------------------------------------------------|

| read OCD status register (02H) 163                   | Power-on and Voltage Brownout electrical charac- |

| read program counter (07H) 164                       | teristics and timing 201                         |

| read program memory (0BH) 164                        | Power-On Reset (POR) 23                          |

| read program memory CRC (0EH) 165                    | program control instructions 181                 |

| read register (09H) 164                              | program counter 177                              |

| read runtime counter (03H) 163                       | program memory 13                                |

| step instruction (10H) 165                           | PUSH 180                                         |

| stuff instruction (11H) 166                          | push using extended addressing 180               |

| write data memory (0CH) 165                          | PUSHX 180                                        |

| write OCD control register (04H) 163                 | PWM mode 89                                      |

| write program counter (06H) 163                      | PxADDR register 41                               |

| write program memory (0AH) 164                       | PxCTL register 42                                |

| write register (08H) 164                             |                                                  |

| on-chip debugger (OCD) 156                           | _                                                |

| on-chip debugger signals 10                          | R                                                |

| ONE-SHOT mode 88                                     | R 176                                            |

| opcode map                                           | r 176                                            |

| abbreviations 193                                    | RA                                               |

| cell description 192                                 | register address 177                             |

| first 194                                            | RCF 179, 180                                     |

| second after 1FH 195                                 | receive                                          |

| Operational Description 21, 30, 33, 69, 91, 97, 117, | IrDA data 119                                    |

| 121, 132, 134, 146, 156, 169, 173                    | receiving UART data-interrupt-driven method 102  |

| OR 181                                               | receiving UART data-polled method 101            |

| ordering information 211                             | register 176                                     |

| ORX 181                                              | ADC control (ADCCTL) 126, 129                    |

|                                                      | ADC data high byte (ADCDH) 130                   |

| <b>B</b>                                             | ADC data low bits (ADCDL) 131                    |

| P                                                    | flash control (FCTL) 141, 148, 149               |

| p 176                                                | flash high and low byte (FFREQH and FRE-         |

| Packaging 210                                        | EQL) 144                                         |

| part selection guide 2                               | flash page select (FPS) 142, 144                 |

| PC 177                                               | flash status (FSTAT) 142                         |

| peripheral AC and DC electrical characteristics 201  | GPIO port A-H address (PxADDR) 41                |

| pin characteristics 11                               | GPIO port A-H alternate function sub-registers   |

| Pin Descriptions 7                                   | 44                                               |

| polarity 176                                         | GPIO port A-H control address (PxCTL) 42         |

| POP 180                                              | GPIO port A-H data direction sub-registers 43    |

| pop using extended addressing 180                    | OCD control 166                                  |

| POPX 180                                             | OCD status 168                                   |

| port availability, device 33                         | UARTx baud rate high byte (UxBRH) 115            |

| port input timing (GPIO) 205                         | UARTx baud rate low byte (UxBRL) 115             |

| port output timing, GPIO 206                         | UARTx Control 0 (UxCTL0) 112, 115                |