Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223pb005sg |

# Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| Flash Code Protection Against Accidental Program and Erasure | 137 |

|--------------------------------------------------------------|-----|

| Byte Programming                                             | 139 |

| Page Erase                                                   | 139 |

| Mass Erase                                                   | 139 |

| Flash Controller Bypass                                      | 140 |

| Flash Controller Behavior in DEBUG Mode                      | 140 |

| Flash Control Register Definitions                           | 141 |

| Flash Control Register                                       | 141 |

| Flash Status Register                                        | 142 |

| Flash Page Select Register                                   | 142 |

| Flash Sector Protect Register                                | 144 |

| Flash Frequency High and Low Byte Registers                  | 144 |

| Flash Option Bits                                            | 146 |

| Operation                                                    |     |

| Option Bit Configuration By Reset                            |     |

| Option Bit Types                                             |     |

| Reading the Flash Information Page                           |     |

| Flash Option Bit Control Register Definitions                |     |

| Trim Bit Address Register                                    |     |

| Trim Bit Data Register                                       |     |

| Flash Option Bit Address Space                               |     |

| Trim Bit Address Space                                       |     |

| Zilog Calibration Data                                       |     |

| ADC Calibration Data                                         |     |

| Serialization Data                                           |     |

| Randomized Lot Identifier                                    |     |

|                                                              |     |

| On-Chip Debugger                                             |     |

| Architecture                                                 |     |

| Operation                                                    |     |

| OCD Interface                                                |     |

| DEBUG Mode                                                   |     |

| OCD Data Format                                              |     |

| OCD Autobaud Detector/Generator                              |     |

| OCD Serial Errors                                            |     |

| OCD Unlock Sequence (8-Pin Devices Only)                     |     |

| Breakpoints                                                  |     |

| Runtime Counter                                              |     |

| On-Chip Debugger Commands                                    |     |

| On-Chip Debugger Control Register Definitions                |     |

| OCD Control Register                                         | 166 |

#### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

### 10-Bit Analog-to-Digital Converter

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

### **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

#### **Timers**

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

# **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

#### **Reset Controller**

Z8 Encore!  $XP^{\textcircled{0}}$  F0823 Series products can be reset using the  $\overline{RESET}$  pin, POR, WDT time-out, STOP Mode exit, or Voltage Brown-Out warning signal. The  $\overline{RESET}$  pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

**Table 3. Signal Descriptions (Continued)**

| Signal Mnemonic               | I/O | Description                                                                                                                                                                                                           |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COUT                          | 0   | Comparator Output. This is the output of the comparator.                                                                                                                                                              |

| Analog                        |     |                                                                                                                                                                                                                       |

| ANA[7:0]                      | I   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                          | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                   |     |                                                                                                                                                                                                                       |

| CLKIN                         | I   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                   |     |                                                                                                                                                                                                                       |

| LED                           | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                           |

| On-Chip Debugger              |     |                                                                                                                                                                                                                       |

| DBG                           | I/O | Debug. This signal is the control and data input and output to and from the OCD.  Caution: The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                            |

| Reset                         |     |                                                                                                                                                                                                                       |

| RESET                         | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                  |     |                                                                                                                                                                                                                       |

| $V_{DD}$                      | ļ   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> <sup>2</sup> | I   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>               | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>              | I   | Analog Ground.                                                                                                                                                                                                        |

| Notos:                        |     |                                                                                                                                                                                                                       |

- 1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are

- replaced by AV<sub>DD</sub> and AV<sub>SS</sub>.

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

Table 8. Register File Address Map (Continued)

| Address (Hex)    | Register Description                  | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------------------|----------|-------------|-------------|

| GPIO Port B (co  | nt'd)                                 |          |             |             |

| FD6              | Port B Input Data                     | PBIN     | XX          | <u>43</u>   |

| FD7              | Port B Output Data                    | PBOUT    | 00          | <u>43</u>   |

| GPIO Port C      |                                       |          |             |             |

| FD8              | Port C Address                        | PCADDR   | 00          | <u>40</u>   |

| FD9              | Port C Control                        | PCCTL    | 00          | <u>42</u>   |

| FDA              | Port C Input Data                     | PCIN     | XX          | <u>43</u>   |

| FDB              | Port C Output Data                    | PCOUT    | 00          | <u>43</u>   |

| FDC-FEF          | Reserved                              | _        | XX          |             |

| Watchdog Time    | r (WDT)                               |          |             |             |

| FF0              | Reset Status                          | RSTSTAT  | XX          | <u>94</u>   |

|                  | Watchdog Timer Control                | WDTCTL   | XX          | <u>94</u>   |

| FF1              | Watchdog Timer Reload Upper Byte      | WDTU     | FF          | <u>95</u>   |

| FF2              | Watchdog Timer Reload High Byte       | WDTH     | FF          | <u>95</u>   |

| FF3              | Watchdog Timer Reload Low Byte        | WDTL     | FF          | <u>95</u>   |

| FF4–FF5          | Reserved                              | _        | XX          |             |

| Trim Bit Control |                                       |          |             |             |

| FF6              | Trim Bit Address                      | TRMADR   | 00          | <u>148</u>  |

| FF7              | Trim Data                             | TRMDR    | XX          | <u>149</u>  |

| Flash Memory C   | Controller                            |          |             |             |

| FF8              | Flash Control                         | FCTL     | 00          | <u>141</u>  |

| FF8              | Flash Status                          | FSTAT    | 00          | <u>142</u>  |

| FF9              | Flash Page Select                     | FPS      | 00          | <u>143</u>  |

|                  | Flash Sector Protect                  | FPROT    | 00          | <u>144</u>  |

| FFA              | Flash Programming Frequency High Byte | FFREQH   | 00          | <u>145</u>  |

| FFB              | Flash Programming Frequency Low Byte  | FFREQL   | 00          | <u>145</u>  |

Note: XX=Undefined.

# **Low-Power Modes**

Z8 Encore! XP F0823 Series products contain power-saving features. The highest level of power reduction is provided by the STOP Mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT Mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in ACTIVE mode (defined as being in neither STOP nor HALT Mode).

#### **STOP Mode**

Executing the eZ8 CPU's Stop instruction places the device into STOP Mode, powering down all peripherals except the Voltage Brown-Out detector, and the Watchdog Timer. These two blocks may also be disabled for additional power savings. In STOP Mode, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; X<sub>IN</sub> and X<sub>OUT</sub> (if previously enabled) are disabled, and PAO/PA1 revert to the states programmed by the GPIO registers

- System clock is stopped

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control Register

- If enabled, the Watchdog Timer logic continues to operate

- If enabled for operation in STOP Mode by the associated Flash Option Bit, the Voltage Brown-Out protection circuit continues to operate

- All other on-chip peripherals are idle

To minimize current in STOP Mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP Mode using Stop Mode Recovery. For more information about Stop Mode Recovery, see the Reset and Stop Mode Recovery chapter on page 21.

Table 18. GPIO Port Registers and Subregisters (Continued)

| Port Register<br>Mnemonic | Port Register Name                |

|---------------------------|-----------------------------------|

| P <i>x</i> HDE            | High Drive Enable.                |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable. |

| P <i>x</i> PUE            | Pull-up Enable.                   |

| PxAFS1                    | Alternate Function Set 1.         |

| PxAFS2                    | Alternate Function Set 2.         |

# Port A-C Address Registers

The Port A–C Address registers select the GPIO port functionality accessible through the Port A–C Control registers. The Port A–C Address and Control registers combine to provide access to all GPIO port controls (Table 19).

Table 19. Port A–C GPIO Address Registers (PxADDR)

| Bit     | 7          | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------|-----------------------------|---|---|---|---|---|---|

| Field   | PADDR[7:0] |                             |   |   |   |   |   |   |

| RESET   | 00H        |                             |   |   |   |   |   |   |

| R/W     | R/W        | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| Address |            | FD0H, FD4H, FD8H            |   |   |   |   |   |   |

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The Port Address selects one of the subregisters accessible through the Port Control Register. |

|       | See Table 20 for each subregister function.                                                    |

Table 20. PADDR[7:0] Subregister Functions

|   | PADDR[7:0] | Port Control Subregister Accessible Using the Port A–C Control Registers       |

|---|------------|--------------------------------------------------------------------------------|

| - | 00H        | No function. Provides some protection against accidental Port reconfiguration. |

| - | 01H        | Data Direction.                                                                |

| - | 02H        | Alternate Function.                                                            |

|   | 03H        | Output Control (Open-Drain).                                                   |

| - | 04H        | High Drive Enable                                                              |

### Port A–C Stop Mode Recovery Source Enable Subregisters

The Port A–C Stop Mode Recovery Source Enable Subregister (Table 26) is accessed through the Port A–C Control Register by writing 05H to the Port A–C Address Register. Setting the bits in the Port A–C Stop Mode Recovery Source Enable subregisters to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

Table 26. Port A-C Stop Mode Recovery Source Enable Subregisters (PSMREx)

| Bit     | 7         | 6                                                                                                                         | 5      | 4      | 3      | 2      | 1      | 0      |  |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|

| Field   | PSMRE7    | PSMRE6                                                                                                                    | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |

| RESET   | 0         | 0                                                                                                                         | 0      | 0      | 0      | 0      | 0      | 0      |  |

| R/W     | R/W       | R/W R/W R/W R/W R/W R/W R/W R/W R/W If 05H in Port A–C Address Register, accessible through the Port A–C Control Register |        |        |        |        |        |        |  |

| Address | If 05H in |                                                                                                                           |        |        |        |        |        |        |  |

[7:0] Port Stop Mode Recovery Source Enabled.

PSMREx 0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7–0).

| Bit          | Description (Continued)                                                                                                                                                        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>U0RXI | UART 0 Receiver Interrupt Request 0 = No interrupt request is pending for the UART 0 receiver. 1 = An interrupt request from the UART 0 receiver is awaiting service.          |

| [3]<br>U0TXI | UART 0 Transmitter Interrupt Request 0 = No interrupt request is pending for the UART 0 transmitter. 1 = An interrupt request from the UART 0 transmitter is awaiting service. |

| [2:1]        | Reserved These bits are reserved and must be programmed to 00.                                                                                                                 |

| [0]<br>ADCI  | ADC Interrupt Request  0 = No interrupt request is pending for the ADC.  1 = An interrupt request from the ADC is awaiting service.                                            |

### **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 37) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 1 Register to determine if any interrupt requests are pending.

Table 37. Interrupt Request 1 Register (IRQ1)

| Bit     | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|-------|-------|------|------|------|------|------|------|

| Field   | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET   | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | FC3H  |       |      |      |      |      |      |      |

| Bit          | Description                                                                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VI | Port A7 Interrupt Request 0 = No interrupt request is pending for GPIO Port A.                                                                                        |

| I AT VI      | 1 = An interrupt request from GPIO Port A.                                                                                                                            |

| [6]<br>PA6CI | Port A6 or Comparator Interrupt Request  0 = No interrupt request is pending for GPIO Port A or Comparator.  1 = An interrupt request from GPIO Port A or Comparator. |

| [5:0]        | Port A Pin x Interrupt Request                                                                                                                                        |

| PAxI         | 0 = No interrupt request is pending for GPIO Port A pin x.                                                                                                            |

|              | 1 = An interrupt request from GPIO Port A pin $x$ is awaiting service.                                                                                                |

| Note: x ir   | ndicates the specific GPIO Port pin number (0–5).                                                                                                                     |

- 1. Checks the UART Status 0 Register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data Register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) Mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

# Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 Register, performs flow control on the outgoing transmit datastream. The Clear To Send (CTS) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert CTS at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If CTS deasserts in the middle of a character transmission, the current character is sent completely.

# **MULTIPROCESSOR (9-Bit) Mode**

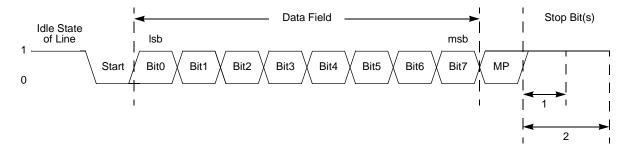

The UART has a MULTIPROCESSOR (9-bit) Mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTI-PROCESSOR Mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is given below:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) Mode, the parity bit location (9<sup>th</sup> bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPRO-CESSOR (9-bit) Mode control and status information. If an automatic address matching

# **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 68 and Table 69) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

Table 68. UART Control 0 Register (U0CTL0)

| Bit     | 7    | 6   | 5    | 4   | 3    | 2    | 1    | 0    |

|---------|------|-----|------|-----|------|------|------|------|

| Field   | TEN  | REN | CTSE | PEN | PSEL | SBRK | STOP | LBEN |

| RESET   | 0    | 0   | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

| Address | F42H |     |      |     |      |      |      |      |

| Bit         | Description                                                                                                                                                                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TEN  | Transmit Enable This bit enables or disables the transmitter. The enable is also controlled by the CTS signal and the CTSE bit. If the CTS signal is low and the CTSE bit is 1, the transmitter is enabled.  0 = Transmitter disabled.  1 = Transmitter enabled.                                          |

| [6]<br>REN  | Receive Enable This bit enables or disables the receiver. 0 = Receiver disabled. 1 = Receiver enabled.                                                                                                                                                                                                    |

| [5]<br>CTSE | CTSE—CTS Enable 0 = The CTS signal has no effect on the transmitter. 1 = The UART recognizes the CTS signal as an enable control from the transmitter.                                                                                                                                                    |

| [4]<br>PEN  | Parity Enable This bit enables or disables parity. Even or odd is determined by the PSEL bit.  0 = Parity is disabled.  1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.                                                                  |

| [3]<br>PSEL | Parity Select 0 = Even parity is transmitted and expected on all received data. 1 = Odd parity is transmitted and expected on all received data.                                                                                                                                                          |

| [2]<br>SBRK | Send Break This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.  0 = No break is sent.  1 = Forces a break condition by setting the output of the transmitter to zero. |

### **Option Bit Types**

This section describes the five types of Flash option bits offered in the F083A Series.

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 in program memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in a Flash memory information page. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

**Note:** The trim address range is from information address 20-3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

#### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in the Flash Information Area section on page 15.

#### Serialization Bits

As an optional feature, Zilog is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

# Oscillator Control

Z8 Encore! XP F0823 Series devices uses three possible clocking schemes, each user-selectable. These three schemes are:

- On-chip precision trimmed RC oscillator

- External clock drive

- On-chip low power Watchdog Timer oscillator

In addition, F0823 Series devices contain clock failure detection and recovery circuitry, which allow continued operation despite a failure of the primary oscillator.

# **Operation**

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document.

# **System Clock Selection**

The oscillator control block selects from the available clocks. Table 104 details each clock source and its usage.

**Table 104. Oscillator Configuration and Selection**

| Clock Source                          | Characteristics                                                                                                                | Required Setup                                                                                                                                                                                                          |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8kHz or 5.53MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>            | Unlock and write Oscillator Control<br>Register (OSCCTL) to enable and<br>select oscillator at either 5.53MHz or<br>32.8kHz                                                                                             |

| External Clock<br>Drive               | 0 to 20MHz     Accuracy dependent on external clock source                                                                     | <ul> <li>Write GPIO registers to configure PB3         pin for external clock function</li> <li>Unlock and write OSCCTL to select         external system clock</li> <li>Apply external clock signal to GPIO</li> </ul> |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Very Low power consumption</li> </ul> | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>                    |

conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

#### **Watchdog Timer Failure**

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control Register.

### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

#### **Assembly Language Source Program Example**

JP START ; Everything after the semicolon is a comment.

START: ; A label called 'START'. The first instruction (JP START) in this

; example causes program execution to jump to the point within the

; program where the START label occurs.

LD R4, R7; A Load (LD) instruction with two operands. The first operand,

; Working Register R4, is the destination. The second operand, ; Working Register R7, is the source. The contents of R7 is

; written into R4.

LD 234H, #%01; Another Load (LD) instruction with two operands.

; The first operand, Extended Mode Register Address 234H, ; identifies the destination. The second operand, Immediate Data ; value 01H, is the source. The value 01H is written into the

; Register at address 234H.

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

#### **Example 1**

If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 106.

Table 106. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 180 | (ADD dst, sro | ( د        |

|------------------------|-----|------|-----|---------------|------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst | <b>:</b> ) |

#### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 107.

**Table 117. Rotate and Shift Instructions (Continued)**

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

| SRL      | dst      | Shift Right Logical        |

| SWAP     | dst      | Swap Nibbles               |

# **eZ8 CPU Instruction Summary**

Table 118 summarizes the eZ8 CPU instruction set. The table identifies the addressing modes employed by the instruction, the effect upon the Flags Register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction execution.

Table 118. eZ8 CPU Instruction Summary

| Assembly      |                           |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ıgs |   |   | Fetch  | Instr. |

|---------------|---------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|--------|--------|

| Mnemonic      | <b>Symbolic Operation</b> | dst | src         | (Hex)       | С | Z | S   | ٧   | D | Н | Cycles |        |

| ADC dst, src  | dst ← dst + src + C       | r   | r           | 12          | * | * | *   | *   | 0 | * | 2      | 3      |

|               |                           | r   | lr          | 13          |   |   |     |     |   |   | 2      | 4      |

|               |                           | R   | R           | 14          |   |   |     |     |   |   | 3      | 3      |

|               |                           | R   | IR          | 15          |   |   |     |     |   |   | 3      | 4      |

|               |                           | R   | IM          | 16          |   |   |     |     |   |   | 3      | 3      |

|               |                           | IR  | IM          | 17          |   |   |     |     |   |   | 3      | 4      |

| ADCX dst, src | dst ← dst + src + C       | ER  | ER          | 18          | * | * | *   | *   | 0 | * | 4      | 3      |

|               |                           | ER  | IM          | 19          |   |   |     |     |   |   | 4      | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

**Table 119. Opcode Map Abbreviations**

| Abbreviation | Description                             | Abbreviation                                   | Description            |

|--------------|-----------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                            | IRR                                            | Indirect Register Pair |

| СС           | Condition code                          | р                                              | Polarity (0 or 1)      |

| X            | 8-bit signed index or displace-<br>ment | r                                              | 4-bit Working Register |

| DA           | Destination address                     | R                                              | 8-bit register         |

| ER           | Extended Addressing register            | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                    | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register               | RA                                             | Relative               |

| IR           | Indirect register                       | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair          | RR                                             | Register Pair          |

212

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

|                                            |               |           |            |                        |                     | 9              |                     |  |  |

|--------------------------------------------|---------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|--|

| Part Number                                | Flash<br>RAM  | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |

| Z8 Encore! XP F0823 Series with 8 KB Flash |               |           |            |                        |                     |                |                     |  |  |

| Standard Temperature: 0°C to 70°C          |               |           |            |                        |                     |                |                     |  |  |

| Z8F0813PB005SG                             | 8 KB 1 K      | B 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0813QB005SG                             | 8 KB 1 K      | B 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |

| Z8F0813SB005SG                             | 8 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0813SH005SG                             | 8 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |

| Z8F0813HH005SG                             | 8 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |

| Z8F0813PH005SG                             | 8 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |

| Z8F0813SJ005SG                             | 8 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |

| Z8F0813HJ005SG                             | 8 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |

| Z8F0813PJ005SG                             | 8 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |

| Extended Temperatu                         | ıre: –40°C to | 105°C     |            |                        |                     |                |                     |  |  |

| Z8F0813PB005EG                             | 8 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0813QB005EG                             | 8 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |

| Z8F0813SB005EG                             | 8 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0813SH005EG                             | 8 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |

| Z8F0813HH005EG                             | 8 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |

| Z8F0813PH005EG                             | 8 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |

| Z8F0813SJ005EG                             | 8 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |

| Z8F0813HJ005EG                             | 8 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |

| Z8F0813PJ005EG                             | 8 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |

213

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

| Part Number                       | Flash      | RAM   | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|-----------------------------------|------------|-------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP F0823               | Series w   | ith 4 | KB Fla    | sh, 10     | -Bit An                | alog-1              | o-Digi         | tal Converter       |

| Standard Temperature: 0°C to 70°C |            |       |           |            |                        |                     |                |                     |

| Z8F0423PB005SG                    | 4 KB       | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005SG                    | 4 KB       | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005SG                    | 4 KB       | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005SG                    | 4 KB       | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005SG                    | 4 KB       | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005SG                    | 4 KB       | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005SG                    | 4 KB       | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005SG                    | 4 KB       | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005SG                    | 4 KB       | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatu                | ıre: –40°C | to 10 | 5°C       |            |                        |                     |                |                     |

| Z8F0423PB005EG                    | 4 KB       | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005EG                    | 4 KB       | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005EG                    | 4 KB       | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005EG                    | 4 KB       | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005EG                    | 4 KB       | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005EG                    | 4 KB       | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005EG                    | 4 KB       | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005EG                    | 4 KB       | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005EG                    | 4 KB       | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| LD 180                           | Interrupt Controller 54                               |

|----------------------------------|-------------------------------------------------------|

| LDC 180                          | interrupt controller                                  |

| LDCI 179, 180                    | architecture 54                                       |

| LDE 180                          | interrupt assertion types 57                          |

| LDEI 179                         | interrupt vectors and priority 57                     |

| LDX 180                          | operation 56                                          |

| LEA 180                          | register definitions 59                               |

| load 180                         | software interrupt assertion 58                       |

| logical 181                      | interrupt edge select register 66                     |

| MULT 179                         | interrupt request 0 register 59                       |

| NOP 180                          | interrupt request 1 register 60                       |

| OR 181                           | interrupt request 2 register 61                       |

| ORX 181                          | interrupt return 181                                  |

| POP 180                          | interrupt vector listing 54                           |

| POPX 180                         | interrupts                                            |

| program control 181              | UART 105                                              |

| PUSH 180                         | IR 176                                                |

| PUSHX 180                        | Ir 176                                                |

| RCF 179, 180                     | IrDA                                                  |

| RET 181                          | architecture 117                                      |

| RL 181                           | block diagram 117                                     |

| RLC 181                          | control register definitions 120                      |

| rotate and shift 181             | operation 117                                         |

| RR 182                           | receiving data 119                                    |

| RRC 182                          | transmitting data 118                                 |

| SBC 179                          | IRET 181                                              |

| SCF 179, 180                     | IRQ0 enable high and low bit registers 61             |

| SRA 182                          | IRQ1 enable high and low bit registers 63             |

| SRL 182                          | IRQ2 enable high and low bit registers 65             |

| SRP 180                          | IRR 176                                               |

| STOP 180                         | Irr 176                                               |

| SUB 179                          |                                                       |

| SUBX 179                         |                                                       |

| SWAP 182                         | J                                                     |

| TCM 179                          | JP 181                                                |

| TCMX 179                         | jump, conditional, relative, and relative conditional |

| TM 179                           | 181                                                   |

| TMX 179                          |                                                       |

| TRAP 181                         |                                                       |

| Watchdog Timer refresh 180       | L                                                     |

| XOR 181                          | LD 180                                                |

| XORX 181                         | LDC 180                                               |

| instructions, eZ8 classes of 178 | LDCI 179, 180                                         |

| interrupt control register 68    | LDE 180                                               |

230

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <a href="http://zilog.com/forum">http://zilog.com/forum</a>. <a href="http://zilog.com/forum">zilog.com/forum</a>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <a href="http://www.zilog.com">http://www.zilog.com</a>.

PS024315-1011 PRELIMINARY Customer Support