Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223pj005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ilog Embedded in Life An 🛙 IXYS Company

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 8-pin devices.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                         | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up<br>or Pull-<br>down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                    |

|--------------------|-----------|----------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if<br>key<br>sequence<br>detected) | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O<br>(defaults<br><u>to</u><br>RESET)                                    | N/A                                   | Yes                | Program-<br>mable for<br>PA2;<br>always<br>on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

| VSS                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

### Table 5. Pin Characteristics (8-Pin Devices)

ilog° Embedded in Life An∎IXYS Company 18

| Address (Hex)    | Register Description     | Mnemonic       | Reset (Hex) | Page<br>No. |

|------------------|--------------------------|----------------|-------------|-------------|

| LED Controller   | (cont'd)                 |                |             |             |

| F84              | LED Drive Level Low Byte | LEDLVLL        | 00          | <u>53</u>   |

| F85              | Reserved                 | —              | XX          |             |

| Oscillator Conti | rol                      |                |             |             |

| F86              | Oscillator Control       | OSCCTL         | A0          | <u>172</u>  |

| F87–F8F          | Reserved                 | —              | XX          |             |

| Comparator 0     |                          |                |             |             |

| F90              | Comparator 0 Control     | CMP0           | 14          | <u>133</u>  |

| F91–FBF          | Reserved                 | _              | XX          |             |

| Interrupt Contro | oller                    |                |             |             |

| FC0              | Interrupt Request 0      | IRQ0           | 00          | <u>59</u>   |

| FC1              | IRQ0 Enable High Bit     | IRQ0ENH        | 00          | <u>62</u>   |

| FC2              | IRQ0 Enable Low Bit      | <b>IRQ0ENL</b> | 00          | <u>62</u>   |

| FC3              | Interrupt Request 1      | IRQ1           | 00          | <u>60</u>   |

| FC4              | IRQ1 Enable High Bit     | IRQ1ENH        | 00          | <u>64</u>   |

| FC5              | IRQ1 Enable Low Bit      | IRQ1ENL        | 00          | <u>64</u>   |

| FC6              | Interrupt Request 2      | IRQ2           | 00          | <u>61</u>   |

| FC7              | IRQ2 Enable High Bit     | IRQ2ENH        | 00          | <u>65</u>   |

| FC8              | IRQ2 Enable Low Bit      | IRQ2ENL        | 00          | <u>66</u>   |

| FC9–FCC          | Reserved                 | —              | XX          |             |

| FCD              | Interrupt Edge Select    | IRQES          | 00          | <u>67</u>   |

| FCE              | Shared Interrupt Select  | IRQSS          | 00          | <u>67</u>   |

| FCF              | Interrupt Control        | IRQCTL         | 00          | <u>68</u>   |

| GPIO Port A      |                          |                |             |             |

| FD0              | Port A Address           | PAADDR         | 00          | <u>40</u>   |

| FD1              | Port A Control           | PACTL          | 00          | <u>42</u>   |

| FD2              | Port A Input Data        | PAIN           | XX          | <u>43</u>   |

| FD3              | Port A Output Data       | PAOUT          | 00          | <u>43</u>   |

| GPIO Port B      |                          |                |             |             |

| FD4              | Port B Address           | PBADDR         | 00          | <u>40</u>   |

| FD5              | Port B Control           | PBCTL          | 00          | <u>42</u>   |

### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

#### ilog Embedded in Life An ∎IXYS Company 51

### Port A–C Output Data Register

The Port A–C Output Data Register (Table 31) controls the output data to the pins.

#### Table 31. Port A–C Output Data Register (PxOUT)

| Bit     | 7     | 6     | 5     | 4        | 3        | 2     | 1     | 0     |

|---------|-------|-------|-------|----------|----------|-------|-------|-------|

| Field   | POUT7 | POUT6 | POUT5 | POUT4    | POUT3    | POUT2 | POUT1 | POUT0 |

| RESET   | 0     | 0     | 0     | 0        | 0        | 0     | 0     | 0     |

| R/W     | R/W   | R/W   | R/W   | R/W      | R/W      | R/W   | R/W   | R/W   |

| Address |       |       |       | FD3H, FD | 7H, FDBH |       |       |       |

#### Bit Description

[7:0] **Port Output Data**

PxOUT These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 = Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.

Note: x indicates the specific GPIO port pin number (7–0).

## **LED Drive Enable Register**

The LED Drive Enable Register, shown in Table 32, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|

| Field   |     | LEDEN[7:0] |     |     |     |     |     |     |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |            |     | F8  | 2H  |     |     |     |

#### Table 32. LED Drive Enable (LEDEN)

| [7:0] | LED Drive Enable |  |

|-------|------------------|--|

Description

LEDEN These bits determine which Port C pins are connected to an internal current sink.

1= Connect controlled current sink to the Port C pin.

Bit

<sup>0 =</sup> Tristate the Port C pin.

nbedded in Life

81

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The compare time can be calculated by the following equation:

COMPARE Mode Time (s) = (Compare Value – Start Value) × Prescale System Clock Frequency (Hz)

#### **GATED Mode**

In GATED Mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following steps to configure a timer for GATED Mode and to initiate the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL1 Register.

ilog<sup>°</sup> Embedded in Life An∎IXYS Company **88**

|         |     |      |            |       | <b>U</b> ( | ,   |     |     |

|---------|-----|------|------------|-------|------------|-----|-----|-----|

| Bit     | 7   | 6    | 5          | 4     | 3          | 2   | 1   | 0   |

| Field   | TEN | TPOL | PRES TMODE |       |            |     |     |     |

| RESET   | 0   | 0    | 0          | 0     | 0          | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W        | R/W   | R/W        | R/W | R/W | R/W |

| Address |     |      |            | F07H, | F0FH       |     |     |     |

#### Table 58. Timer 0–1 Control Register 1 (TxCTL1)

| Audress     |                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Description                                                                                                                                                                                                                                                                                                                    |

| [7]<br>TEN  | Timer Enable0 = Timer is disabled.1 = Timer enabled to count.                                                                                                                                                                                                                                                                  |

| [6]<br>TPOL | <b>Timer Input/Output Polarity</b><br>Operation of this bit is a function of the current operating mode of the timer.<br><b>ONE-SHOT Mode</b><br>When the timer is disabled, the Timer Output signal is set to the value of this bit. When the<br>timer is enabled, the Timer Output signal is complemented upon timer reload. |

|             | <b>CONTINUOUS Mode</b><br>When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer reload.                                                                                                                           |

#### ilog<sup>®</sup> Embedded in Life An∎IXYS Company 94

<u>Watchdog Timer Reload High Byte Register (WDTH)</u>: see page 95 <u>Watchdog Timer Reload Low Byte Register (WDTL)</u>: see page 95

## Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status Register.

| Bit              | 7       | 6                                                                                                                     | 5 | 4   | 3    | 2 | 1 | 0 |  |

|------------------|---------|-----------------------------------------------------------------------------------------------------------------------|---|-----|------|---|---|---|--|

| Field            |         |                                                                                                                       |   | WDT | UNLK |   |   |   |  |

| RESET            | Х       | Х                                                                                                                     | Х | Х   | Х    | Х | Х | Х |  |

| R/W              | W       | W                                                                                                                     | W | W   | W    | W | W | W |  |

| Address          |         |                                                                                                                       |   | FF  | ОH   |   |   |   |  |

| Bit              | Descrip | tion                                                                                                                  |   |     |      |   |   |   |  |

| [7:0]<br>WDTUNLK |         | Watchdog Timer Unlock<br>The software must write the correct unlocking sequence to this register before it is allowed |   |     |      |   |   |   |  |

Table 60. Watchdog Timer Control Register (WDTCTL)

### Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 61 through 63, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT Reload Value must not be set to a value less than 000004H.

to modify the contents of the Watchdog Timer reload registers.

nbedded in Life

102

### **Receiving Data Using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Observe the following steps to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR Mode

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

Embedded in Life

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 68 and Table 69) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

| Bit     | 7           | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|---------|-------------|------|------|-----|------|------|------|------|

| Field   | TEN         | REN  | CTSE | PEN | PSEL | SBRK | STOP | LBEN |

| RESET   | 0           | 0    | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W         | R/W  | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

| Address |             | F42H |      |     |      |      |      |      |

| Bit     | Description | n    |      |     |      |      |      |      |

#### Table 68. UART Control 0 Register (U0CTL0)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TEN  | Transmit EnableThis bit enables or disables the transmitter. The enable is also controlled by the $\overline{CTS}$ signaland the CTSE bit. If the $\overline{CTS}$ signal is low and the CTSE bit is 1, the transmitter is enabled.0 = Transmitter disabled.1 = Transmitter enabled.                                                                   |

| [6]<br>REN  | Receive Enable<br>This bit enables or disables the receiver.<br>0 = Receiver disabled.<br>1 = Receiver enabled.                                                                                                                                                                                                                                        |

| [5]<br>CTSE | <b>CTSE—CTS Enable</b><br>0 = The CTS signal has no effect on the transmitter.<br>1 = The UART recognizes the CTS signal as an enable control from the transmitter.                                                                                                                                                                                    |

| [4]<br>PEN  | <ul> <li>Parity Enable</li> <li>This bit enables or disables parity. Even or odd is determined by the PSEL bit.</li> <li>0 = Parity is disabled.</li> <li>1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit .</li> </ul>                                                                 |

| [3]<br>PSEL | <ul> <li>Parity Select</li> <li>0 = Even parity is transmitted and expected on all received data.</li> <li>1 = Odd parity is transmitted and expected on all received data.</li> </ul>                                                                                                                                                                 |

| [2]<br>SBRK | <ul> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = Forces a break condition by setting the output of the transmitter to zero.</li> </ul> |

nbedded in Life IXYS Company 120

The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the endec clock counter is reset, resynchronizing the endec to the incoming signal, allowing the endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

## Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART control registers as defined in the <u>Universal Asynchronous Receiver/Transmitter</u> chapter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the endec before enabling the GPIO port alternate function for the corresponding pin.

edded in Life

132

# Comparator

Z8 Encore! XP F0823 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex.

The features of the comparator include:

- Two inputs which can be connected up using the GPIO multiplex (MUX)

- One input can be connected to a programmable internal reference

- One input can be connected to the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

### Operation

One of the comparator inputs can be connected to an internal reference which is a user selectable reference that is user programmable with 200 mV resolution.

The comparator can be powered down to save on supply current. For details, see the <u>Power</u> <u>Control Register 0</u> section on page 31.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

The following example shows how to safely enable the comparator:

```

di

ld cmp0

nop

i, wait for output to settle

clr irq0; clear any spurious interrupts pending

ei

```

#### illog<sup>®</sup> Ibedded in Life IXYS Company 138

## Table 80. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code program-<br>ming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-<br>Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                    |

### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

### **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F0823 Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 79</u> on page 134.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

#### ILO 9<sup>°</sup> Inbedded in Life IIXYS Company 147

## **Option Bit Types**

This section describes the five types of Flash option bits offered in the F083A Series.

### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 in program memory is erased.

### **Trim Option Bits**

The trim option bits are contained in a Flash memory information page. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

**Note:** The trim address range is from information address 20–3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in the <u>Flash Information Area</u> section on page 15.

### **Serialization Bits**

As an optional feature, Zilog is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

#### ilog<sup>°</sup> Embedded in Life An TIXYS Company 158

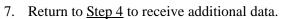

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 2 of 2

### **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The device enters DEBUG Mode following the operations below:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (breakpoint) instruction

- If the DBG pin is held Low during the most recent clock cycle of System Reset, the part enters DEBUG Mode upon exiting System Reset

• Note: Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an autobaud sequence (see the <u>OCD Autobaud Detector/</u><u>Generator section on page 159</u>).

## Embedded in Life An IXYS Company

## **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

| Bit   | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |

|-------|-----|------|--------|----------|---|---|---|---|

| Field | DBG | HALT | FRPENB | Reserved |   |   |   |   |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |

| R/W   | R   | R    | R      | R        | R | R | R | R |

|       |     |      |        |          |   |   |   |   |

| Bit           | Description                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBG    | Debug Status<br>0 = NORMAL Mode.<br>1 = DEBUG Mode.                                                                                |

| [6]<br>HALT   | HALT Mode<br>0 = Not in HALT Mode.<br>1 = In HALT Mode.                                                                            |

| [5]<br>FRPENB | Flash Read Protect Option Bit Enable<br>0 = FRP bit enabled to allow disabling of many OCD commands.<br>1 = FRP bit has no effect. |

| [4:0]         | Reserved<br>These bits are reserved and must be 00000 when read.                                                                   |

nbedded in Life

170

ages to the Oscillator Control Desistor can actually stor the ship by

**Caution:** Unintentional accesses to the Oscillator Control Register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

### **OSC Control Register Unlocking/Locking**

To write to the Oscillator Control Register, unlock it by making two writes to the OSC-CTL Register with the values E7H followed by 18H. A third write to the OSCCTL Register changes the value of the actual register and returns the register to a locked state. Any other sequence of Oscillator Control Register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

### **Clock Failure Detection and Recovery**

Should an oscillator or timer fail, there are methods of recovery, as this section describes.

### **Primary Oscillator Failure**

Z8 Encore! XP F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the the <u>Watchdog Timer</u> section on page 91.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below  $1 \text{ kHz} \pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these

I

199

|                           |                                                         | VD                   | <sub>D</sub> = 2.7V to 3         | 8.6V                             |    |                                                                   |  |

|---------------------------|---------------------------------------------------------|----------------------|----------------------------------|----------------------------------|----|-------------------------------------------------------------------|--|

| Symbol                    | Parameter                                               | Typical <sup>1</sup> | Maximum <sup>2</sup><br>Std Temp | Maximum <sup>3</sup><br>Ext Temp |    | Conditions                                                        |  |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                          | 0.1                  | 2                                | 7.5                              | μA | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}$ . |  |

| I <sub>DD</sub> Halt      | Supply Current in HALT                                  | 35                   | 55                               | 65                               | μA | 32kHz.                                                            |  |

|                           | Mode (with all peripher-                                | 520                  | 630                              | 700                              | μA | 5.5MHz.                                                           |  |

| I <sub>DD</sub>           | Supply Current in                                       | 2.8                  | 4.5                              | 4.8                              | mA | 32kHz.                                                            |  |

|                           | ACTIVE Mode (with all peripherals disabled)             | 4.5                  | 5.2                              | 5.2                              | mA | 5.5MHz.                                                           |  |

| I <sub>DD</sub> WDT       | Watchdog Timer Sup-<br>ply Current                      | 0.9                  | 1.0                              | 1.1                              | μA |                                                                   |  |

| I <sub>DD</sub> IPO       | Internal Precision Oscil-<br>lator Supply Current       | 350                  | 500                              | 550                              | μA |                                                                   |  |

| I <sub>DD</sub> VBO       | Voltage Brown-Out Sup-<br>ply Current                   | 50                   |                                  |                                  | μA | For 20-/28-pin devices (VBO only). <sup>4</sup>                   |  |

|                           | -                                                       |                      |                                  |                                  |    | For 8-pin devices. <sup>4</sup>                                   |  |

| I <sub>DD</sub> ADC       | Analog-to-Digital Con-                                  | 2.8                  | 3.1                              | 3.2                              | mA | 32kHz.                                                            |  |

|                           | verter Supply Current<br>(with External Refer-<br>ence) | 3.1                  | 3.6                              | 3.7                              | mA | 5.5MHz.                                                           |  |

|                           |                                                         | 3.3                  | 3.7                              | 3.8                              | mA | 10MHz.                                                            |  |

|                           | ,                                                       | 3.7                  | 4.2                              | 4.3                              | mA | 20MHz.                                                            |  |

| I <sub>DD</sub><br>ADCRef | ADC Internal Refer-<br>ence Supply Current              | 0                    |                                  |                                  | μA | See Note 4.                                                       |  |

| I <sub>DD</sub> CMP       | Comparator supply Cur-<br>rent                          | 150                  | 180                              | 190                              | μA | See Note 4.                                                       |  |

| I <sub>DD</sub> BG        | Band Gap Supply Cur-                                    | 320                  | 480                              | 500                              | μA | For 20-/28-pin devices.                                           |  |

#### Table 122. Power Consumption

Notes:

1. Typical conditions are defined as  $V_{DD}$  = 3.3 V and +30°C.

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

#### $V_{DD} = 3.0 V \text{ to } 3.6 V$ $T_A = 0^{\circ}C$ to +70°C (unless otherwise stated) Symbol Parameter **Maximum Units Conditions** Minimum Typical As defined by -3 dB Signal Input Bandwidth 10 kHz \_ point Analog Source Impedance<sup>4</sup> kW In unbuffered mode Rs 10 \_ \_ Zin kW In unbuffered mode at Input Impedance 150 20MHz<sup>5</sup> Vin Input Voltage Range 0 $V_{DD}$ V **Unbuffered Mode**

Table 128. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

| V <sub>DD</sub> = 2.7V to 3.6V<br>T <sub>A</sub> = -40°C to +105°C |                                            |                 |            |                    |       |                    |  |  |

|--------------------------------------------------------------------|--------------------------------------------|-----------------|------------|--------------------|-------|--------------------|--|--|

| Symbol                                                             | Parameter                                  | Minimum         | Typical    | Maximum            | Units | Conditions         |  |  |

| V <sub>OS</sub>                                                    | Input DC Offset                            |                 | 5          |                    | mV    |                    |  |  |

| V <sub>CREF</sub>                                                  | Programmable Internal<br>Reference Voltage |                 | <u>+</u> 5 |                    | %     | 20-/28-pin devices |  |  |

|                                                                    |                                            |                 | <u>+</u> 3 |                    | %     | 8-pin devices      |  |  |

| T <sub>PROP</sub>                                                  | Propagation Delay                          |                 | 200        |                    | ns    |                    |  |  |

| V <sub>HYS</sub>                                                   | Input Hysteresis                           |                 | 4          |                    | mV    |                    |  |  |

| V <sub>IN</sub>                                                    | Input Voltage Range                        | V <sub>SS</sub> |            | V <sub>DD</sub> -1 | V     |                    |  |  |

#### Table 129. Comparator Electrical Characteristics

### General Purpose I/O Port Input Data Sample Timing

Figure 29 displays a timing sequence for the GPIO port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The port value is

209

0g

■IXYS Company

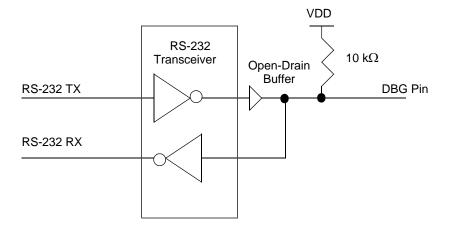

Figure 33 and Table 134 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

|                |                                                                        | Delay (ns)                 |            |  |  |

|----------------|------------------------------------------------------------------------|----------------------------|------------|--|--|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |  |  |

| UART           |                                                                        |                            |            |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5                        |            |  |  |

> ilog Embedded in Life An IXYS Company 214

|                     |                 |           |            |                        |                     | -              |                     |

|---------------------|-----------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number         | Flash<br>RAM    | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 | Series with 4   | KB Fla    | ash        |                        |                     |                |                     |

| Standard Temperatu  | re: 0°C to 70°C | ;         |            |                        |                     |                |                     |

| Z8F0413PB005SG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005SG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005SG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005SG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005SG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005SG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005SG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005SG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005SG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu  | re: -40°C to 1  | 05°C      |            |                        |                     |                |                     |

| Z8F0413PB005EG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005EG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005EG      | 4 KB 1 KB       | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005EG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005EG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005EG      | 4 KB 1 KB       | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005EG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005EG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005EG      | 4 KB 1 KB       | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

225

LDEI 179, 180 LDX 180 LEA 180 load 180 load constant 179 load constant to/from program memory 180 load constant with auto-increment addresses 180 load effective address 180 load external data 180 load external data to/from data memory and autoincrement addresses 179 load external to/from data memory and auto-increment addresses 180 load instructions 180 load using extended addressing 180 logical AND 181 logical AND/extended addressing 181 logical exclusive OR 181 logical exclusive OR/extended addressing 181 logical instructions 181 logical OR 181 logical OR/extended addressing 181 low power modes 30

### Μ

master interrupt enable 56 memory data 15 program 13 mode CAPTURE 89 **CAPTURE/COMPARE 89 CONTINUOUS 88 COUNTER 89** GATED 89 **ONE-SHOT 88 PWM 89** modes 89 **MULT 179** multiply 179 MULTIPROCESSOR mode, UART 103

### Ν

NOP (no operation) 180 notation b 176 cc 176 DA 176 ER 176 IM 176 IR 176 Ir 176 **IRR 176** Irr 176 p 176 R 176 r 176 RA 177 RR 177 rr 177 vector 177 X 177 notational shorthand 176

## 0

OCD architecture 156 auto-baud detector/generator 159 baud rate limits 160 block diagram 156 breakpoints 161 commands 162 control register 166 data format 159 DBG pin to RS-232 Interface 157 DEBUG mode 158 debugger break 181 interface 157 serial errors 160 status register 168 timing 207 **OCD** commands execute instruction (12H) 166 read data memory (0DH) 165 read OCD control register (05H) 163