Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |  |  |  |

|----------------------------|-----------------------------------------------------------|--|--|--|

| Product Status             | Active                                                    |  |  |  |

| Core Processor             | eZ8                                                       |  |  |  |

| Core Size                  | 8-Bit                                                     |  |  |  |

| Speed                      | 5MHz                                                      |  |  |  |

| Connectivity               | IrDA, UART/USART                                          |  |  |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |  |  |

| Number of I/O              | 6                                                         |  |  |  |

| Program Memory Size        | 2KB (2K x 8)                                              |  |  |  |

| Program Memory Type        | FLASH                                                     |  |  |  |

| EEPROM Size                | -                                                         |  |  |  |

| RAM Size                   | 512 x 8                                                   |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |  |  |

| Data Converters            | A/D 4x10b                                                 |  |  |  |

| Oscillator Type            | Internal                                                  |  |  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |  |  |

| Mounting Type              | Surface Mount                                             |  |  |  |

| Package / Case             | 8-VDFN Exposed Pad                                        |  |  |  |

| Supplier Device Package    | 8-QFN (5x6)                                               |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223qb005eg |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Flash Code Protection Against Accidental Program and Erasure |       |

|--------------------------------------------------------------|-------|

| Byte Programming                                             | . 139 |

| Page Erase                                                   | . 139 |

| Mass Erase                                                   | . 139 |

| Flash Controller Bypass                                      |       |

| Flash Controller Behavior in DEBUG Mode                      | . 140 |

| Flash Control Register Definitions                           | . 141 |

| Flash Control Register                                       | . 141 |

| Flash Status Register                                        | . 142 |

| Flash Page Select Register                                   | . 142 |

| Flash Sector Protect Register                                | . 144 |

| Flash Frequency High and Low Byte Registers                  | . 144 |

| Flash Option Bits                                            | . 146 |

| Operation                                                    |       |

| Option Bit Configuration By Reset                            |       |

| Option Bit Types                                             |       |

| Reading the Flash Information Page                           |       |

| Flash Option Bit Control Register Definitions                |       |

| Trim Bit Address Register                                    |       |

| Trim Bit Data Register                                       |       |

| Flash Option Bit Address Space                               |       |

| Trim Bit Address Space                                       |       |

| Zilog Calibration Data                                       |       |

| ADC Calibration Data                                         |       |

| Serialization Data                                           |       |

| Randomized Lot Identifier                                    |       |

| On-Chip Debugger                                             |       |

| Architecture                                                 |       |

| Operation                                                    |       |

| OCD Interface                                                |       |

| DEBUG Mode                                                   |       |

| OCD Data Format                                              |       |

| OCD Autobaud Detector/Generator                              |       |

|                                                              |       |

| OCD Serial Errors OCD Unlock Sequence (8-Pin Devices Only)   |       |

|                                                              |       |

| Breakpoints                                                  |       |

|                                                              |       |

| On-Chip Debugger Commands                                    |       |

| On-Chip Debugger Control Register Definitions                | . 100 |

OCD Control Register ...... 166

#### ilog<sup>°</sup> Embedded in Life An ∎IXYS Company

5

### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

## **10-Bit Analog-to-Digital Converter**

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

## **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

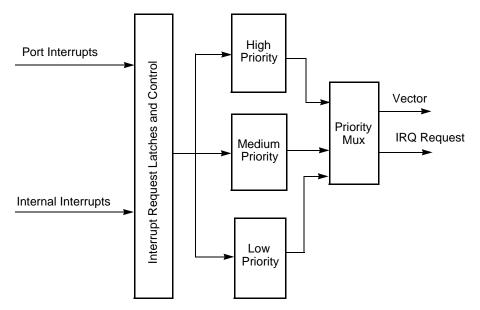

### **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

## **Reset Controller**

Z8 Encore!  $XP^{\text{(B)}}$  F0823 Series products can be reset using the RESET pin, POR, WDT time-out, STOP Mode exit, or Voltage Brown-Out warning signal. The RESET pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

| Program Memory Address (Hex)                                                                          | Function                 |

|-------------------------------------------------------------------------------------------------------|--------------------------|

| Z8F0123 and Z8F0113 Products                                                                          |                          |

| 0000–0001                                                                                             | Flash Option Bits        |

| 0002–0003                                                                                             | Reset Vector             |

| 0004–0005                                                                                             | WDT Interrupt Vector     |

| 0006–0007                                                                                             | Illegal Instruction Trap |

| 0008–0037                                                                                             | Interrupt Vectors*       |

| 0038–003D                                                                                             | Oscillator Fail Traps*   |

| 003E-03FF                                                                                             | Program Memory           |

| Note: *See the <u>Trap and Interrupt Vectors in C</u><br>for a list of the interrupt vectors and trap |                          |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

## **Data Memory**

Z8 Encore! XP F0823 Series does not use the eZ8 CPU's 64KB Data Memory address space.

## **Flash Information Area**

Table 7 lists the F0823 Series Flash Information Area. This 128B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory<br>Address (Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00–FE3F                       | Zilog Option Bits.                                                                         |

| FE40–FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60–FE7F                       | Zilog Calibration Data.                                                                    |

| FE80–FFFF                       | Reserved.                                                                                  |

Table 7. F0823 Series Flash Memory Information Area Map

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see **the** <u>Port A–C Control Registers</u> **section on page 42**), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overrightarrow{\text{RESET}}$  pin Low. The  $\overrightarrow{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

## **Stop Mode Recovery**

The device enters into STOP Mode when eZ8 CPU executes a STOP instruction. For more details about STOP Mode, see **the** Low-Power Modes **section on page 30**. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

iloa 39

dded in Life

For correct operation, the LED anode must be connected to V<sub>DD</sub> and the cathode must be connected to the GPIO pin. Using all Port C pins in LED Drive Mode with maximum current can result in excessive total current. For the maximum total current for the applicable package, see the Electrical Characteristics chapter on page 196.

## Shared Reset Pin

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO Mode.

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, ensure that no external stimulus 1 drives the pin Low during any reset sequence. Because PA2 returns to its RESET alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

## Shared Debug Pin

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer functions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see the On-Chip Debugger chapter on page 156.

## **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see the Oscillator Control Register Definitions section on page 171), the GPIO settings are overridden and PA0 and PA1 are disabled.

## **5V Tolerance**

All six I/O pins on the 8-pin devices are 5V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5V-tolerant, including PA[1:0], PB[5:0], and

| <b>Z</b> 8 | Encore! XP <sup>®</sup> | F0823  | Series  |

|------------|-------------------------|--------|---------|

|            | Product                 | Specif | ication |

|            |                         |        |         |

nbedded in Life

n 🗖 IXYS Company

56

## Architecture

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

## Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 56

Interrupt Vectors and Priority: see page 57

Interrupt Assertion: see page 57

Software Interrupt Assertion: see page 58

Watchdog Timer Interrupt Assertion: see page 58

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

• Execution of an Enable Interrupt (EI) instruction

ILO<u>G</u> abedded in Life

68

## Interrupt Control Register

The Interrupt Control (IRQCTL) Register (Table 50) contains the master enable bit for all interrupts.

| Bit     | 7    | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|----------|---|---|---|---|---|---|

| Field   | IRQE | Reserved |   |   |   |   |   |   |

| RESET   | 0    | 0        | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W     | R/W  | R        | R | R | R | R | R | R |

| Address | FCFH |          |   |   |   |   |   |   |

|         |      |          |   |   |   |   |   |   |

#### Table 50. Interrupt Control Register (IRQCTL)

#### Bit Description

[7] Interrupt Request Enable

IRQE This bit is set to 1 by executing an Enable Interrupts (EI) or Interrupt Return (IRET) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset or by a direct register write of a 0 to this bit.

0 = Interrupts are disabled.

1 = Interrupts are enabled.

[6:0] Reserved These bits are reserved and must be programmed to 0000000 when read.

## Embedded in Life An IXYS Company 97

# Universal Asynchronous Receiver/ Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. The features of UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) Mode with three configurable interrupt schemes

- BRG can be configured and used as a basic 16-bit timer

- Driver Enable output for external bus transceivers

## Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

#### ilog Embedded in Life An IXYS Company 110

## **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 66 and Table 67) identify the current UART operating configuration and status.

| Bit         | 7                                                                                                                                                                                                                                                                                                                                         | 6  | 5  | 4  | 3    | 2    | 1   | 0   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|------|------|-----|-----|

| Field       | RDA                                                                                                                                                                                                                                                                                                                                       | PE | OE | FE | BRKD | TDRE | TXE | CTS |

| RESET       | 0                                                                                                                                                                                                                                                                                                                                         | 0  | 0  | 0  | 0    | 1    | 1   | Х   |

| R/W         | R                                                                                                                                                                                                                                                                                                                                         | R  | R  | R  | R    | R    | R   | R   |

| Address     |                                                                                                                                                                                                                                                                                                                                           |    |    | F4 | 1H   |      |     |     |

| Bit         | Description                                                                                                                                                                                                                                                                                                                               |    |    |    |      |      |     |     |

| [7]<br>RDA  | <ul> <li>Receive Data Available</li> <li>This bit indicates that the UART Receive Data Register has received data. Reading the UART Receive Data Register clears this bit.</li> <li>0 = The UART Receive Data Register is empty.</li> <li>1 = There is a byte in the UART Receive Data Register.</li> </ul>                               |    |    |    |      |      |     |     |

| [6]<br>PE   | <ul> <li>Parity Error</li> <li>This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.</li> <li>0 = No parity error has occurred.</li> <li>1 = A parity error has occurred.</li> </ul>                                                                                               |    |    |    |      |      |     |     |

| [5]<br>OE   | Overrun Error<br>This bit indicates that an overrun error has occurred. An overrun occurs when new data is<br>received and the UART Receive Data Register has not been read. If the RDA bit is reset to 0,<br>reading the UART Receive Data Register clears this bit.<br>0 = No overrun error occurred.<br>1 = An overrun error occurred. |    |    |    |      |      |     |     |

| [4]<br>FE   | Framing Error<br>This bit indicates that a framing error (no Stop bit following data reception) was detected.<br>Reading the UART Receive Data Register clears this bit.<br>0 = No framing error occurred.<br>1 = A framing error occurred.                                                                                               |    |    |    |      |      |     |     |

| [3]<br>BRKD | <b>Break Detect</b><br>This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data Register clears this bit.<br>0 = No break occurred.<br>1 = A break occurred.                                                                 |    |    |    |      |      |     |     |

#### ilog Embedded in Life An TIXYS Company 131

## ADC Data Low Bits Register

The ADC Data Low Byte register contains the lower bits of the ADC output as well as an overflow status bit. The output is a 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits Register.

| Bit     | 7     | 6 | 5 | 4        | 3 | 2 | 1 | 0   |

|---------|-------|---|---|----------|---|---|---|-----|

| Field   | ADCDL |   |   | Reserved |   |   |   | OVF |

| RESET   | Х     | Х | Х | Х        | Х | Х | Х | Х   |

| R/W     | R     | R | R | R        | R | R | R | R   |

| Address | F73H  |   |   |          |   |   |   |     |

| Table 77. | ADC Data    | Low Bits | Register | (ADCD L) |

|-----------|-------------|----------|----------|----------|

| 14010 111 | /10 0 D ulu |          |          |          |

| Bit            | Description                                                                                                                                                               |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]<br>ADCDL | ADC Data Low Bits<br>These bits are the least significant three bits of the 11-bits of the ADC output. These bits are<br>undefined after a Reset.                         |

| [4:1]          | Reserved<br>These bits are reserved and are undefined when read.                                                                                                          |

| [0]<br>OVF     | Overflow Status<br>0 = An overflow did not occur in the digital filter for the current sample.<br>1 = An overflow did occur in the digital filter for the current sample. |

## **OCD Unlock Sequence (8-Pin Devices Only)**

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5 ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

\begin{array}{l} \text{DBG} \leftarrow 80\text{H} \text{ (autobaud)} \\ \\ \text{DBG} \leftarrow \text{EBH} \\ \\ \text{DBG} \leftarrow 5\text{AH} \\ \\ \\ \text{DBG} \leftarrow 70\text{H} \\ \\ \\ \\ \text{DBG} \leftarrow \text{CDH} \text{ (32-bit unlock key)} \end{array}

```

Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20- or 28-pin device. To enter DEBUG Mode, reautobaud and write 80H to the OCD Control Register (see the <u>On-Chip Debugger Commands</u> section on page 162).

### **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

### **Runtime Counter**

The OCD contains a 16-bit Runtime Counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

ILO O hbedded in Life IXYS Company

166

**Stuff Instruction (11H).** The Stuff command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0–4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

**Execute Instruction (12H).** The Execute command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

## **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

### **OCD Control Register**

The OCD Control Register controls the state of the OCD. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It also resets Z8 Encore! XP F0823 Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

# eZ8 CPU Instruction Set

This chapter describes the following features of the eZ8 CPU instruction set: <u>Assembly Language Programming Introduction</u>: see page 174 <u>Assembly Language Syntax</u>: see page 175

eZ8 CPU Instruction Notation: see page 176

eZ8 CPU Instruction Classes: see page 178

eZ8 CPU Instruction Summary: see page 182

## **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called *statements*. Each statement can contain labels, operations, operands, and comments.

Labels are assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

177

#### Table 108. Notational Shorthand (Continued)

| Notation | Description           | Operand | Range                                                                                                                     |

|----------|-----------------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| RA       | Relative Address      | Х       | X represents an index in the range of $+127$ to $-128$ which is an offset relative to the address of the next instruction |

| rr       | Working Register Pair | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                         |

| RR       | Register Pair         | Reg     | Reg. represents an even number in the range of 00H to FEH.                                                                |

| Vector   | Vector Address        | Vector  | Vector represents a number in the range of 00H to FFH.                                                                    |

| X        | Indexed               | #Index  | The register or register pair to be indexed is offset<br>by the signed Index value (#Index) in a +127 to<br>-128 range.   |

Table 109 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol | Definition                |  |  |  |  |  |

|--------|---------------------------|--|--|--|--|--|

| dst    | Destination Operand       |  |  |  |  |  |

| src    | Source Operand            |  |  |  |  |  |

| @      | Indirect Address Prefix   |  |  |  |  |  |

| SP     | Stack Pointer             |  |  |  |  |  |

| PC     | Program Counter           |  |  |  |  |  |

| FLAGS  | Flags Register            |  |  |  |  |  |

| RP     | Register Pointer          |  |  |  |  |  |

| #      | Immediate Operand Prefix  |  |  |  |  |  |

| В      | Binary Number Suffix      |  |  |  |  |  |

| %      | Hexadecimal Number Prefix |  |  |  |  |  |

| Н      | Hexadecimal Number Suffix |  |  |  |  |  |

#### Table 109. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.

$dst \leftarrow dst + src$

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

## eZ8 CPU Instruction Classes

eZ8 CPU instructions are divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

Tables 110 through 117 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| СР       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| СРХ      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

| INCW     | dst      | Increment Word                               |

201

ilog nbedded in Life

## **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 125 tabulates the electrical characteristics of the POR and VBO blocks.

#### Table 125. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                   |                                                                                  | T <sub>A</sub> = - | –40°C to +′     | 105°C   |       |                                                                                           |

|-------------------|----------------------------------------------------------------------------------|--------------------|-----------------|---------|-------|-------------------------------------------------------------------------------------------|

| Symbol            | Parameter                                                                        | Minimum            | Typical*        | Maximum | Units | Conditions                                                                                |

| V <sub>POR</sub>  | Power-On Reset Voltage<br>Threshold                                              | 2.20               | 2.45            | 2.70    | V     | $V_{DD} = V_{POR}$                                                                        |

| V <sub>VBO</sub>  | Voltage Brown-Out Reset Volt-<br>age Threshold                                   | 2.15               | 2.40            | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                        |

|                   | $V_{\mbox{POR}}$ to $V_{\mbox{VBO}}$ hysteresis                                  |                    | 50              | 75      | mV    |                                                                                           |

|                   | Starting V <sub>DD</sub> voltage to ensure valid Power-On Reset.                 | -                  | V <sub>SS</sub> | _       | V     |                                                                                           |

| T <sub>ANA</sub>  | Power-On Reset Analog Delay                                                      | -                  | 70              | -       | μs    | $V_{DD} > V_{POR};$<br>$T_{POR}$ Digital<br>Reset delay fol-<br>lows $T_{ANA}$            |

| T <sub>POR</sub>  | Power-On Reset Digital Delay                                                     |                    | 16              |         | μs    | 66 Internal Precision Oscillator<br>cycles + IPO<br>startup time<br>(T <sub>IPOST</sub> ) |

| T <sub>SMR</sub>  | Stop Mode Recovery                                                               |                    | 16              |         | μs    | 66 Internal Precision Oscillator cycles                                                   |

| T <sub>VBO</sub>  | Voltage Brown-Out Pulse<br>Rejection Period                                      | -                  | 10              | _       | μs    | Period of time in<br>which $V_{DD} < V_{VBO}$ without<br>generating a<br>Reset.           |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to transition from $V_{SS}$ to $V_{POR}$ to ensure valid Reset | 0.10               | -               | 100     | ms    |                                                                                           |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                    |                    | 20              |         | ns    | For any SMR pin<br>or for the Reset<br>pin when it is<br>asserted in STOF<br>Mode.        |

guidance only and are not tested in production.

## Embedded in Life An IXYS Company 206

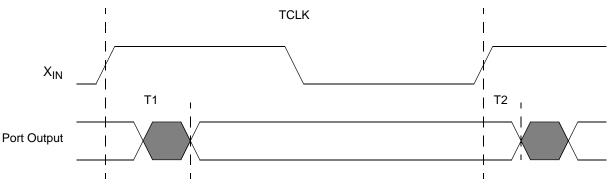

## **General Purpose I/O Port Output Timing**

Figure 30 and Table 131 provide timing information for GPIO Port pins.

|                |                                                 | Delay (ns) |         |  |  |

|----------------|-------------------------------------------------|------------|---------|--|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |  |

| GPIO Port p    | bins                                            |            |         |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _          | 15      |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |  |  |

#### Table 131. GPIO Port Output Timing

> ilog Embedded in Life An IXYS Company 217

|                                                                                |           |         |           |            |                        |                     | •              | · · · ·             |

|--------------------------------------------------------------------------------|-----------|---------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                                                                    | Flash     | RAM     | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 Series with 1 KB Flash, 10-Bit Analog-to-Digital Converter |           |         |           |            |                        |                     | tal Converter  |                     |

| Standard Temperatu                                                             | re: 0°C t | o 70°C  |           |            |                        |                     |                |                     |

| Z8F0123PB005SG                                                                 | 1 KB      | 256 B   | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0123QB005SG                                                                 | 1 KB      | 256 B   | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0123SB005SG                                                                 | 1 KB      | 256 B   | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0123SH005SG                                                                 | 1 KB      | 256 B   | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0123HH005SG                                                                 | 1 KB      | 256 B   | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0123PH005SG                                                                 | 1 KB      | 256 B   | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0123SJ005SG                                                                 | 1 KB      | 256 B   | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0123HJ005SG                                                                 | 1 KB      | 256 B   | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0123PJ005SG                                                                 | 1 KB      | 256 B   | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatu                                                             | ure: –40° | C to 10 | 5°C       |            |                        |                     |                |                     |

| Z8F0123PB005EG                                                                 | 1 KB      | 256 B   | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0123QB005EG                                                                 | 1 KB      | 256 B   | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0123SB005EG                                                                 | 1 KB      | 256 B   | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0123SH005EG                                                                 | 1 KB      | 256 B   | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0123HH005EG                                                                 | 1 KB      | 256 B   | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0123PH005EG                                                                 | 1 KB      | 256 B   | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0123SJ005EG                                                                 | 1 KB      | 256 B   | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0123HJ005EG                                                                 | 1 KB      | 256 B   | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0123PJ005EG                                                                 | 1 KB      | 256 B   | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

nbedded in Life

read OCD revision (00H) 163 read OCD status register (02H) 163 read program counter (07H) 164 read program memory (0BH) 164 read program memory CRC (0EH) 165 read register (09H) 164 read runtime counter (03H) 163 step instruction (10H) 165 stuff instruction (11H) 166 write data memory (0CH) 165 write OCD control register (04H) 163 write program counter (06H) 163 write program memory (0AH) 164 write register (08H) 164 on-chip debugger (OCD) 156 on-chip debugger signals 10 ONE-SHOT mode 88 opcode map abbreviations 193 cell description 192 first 194 second after 1FH 195 Operational Description 21, 30, 33, 69, 91, 97, 117, 121, 132, 134, 146, 156, 169, 173 OR 181 ordering information 211 **ORX 181**

### Ρ

p 176 Packaging 210 part selection guide 2 PC 177 peripheral AC and DC electrical characteristics 201 pin characteristics 11 Pin Descriptions 7 polarity 176 POP 180 pop using extended addressing 180 POPX 180 port availability, device 33 port input timing (GPIO) 205 port output timing, GPIO 206 power supply signals 10

Power-on and Voltage Brownout electrical characteristics and timing 201

Power-On Reset (POR) 23

program control instructions 181

program counter 177

program memory 13

PUSH 180

push using extended addressing 180

PUSHX 180

PWM mode 89

PxADDR register 41

PxCTL register 42

## R

R 176 r 176 RA register address 177 RCF 179. 180 receive IrDA data 119 receiving UART data-interrupt-driven method 102 receiving UART data-polled method 101 register 176 ADC control (ADCCTL) 126, 129 ADC data high byte (ADCDH) 130 ADC data low bits (ADCDL) 131 flash control (FCTL) 141, 148, 149 flash high and low byte (FFREQH and FRE-EQL) 144 flash page select (FPS) 142, 144 flash status (FSTAT) 142 GPIO port A-H address (PxADDR) 41 GPIO port A-H alternate function sub-registers 44 GPIO port A-H control address (PxCTL) 42 GPIO port A-H data direction sub-registers 43 OCD control 166 OCD status 168 UARTx baud rate high byte (UxBRH) 115 UARTx baud rate low byte (UxBRL) 115 UARTx Control 0 (UxCTL0) 112, 115

UARTx control 1 (UxCTL1) 113 UARTx receive data (UxRXD) 109 UARTx status 0 (UxSTAT0) 110 UARTx status 1 (UxSTAT1) 111 UARTx transmit data (UxTXD) 109 Watchdog Timer control (WDTCTL) 94, 133 watch-dog timer control (WDTCTL) 172 Watchdog Timer reload high byte (WDTH) 95 Watchdog Timer reload low byte (WDTL) 95 Watchdog Timer reload upper byte (WDTU) 95 register file 13 register pair 177 register pointer 177 reset and stop mode characteristics 21 and stop mode recovery 21 carry flag 179 sources 23 **RET 181** return 181 RL 181 **RLC 181** rotate and shift instructions 181 rotate left 181 rotate left through carry 181 rotate right 182 rotate right through carry 182 RP 177 RR 177, 182 rr 177 **RRC 182**

## S

SBC 179 SCF 179, 180 second opcode map after 1FH 195 set carry flag 179, 180 set register pointer 180 shift right arithmetic 182 shift right logical 182 signal descriptions 9 single-sho conversion (ADC) 123 software trap 181 source operand 177 SP 177 **SRA 182** src 177 **SRL 182 SRP 180** stack pointer 177 **STOP 180** STOP mode 30, 180 Stop Mode Recovery sources 26 using a GPIO port pin transition 27, 28 using Watchdog Timer time-out 27 **SUB 179** subtract 179 subtract - extended addressing 179 subtract with carry 179 subtract with carry - extended addressing 179 **SUBX 179 SWAP 182** swap nibbles 182 symbols, additional 177

## Т

**TCM 179 TCMX 179** test complement under mask 179 test complement under mask - extended addressing 179 test under mask 179 test under mask - extended addressing 179 timer signals 9 timers 69 architecture 70 block diagram 70 CAPTURE mode 78, 79, 89 CAPTURE/COMPARE mode 82, 89 COMPARE mode 80, 89 CONTINUOUS mode 71, 88 COUNTER mode 72, 73 **COUNTER modes 89** GATED mode 81, 89