Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223qb005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 30. | GPIO Port Output Timing | 206 |

|------------|-------------------------|-----|

| Figure 31. | On-Chip Debugger Timing | 207 |

| Figure 32. | UART Timing With CTS    | 208 |

| Figure 33. | UART Timing Without CTS | 209 |

9

IXYS Company

**Note:** \*Analog input alternate functions (ANA) are not available on Z8F0x13 devices.

## **Signal Descriptions**

>

Table 3 lists the Z8 Encore! XP F0823 Series signals. To determine the signals available for the specific package styles, see the Pin Configurations section on page 7.

| Signal Mnemonic      | I/O     | Description                                                                                                                                                                                                                                                                                             |

|----------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/   | O Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]              | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0] <sup>1</sup> | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]              | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| UART Controllers     |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                 | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                 | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                 | I       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                   | Ο       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 Register. The DE signal can be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers               |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT          | 0       | Timer Output 0–1. These signals are output from the timers.                                                                                                                                                                                                                                             |

| T0OUT/T1OUT          | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM DUAL OUTPUT Mode.                                                                                                                                                                                                          |

| T0IN/T1IN            | I       | Timer Input 0–1. These signals are used as the capture, gating and counter inputs. The T0IN signal is multiplexed T0OUT signals.                                                                                                                                                                        |

| Comparator           |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN            | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| Notes:               |         |                                                                                                                                                                                                                                                                                                         |

#### **Table 3. Signal Descriptions**

1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

edded in Life

Iloa

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the STOP bit in the Watchdog Timer Control Register is set to 1. Table 11 lists the Stop Mode Recovery sources and resulting actions. The section following the table provides more detailed information about each of the Stop Mode Recovery sources.

| <b>Operating Mode</b> | Stop Mode Recovery Source                                                      | Action                                                               |

|-----------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP Mode             | Watchdog Timer time-out when configured for Reset                              | Stop Mode Recovery                                                   |

|                       | Watchdog Timer time-out when configured for interrupt                          | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                       | Data transition on any GPIO port pin<br>enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |

|                       | Assertion of external RESET Pin                                                | System Reset                                                         |

|                       | Debug Pin driven Low                                                           | System Reset                                                         |

#### Table 11. Stop Mode Recovery Sources and Resulting Action

## Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Watchdog Timer Control Register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and Z8 Encore! XP F0823 Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

## Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO port pins can be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

**Note:** The SMR pulses shorter than specified does not trigger a recovery. When this happens, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the port transition only if the signal stays on the port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the port pin can initiate Stop Mode Recovery without being written to the Port Input Data Register or without initiating an interrupt (if enabled for that pin).

# Embedded in Life

| Port Register   |                                   |

|-----------------|-----------------------------------|

| Mnemonic        | Port Register Name                |

| P <i>x</i> HDE  | High Drive Enable.                |

| P <i>x</i> SMRE | Stop Mode Recovery Source Enable. |

| P <i>x</i> PUE  | Pull-up Enable.                   |

| PxAFS1          | Alternate Function Set 1.         |

| PxAFS2          | Alternate Function Set 2.         |

#### Table 18. GPIO Port Registers and Subregisters (Continued)

## **Port A–C Address Registers**

The Port A–C Address registers select the GPIO port functionality accessible through the Port A–C Control registers. The Port A–C Address and Control registers combine to provide access to all GPIO port controls (Table 19).

| Table 19. Port | A-C GPIO | Address R | egisters ( | (P <i>x</i> ADDR) |

|----------------|----------|-----------|------------|-------------------|

|----------------|----------|-----------|------------|-------------------|

| Bit     | 7                                                               | 6          | 5 | 4        | 3        | 2 | 1 | 0 |

|---------|-----------------------------------------------------------------|------------|---|----------|----------|---|---|---|

| Field   |                                                                 | PADDR[7:0] |   |          |          |   |   |   |

| RESET   | 00H                                                             |            |   |          |          |   |   |   |

| R/W     | R/W         R/W         R/W         R/W         R/W         R/W |            |   |          |          |   |   |   |

| Address |                                                                 |            | · | FD0H, FD | 4H, FD8H |   |   |   |

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The Port Address selects one of the subregisters accessible through the Port Control Register. |

|       | See Table 20 for each subregister function.                                                    |

#### Table 20. PADDR[7:0] Subregister Functions

| PADDR[7:0] | Port Control Subregister Accessible Using the Port A–C Control Registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental Port reconfiguration. |

| 01H        | Data Direction.                                                                |

| 02H        | Alternate Function.                                                            |

| 03H        | Output Control (Open-Drain).                                                   |

| 04H        | High Drive Enable.                                                             |

#### ilog° Embedded in Life An TXYS Company

61

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 38) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit           | 7                                                                                                                                                                    | 6             | 5              | 4           | 3    | 2    | 1    | 0    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-------------|------|------|------|------|

| Field         |                                                                                                                                                                      | Rese          | erved          |             | PC3I | PC2I | PC1I | PC0I |

| RESET         | 0                                                                                                                                                                    | 0             | 0              | 0           | 0    | 0    | 0    | 0    |

| R/W           | R/W                                                                                                                                                                  | R/W           | R/W            | R/W         | R/W  | R/W  | R/W  | R/W  |

| Address       |                                                                                                                                                                      | FC6H          |                |             |      |      |      |      |

| Bit           | Description                                                                                                                                                          |               |                |             |      |      |      |      |

| [7:4]         | Reserved<br>These bits are reserved and must be programmed to 0000.                                                                                                  |               |                |             |      |      |      |      |

| [3:0]<br>PCxI | Port C Pin x Interrupt Request<br>0 = No interrupt request is pending for GPIO Port C pin x.<br>1 = An interrupt request from GPIO Port C pin x is awaiting service. |               |                |             |      |      |      |      |

| Note: x in    | dicates the sp                                                                                                                                                       | ecific GPIO F | Port C pin nun | nber (3–0). |      |      |      |      |

#### Table 38. Interrupt Request 2 Register (IRQ2)

## **IRQ0 Enable High and Low Bit Registers**

Table 39 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 40 and Table 41) form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register. Priority is generated by setting bits in each register.

| Table 39. IRQ0 Enable and Priority Encoding |

|---------------------------------------------|

|---------------------------------------------|

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Note: where x indicates the register bits from 0–7.

#### Table 47. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |  |

|---------|-----|------|-------|-----|-------|-------|-------|-------|--|--|

| Field   |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |  |  |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |     | FC8H |       |     |       |       |       |       |  |  |

| Bit          | Description                                                                |

|--------------|----------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENL | Port C3 Interrupt Request Enable Low Bit                                   |

| [2]<br>C2ENL | Port C2 Interrupt Request Enable Low Bit                                   |

| [1]<br>C1ENL | Port C1 Interrupt Request Enable Low Bit                                   |

| [0]<br>C0ENL | Port C0 Interrupt Request Enable High Low                                  |

## Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) Register (Table 48) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|------|------|------|------|------|------|------|------|--|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |

| Address | FCDH |      |      |      |      |      |      |      |  |

| Table 48. | Interrupt | Edae | Select | Register | (IRQES) |

|-----------|-----------|------|--------|----------|---------|

|           |           |      |        |          |         |

| Bit         | Description                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IESx | <b>Interrupt Edge Select</b> $x$<br>0 = An interrupt request is generated on the falling edge of the PA $x$ input or PD $x$ .<br>1 = An interrupt request is generated on the rising edge of the PA $x$ input PD $x$ . |

Note: x indicates the specific GPIO port pin number (7–0).

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is

# Embedded in Life

two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

Table 57. Timer 0–1 Control Register 0 (TxCTL0)

| Table 57. Timer 0–1 Control Register 0 (TxCTL0) |                                                                                                                |                                                                                                                                                                                                                                                                                                      |                                              |                                                    |             |             |     |              |  |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------|-------------|-------------|-----|--------------|--|--|--|

| Bit                                             | 7                                                                                                              | 6                                                                                                                                                                                                                                                                                                    | 5                                            | 4                                                  | 3           | 2           | 1   | 0            |  |  |  |

| Field                                           | TMODEHI                                                                                                        | TICO                                                                                                                                                                                                                                                                                                 | NFIG                                         | Reserved                                           |             | PWMD        |     | INPCAP       |  |  |  |

| RESET                                           | 0                                                                                                              | 0                                                                                                                                                                                                                                                                                                    | 0                                            | 0                                                  | 0           | 0           | 0   | 0            |  |  |  |

| R/W                                             | R/W                                                                                                            | R/W                                                                                                                                                                                                                                                                                                  | R/W                                          | R/W                                                | R/W         | R/W         | R/W | R/W          |  |  |  |

| Address                                         |                                                                                                                |                                                                                                                                                                                                                                                                                                      |                                              | F06H,                                              | F0EH        | ·           |     |              |  |  |  |

| Bit                                             | Descript                                                                                                       | Description                                                                                                                                                                                                                                                                                          |                                              |                                                    |             |             |     |              |  |  |  |

| [7]<br>TMODEHI                                  | This bit a                                                                                                     | <b>Timer Mode High Bit</b><br>This bit along with the TMODE field in TxCTL1 Register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value.                                                                                                 |                                              |                                                    |             |             |     |              |  |  |  |

| [6:5]<br>TICONFIG                               | 6 This field<br>0x = Tim<br>10 = Tim                                                                           | Timer Interrupt ConfigurationThis field configures timer interrupt definition. $0x = Timer$ Interrupt occurs on all defined reload, compare and input events. $10 = Timer$ Interrupt only on defined input capture/deassertion events. $11 = Timer$ Interrupt only on defined reload/compare events. |                                              |                                                    |             |             |     |              |  |  |  |

| [4]                                             | <b>Reserve</b><br>This bit is                                                                                  |                                                                                                                                                                                                                                                                                                      | and must be                                  | programme                                          | d to 0.     |             |     |              |  |  |  |

| [3:1]<br>PWMD                                   | This field<br>before th<br>000 = Nc<br>001 = 2 c<br>010 = 4 c<br>011 = 8 c<br>100 = 16<br>101 = 32<br>110 = 64 | e Timer Ou                                                                                                                                                                                                                                                                                           | mmable del<br>tput and the<br>y.<br>y.<br>y. | ay to control                                      |             |             |     |              |  |  |  |

| [0]<br>INPCAP                                   | This bit i<br>0 = Previ                                                                                        | ious timer in                                                                                                                                                                                                                                                                                        | ne most rec<br>iterrupt is no                | ent timer inte<br>ot a result of<br>result of Time | Timer Input | capture eve | •   | pture event. |  |  |  |

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

#### ILOG<sup>°</sup> Inbedded in Life

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

## Operation

The WDT is a retriggerable one-shot timer that resets or interrupts F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 59 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10kHz typical WDT oscillator frequency) |                        |  |  |  |

|------------------|------------------|-----------------------------------------------------------------------------|------------------------|--|--|--|

| (Hex)            | (Decimal)        | Typical                                                                     | Description            |  |  |  |

| 000004           | 4                | 400 μs                                                                      | Minimum time-out delay |  |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                                  | Maximum time-out delay |  |  |  |

#### Table 59. Watchdog Timer Approximate Time-Out Delays

#### ilog<sup>®</sup> Embedded in Life An∎IXYS Company 94

<u>Watchdog Timer Reload High Byte Register (WDTH)</u>: see page 95 <u>Watchdog Timer Reload Low Byte Register (WDTL)</u>: see page 95

## Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status Register.

| Bit              | 7                                                                                                                                       | 6    | 5 | 4   | 3    | 2 | 1 | 0 |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|---|-----|------|---|---|---|--|

| Field            |                                                                                                                                         |      |   | WDT | UNLK |   |   |   |  |

| RESET            | Х                                                                                                                                       | Х    | Х | Х   | Х    | Х | Х | Х |  |

| R/W              | W                                                                                                                                       | W    | W | W   | W    | W | W | W |  |

| Address          | ess FF0H                                                                                                                                |      |   |     |      |   |   |   |  |

| Bit              | Descrip                                                                                                                                 | tion |   |     |      |   |   |   |  |

| [7:0]<br>WDTUNLK | Watchdog Timer Unlock           .K         The software must write the correct unlocking sequence to this register before it is allowed |      |   |     |      |   |   |   |  |

Table 60. Watchdog Timer Control Register (WDTCTL)

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 61 through 63, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT Reload Value must not be set to a value less than 000004H.

to modify the contents of the Watchdog Timer reload registers.

## Operation

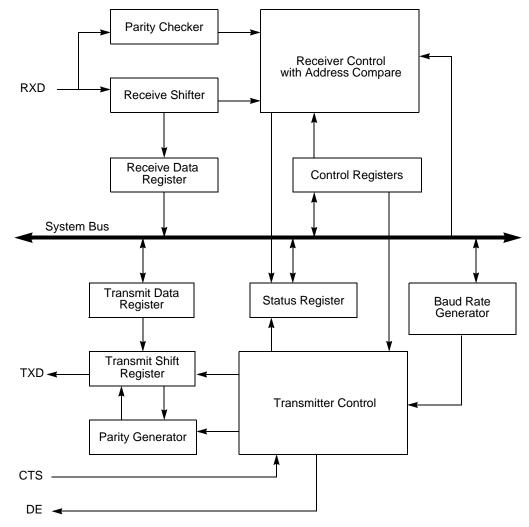

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

#### ilog Embedded in Life An IXYS Company 117

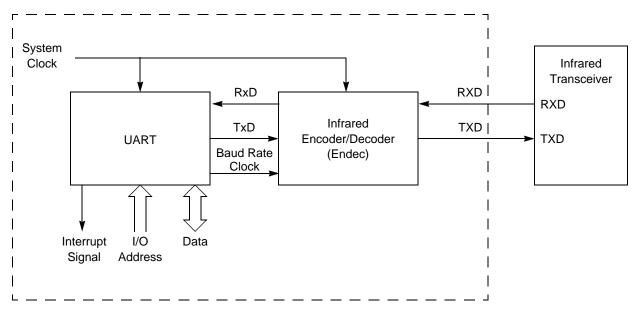

## Infrared Encoder/Decoder

Z8 Encore! XP F0823 Series products contain a fully-functional, high-performance UART with an infrared encoder/decoder (endec). The infrared endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

## Architecture

Figure 16 displays the architecture of the infrared endec.

Figure 16. Infrared Data Communication System Block Diagram

## Operation

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the infrared endec through the RXD pin, decoded by the infrared endec, and

Embedded in Life An TIXYS Company

bits can only be set to 1. Thus, sectors can be protected, but not unprotected, via register write operations. Writing a value other than 5EH to the Flash Control Register deselects the Flash Sector Protect Register and reenables access to the Page Select Register.

Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control Register to return the Flash Controller to its reset state.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased by the CPU. External Flash programming through the OCD or via the Flash Controller Bypass mode are unaffected. After a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

## **Byte Programming**

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully enabled, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming is accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. For a description of the LDC and LDCI instructions, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, available for download at <u>www.zilog.com</u>. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control Register, except the Mass Erase or Page Erase commands.

# **Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

ILO<u>G</u> nbedded in Life

141

- Programming operations are not limited to the page selected in the Page Select register

- Bits in the Flash Sector Protect register can be written to one or zero

- The second write of the Page Select register to unlock the Flash Controller is not necessary

- The Page Select register can be written when the Flash Controller is unlocked

- The Mass Erase command is enabled through the Flash Control Register

**Caution:** For security reasons, the Flash Controller allows only a single page to be opened for write/erase. When writing multiple Flash pages, the Flash controller must repeat the unlock sequence to select another page.

## **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 141

Flash Status Register: see page 143

Flash Page Select Register: see page 143

Flash Sector Protect Register: see page 145

Flash Frequency High and Low Byte Registers: see page 145

## **Flash Control Register**

٠

The Flash Controller must be unlocked using the Flash Control (FTCTL) Register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select register. Mass Erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

ilog Embedded in Life

IXYS Company

149

## **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits.

| Bit     | 7   | 6                    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|----------------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | TRMDR: Trim Bit Data |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0                    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W | R/W                  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | FF7H                 |     |     |     |     |     |     |  |  |

#### Table 88. Trim Bit Data Register (TRMDR)

## Flash Option Bit Address Space

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

#### Table 89. Flash Option Bits at Program Memory Address 0000H

| Bit       | 7            | 6                                             | 5        | 4   | 3      | 2   | 1        | 0   |  |  |

|-----------|--------------|-----------------------------------------------|----------|-----|--------|-----|----------|-----|--|--|

| Field     | WDT_RES      | WDT_AO                                        | Reserved |     | VBO_AO | FRP | Reserved | FWP |  |  |

| RESET     | U            | U                                             | U        | U   | U      | U   | U        | U   |  |  |

| R/W       | R/W          | R/W                                           | R/W      | R/W | R/W    | R/W | R/W      | R/W |  |  |

| Address   |              | Program Memory 0000H                          |          |     |        |     |          |     |  |  |

| Note: U = | Unchanged by | Note: U = Unchanged by Reset R/W = Read/Write |          |     |        |     |          |     |  |  |

U = Unchanged by Reset. R/W = Read/Write.

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>WDT_RES | <ul> <li>Watchdog Timer Reset</li> <li>0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.</li> <li>1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                           |

| [6]<br>WDT_AO  | <ul> <li>Watchdog Timer Always ON</li> <li>0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.</li> <li>1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.</li> </ul> |

| [5:4]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 11 during writes, and to 11 when read.                                                                                                                                                                                                                                                                                                |

PS024315-1011

If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/ DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled high. At this point, the PA0/DBG pin can be used to autobaud and cause the device to enter DEBUG Mode. For more details, see the OCD Unlock Sequence (8-Pin Devices Only) section on page 161.

#### Exiting DEBUG Mode

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

- Watchdog Timer reset

- Asserting the **RESET** pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a system reset

### **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 Stop bit as displayed in Figure 25.

|  | START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |  |

|--|-------|----|----|----|----|----|----|----|----|------|--|

|--|-------|----|----|----|----|----|----|----|----|------|--|

Figure 25. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. Zilog recommends that, if possible, the host drives the DBG pin using an open-drain output.

## **OCD** Autobaud Detector/Generator

To run over a range of baud rates (data bits per second) with various system clock frequencies, the OCD contains an auto-baud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data

# eZ8 CPU Instruction Set

This chapter describes the following features of the eZ8 CPU instruction set: <u>Assembly Language Programming Introduction</u>: see page 174 <u>Assembly Language Syntax</u>: see page 175

eZ8 CPU Instruction Notation: see page 176

eZ8 CPU Instruction Classes: see page 178

eZ8 CPU Instruction Summary: see page 182

## **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called *statements*. Each statement can contain labels, operations, operands, and comments.

Labels are assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

Embedded in Life

ilog

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

| SRL      | dst      | Shift Right Logical        |

| SWAP     | dst      | Swap Nibbles               |

#### Table 117. Rotate and Shift Instructions (Continued)

## eZ8 CPU Instruction Summary

Table 118 summarizes the eZ8 CPU instruction set. The table identifies the addressing modes employed by the instruction, the effect upon the Flags Register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly      | Symbolic Operation        | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   | _ Fetch | Instr. |        |   |

|---------------|---------------------------|-----------------|-----|-------------|-------|---|---|---|---------|--------|--------|---|

| Mnemonic      |                           | dst             | src | (Hex)       | С     | Ζ | S | ۷ | D       | Н      | Cycles |   |

| ADC dst, src  | $dst \gets dst + src + C$ | r               | r   | 12          | *     | * | * | * | 0       | *      | 2      | 3 |

|               |                           | r               | lr  | 13          |       |   |   |   |         |        | 2      | 4 |

|               |                           | R               | R   | 14          |       |   |   |   |         |        | 3      | 3 |

|               |                           | R               | IR  | 15          |       |   |   |   |         |        | 3      | 4 |

|               |                           | R               | IM  | 16          |       |   |   |   |         |        | 3      | 3 |

|               |                           | IR              | IM  | 17          |       |   |   |   |         |        | 3      | 4 |

| ADCX dst, src | $dst \gets dst + src + C$ | ER              | ER  | 18          | *     | * | * | * | 0       | *      | 4      | 3 |

|               |                           | ER              | IM  | 19          |       |   |   |   |         |        | 4      | 3 |

#### Table 118. eZ8 CPU Instruction Summary

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

201

ilog nbedded in Life

## **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 125 tabulates the electrical characteristics of the POR and VBO blocks.

#### Table 125. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                   |                                                                                  | T <sub>A</sub> = - | –40°C to +′     | 105°C   |       |                                                                                           |  |

|-------------------|----------------------------------------------------------------------------------|--------------------|-----------------|---------|-------|-------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                                        | Minimum            | Typical*        | Maximum | Units | Conditions                                                                                |  |

| V <sub>POR</sub>  | Power-On Reset Voltage<br>Threshold                                              | 2.20               | 2.45            | 2.70    | V     | $V_{DD} = V_{POR}$                                                                        |  |

| V <sub>VBO</sub>  | Voltage Brown-Out Reset Volt-<br>age Threshold                                   | 2.15               | 2.40            | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                        |  |

|                   | $V_{\mbox{POR}}$ to $V_{\mbox{VBO}}$ hysteresis                                  |                    | 50              | 75      | mV    |                                                                                           |  |

|                   | Starting V <sub>DD</sub> voltage to ensure valid Power-On Reset.                 | -                  | V <sub>SS</sub> | _       | V     |                                                                                           |  |

| T <sub>ANA</sub>  | Power-On Reset Analog Delay                                                      | -                  | 70              | -       | μs    | $V_{DD} > V_{POR};$<br>$T_{POR}$ Digital<br>Reset delay fol-<br>lows $T_{ANA}$            |  |

| T <sub>POR</sub>  | Power-On Reset Digital Delay                                                     |                    | 16              |         | μs    | 66 Internal Precision Oscillator<br>cycles + IPO<br>startup time<br>(T <sub>IPOST</sub> ) |  |

| T <sub>SMR</sub>  | Stop Mode Recovery                                                               |                    | 16              |         | μs    | 66 Internal Precision Oscillator cycles                                                   |  |

| T <sub>VBO</sub>  | Voltage Brown-Out Pulse<br>Rejection Period                                      | -                  | 10              | _       | μs    | Period of time in<br>which $V_{DD} < V_{VBO}$ without<br>generating a<br>Reset.           |  |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to transition from $V_{SS}$ to $V_{POR}$ to ensure valid Reset | 0.10               | -               | 100     | ms    |                                                                                           |  |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                    |                    | 20              |         | ns    | For any SMR pin<br>or for the Reset<br>pin when it is<br>asserted in STOP<br>Mode.        |  |

guidance only and are not tested in production.

## G

GATED mode 89 general-purpose I/O 33 GPIO 4.33 alternate functions 34 architecture 34 control register definitions 40 input data sample timing 204 interrupts 40 port A-C pull-up enable sub-registers 47, 48, 49 port A-H address registers 41 port A-H alternate function sub-registers 43 port A-H control registers 42 port A-H data direction sub-registers 43 port A-H high drive enable sub-registers 45 port A-H input data registers 50 port A-H output control sub-registers 44 port A-H output data registers 51 port A-H stop mode recovery sub-registers 46 port availability by device 33 port input timing 205 port output timing 206

## Η

H 177 HALT 180 halt mode 31, 180 hexadecimal number prefix/suffix 177

## I

I2C 4 IM 176 immediate data 176 immediate operand prefix 177 INC 178 increment 178 increment word 178 INCW 178 indexed 177 indirect address prefix 177 indirect register 176 indirect register pair 176 indirect working register 176 indirect working register pair 176 infrared encoder/decoder (IrDA) 117 Instruction Set 174 instruction set, eZ8 CPU 174 instructions ADC 178 **ADCX 178** ADD 178 **ADDX 178** AND 181 **ANDX 181** arithmetic 178 **BCLR 179 BIT 179** bit manipulation 179 block transfer 179 **BRK 181 BSET 179** BSWAP 179, 181 BTJ 181 **BTJNZ 181 BTJZ 181 CALL 181** CCF 179, 180 **CLR 180** COM 181 CP 178 **CPC 178 CPCX 178** CPU control 180 **CPX 178** DA 178 **DEC 178 DECW 178** DI 180 DJNZ 181 EI 180 **HALT 180 INC 178 INCW 178 IRET 181** JP 181