Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 5MHz                                                      |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 6                                                         |  |

| Program Memory Size        | 2KB (2K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 512 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | A/D 4x10b                                                 |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223sb005eg |  |

## Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| OCD Status Register                                     | 168 |

|---------------------------------------------------------|-----|

| Oscillator Control                                      | 169 |

| Operation                                               |     |

| System Clock Selection                                  |     |

| Clock Failure Detection and Recovery                    |     |

| Oscillator Control Register Definitions                 | 171 |

| Internal Precision Oscillator                           |     |

| Operation                                               | 173 |

| eZ8 CPU Instruction Set                                 | 174 |

| Assembly Language Programming Introduction              | 174 |

| Assembly Language Syntax                                | 175 |

| eZ8 CPU Instruction Notation                            |     |

| eZ8 CPU Instruction Classes                             |     |

| eZ8 CPU Instruction Summary                             | 182 |

| Opcode Maps                                             | 192 |

| Electrical Characteristics                              | 196 |

| Absolute Maximum Ratings                                | 196 |

| DC Characteristics                                      | 197 |

| AC Characteristics                                      |     |

| On-Chip Peripheral AC and DC Electrical Characteristics |     |

| General Purpose I/O Port Input Data Sample Timing       |     |

| General Purpose I/O Port Output Timing                  |     |

| On-Chip Debugger Timing                                 |     |

| UART Timing                                             | 208 |

| Packaging                                               | 210 |

| Ordering Information                                    | 211 |

| Part Number Suffix Designations                         | 220 |

| Index                                                   | 221 |

| Customer Support                                        | 230 |

| Customer Support                                        |     |

# List of Figures

| Figure 1.  | Z8 Encore! XP F0823 Series Block Diagram                                      |

|------------|-------------------------------------------------------------------------------|

| Figure 2.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package |

| Figure 3.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package      |

| Figure 4.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package      |

| Figure 5.  | Power-On Reset Operation                                                      |

| Figure 6.  | Voltage Brown-Out Reset Operation                                             |

| Figure 7.  | GPIO Port Pin Block Diagram                                                   |

| Figure 8.  | Interrupt Controller Block Diagram                                            |

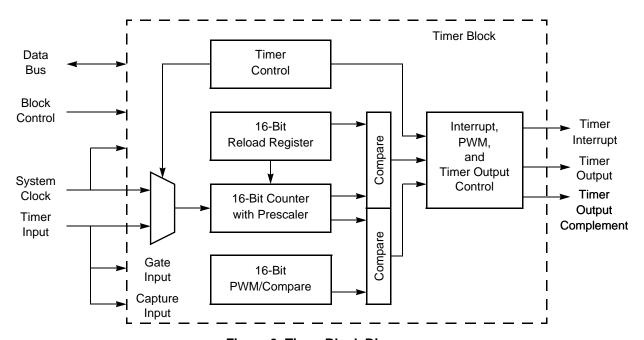

| Figure 9.  | Timer Block Diagram                                                           |

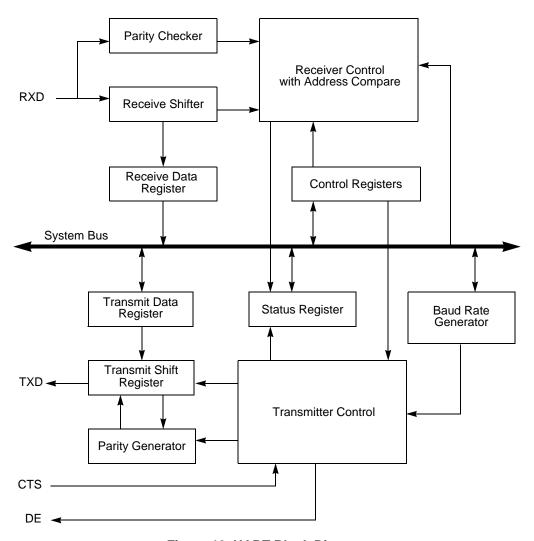

| Figure 10. | UART Block Diagram                                                            |

| Figure 11. | UART Asynchronous Data Format without Parity                                  |

| Figure 12. | UART Asynchronous Data Format with Parity                                     |

| Figure 13. | UART Asynchronous MULTIPROCESSOR Mode Data Format 103                         |

| Figure 14. | UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity) 105       |

| Figure 15. | UART Receiver Interrupt Service Routine Flow                                  |

| Figure 16. | Infrared Data Communication System Block Diagram                              |

| Figure 17. | Infrared Data Transmission                                                    |

| Figure 18. | IrDA Data Reception                                                           |

| Figure 19. | Analog-to-Digital Converter Block Diagram                                     |

| Figure 20. | Flash Memory Arrangement                                                      |

| Figure 21. | Flash Controller Operation Flowchart                                          |

| Figure 22. | On-Chip Debugger Block Diagram                                                |

| Figure 23. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 1 of 2 |

| Figure 24. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 2 of 2 |

| Figure 25. | OCD Data Format                                                               |

| Figure 26. | Opcode Map Cell Description                                                   |

| Figure 27. | •                                                                             |

| Figure 28. |                                                                               |

| Figure 29. | Port Input Sample Timing                                                      |

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the  $\overline{RESET}$  input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the  $\overline{RESET}$  pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following  $\overline{RESET}$  pin deassertion. Following a System Reset initiated by the external  $\overline{RESET}$  pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see **the** <u>Port A–C Control Registers</u> **section on page 42**), the <u>RESET</u> pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

## **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

## **Stop Mode Recovery**

The device enters into STOP Mode when eZ8 CPU executes a STOP instruction. For more details about STOP Mode, see **the** <u>Low-Power Modes</u> **section on page 30**. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

## **Low-Power Modes**

Z8 Encore! XP F0823 Series products contain power-saving features. The highest level of power reduction is provided by the STOP Mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT Mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in ACTIVE mode (defined as being in neither STOP nor HALT Mode).

### **STOP Mode**

Executing the eZ8 CPU's Stop instruction places the device into STOP Mode, powering down all peripherals except the Voltage Brown-Out detector, and the Watchdog Timer. These two blocks may also be disabled for additional power savings. In STOP Mode, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; X<sub>IN</sub> and X<sub>OUT</sub> (if previously enabled) are disabled, and PAO/PA1 revert to the states programmed by the GPIO registers

- System clock is stopped

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control Register

- If enabled, the Watchdog Timer logic continues to operate

- If enabled for operation in STOP Mode by the associated Flash Option Bit, the Voltage Brown-Out protection circuit continues to operate

- All other on-chip peripherals are idle

To minimize current in STOP Mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP Mode using Stop Mode Recovery. For more information about Stop Mode Recovery, see the Reset and Stop Mode Recovery chapter on page 21.

### Port A-C Alternate Function Set 1 Subregisters

The Port A–C Alternate Function Set1 Subregister (Table 28) is accessed through the Port A–C Control Register by writing 07H to the Port A–C Address Register. The Alternate Function Set 1 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in "GPIO Alternate Functions" on page 34.

**Note:** Alternate function selection on port pins must also be enabled as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43.

Table 28. Port A–C Alternate Function Set 1 Subregisters (PAFS1x)

| Bit     | 7         | 6                                                                  | 5           | 4             | 3             | 2            | 1            | 0        |  |  |

|---------|-----------|--------------------------------------------------------------------|-------------|---------------|---------------|--------------|--------------|----------|--|--|

| Field   | PAFS17    | PAFS16                                                             | PAFS15      | PAFS14        | PAFS13        | PAFS12       | PAFS11       | PAFS10   |  |  |

| RESET   |           | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |             |               |               |              |              |          |  |  |

| R/W     | R/W       | R/W                                                                | R/W         | R/W           | R/W           | R/W          | R/W          | R/W      |  |  |

| Address | If 07H ir | Port A–C A                                                         | Address Reg | jister, acces | sible througl | n the Port A | -C Control F | Register |  |  |

| Bit    | Description                                                                                                               |

|--------|---------------------------------------------------------------------------------------------------------------------------|

| [7:0]  | Port Alternate Function Set to 1                                                                                          |

| PAFS1x | 0 = Port Alternate Function selected as defined in Table 15 (see the <u>GPIO Alternate Functions</u> section on page 34). |

|        | 1 = Port Alternate Function selected as defined in Table 15 (see the <u>GPIO Alternate Functions</u> section on page 34). |

Note: x indicates the specific GPIO port pin number (7–0).

**Caution:** To avoid retriggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, Zilog recommends that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as shown in the following example.

CLEARWDT:

LDX r0, RSTSTAT; read reset status register to clear wdt bit

BTJNZ 5, r0, CLEARWDT; loop until bit is cleared

## **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Timer Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 36) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 register to determine if any interrupt requests are pending.

Table 36. Interrupt Request 0 Register (IRQ0)

| Bit     | 7        | 6   | 5   | 4     | 3     | 2        | 1 | 0    |

|---------|----------|-----|-----|-------|-------|----------|---|------|

| Field   | Reserved | T1I | TOI | U0RXI | U0TXI | Reserved |   | ADCI |

| RESET   | 0        | 0   | 0   | 0     | 0     | 0        |   | 0    |

| R/W     | R/W      | R/W | R/W | R/W   | R/W   | R/W      |   | R/W  |

| Address |          |     |     | FC    | 0H    |          |   |      |

| Bit        | Description                                                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| [7]        | Reserved This bit is reserved and must be programmed to 0.                                                                            |

| [6]<br>T1I | Timer 1 Interrupt Request 0 = No interrupt request is pending for Timer 1. 1 = An interrupt request from Timer 1 is awaiting service. |

| [5]<br>T0I | Timer 0 Interrupt Request 0 = No interrupt request is pending for Timer 0. 1 = An interrupt request from Timer 0 is awaiting service. |

### **Architecture**

Figure 9 displays the architecture of the timers.

Figure 9. Timer Block Diagram

## **Operation**

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a PWM output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps to configure a timer for PWM Single Output mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H); this write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

### **Watchdog Timer Refresh**

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

### **Watchdog Timer Time-Out Response**

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information about programming of the WDT\_RES Flash Option Bit, see **the** <u>Flash Option Bits</u> chapter on page 146.

### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see the <u>Reset Status Register</u> section on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

#### **WDT Interrupt in STOP Mode**

If configured to generate an interrupt when a time-out occurs and F0823 Series are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. For more information about Stop Mode Recovery, see **the** Reset and Stop Mode Recovery chapter on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

Figure 10. UART Block Diagram

## **Operation**

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

### **UART Address Compare Register**

The UART Address Compare Register stores the multinode network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

Table 70. UART Address Compare Register (U0ADDR)

| Bit     | 7   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|-----------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | COMP_ADDR |     |     |     |     |     |     |  |

| RESET   | 0   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F45H      |     |     |     |     |     |     |  |

| Bit       | Description                                             |

|-----------|---------------------------------------------------------|

| [7:0]     | Compare Address                                         |

| COMP_ADDR | This 8-bit value is compared to incoming address bytes. |

## **UART Baud Rate High and Low Byte Registers**

The UART Baud Rate High and Low Byte registers (Table 71 and Table 72) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

Table 71. UART Baud Rate High Byte Register (U0BRH)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| Field   |     | BRH |     |     |     |     |     |     |  |

| RESET   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     |     |     | F4  | 6H  |     |     |     |  |

Table 72. UART Baud Rate Low Byte Register (U0BRL)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | BRL  |     |     |     |     |     |     |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F47H |     |     |     |     |     |     |  |

139

bits can only be set to 1. Thus, sectors can be protected, but not unprotected, via register write operations. Writing a value other than 5EH to the Flash Control Register deselects the Flash Sector Protect Register and reenables access to the Page Select Register.

Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control Register to return the Flash Controller to its reset state.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased by the CPU. External Flash programming through the OCD or via the Flash Controller Bypass mode are unaffected. After a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

## **Byte Programming**

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully enabled, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming is accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. For a description of the LDC and LDCI instructions, refer to the eZ8 CPU Core User Manual (UM0128), available for download at <a href="https://www.zilog.com">www.zilog.com</a>. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control Register, except the Mass Erase or Page Erase commands.

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

## Flash Sector Protect Register

The Flash Sector Protect (FPROT) Register is shared with the Flash Page Select Register. When the Flash Control Register is written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

Table 84. Flash Sector Protect Register (FPROT)

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address |        |        |        | FF     | 9H     |        |        |        |

#### Bit Description

#### [7] Sector Protection

SPROT*n* Each bit corresponds to a 1024-byte Flash sector on devices in the 8K range, while the remaining devices correspond to a 512-byte Flash sector. To determine the appropriate Flash memory sector address range and sector number for your Z8F0823 Series product, please refer to <u>Table 79</u> on page 134 and to Figure 20, which follows the table.

- For Z8F08x3 and Z8F04x3 devices, all bits are used.

- For Z8F02x3 devices, the upper 4 bits are unused.

- For Z8F01x3 devices, the upper 6 bits are unused.

Note: n indicates the specific Flash sector (7–0).

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20kHz or above 20MHz.

Table 85. Flash Frequency High Byte Register (FFREQH)

| Bit     | 7      | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|--------|------|-----|-----|-----|-----|-----|-----|

| Field   | FFREQH |      |     |     |     |     |     |     |

| RESET   | 0      | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W    | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |        | FFAH |     |     |     |     |     |     |

| Bit    | Description                                    |

|--------|------------------------------------------------|

| [7:0]  | Flash Frequency High Byte                      |

| FFREQH | High byte of the 16-bit Flash Frequency value. |

Table 86. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7      | 6    | 5 | 4 | 3 | 3 2 1 |  |  |  |  |

|---------|--------|------|---|---|---|-------|--|--|--|--|

| Field   | FFREQL |      |   |   |   |       |  |  |  |  |

| RESET   |        | 0    |   |   |   |       |  |  |  |  |

| R/W     |        | R/W  |   |   |   |       |  |  |  |  |

| Address |        | FFBH |   |   |   |       |  |  |  |  |

| Bit    | Description                                   |

|--------|-----------------------------------------------|

| [7:0]  | Flash Frequency Low Byte                      |

| FFREQL | Low byte of the 16-bit Flash Frequency value. |

Table 118. eZ8 CPU Instruction Summary (Continued)

| Assembly  |                           |     | ress<br>ode | _ Opcode(s) |    |   | Fla | ags |   |   | _ Fetch | Instr. |

|-----------|---------------------------|-----|-------------|-------------|----|---|-----|-----|---|---|---------|--------|

| Mnemonic  | Symbolic Operation        | dst | src         | (Hex)       |    | Z | S   | ٧   | D | Н | Cycles  |        |

| POPX dst  | dst ← @SP<br>SP ← SP + 1  | ER  |             | D8          | _  | - | _   | -   | - | - | 3       | 2      |

| PUSH src  | SP ← SP – 1               | R   |             | 70          | -  | - | -   | -   | - | - | 2       | 2      |

|           | @SP ← src                 | IR  |             | 71          | •  |   |     |     |   |   | 2       | 3      |

|           |                           | IM  |             | IF70        |    |   |     |     |   |   | 3       | 2      |

| PUSHX src | SP ← SP − 1<br>@SP ← src  | ER  |             | C8          | _  | _ | _   | _   | _ | _ | 3       | 2      |

| RCF       | C ← 0                     |     |             | CF          | 0  | _ | _   | _   | _ | _ | 1       | 2      |

| RET       | PC ← @SP<br>SP ← SP + 2   |     |             | AF          | -  | - | -   | -   | - | - | 1       | 4      |

| RL dst    |                           | R   |             | 90          | *  | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 91          | -  |   |     |     |   |   | 2       | 3      |

| RLC dst   | <u> </u>                  | R   |             | 10          | *  | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 11          | -  |   |     |     |   |   | 2       | 3      |

| RR dst    |                           | R   |             | E0          | *  | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  | _           | E1          | =" |   |     |     |   |   | 2       | 3      |

| RRC dst   | <u> </u>                  | R   |             | C0          | *  | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  |             | C1          | •  |   |     |     |   |   | 2       | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

# **Ordering Information**

Order your F0823 Series products from Zilog using the part numbers shown in Table 135. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix

|                     | Table 1    | 33. ZO  | EIICOI    | G: VL      | FU023 (                | oei ies             | Oruei          | ing watrix          |

|---------------------|------------|---------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number         | Flash      | RAM     | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 | 3 Series v | vith 8  | KB Fla    | ash, 10    | -Bit An                | alog-1              | o-Digi         | ital Converter      |

| Standard Temperatu  | re: 0°C to | 70°C    |           |            |                        |                     |                |                     |

| Z8F0823PB005SG      | 8 KB       | 1 KB    | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005SG      | 8 KB       | 1 KB    | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005SG      | 8 KB       | 1 KB    | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005SG      | 8 KB       | 1 KB    | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005SG      | 8 KB       | 1 KB    | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005SG      | 8 KB       | 1 KB    | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005SG      | 8 KB       | 1 KB    | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005SG      | 8 KB       | 1 KB    | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005SG      | 8 KB       | 1 KB    | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatu  | ıre: –40°( | C to 10 | 5°C       |            |                        |                     |                |                     |

| Z8F0823PB005EG      | 8 KB       | 1 KB    | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005EG      | 8 KB       | 1 KB    | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005EG      | 8 KB       | 1 KB    | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005EG      | 8 KB       | 1 KB    | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005EG      | 8 KB       | 1 KB    | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005EG      | 8 KB       | 1 KB    | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005EG      | 8 KB       | 1 KB    | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005EG      | 8 KB       | 1 KB    | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005EG      | 8 KB       | 1 KB    | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

214

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

|                     |               |           |            |                        |                     |                | (                   |

|---------------------|---------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number         | Flash<br>RAM  | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 | Series with   | 4 KB FI   | lash       |                        |                     |                |                     |

| Standard Temperatu  | re: 0°C to 70 | °C        |            |                        |                     |                |                     |

| Z8F0413PB005SG      | 4 KB 1 K      | B 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005SG      | 4 KB 1 K      | B 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005SG      | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005SG      | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005SG      | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005SG      | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005SG      | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005SG      | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005SG      | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu  | ıre: –40°C to | 105°C     |            |                        |                     |                |                     |

| Z8F0413PB005EG      | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005EG      | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005EG      | 4 KB 1 K      | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005EG      | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005EG      | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005EG      | 4 KB 1 K      | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005EG      | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005EG      | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005EG      | 4 KB 1 K      | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| read OCD revision (00H) 163                          | power supply signals 10                          |

|------------------------------------------------------|--------------------------------------------------|

| read OCD status register (02H) 163                   | Power-on and Voltage Brownout electrical charac- |

| read program counter (07H) 164                       | teristics and timing 201                         |

| read program memory (0BH) 164                        | Power-On Reset (POR) 23                          |

| read program memory CRC (0EH) 165                    | program control instructions 181                 |

| read register (09H) 164                              | program counter 177                              |

| read runtime counter (03H) 163                       | program memory 13                                |

| step instruction (10H) 165                           | PUSH 180                                         |

| stuff instruction (11H) 166                          | push using extended addressing 180               |

| write data memory (0CH) 165                          | PUSHX 180                                        |

| write OCD control register (04H) 163                 | PWM mode 89                                      |

| write program counter (06H) 163                      | PxADDR register 41                               |

| write program memory (0AH) 164                       | PxCTL register 42                                |

| write register (08H) 164                             |                                                  |

| on-chip debugger (OCD) 156                           | _                                                |

| on-chip debugger signals 10                          | R                                                |

| ONE-SHOT mode 88                                     | R 176                                            |

| opcode map                                           | r 176                                            |

| abbreviations 193                                    | RA                                               |

| cell description 192                                 | register address 177                             |

| first 194                                            | RCF 179, 180                                     |

| second after 1FH 195                                 | receive                                          |

| Operational Description 21, 30, 33, 69, 91, 97, 117, | IrDA data 119                                    |

| 121, 132, 134, 146, 156, 169, 173                    | receiving UART data-interrupt-driven method 102  |

| OR 181                                               | receiving UART data-polled method 101            |

| ordering information 211                             | register 176                                     |

| ORX 181                                              | ADC control (ADCCTL) 126, 129                    |

|                                                      | ADC data high byte (ADCDH) 130                   |

| <b>B</b>                                             | ADC data low bits (ADCDL) 131                    |

| P                                                    | flash control (FCTL) 141, 148, 149               |

| p 176                                                | flash high and low byte (FFREQH and FRE-         |

| Packaging 210                                        | EQL) 144                                         |

| part selection guide 2                               | flash page select (FPS) 142, 144                 |

| PC 177                                               | flash status (FSTAT) 142                         |

| peripheral AC and DC electrical characteristics 201  | GPIO port A-H address (PxADDR) 41                |

| pin characteristics 11                               | GPIO port A-H alternate function sub-registers   |

| Pin Descriptions 7                                   | 44                                               |

| polarity 176                                         | GPIO port A-H control address (PxCTL) 42         |

| POP 180                                              | GPIO port A-H data direction sub-registers 43    |

| pop using extended addressing 180                    | OCD control 166                                  |

| POPX 180                                             | OCD status 168                                   |

| port availability, device 33                         | UARTx baud rate high byte (UxBRH) 115            |

| port input timing (GPIO) 205                         | UARTx baud rate low byte (UxBRL) 115             |

| port output timing, GPIO 206                         | UARTx Control 0 (UxCTL0) 112, 115                |

| ONE-SHOT mode 70, 88                          | UxSTAT1 register 111                           |

|-----------------------------------------------|------------------------------------------------|

| operating mode 70                             | UxTXD register 109                             |

| PWM mode 75, 76, 89                           |                                                |

| reading the timer count values 83             |                                                |

| reload high and low byte registers 84         | V                                              |

| timer control register definitions 83         | vector 177                                     |

| timer output signal operation 83              | Voltage Brownout reset (VBR) 24                |

| timers 0-3                                    | -                                              |

| control registers 86, 87                      |                                                |

| high and low byte registers 83, 86            | W                                              |

| TM 179                                        | Watchdog Timer                                 |

| TMX 179                                       | approximate time-out delay 91                  |

| tools, hardware and software 220              | CNTL 24                                        |

| transmit                                      | control register 94, 171                       |

| IrDA data 118                                 | electrical characteristics and timing 202, 204 |

| transmitting UART data-polled method 99       | interrupt in normal operation 92               |

| transmitting UART dat-interrupt-driven method | interrupt in STOP mode 92                      |

| 100                                           | refresh 92, 180                                |

| TRAP 181                                      | reload unlock sequence 93                      |

|                                               | reload upper, high and low registers 94        |

|                                               | reset 25                                       |

| U                                             | reset in normal operation 93                   |

| UART 4                                        | reset in STOP mode 93                          |

| architecture 97                               | time-out response 92                           |

| baud rate generator 108                       | Watchdog Timer Control Register (WDTCTL) 94    |

| control register definitions 108              | WDTCTL register 94, 133, 172                   |

| controller signals 9                          | WDTH register 95                               |

| interrupts 105                                | WDTL register 95                               |

| MULTIPROCESSOR mode 103                       | WDTU register 95                               |

| receiving data using interrupt-driven method  | working register 176                           |

| 102                                           | working register pair 177                      |

| receiving data using the polled method 101    |                                                |

| transmitting data using the interrupt-driven  |                                                |

| method 100                                    | X                                              |

| transmitting data using the polled method 99  | X 177                                          |

| x baud rate high and low registers 115        | XOR 181                                        |

| x control 0 and control 1 registers 112       | XORX 181                                       |

| x status 0 and status 1 registers 110, 111    |                                                |

| UxBRH register 115                            |                                                |

| UxBRL register 115                            | Z                                              |

| UxCTL0 register 112, 115                      | Z8 Encore!                                     |

| UxCTL1 register 113                           | block diagram 3                                |

| UxRXD register 109                            | features 1                                     |

| UxSTAT0 register 110                          |                                                |