Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223sb005sg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

7

# **Pin Description**

Z8 Encore! XP F0823 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and pin configurations available for each of the package styles. For information about physical package specifications, see the Packaging chapter on page 210.

# **Available Packages**

Table 2 lists the package styles that are available for each device in the F0823 Series product line.

| Part<br>Number | ADC | 8-pin<br>PDIP | 8-pin<br>SOIC | 20-pin<br>PDIP | 20-pin<br>SOIC | 20-pin<br>SSOP | 28-pin<br>PDIP | 28-pin<br>SOIC | 28-pin<br>SSOP | 8-pin QFN/<br>MLF-S |

|----------------|-----|---------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------|

| Z8F0823        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0813        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0423        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0413        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0223        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0213        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0123        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0113        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

Table 2. F0823 Series Package Options

# **Pin Configurations**

Figures 2 through 4 display the pin configurations for all packages available in the F0823 Series. For description of signals, see Table 3. The analog input alternate functions (ANAx) are not available on the Z8F0x13 devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all pins of Ports A, B, and C default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general-purpose input ports until programmed otherwise.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

#### ilog<sup>°</sup> Embedded in Life 10 An∎IXYS Company

| Signal Mnemonic               | I/O | Description                                                                                                                                                                                                           |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COUT                          | 0   | Comparator Output. This is the output of the comparator.                                                                                                                                                              |

| Analog                        |     |                                                                                                                                                                                                                       |

| ANA[7:0]                      | I   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                          | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                   |     |                                                                                                                                                                                                                       |

| CLKIN                         | Ι   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                   |     |                                                                                                                                                                                                                       |

| LED                           | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programma ble drive strengths set by the GPIO block.                          |

| On-Chip Debugger              |     |                                                                                                                                                                                                                       |

| DBG                           | I/O | Debug. This signal is the control and data input and output to and from the OCD.<br><b>Caution:</b> The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                   |

| Reset                         |     |                                                                                                                                                                                                                       |

| RESET                         | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                  |     |                                                                                                                                                                                                                       |

| V <sub>DD</sub>               | I   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> <sup>2</sup> | I   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>               | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>              | I   | Analog Ground.                                                                                                                                                                                                        |

#### Table 3. Signal Descriptions (Continued)

replaced by AV<sub>DD</sub> and AV<sub>SS</sub>.

The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

#### ilog Embedded in Life An 🛙 IXYS Company

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 8-pin devices.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                         | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up<br>or Pull-<br>down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                    |

|--------------------|-----------|----------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if<br>key<br>sequence<br>detected) | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O<br>(defaults<br><u>to</u><br>RESET)                                    | N/A                                   | Yes                | Program-<br>mable for<br>PA2;<br>always<br>on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

| VSS                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

#### Table 5. Pin Characteristics (8-Pin Devices)

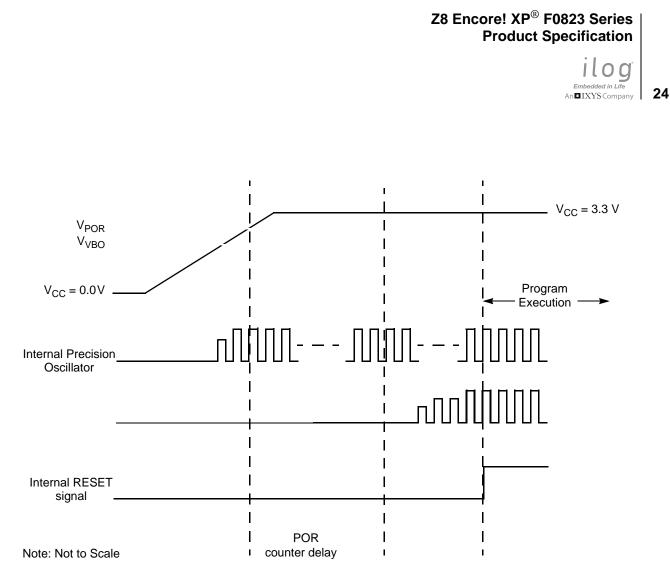

Figure 5. Power-On Reset Operation

# Voltage Brown-Out Reset

The devices in the Z8 Encore! XP F0823 Series provide low VBO protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO threshold voltage) and forces the device into the Reset state. While the supply voltage remains below the POR voltage threshold ( $V_{POR}$ ), the VBO block holds the device in the Reset.

After the supply voltage again exceeds the Power-On Reset voltage threshold, the device progresses through a full System Reset sequence, as described in the <u>Power-On Reset</u> section on page 23. Following POR, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 6 displays Voltage Brown-Out operation. For the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ), see the <u>Electrical Characteristics</u> chapter on page 196.

The VBO circuit can be either enabled or disabled during STOP Mode. Operation during STOP Mode is set by the VBO\_AO Flash Option bit. For information about configuring VBO\_AO, see the <u>Flash Option Bits</u> chapter on page 146.

ILO<u>G</u> abedded in Life

74

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps to configure a timer for COMPARATOR COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer reload in COMPARATOR COUNTER Mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions since the timer start is computed via the following equation:

Comparator Output Transitions = Current Count Value – Start Value

89

#### Bit **Description (Continued)**

#### [6] COUNTER Mode

- TPOL If the timer is enabled the Timer Output signal is complemented after timer reload. (cont'd.)

- 0 =Count occurs on the rising edge of the Timer Input signal.

- 1 = Count occurs on the falling edge of the Timer Input signal.

#### **PWM SINGLE OUTPUT Mode**

- 0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon reload.

- 1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon reload.

#### **CAPTURE Mode**

- 0 = Count is captured on the rising edge of the Timer Input signal.

- 1 = Count is captured on the falling edge of the Timer Input signal.

#### COMPARE Mode

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer reload.

#### GATED Mode

- 0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

- 1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

#### CAPTURE/COMPARE Mode

- 0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

- 1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### **PWM DUAL OUTPUT Mode**

- 0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

- 1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

#### **CAPTURE RESTART Mode**

- 0 = Count is captured on the rising edge of the Timer Input signal.

- 1 = Count is captured on the falling edge of the Timer Input signal.

nbedded in Life

100

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled,.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

#### Transmitting Data Using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

nbedded in Life

101

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) performs the following:

1. Write the UART Control 1 Register to select the multiprocessor bit for the byte to be transmitted:

Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 3. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 4. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data Register to again become empty.

#### **Receiving Data Using the Polled Method**

Observe the following steps to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set an acceptable baud rate for the incoming data stream.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable MULTIPROCESSOR Mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if Multiprocessor mode is not enabled, and select either even or odd parity

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to <u>Step 6</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

- 6. Read data from the UART Receive Data Register. If operating in MULTIPROCES-SOR (9-bit) Mode, further actions may be required depending on the MULTIPRO-CESSOR Mode bits MPMD[1:0].

#### ilog Embedded in Life An IXYS Company 113

| Bit         | Description (Continued)                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>STOP | <ul> <li>Stop Bit Select</li> <li>0 = The transmitter sends one stop bit.</li> <li>1 = The transmitter sends two stop bits.</li> </ul> |

| [0]<br>LBEN | Loop Back Enable<br>0 = Normal operation.<br>1 = All transmitted data is looped back to the receiver.                                  |

#### Table 69. UART Control 1 Register (U0CTL1)

| Bit               | 7        | 6            | 5                       | 4            | 3             | 2            | 1             | 0          |  |  |  |

|-------------------|----------|--------------|-------------------------|--------------|---------------|--------------|---------------|------------|--|--|--|

| Field             | MPMD[1]  | MPEN         | MPMD[0]                 | MPBT         | DEPOL         | BRGCTL       | RDAIRQ        | IREN       |  |  |  |

| RESET             | 0        | 0            | 0                       | 0            | 0             | 0            | 0             | 0          |  |  |  |

| R/W               | R/W      | R/W          | R/W                     | R/W          | R/W           | R/W          | R/W           | R/W        |  |  |  |

| Address           |          | F43H         |                         |              |               |              |               |            |  |  |  |

|                   |          |              |                         |              |               |              |               |            |  |  |  |

| Bit               | Descript | tion         |                         |              |               |              |               |            |  |  |  |

| [7,5]<br>MPMD[1:0 |          | ROCESSO      | R Mode<br>DR (9-bit) Mo | nde is enabl | ed            |              |               |            |  |  |  |

|                   | -        |              | · · ·                   |              |               | aived bytes  | (data and a   | ddrooo)    |  |  |  |

|                   |          | -            | erates an int           | • •          |               | •            | •             | aaress).   |  |  |  |

|                   |          | •            | erates an int           |              |               |              | •             |            |  |  |  |

|                   |          | •            | erates an int           |              |               |              |               |            |  |  |  |

|                   | valu     | le stored in | the Address             | Compare R    | egister and   | on all succe | ssive data b  | ytes until |  |  |  |

|                   | an a     | address mis  | match occur             | S.           |               |              |               |            |  |  |  |

|                   | 11 – Tho |              | arates an inte          | errunt reque | st on all rec | d etch havia | vtes for whic | h the most |  |  |  |

| 11 = The UART generates an interrupt request on all received data bytes for which the most |

|--------------------------------------------------------------------------------------------|

| recent address byte matched the value in the Address Compare Register.                     |

| [6]<br>MPEN  | MULTIPROCESSOR (9-bit) Enable<br>This bit is used to enable MULTIPROCESSOR (9-bit) Mode.<br>0 = Disable MULTIPROCESSOR (9-bit) Mode.<br>1 = Enable MULTIPROCESSOR (9-bit) Mode.                                                                                                                                                                                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>MPBT  | <ul> <li>Multiprocessor Bit Transmit</li> <li>This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.</li> <li>0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).</li> <li>1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li> </ul> |

| [3]<br>DEPOL | Driver Enable Polarity<br>0 = DE signal is Active High.<br>1 = DE signal is Active Low.                                                                                                                                                                                                                                                                                                                                                |

#### Tilog Embedded in Life IXYS Company 123

# **Automatic Powerdown**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to powerup. The ADC powers up when a conversion is requested by the ADC Control Register.

# **Single-Shot Conversion**

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the acceptable analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}

#### ilog Embedded in Life An∎IXYS Company 130

# ADC Data High Byte Register

The ADC Data High Byte Register contains the upper eight bits of the ADC output. The output is an 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit     | 7     | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|---------|-------|---|---|----|----|---|---|---|--|

| Field   | ADCDH |   |   |    |    |   |   |   |  |

| RESET   | Х     | Х | Х | Х  | Х  | Х | Х | Х |  |

| R/W     | R     | R | R | R  | R  | R | R | R |  |

| Address |       |   |   | F7 | 2H |   |   |   |  |

| Table 1 | 76. | ADC | Data | High          | <b>Byte</b> | Register | (ADCD | H) |

|---------|-----|-----|------|---------------|-------------|----------|-------|----|

|         |     |     |      | · · · · · · · | -,          |          | ····· | /  |

# Bit Description [7:0] ADC Data High Byte ADCDH This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

## 137

nbedded in Life

# Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

FFREQ[15:0] = System Clock Frequency (Hz) 1000

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768 Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of Z8 Encore! XP F0823 Series devices.

# Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access with the On-Chip Debugger. Programming the FRP Flash Option Bit prevents reading of the user code with the On-Chip Debugger. For more information, see the <u>Flash Option Bits</u> section on page 146 and the <u>On-Chip Debugger</u> chapter on page 156.

# Flash Code Protection Against Accidental Program and Erasure

F0823 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash Option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash Option Bits combine to provide three levels of Flash Program Memory protection as listed in Table 80. For more information, see the <u>Flash Option Bits</u> section on page 146.

ilog<sup>®</sup>

143

# Flash Status Register

The Flash Status Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

| Bit     | 7          | 6     | 5     | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------------|-------|-------|---|---|---|---|---|--|--|

| Field   | Rese       | erved | FSTAT |   |   |   |   |   |  |  |

| RESET   | 0          | 0     | 0     | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W     | R          | R     | R     | R | R | R | R | R |  |  |

| Address |            | FF8H  |       |   |   |   |   |   |  |  |

| Bit     | Descriptio | n     |       |   |   |   |   |   |  |  |

| Table 82 | . Flash | Status | Register | (FSTAT) |

|----------|---------|--------|----------|---------|

|----------|---------|--------|----------|---------|

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 0 when read.                                                                                                                                                                                                                                                                                           |

| [5:0]<br>FSTAT | Flash Controller Status000000 = Flash Controller locked.000001 = First unlock command received (73H written).000010 = Second unlock command received (8CH written).000011 = Flash Controller unlocked.000100 = Sector protect register selected.001xxx = Program operation in progress.010xxx = Page erase operation in progress.100xxx = Mass erase operation in progress. |

# Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

ILOG<sup>®</sup> Ibedded in Life IXYS Company 164

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

**Read Register (09H).** The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

Write Program Memory (0AH). The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

## Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                       |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data<br>; value 01H, is the source. The value 01H is written into the<br>; Register at address 234H. |

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

#### Example 1

If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 106.

#### Table 106. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

#### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 107.

ilog° Embedded in Life An∎IXYS Company

186

| Assembly      |                          |         | lress<br>ode | _ Opcode(s) |   |   | Fla | ags  |   |   | _ Fetch | Instr. |  |

|---------------|--------------------------|---------|--------------|-------------|---|---|-----|------|---|---|---------|--------|--|

| Mnemonic      | Symbolic Operation       | dst src |              | (Hex)       | С | Ζ | S   | SVDH |   |   |         | Cycles |  |

| LD dst, rc    | $dst \leftarrow src$     | r       | IM           | 0C-FC       | - | _ | -   | -    | - | _ | 2       | 2      |  |

|               |                          | r       | X(r)         | C7          | - |   |     |      |   |   | 3       | 3      |  |

|               |                          | X(r)    | r            | D7          | - |   |     |      |   |   | 3       | 4      |  |

|               |                          | r       | lr           | E3          | - |   |     |      |   |   | 2       | 3      |  |

|               |                          | R       | R            | E4          | - |   |     |      |   |   | 3       | 2      |  |

|               |                          | R       | IR           | E5          | - |   |     |      |   |   | 3       | 4      |  |

|               |                          | R       | IM           | E6          | - |   |     |      |   |   | 3       | 2      |  |

|               |                          | IR      | IM           | E7          | - |   |     |      |   |   | 3       | 3      |  |

|               |                          | lr      | r            | F3          | - |   |     |      |   |   | 2       | 3      |  |

|               |                          | IR      | R            | F5          | - |   |     |      |   |   | 3       | 3      |  |

| LDC dst, src  | $dst \gets src$          | r       | Irr          | C2          | - | _ | _   | -    | _ | - | 2       | 5      |  |

|               |                          | lr      | Irr          | C5          | - |   |     |      |   |   | 2       | 9      |  |

|               |                          | Irr     | r            | D2          | - |   |     |      |   |   | 2       | 5      |  |

| LDCI dst, src | $dst \gets src$          | lr      | Irr          | C3          | - | _ | _   | _    | _ | - | 2       | 9      |  |

|               | r ← r + 1<br>rr ← rr + 1 | Irr     | lr           | D3          | - |   |     |      |   |   | 2       | 9      |  |

| LDE dst, src  | $dst \leftarrow src$     | r       | Irr          | 82          | - | _ | _   | -    | - | - | 2       | 5      |  |

|               |                          | Irr     | r            | 92          | - |   |     |      |   |   | 2       | 5      |  |

| LDEI dst, src | dst $\leftarrow$ src     | lr      | Irr          | 83          | _ | _ | _   | -    | - | _ | 2       | 9      |  |

|               | r ← r + 1<br>rr ← rr + 1 | Irr     | lr           | 93          | - |   |     |      |   |   | 2       | 9      |  |

| LDWX dst, src | dst $\leftarrow$ src     | ER      | ER           | 1FE8        | _ | _ | _   | _    | _ | _ | 5       | 4      |  |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

|   |                                |                                  |                                      |                                        |                                     |                             | Lo                                   | ower Nil                                  | oble (He                                | x)                           |                            |                          |                           |                           |                         |                          |

|---|--------------------------------|----------------------------------|--------------------------------------|----------------------------------------|-------------------------------------|-----------------------------|--------------------------------------|-------------------------------------------|-----------------------------------------|------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|--------------------------|

|   | 0                              | 1                                | 2                                    | 3                                      | 4                                   | 5                           | 6                                    | 7                                         | 8                                       | 9                            | А                          | В                        | С                         | D                         | Е                       | F                        |

| 0 | 1.1<br>BRK                     | 2.2<br>SRP<br>IM                 | 2.3<br><b>ADD</b><br>r1,r2           | 2.4<br><b>ADD</b><br>r1,lr2            | 3.3<br><b>ADD</b><br>R2,R1          | 3.4<br><b>ADD</b><br>IR2,R1 | 3.3<br><b>ADD</b><br>R1,IM           | 3.4<br>ADD<br>IR1,IM                      | 4.3<br>ADDX<br>ER2,ER1                  | 4.3<br>ADDX<br>IM,ER1        | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1        | 2.3<br><b>RLC</b><br>IR1         | 2.3<br>ADC<br>r1,r2                  | 2.4<br>ADC<br>r1,lr2                   | 3.3<br>ADC<br>R2,R1                 | 3.4<br>ADC<br>IR2,R1        | 3.3<br>ADC<br>R1,IM                  | 3.4<br>ADC<br>IR1,IM                      | 4.3<br>ADCX<br>ER2,ER1                  | 4.3<br>ADCX<br>IM,ER1        |                            |                          |                           |                           |                         | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1               | 2.3<br>INC<br>IR1                | 2.3<br><b>SUB</b><br>r1,r2           | 2.4<br>SUB<br>r1,lr2                   | 3.3<br><b>SUB</b><br>R2,R1          | 3.4<br>SUB<br>IR2,R1        | 3.3<br><b>SUB</b><br>R1,IM           | 3.4<br>SUB<br>IR1,IM                      | 4.3<br><b>SUBX</b><br>ER2,ER1           | 4.3<br><b>SUBX</b><br>IM,ER1 |                            |                          |                           |                           |                         | 1                        |

| 3 | 2.2<br>DEC<br>R1               | 2.3<br>DEC<br>IR1                | 2.3<br>SBC<br>r1,r2                  | 2.4<br>SBC<br>r1,lr2                   | 3.3<br>SBC<br>R2,R1                 | 3.4<br>SBC<br>IR2,R1        | 3.3<br>SBC<br>R1,IM                  | 3.4<br>SBC<br>IR1,IM                      | 4.3<br><b>SBCX</b><br>ER2,ER1           | 4.3<br>SBCX                  |                            |                          |                           |                           |                         |                          |

| 4 | 2.2<br>DA<br>R1                | 2.3<br>DA<br>IR1                 | 2.3<br><b>OR</b>                     | 2.4<br>OR                              | 3.3<br>OR<br>R2,R1                  | 3.4<br><b>OR</b>            | 3.3<br><b>OR</b>                     | 3.4<br><b>OR</b>                          | 4.3<br>ORX<br>ER2,ER1                   | 4.3<br>ORX                   |                            |                          |                           |                           |                         |                          |

| 5 | 2.2<br><b>POP</b><br>R1        | 2.3<br><b>POP</b>                | r1,r2<br>2.3<br>AND                  | r1,lr2<br>2.4<br>AND                   | 3.3<br>AND<br>R2,R1                 | 3.4<br>AND                  | 81,IM<br>3.3<br><b>AND</b>           | 3.4<br>AND                                | 4.3<br>ANDX                             | 4.3<br>ANDX                  |                            |                          |                           |                           |                         | 1.2<br>WDT               |

| 6 | 2.2<br>COM                     | 1R1<br>2.3<br>COM                | r1,r2<br>2.3<br>TCM                  | r1,lr2<br>2.4<br>TCM                   | 3.3<br>TCM                          | 3.4<br>TCM                  | 81,IM<br>3.3<br><b>TCM</b>           | 3.4<br>TCM                                | 4.3<br><b>TCMX</b>                      | 4.3<br><b>TCMX</b>           |                            |                          |                           |                           |                         | 1.2<br>STOP              |

| 7 | R1<br>2.2<br><b>PUSH</b><br>R2 | IR1<br>2.3<br><b>PUSH</b><br>IR2 | r1,r2<br>2.3<br><b>TM</b>            | r1,lr2<br>2.4<br><b>TM</b>             | R2,R1<br>3.3<br><b>TM</b>           | IR2,R1<br>3.4<br><b>TM</b>  | R1,IM<br>3.3<br><b>TM</b>            | IR1,IM<br>3.4<br><b>TM</b>                | 4.3<br><b>TMX</b>                       | 4.3<br><b>TMX</b>            |                            |                          |                           |                           |                         | 1.2<br>HALT              |

| 8 | 2.5<br>DECW<br>RR1             | 2.6<br>DECW                      | r1,r2<br>2.5<br>LDE                  | r1,lr2<br>2.9<br><b>LDEI</b>           | R2,R1<br>3.2<br>LDX                 | IR2,R1<br>3.3<br>LDX        | R1,IM<br>3.4<br>LDX                  | IR1,IM<br>3.5<br><b>LDX</b>               | 3.4<br>LDX                              | IM,ER1<br>3.4<br>LDX         |                            |                          |                           |                           |                         | 1.2<br><b>DI</b>         |

| 9 | 2.2<br>RL<br>R1                | IRR1<br>2.3<br><b>RL</b>         | r1,Irr2<br>2.5<br>LDE                | 2.9<br>LDEI                            | r1,ER2<br>3.2<br>LDX                | 1r1,ER2<br>3.3<br>LDX       | 3.4<br>LDX                           | IRR2,IR1<br>3.5<br><b>LDX</b><br>IR2,IRR1 | r1,rr2,X<br>3.3<br><b>LEA</b>           | 3.5<br><b>LEA</b>            |                            |                          |                           |                           |                         | 1.2<br>El                |

| A | 2.5<br>INCW<br>RR1             | IR1<br>2.6<br>INCW<br>IRR1       | r2,Irr1<br>2.3<br><b>CP</b><br>r1,r2 | 1r2,Irr1<br>2.4<br><b>CP</b><br>r1,Ir2 | r2,ER1<br>3.3<br><b>CP</b><br>R2,R1 | 3.4<br><b>CP</b><br>IR2,R1  | 82,IRR1<br>3.3<br><b>CP</b><br>R1,IM | 3.4<br>CP<br>IR1,IM                       | r1,r2,X<br>4.3<br><b>CPX</b><br>ER2,ER1 | 4.3<br>CPX<br>IM,ER1         |                            |                          |                           |                           |                         | 1.4<br>RET               |

| в | 2.2<br>CLR<br>R1               | 2.3<br>CLR<br>IR1                | 2.3<br>XOR<br>r1,r2                  | 2.4<br>XOR<br>r1,lr2                   | 3.3<br>XOR<br>R2,R1                 | 3.4<br>XOR<br>IR2,R1        | 3.3<br>XOR<br>R1,IM                  | 3.4<br>XOR<br>IR1,IM                      | 4.3<br><b>XORX</b><br>ER2,ER1           | 4.3<br><b>XORX</b><br>IM,ER1 |                            |                          |                           |                           |                         | 1.5<br>IRET              |

| С | 2.2<br>RRC<br>R1               | 2.3<br>RRC<br>IR1                | 2.5<br>LDC<br>r1,lrr2                | 2.9<br>LDCI<br>lr1,lrr2                | 2.3<br>JP<br>IRR1                   | 2.9<br>LDC<br>lr1,lrr2      | IXT,IW                               | 3.4<br>LD<br>r1,r2,X                      | 3.2<br>PUSHX<br>ER2                     |                              |                            |                          |                           |                           |                         | 1.2<br>RCF               |

| D | 2.2<br>SRA<br>R1               | 2.3<br>SRA<br>IR1                | 2.5<br>LDC<br>r2,Irr1                | 2.9<br>LDCI<br>lr2,lrr1                | 2.6                                 | 2.2<br>BSWAP<br>R1          | 3.3<br>CALL<br>DA                    | 3.4<br>LD<br>r2,r1,X                      | 3.2<br>POPX<br>ER1                      |                              |                            |                          |                           |                           |                         | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1         | 2.3<br><b>RR</b><br>IR1          | 2.2<br>BIT<br>p,b,r1                 | 2.3<br>LD<br>r1,lr2                    | 3.2<br>LD<br>R2,R1                  | 3.3<br>LD<br>IR2,R1         | 3.2<br>LD<br>R1,IM                   | 3.3<br>LD<br>IR1,IM                       | 4.2<br>LDX<br>ER2,ER1                   | 4.2<br>LDX<br>IM,ER1         |                            |                          |                           |                           |                         | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1              | 2.3<br>SWAP<br>IR1               | 2.6<br>TRAP<br>Vector                | 2.3<br>LD<br>lr1,r2                    | 2.8<br>MULT<br>RR1                  | 3.3<br>LD<br>R2,IR1         | 3.3<br><b>BTJ</b><br>p,b,r1,X        | 3.4<br><b>BTJ</b><br>p,b,lr1,X            |                                         |                              | V                          | ▼                        | V                         | ▼                         | V                       |                          |

Figure 27. First Opcode Map

#### $V_{DD} = 3.0 V$ to 3.6 V $T_A = 0^{\circ}C$ to +70°C (unless otherwise stated) Symbol Parameter **Maximum Units Conditions** Minimum Typical As defined by -3 dB Signal Input Bandwidth 10 kHz \_ point Analog Source Impedance<sup>4</sup> kW In unbuffered mode $R_S$ 10 \_ \_ Zin kW In unbuffered mode at Input Impedance 150 20MHz<sup>5</sup> Vin Input Voltage Range 0 $V_{DD}$ V **Unbuffered Mode**

Table 128. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

| V <sub>DD</sub> = 2.7V to 3.6V<br>T <sub>A</sub> = -40°C to +105°C |                                            |                 |            |                    |       |                    |  |  |  |

|--------------------------------------------------------------------|--------------------------------------------|-----------------|------------|--------------------|-------|--------------------|--|--|--|

| Symbol                                                             | Parameter                                  | Minimum         | Typical    | Maximum            | Units | Conditions         |  |  |  |

| V <sub>OS</sub>                                                    | Input DC Offset                            |                 | 5          |                    | mV    |                    |  |  |  |

| V <sub>CREF</sub>                                                  | Programmable Internal<br>Reference Voltage |                 | <u>+</u> 5 |                    | %     | 20-/28-pin devices |  |  |  |

|                                                                    |                                            |                 | <u>+</u> 3 |                    | %     | 8-pin devices      |  |  |  |

| T <sub>PROP</sub>                                                  | Propagation Delay                          |                 | 200        |                    | ns    |                    |  |  |  |

| V <sub>HYS</sub>                                                   | Input Hysteresis                           |                 | 4          |                    | mV    |                    |  |  |  |

| V <sub>IN</sub>                                                    | Input Voltage Range                        | V <sub>SS</sub> |            | V <sub>DD</sub> -1 | V     |                    |  |  |  |

#### Table 129. Comparator Electrical Characteristics

# General Purpose I/O Port Input Data Sample Timing

Figure 29 displays a timing sequence for the GPIO port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The port value is

225

LDEI 179, 180 LDX 180 LEA 180 load 180 load constant 179 load constant to/from program memory 180 load constant with auto-increment addresses 180 load effective address 180 load external data 180 load external data to/from data memory and autoincrement addresses 179 load external to/from data memory and auto-increment addresses 180 load instructions 180 load using extended addressing 180 logical AND 181 logical AND/extended addressing 181 logical exclusive OR 181 logical exclusive OR/extended addressing 181 logical instructions 181 logical OR 181 logical OR/extended addressing 181 low power modes 30

## Μ

master interrupt enable 56 memory data 15 program 13 mode CAPTURE 89 **CAPTURE/COMPARE 89 CONTINUOUS 88 COUNTER 89** GATED 89 **ONE-SHOT 88 PWM 89** modes 89 **MULT 179** multiply 179 MULTIPROCESSOR mode, UART 103

# Ν

NOP (no operation) 180 notation b 176 cc 176 DA 176 ER 176 IM 176 IR 176 Ir 176 **IRR 176** Irr 176 p 176 R 176 r 176 RA 177 **RR 177** rr 177 vector 177 X 177 notational shorthand 176

# 0

OCD architecture 156 auto-baud detector/generator 159 baud rate limits 160 block diagram 156 breakpoints 161 commands 162 control register 166 data format 159 DBG pin to RS-232 Interface 157 DEBUG mode 158 debugger break 181 interface 157 serial errors 160 status register 168 timing 207 **OCD** commands execute instruction (12H) 166 read data memory (0DH) 165 read OCD control register (05H) 163

228

ONE-SHOT mode 70, 88 operating mode 70 PWM mode 75, 76, 89 reading the timer count values 83 reload high and low byte registers 84 timer control register definitions 83 timer output signal operation 83 timers 0-3 control registers 86, 87 high and low byte registers 83, 86 TM 179 **TMX 179** tools, hardware and software 220 transmit IrDA data 118 transmitting UART data-polled method 99 transmitting UART dat-interrupt-driven method 100 **TRAP 181**

# U

UART 4 architecture 97 baud rate generator 108 control register definitions 108 controller signals 9 interrupts 105 MULTIPROCESSOR mode 103 receiving data using interrupt-driven method 102 receiving data using the polled method 101 transmitting data using the interrupt-driven method 100 transmitting data using the polled method 99 x baud rate high and low registers 115 x control 0 and control 1 registers 112 x status 0 and status 1 registers 110, 111 UxBRH register 115 **UxBRL** register 115 UxCTL0 register 112, 115 UxCTL1 register 113 UxRXD register 109 UxSTAT0 register 110

UxSTAT1 register 111 UxTXD register 109

# V

vector 177 Voltage Brownout reset (VBR) 24

# W

Watchdog Timer approximate time-out delay 91 CNTL 24 control register 94, 171 electrical characteristics and timing 202, 204 interrupt in normal operation 92 interrupt in STOP mode 92 refresh 92, 180 reload unlock sequence 93 reload upper, high and low registers 94 reset 25 reset in normal operation 93 reset in STOP mode 93 time-out response 92 Watchdog Timer Control Register (WDTCTL) 94 WDTCTL register 94, 133, 172 WDTH register 95 WDTL register 95 WDTU register 95 working register 176 working register pair 177

# Χ

X 177 XOR 181 XORX 181

# Ζ

Z8 Encore! block diagram 3 features 1