Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223sh005sg |

## **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                                           | Description                                                                                                                                                                                        | Page<br>No.                             |

|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Sep         | 15                | LED Drive Enable Register                                                                                                                 | Clarified statement surrounding the Alternate Function Register as it relates to the LED function; revised Flash Sector Protect Register description; revised Packaging chapter.                   | 51,<br>144,<br>210                      |

| Mar<br>2008 | 14                | n/a                                                                                                                                       | Changed branding to Z8 Encore! XP F0823 Series where appropriate.                                                                                                                                  | All                                     |

| Dec<br>2007 | 13                | Pin Description, General-Purpose Input/Output, Interrupt Controller, Watchdog Timer, Electrical Characteristics, and Ordering Information | Updated title from Z8 Encore! 8K and 4K Series to Z8 Encore! XP Z8F0823 Series. Updated Figure 3, Table 15, Table 35, Tables 59 through 61, Table 119 and Part Number Suffix Designations section. | 8, 36,<br>60, 95,<br>199,<br>and<br>220 |

| Aug<br>2007 | 12                | Part Selection Guide, External<br>Clock Setup, and Program<br>Memory                                                                      | Updated Table 1, Table 16, and Program Memory section.                                                                                                                                             | 2, <u>35,</u><br>and <u>13</u>          |

| Jun<br>2007 | 11                | n/a                                                                                                                                       | Updated to combine Z8 Encore! 8K and Z8 Encore! 4K Series.                                                                                                                                         | All                                     |

| Dec<br>2006 | 10                | Ordering Information                                                                                                                      | Updated Ordering Information chapter.                                                                                                                                                              | <u>211</u>                              |

# List of Figures

| Figure 1.  | Z8 Encore! XP F0823 Series Block Diagram                                      |

|------------|-------------------------------------------------------------------------------|

| Figure 2.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package |

| Figure 3.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package      |

| Figure 4.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package      |

| Figure 5.  | Power-On Reset Operation                                                      |

| Figure 6.  | Voltage Brown-Out Reset Operation                                             |

| Figure 7.  | GPIO Port Pin Block Diagram                                                   |

| Figure 8.  | Interrupt Controller Block Diagram                                            |

| Figure 9.  | Timer Block Diagram                                                           |

| Figure 10. | UART Block Diagram                                                            |

| Figure 11. | UART Asynchronous Data Format without Parity                                  |

| Figure 12. | UART Asynchronous Data Format with Parity                                     |

| Figure 13. | UART Asynchronous MULTIPROCESSOR Mode Data Format 103                         |

| Figure 14. | UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity) 105       |

| Figure 15. | UART Receiver Interrupt Service Routine Flow                                  |

| Figure 16. | Infrared Data Communication System Block Diagram                              |

| Figure 17. | Infrared Data Transmission                                                    |

| Figure 18. | IrDA Data Reception                                                           |

| Figure 19. | Analog-to-Digital Converter Block Diagram                                     |

| Figure 20. | Flash Memory Arrangement                                                      |

| Figure 21. | Flash Controller Operation Flowchart                                          |

| Figure 22. | On-Chip Debugger Block Diagram                                                |

| Figure 23. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 1 of 2 |

| Figure 24. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 2 of 2 |

| Figure 25. | OCD Data Format                                                               |

| Figure 26. | Opcode Map Cell Description                                                   |

| Figure 27. | •                                                                             |

| Figure 28. |                                                                               |

| Figure 29. | Port Input Sample Timing                                                      |

## Z8 Encore! XP<sup>®</sup> F0823 Series | Product Specification

χi

| Figure 30. | GPIO Port Output Timing | 206 |

|------------|-------------------------|-----|

| Figure 31. | On-Chip Debugger Timing | 207 |

| Figure 32. | UART Timing With CTS    | 208 |

| Figure 33. | UART Timing Without CTS | 209 |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Table 70.  | UART Address Compare Register (U0ADDR)                 | 115 |

|------------|--------------------------------------------------------|-----|

| Table 71.  | UART Baud Rate High Byte Register (U0BRH)              | 115 |

| Table 72.  | UART Baud Rate Low Byte Register (U0BRL)               | 115 |

| Table 73.  | UART Baud Rates                                        | 116 |

| Table 74.  | ADC Control Register 0 (ADCCTL0)                       | 127 |

| Table 75.  | ADC Control/Status Register 1 (ADCCTL1)                | 129 |

| Table 76.  | ADC Data High Byte Register (ADCD_H)                   | 130 |

| Table 77.  | ADC Data Low Bits Register (ADCD_L)                    | 131 |

| Table 78.  | Comparator Control Register (CMP0)                     | 133 |

| Table 79.  | Z8 Encore! XP F0823 Series Flash Memory Configurations | 134 |

| Table 80.  | Flash Code Protection Using the Flash Option Bits      | 138 |

| Table 81.  | Flash Control Register (FCTL)                          | 141 |

| Table 82.  | Flash Status Register (FSTAT)                          | 142 |

| Table 83.  | Flash Page Select Register (FPS)                       | 143 |

| Table 84.  | Flash Sector Protect Register (FPROT)                  | 144 |

| Table 85.  | Flash Frequency High Byte Register (FFREQH)            | 145 |

| Table 86.  | Flash Frequency Low Byte Register (FFREQL)             |     |

| Table 87.  | Trim Bit Address Register (TRMADR)                     | 148 |

| Table 88.  | Trim Bit Data Register (TRMDR)                         | 149 |

| Table 89.  | Flash Option Bits at Program Memory Address 0000H      | 149 |

| Table 90.  | Flash Options Bits at Program Memory Address 0001H     | 150 |

| Table 91.  | Trim Options Bits at Address 0000H                     | 151 |

| Table 92.  | Trim Option Bits at 0001H                              | 152 |

| Table 93.  | Trim Option Bits at 0002H (TIPO)                       | 152 |

| Table 94.  | ADC Calibration Bits                                   | 153 |

| Table 95.  | ADC Calibration Data Location                          | 153 |

| Table 96.  | Serial Number at 001C-001F (S_NUM)                     | 154 |

| Table 97.  | Serialization Data Locations                           | 154 |

| Table 98.  | Lot Identification Number (RAND_LOT)                   | 154 |

| Table 99.  | Randomized Lot ID Locations                            | 155 |

| Table 100. | OCD Baud-Rate Limits                                   | 160 |

| Table 101. | OCD Commands                                           | 162 |

| Table 102. | OCD Control Register (OCDCTL)                          | 167 |

| Table 103. | OCD Status Register (OCDSTAT)                          | 168 |

|            | Oscillator Configuration and Selection                 |     |

| Table 105. | Oscillator Control Register (OSCCTL)                   | 172 |

|            |                                                        |     |

### **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 20- and 28-pin devices. Data in Table 4 is sorted alphabetically by the pin symbol mnemonic.

**Note:** All six I/O pins on the 8-pin packages are 5V-tolerant (unless the pull-up devices are enabled). The right-most column in Table 4 describes 5V tolerance for the 20- and 28-pin packages only.

Table 4. Pin Characteristics (20- and 28-pin Devices)\*

| Symbol<br>Mnemonic | Direction | Reset<br>Direction               | Active<br>Low or<br>Active<br>High | Tristate<br>Output   | Internal<br>Pull-up<br>or Pull-<br>down | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output   | 5V<br>Tolerance |

|--------------------|-----------|----------------------------------|------------------------------------|----------------------|-----------------------------------------|------------------------------|------------------------|-----------------|

| AVDD               | N/A       | N/A                              | N/A                                | N/A                  | N/A                                     | N/A                          | N/A                    | N/A             |

| AVSS               | N/A       | N/A                              | N/A                                | N/A                  | N/A                                     | N/A                          | N/A                    | NA              |

| DBG                | I/O       | ı                                | N/A                                | Yes                  | No                                      | Yes                          | Yes                    | Yes             |

| PA[7:0]            | I/O       | I                                | N/A                                | Yes                  | Program-<br>mable<br>Pull-up            | Yes                          | Yes,<br>Programmable   | PA[7:2] only    |

| PB[7:0]            | I/O       | I                                | N/A                                | Yes                  | Program-<br>mable<br>Pull-up            | Yes                          | Yes,<br>Programmable   | PB[7:6] only    |

| PC[7:0]            | I/O       | I                                | N/A                                | Yes                  | Program-<br>mable<br>Pull-up            | Yes                          | Yes,<br>Programmable   | PC[7:3] only    |

| RESET              | I/O       | I/O<br>(defaults<br>to<br>RESET) | Low (in<br>Reset<br>mode)          | Yes<br>(PD0<br>only) | Always<br>on for<br>RESET               | Yes                          | Always on for<br>RESET | Yes             |

| VDD                | N/A       | N/A                              | N/A                                | N/A                  |                                         |                              | N/A                    | N/A             |

| VSS                | N/A       | N/A                              | N/A                                | N/A                  |                                         |                              | N/A                    | N/A             |

Note: PB6 and PB7 are available only in the devices without ADC.

Table 8. Register File Address Map (Continued)

| Address (Hex)    | Register Description                  | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------------------|----------|-------------|-------------|

| GPIO Port B (co  | nt'd)                                 |          |             |             |

| FD6              | Port B Input Data                     | PBIN     | XX          | <u>43</u>   |

| FD7              | Port B Output Data                    | PBOUT    | 00          | <u>43</u>   |

| GPIO Port C      |                                       |          |             |             |

| FD8              | Port C Address                        | PCADDR   | 00          | <u>40</u>   |

| FD9              | Port C Control                        | PCCTL    | 00          | <u>42</u>   |

| FDA              | Port C Input Data                     | PCIN     | XX          | <u>43</u>   |

| FDB              | Port C Output Data                    | PCOUT    | 00          | <u>43</u>   |

| FDC-FEF          | Reserved                              | _        | XX          |             |

| Watchdog Time    | r (WDT)                               |          |             |             |

| FF0              | Reset Status                          | RSTSTAT  | XX          | <u>94</u>   |

|                  | Watchdog Timer Control                | WDTCTL   | XX          | 94          |

| FF1              | Watchdog Timer Reload Upper Byte      | WDTU     | FF          | <u>95</u>   |

| FF2              | Watchdog Timer Reload High Byte       | WDTH     | FF          | <u>95</u>   |

| FF3              | Watchdog Timer Reload Low Byte        | WDTL     | FF          | <u>95</u>   |

| FF4–FF5          | Reserved                              | _        | XX          |             |

| Trim Bit Control |                                       |          |             |             |

| FF6              | Trim Bit Address                      | TRMADR   | 00          | <u>148</u>  |

| FF7              | Trim Data                             | TRMDR    | XX          | <u>149</u>  |

| Flash Memory C   | Controller                            |          |             |             |

| FF8              | Flash Control                         | FCTL     | 00          | <u>141</u>  |

| FF8              | Flash Status                          | FSTAT    | 00          | <u>142</u>  |

| FF9              | Flash Page Select                     | FPS      | 00          | <u>143</u>  |

|                  | Flash Sector Protect                  | FPROT    | 00          | <u>144</u>  |

| FFA              | Flash Programming Frequency High Byte | FFREQH   | 00          | <u>145</u>  |

| FFB              | Flash Programming Frequency Low Byte  | FFREQL   | 00          | <u>145</u>  |

Note: XX=Undefined.

**Table 17. Port Alternate Function Mapping (Non 8-Pin Parts)**

| Port                | Pin | Mnemonic                | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-------------------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1</sup> | PA0 | T0IN/T0OUT              | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|                     |     | Reserved                |                                         | -                                       |

|                     | PA1 | T0OUT                   | Timer 0 Output                          | _                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA2 | DE0                     | UART 0 Driver Enable                    | _                                       |

|                     |     | Reserved                |                                         | -                                       |

|                     | PA3 | CTS0                    | UART 0 Clear to Send                    | -                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA4 | RXD0/IRRX0              | UART 0 / IrDA 0 Receive Data            | _                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA5 | TXD0/IRTX0              | UART 0 / IrDA 0 Transmit Data           | -                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA6 | T1IN/T1OUT <sup>2</sup> | Timer 1 Input/Timer 1 Output Complement | -                                       |

|                     |     | Reserved                |                                         | -                                       |

|                     | PA7 | T1OUT                   | Timer 1 Output                          |                                         |

|                     |     | Reserved                |                                         | -                                       |

#### Notes:

- 1. Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in the <a href="Port A—C Alternate Function">Port A—C Alternate Function</a> Subregisters section on page 43 automatically enables the associated alternate function.

- 2. Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in the <u>Timer Pin Signal Operation</u> section on page 83.

- 3. Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, alternate function selection as described in the <a href="Port A-C Alternate Function Subregisters">Port A-C Alternate Function Subregisters</a> section on page 43 must also be enabled.

- 4. V<sub>REF</sub> is available on PB5 in 28-pin products only.

- 5. Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in the <a href="Port A-C Alternate Function Subregisters">Port A-C Alternate Function Subregisters</a> section on page 43 must also be enabled.

- 6. V<sub>REF</sub> is available on PC2 in 20-pin parts only.

## **LED Drive Level High Register**

The LED Drive Level registers contain two control bits for each Port C pin (Table 33). These two bits select between four programmable drive levels. Each pin is individually programmable.

Table 33. LED Drive Level High Register (LEDLVLH)

| Bit     | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | LEDLVLH[7:0] |     |     |     |     |     |     |  |

| RESET   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     |              |     | F8  | 3H  |     |     |     |  |

| Bit     | Description                                                                                                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]   | LED Level High Bit                                                                                                                          |

| LEDLVLH | {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.  00 = 3 mA.  01= 7 mA.  10= 13 mA.  11= 20 mA. |

## **Architecture**

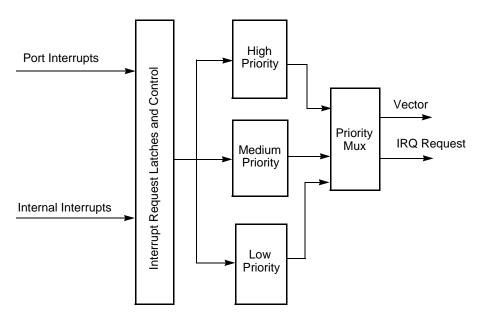

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

## **Operation**

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 56

**Interrupt Vectors and Priority**: see page 57

**Interrupt Assertion**: see page 57

Software Interrupt Assertion: see page 58

Watchdog Timer Interrupt Assertion: see page 58

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

• Execution of an Enable Interrupt (EI) instruction

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TxL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

Table 51. Timer 0–1 High Byte Register (TxH)

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |

|---------|-----|-----|-----|-------|------|-----|-----|-----|--|

| Field   |     | TH  |     |       |      |     |     |     |  |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |  |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |

| Address |     |     |     | F00H, | F08H |     |     |     |  |

Table 52. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |  |

|---------|-----|-----|-----|-------|------|-----|-----|-----|--|--|

| Field   |     | TL  |     |       |      |     |     |     |  |  |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 1   |  |  |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |

| Address |     |     |     | F01H, | F09H |     |     |     |  |  |

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

## **Timer Reload High and Low Byte Registers**

The Timer 0-1 Reload High and Low Byte (TxRH and TxRL) registers (Table 53 and Table 54) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer reload value. In COMPARE Mode, the Timer Reload High and Low Byte registers store the 16-bit compare value.

Watchdog Timer Reload High Byte Register (WDTH): see page 95 Watchdog Timer Reload Low Byte Register (WDTL): see page 95

## **Watchdog Timer Control Register**

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status Register.

Table 60. Watchdog Timer Control Register (WDTCTL)

| Bit     | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---------|---|---|---|---|---|---|---|

| Field   | WDTUNLK |   |   |   |   |   |   |   |

| RESET   | Х       | Х | Х | Х | Х | Х | Х | Х |

| R/W     | W       | W | W | W | W | W | W | W |

| Address | FF0H    |   |   |   |   |   |   |   |

| Bit     | Description                                                                                  |

|---------|----------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Unlock                                                                        |

| WDTUNLK | The software must write the correct unlocking sequence to this register before it is allowed |

|         | to modify the contents of the Watchdog Timer reload registers.                               |

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 61 through 63, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT Reload Value must not be set to a value less than 000004H.

96

| Bit   | Description                                                              |

|-------|--------------------------------------------------------------------------|

| [7:0] | WDT Reload Low                                                           |

| WDTL  | Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value. |

| Bit    | Description                                                                                                                                                                                                                                                                                                                                            |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]  | Reserved                                                                                                                                                                                                                                                                                                                                               |

|        | These bits are reserved and must be programmed to 111 during writes and to 111 when read.                                                                                                                                                                                                                                                              |

| [4]    | State of Crystal Oscillator at Reset                                                                                                                                                                                                                                                                                                                   |

| XTLDIS | This bit only enables the crystal oscillator. Its selection as a system clock must be performed manually.                                                                                                                                                                                                                                              |

|        | 0 = The crystal oscillator is enabled during reset, resulting in longer reset timing.                                                                                                                                                                                                                                                                  |

|        | 1 = The crystal oscillator is disabled during reset, resulting in shorter reset timing.                                                                                                                                                                                                                                                                |

|        | <b>Caution:</b> Programming the XTLDIS bit to zero on 8-pin versions of F0823 Series devices prevents any further communication via the debug pin due to the $X_{\rm IN}$ and DBG functions being shared on pin 2 of the 8-pin package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required. |

| [3:0]  | Reserved                                                                                                                                                                                                                                                                                                                                               |

|        | These bits are reserved and must be programmed to 1111 during writes and to 1111 when read                                                                                                                                                                                                                                                             |

## **Trim Bit Address Space**

All available trim bit addresses and their functions are listed in Tables 91 through 93.

Table 91. Trim Options Bits at Address 0000H

| Bit       | 7                                           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|---------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field     | Reserved                                    |     |     |     |     |     |     |     |

| RESET     | U U U U U U U U                             |     |     |     |     |     |     |     |

| R/W       | R/W                                         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address   | Information Page Memory 0020H               |     |     |     |     |     |     |     |

| Note: U = | : U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |

| Bit   | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                  |

|       | These bits are reserved. Altering this register may result in incorrect device operation. |

164

Read Program Counter (07H). The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG → ProgramCounter[15:8]

DBG → ProgramCounter[7:0]

```

Write Register (08H). The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG ← 08H

DBG \leftarrow \{4'h0, Register Address[11:8]\}

DBG ← Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG ← 1-256 data bytes

```

**Read Register (09H).** The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow \{4'h0, Register Address[11:8]\}

DBG ← Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

Write Program Memory (0AH). The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG ← 0AH

DBG ← Program Memory Address[15:8]

DBG ← Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG ← 1-65536 data bytes

```

Read Program Memory (0BH). The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

180

**Table 113. CPU Control Instructions**

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| ATM      |          | Atomic Execution       |

| CCF      | _        | Complement Carry Flag  |

| DI       | _        | Disable Interrupts     |

| EI       | _        | Enable Interrupts      |

| HALT     | _        | HALT Mode              |

| NOP      | _        | No Operation           |

| RCF      | _        | Reset Carry Flag       |

| SCF      | _        | Set Carry Flag         |

| SRP      | src      | Set Register Pointer   |

| STOP     | _        | STOP Mode              |

| WDT      | _        | Watchdog Timer Refresh |

**Table 114. Load Instructions**

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Pop                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

## Electrical Characteristics

The data in this chapter represents all known data prior to qualification and characterization of the F0823 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 120 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

**Table 120. Absolute Maximum Ratings**

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | -40     | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     | 1     |

|                                                                | -0.3    | +3.9    | V     | 2     |

| Voltage on V <sub>DD</sub> pin with respect to V <sub>SS</sub> | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0°C to 70°C                  |         |         |       |       |

| Total power dissipation                                        |         | 220     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 125     | mA    |       |

Notes: Operating temperature is specified in DC Characteristics.

- This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

- 2. This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

**Table 121. DC Characteristics (Continued)**

|                   |                                       | T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise specified) |                  |         |       |                                                                               |

|-------------------|---------------------------------------|------------------------------------------------------------------|------------------|---------|-------|-------------------------------------------------------------------------------|

| Symbol            | Parameter                             | Minimum                                                          | Typical          | Maximum | Units | Conditions                                                                    |

| I <sub>LED</sub>  | Controlled Current                    | 1.8                                                              | 3                | 4.5     | mA    | $\{AFS2,AFS1\} = \{0,0\}.$                                                    |

|                   | Drive                                 | 2.8                                                              | 7                | 10.5    | mA    | $\{AFS2,AFS1\} = \{0,1\}.$                                                    |

|                   |                                       | 7.8                                                              | 13               | 19.5    | mΑ    | $\{AFS2,AFS1\} = \{1,0\}.$                                                    |

|                   |                                       | 12                                                               | 20               | 30      | mΑ    | {AFS2,AFS1} = {1,1}.                                                          |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance          | _                                                                | 8.0 <sup>2</sup> | _       | pF    |                                                                               |

| C <sub>XIN</sub>  | X <sub>IN</sub> Pad Capaci-<br>tance  | _                                                                | 8.0 <sup>2</sup> | -       | pF    |                                                                               |

| C <sub>XOUT</sub> | X <sub>OUT</sub> Pad Capaci-<br>tance | _                                                                | 9.5 <sup>2</sup> | -       | pF    |                                                                               |

| I <sub>PU</sub>   | Weak Pull-up Cur-<br>rent             | 30                                                               | 100              | 350     | μΑ    | V <sub>DD</sub> = 3.0V–3.6V.                                                  |

| V <sub>RAM</sub>  | RAM Data Retention Voltage            | TBD                                                              |                  |         | V     | Voltage at which RAM retains static values; no reading or writing is allowed. |

#### Notes:

- 1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

- 2. These values are provided for design guidance only and are not tested in production.

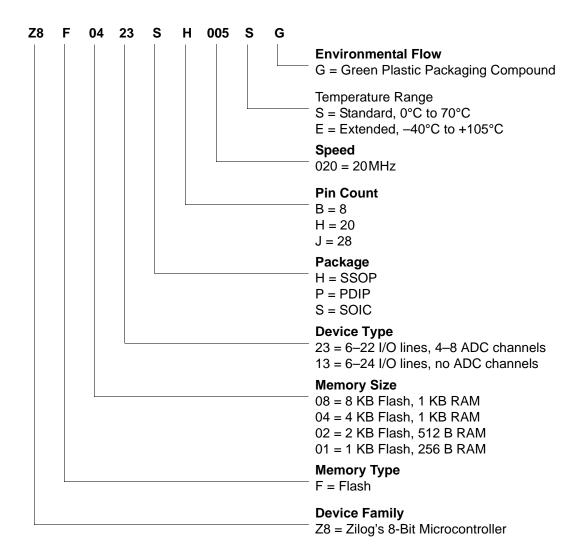

## **Part Number Suffix Designations**

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0423SH005SG is an 8-bit 20MHz Flash MCU with 4KB of Program Memory and equipped with 6–22 I/O lines and 4–8 ADC channels in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

| LDEI 179, 180                                     | N                                   |

|---------------------------------------------------|-------------------------------------|

| LDX 180                                           | NOP (no operation) 180              |

| LEA 180                                           | notation                            |

| load 180                                          | b 176                               |

| load constant 179                                 | cc 176                              |

| load constant to/from program memory 180          | DA 176                              |

| load constant with auto-increment addresses 180   | ER 176                              |

| load effective address 180                        | IM 176                              |

| load external data 180                            | IR 176                              |

| load external data to/from data memory and auto-  | Ir 176                              |

| increment addresses 179                           | IRR 176                             |

| load external to/from data memory and auto-incre- | Irr 176                             |

| ment addresses 180                                | p 176                               |

| load instructions 180                             | R 176                               |

| load using extended addressing 180                | r 176                               |

| logical AND 181                                   | RA 177                              |

| logical AND/extended addressing 181               | RR 177                              |

| logical exclusive OR 181                          | rr 177                              |

| logical exclusive OR/extended addressing 181      | vector 177                          |

| logical instructions 181                          | X 177                               |

| logical OR 181                                    | notational shorthand 176            |

| logical OR/extended addressing 181                | notational shorthand 170            |

| low power modes 30                                |                                     |

|                                                   | 0                                   |

|                                                   | OCD                                 |

| M                                                 | architecture 156                    |

| master interrupt enable 56                        | auto-baud detector/generator 159    |

| memory                                            | baud rate limits 160                |

| data 15                                           | block diagram 156                   |

| program 13                                        | breakpoints 161                     |

| mode                                              | commands 162                        |

| CAPTURE 89                                        | control register 166                |

| CAPTURE/COMPARE 89                                | data format 159                     |

| CONTINUOUS 88                                     | DBG pin to RS-232 Interface 157     |

| COUNTER 89                                        | DEBUG mode 158                      |

| GATED 89                                          | debugger break 181                  |

| ONE-SHOT 88                                       | interface 157                       |

| PWM 89                                            | serial errors 160                   |

| modes 89                                          | status register 168                 |

| MULT 179                                          | timing 207                          |

| multiply 179                                      | OCD commands                        |

| MULTIPROCESSOR mode, UART 103                     | execute instruction (12H) 166       |

| ,                                                 | read data memory (0DH) 165          |

|                                                   | • • •                               |

|                                                   | read OCD control register (05H) 163 |