Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223sj005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

nbedded in Life

13

## Address Space

The eZ8 CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O Port Control Registers

- The Program Memory contains addresses for all memory locations having executable code and/or data

- The Data Memory contains addresses for all memory locations that contain data only

These three address spaces are covered briefly in the following subsections. For more detailed information regarding the eZ8 CPU and its address space, refer to the <u>eZ8 CPU</u> <u>Core User Manual (UM0128)</u>, available for download at <u>www.zilog.com</u>.

## **Register File**

The Register File address space in the Z8 Encore! XP<sup>™</sup> MCU is 4KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. Z8 Encore! XP F0823 Series devices contain 256B–1KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

## **Program Memory**

The eZ8 CPU supports 64KB of Program Memory address space. F0823 Series devices contain 1KB to 8KB of on-chip Flash memory in the Program Memory address space. Reading from Program Memory addresses outside the available Flash memory addresses

returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the Z8 Encore! XP F0823 Series products.

| Program Memory Address (Hex) | Function                 |

|------------------------------|--------------------------|

| Z8F0823 and Z8F0813 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0423 and Z8F0413 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0223 and Z8F0213 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-07FF                    | Program Memory           |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps

Note: \*See the <u>Trap and Interrupt Vectors in Order of Priority section on page 55</u> for a list of the interrupt vectors and traps.

Embedded in Life An IXYS Company

ilog<sup>®</sup> Embedded in Life

ilog Embedded in Life An IXYS Company 17

| Address (Hex)    | Register Description      | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------|----------|-------------|-------------|

| Timer 1 (cont'd) |                           |          |             |             |

| F0A              | Timer 1 Reload High Byte  | T1RH     | FF          | <u>85</u>   |

| F0B              | Timer 1 Reload Low Byte   | T1RL     | FF          | <u>85</u>   |

| F0C              | Timer 1 PWM High Byte     | T1PWMH   | 00          | <u>86</u>   |

| F0D              | Timer 1 PWM Low Byte      | T1PWML   | 00          | <u>86</u>   |

| F0E              | Timer 1 Control 0         | T1CTL0   | 00          | <u>87</u>   |

| F0F              | Timer 1 Control 1         | T1CTL1   | 00          | <u>84</u>   |

| F10–F3F          | Reserved                  | —        | XX          |             |

| UART             |                           |          |             |             |

| F40              | UART0 Transmit Data       | U0TXD    | XX          | <u>109</u>  |

|                  | UART0 Receive Data        | U0RXD    | XX          | <u>109</u>  |

| F41              | UART0 Status 0            | U0STAT0  | 0000011Xb   | <u>110</u>  |

| F42              | UART0 Control 0           | U0CTL0   | 00          | <u>112</u>  |

| F43              | UART0 Control 1           | U0CTL1   | 00          | <u>112</u>  |

| F44              | UART0 Status 1            | U0STAT1  | 00          | <u>111</u>  |

| F45              | UART0 Address Compare     | U0ADDR   | 00          | <u>115</u>  |

| F46              | UART0 Baud Rate High Byte | U0BRH    | FF          | <u>115</u>  |

| F47              | UART0 Baud Rate Low Byte  | U0BRL    | FF          | <u>115</u>  |

| F48–F6F          | Reserved                  | —        | XX          |             |

| Analog-to-Digita | al Converter (ADC)        |          |             |             |

| F70              | ADC Control 0             | ADCCTL0  | 00          | <u>127</u>  |

| F71              | ADC Control 1             | ADCCTL1  | 80          | <u>127</u>  |

| F72              | ADC Data High Byte        | ADCD_H   | XX          | <u>130</u>  |

| F73              | ADC Data Low Bits         | ADCD_L   | XX          | <u>130</u>  |

| F74–F7F          | Reserved                  | —        | XX          |             |

| Low Power Con    | trol                      |          |             |             |

| F80              | Power Control 0           | PWRCTL0  | 80          | <u>32</u>   |

| F81              | Reserved                  | _        | XX          |             |

| LED Controller   |                           |          |             |             |

| F82              | LED Drive Enable          | LEDEN    | 00          | <u>51</u>   |

| F83              | LED Drive Level High Byte | LEDLVLH  | 00          | <u>52</u>   |

| Note: XX=Undefi  |                           |          |             |             |

#### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

#### ilog Embedded in Life An IXYS Company 45

#### Port A–C High Drive Enable Subregisters

The Port A–C High Drive Enable Subregister (Table 25) is accessed through the Port A–C Control Register by writing 04H to the Port A–C Address Register. Setting the bits in the Port A–C High Drive Enable subregisters to 1 configures the specified port pins for high-current output drive operation. The Port A–C High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

| Table 25. Port A–C High Drive Enable Subregiste | ers (PHDEx) |

|-------------------------------------------------|-------------|

|-------------------------------------------------|-------------|

| Bit     | 7                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| Field   | PHDE7                                                                                 | PHDE6 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |  |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address | If 04H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |       |  |

#### Bit Description

[7:0] **Port High Drive Enabled.**

PHDEx 0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

Note: x indicates the specific GPIO port pin number (7–0).

## Embedded in Life

## **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) register (Table 49) determines the source of the PADxS interrupts. The Shared Interrupt Select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit     | 7        | 6     | 5        | 4   | 3   | 2   | 1   | 0   |

|---------|----------|-------|----------|-----|-----|-----|-----|-----|

| Field   | Reserved | PA6CS | Reserved |     |     |     |     |     |

| RESET   | 0        | 0     | 0        | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W      | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |

| Address |          | FCEH  |          |     |     |     |     |     |

#### Table 49. Shared Interrupt Select Register (IRQSS)

| Bit          | Description                                                                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]          | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                   |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The comparator is used as an interrupt for PA6CS interrupt requests.</li> </ul> |

| [5:0]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                           |

Observe the following steps to configure a timer for PWM DUAL OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode. Setting the mode also involves writing to the TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H); this write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) =  $\frac{\text{Reload Value } \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

#### WDT Reset in NORMAL Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Watchdog Timer Control Register is set to 1. For more information about System Reset, see **the** <u>Reset and Stop</u> <u>Mode Recovery</u> chapter on page 21.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following WDT time-out in STOP Mode. For more information, see **the** <u>Reset and Stop Mode Recovery</u> chapter on page 21.

### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer Control Register (WDTCTL) address unlocks the three Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. The following sequence is required to unlock the Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register (WDTCTL): see page 94

Watchdog Timer Reload Upper Byte Register (WDTU): see page 95

## Operation

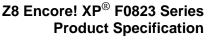

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

#### ilog<sup>°</sup> Embedded in Life An TIXYS Company

111

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | <ul> <li>Transmitter Data Register Empty</li> <li>This bit indicates that the UART Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the UART Transmit Data Register resets this bit.</li> <li>0 = Do not write to the UART Transmit Data Register.</li> <li>1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted.</li> </ul> |

| [1]<br>TXE  | <b>Transmitter Empty</b><br>This bit indicates that the transmit shift register is empty and character transmission is finished.<br>0 = Data is currently transmitting.<br>1 = Transmission is complete.                                                                                                                                                                                               |

| [0]<br>CTS  | <b>CTS</b> Signal When this bit is read, it returns the level of the $\overline{\text{CTS}}$ signal. This signal is active Low.                                                                                                                                                                                                                                                                        |

## **UART Status 1 Register**

This register contains multiprocessor control and status bits.

| Table 67. UART Stat | us 1 Register (U0STAT1) |

|---------------------|-------------------------|

|---------------------|-------------------------|

| Bit     | 7 | 6    | 5    | 4     | 3   | 2   | 1      | 0    |

|---------|---|------|------|-------|-----|-----|--------|------|

| Field   |   |      | Rese | erved |     |     | NEWFRM | MPRX |

| RESET   | 0 | 0    | 0    | 0     | 0   | 0   | 0      | 0    |

| R/W     | R | R    | R    | R     | R/W | R/W | R      | R    |

| Address |   | F44H |      |       |     |     |        |      |

| Bit           | Description                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | <b>Reserved</b><br>These bits are reserved; R/W bits must be programmed to 000000 during writes and 000000 when read.                                                                                                                                                                             |

| [1]<br>NEWFRM | <ul> <li>New Frame</li> <li>A status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.</li> <li>0 = The current byte is not the first data byte of a new frame.</li> <li>1 = The current byte is the first data byte of a new frame.</li> </ul> |

| [0]<br>MPRX   | Multiprocessor Receive<br>Returns the value of the most recent multiprocessor bit received. Reading from the UART<br>Receive Data Register resets this bit to 0.                                                                                                                                  |

#### ilog Embedded in Life An∎IXYS Company 115

## **UART Address Compare Register**

The UART Address Compare Register stores the multinode network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

| Bit     | 7   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----------|-----|-----|-----|-----|-----|-----|

| Field   |     | COMP_ADDR |     |     |     |     |     |     |

| RESET   | 0   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F45H      |     |     |     |     |     |     |

| Table 70. UART Address Compare Register (U0ADDR | Table 70. UART Address Com | npare Register (U0ADDR) |

|-------------------------------------------------|----------------------------|-------------------------|

|-------------------------------------------------|----------------------------|-------------------------|

| Bit       | Description                                             |

|-----------|---------------------------------------------------------|

| [7:0]     | Compare Address                                         |

| COMP_ADDR | This 8-bit value is compared to incoming address bytes. |

## **UART Baud Rate High and Low Byte Registers**

The UART Baud Rate High and Low Byte registers (Table 71 and Table 72) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | BRH |     |     |     |     |     |     |  |  |  |

| RESET   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |  |  |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     |     |     | F4  | 6H  |     |     |     |  |  |  |

Table 71. UART Baud Rate High Byte Register (U0BRH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | BRL  |     |     |     |     |     |     |  |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | F47H |     |     |     |     |     |     |  |  |

Embedded in Life An IXYS Company 139

bits can only be set to 1. Thus, sectors can be protected, but not unprotected, via register write operations. Writing a value other than 5EH to the Flash Control Register deselects the Flash Sector Protect Register and reenables access to the Page Select Register.

Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control Register to return the Flash Controller to its reset state.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased by the CPU. External Flash programming through the OCD or via the Flash Controller Bypass mode are unaffected. After a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

## **Byte Programming**

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully enabled, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming is accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. For a description of the LDC and LDCI instructions, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, available for download at <u>www.zilog.com</u>. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control Register, except the Mass Erase or Page Erase commands.

# **Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

> ilog Embedded in Life An IXYS Company 152

#### Table 92. Trim Option Bits at 0001H

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| Field     | Reserved                                        |     |     |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Information Page Memory 0021H                   |     |     |     |     |     |     |     |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |

| Bit   | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                  |

|       | These bits are reserved. Altering this register may result in incorrect device operation. |

#### Table 93. Trim Option Bits at 0002H (TIPO)

| Bit       | 7                                               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------|-------------------------------------------------|---|---|---|---|---|---|---|--|--|--|

| Field     | IPO_TRIM                                        |   |   |   |   |   |   |   |  |  |  |

| RESET     | U                                               |   |   |   |   |   |   |   |  |  |  |

| R/W       | R/W                                             |   |   |   |   |   |   |   |  |  |  |

| Address   | Information Page Memory 0022H                   |   |   |   |   |   |   |   |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |   |   |   |   |   |   |   |  |  |  |

| Bit      | Description                                                   |

|----------|---------------------------------------------------------------|

| [7:0]    | Internal Precision Oscillator Trim Byte                       |

| IPO_TRIM | Contains trimming bits for the Internal Precision Oscillator. |

## **Zilog Calibration Data**

This section briefly describes the features of the following Flash Option Bit calibration registers.

ADC Calibration Data: see page 153

Serialization Data: see page 154

Randomized Lot Identifier: see page 154

If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/ DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled high. At this point, the PA0/DBG pin can be used to autobaud and cause the device to enter DEBUG Mode. For more details, see the OCD Unlock Sequence (8-Pin Devices Only) section on page 161.

#### Exiting DEBUG Mode

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

- Watchdog Timer reset

- Asserting the **RESET** pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a system reset

### OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 Stop bit as displayed in Figure 25.

|  | START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |  |

|--|-------|----|----|----|----|----|----|----|----|------|--|

|--|-------|----|----|----|----|----|----|----|----|------|--|

Figure 25. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. Zilog recommends that, if possible, the host drives the DBG pin using an open-drain output.

## **OCD** Autobaud Detector/Generator

To run over a range of baud rates (data bits per second) with various system clock frequencies, the OCD contains an auto-baud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data

## Embedded in Life An IXYS Company

## **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

| Table 103. OCD Status | Register (OCDSTAT) |

|-----------------------|--------------------|

|-----------------------|--------------------|

| Bit   | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |

|-------|-----|------|--------|----------|---|---|---|---|--|

| Field | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |

|       |     |      | I      |          |   | I |   |   |  |

| Bit           | Description                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBG    | Debug Status<br>0 = NORMAL Mode.<br>1 = DEBUG Mode.                                                                                |

| [6]<br>HALT   | HALT Mode<br>0 = Not in HALT Mode.<br>1 = In HALT Mode.                                                                            |

| [5]<br>FRPENB | Flash Read Protect Option Bit Enable<br>0 = FRP bit enabled to allow disabling of many OCD commands.<br>1 = FRP bit has no effect. |

| [4:0]         | Reserved<br>These bits are reserved and must be 00000 when read.                                                                   |

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                       |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data<br>; value 01H, is the source. The value 01H is written into the<br>; Register at address 234H. |

## **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

#### Example 1

If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 106.

#### Table 106. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

#### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 107.

Embedded in Life

ilog

| Mnemonic                           | Operands | Instruction            |  |  |

|------------------------------------|----------|------------------------|--|--|

| RR                                 | dst      | Rotate Right           |  |  |

| RRC dst Rotate Right through Carry |          |                        |  |  |

| SRA                                | dst      | Shift Right Arithmetic |  |  |

| SRL                                | dst      | Shift Right Logical    |  |  |

| SWAP                               | dst      | Swap Nibbles           |  |  |

#### Table 117. Rotate and Shift Instructions (Continued)

## eZ8 CPU Instruction Summary

Table 118 summarizes the eZ8 CPU instruction set. The table identifies the addressing modes employed by the instruction, the effect upon the Flags Register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly      |                           | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   | _ Fetch | Instr. |   |

|---------------|---------------------------|-----------------|-----|-------------|-------|---|---|---|---|---------|--------|---|

| Mnemonic      | Symbolic Operation        | dst             | src | (Hex)       | С     | Ζ | S | ۷ | D | Н       | Cycles |   |

| ADC dst, src  | $dst \gets dst + src + C$ | r               | r   | 12          | *     | * | * | * | 0 | *       | 2      | 3 |

|               |                           | r               | lr  | 13          |       |   |   |   |   |         | 2      | 4 |

|               |                           | R               | R   | 14          |       |   |   |   |   |         | 3      | 3 |

|               |                           | R               | IR  | 15          |       |   |   |   |   |         | 3      | 4 |

|               |                           | R               | IM  | 16          |       |   |   |   |   |         | 3      | 3 |

|               |                           | IR              | IM  | 17          |       |   |   |   |   |         | 3      | 4 |

| ADCX dst, src | $dst \gets dst + src + C$ | ER              | ER  | 18          | *     | * | * | * | 0 | *       | 4      | 3 |

|               |                           | ER              | IM  | 19          |       |   |   |   |   |         | 4      | 3 |

#### Table 118. eZ8 CPU Instruction Summary

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

ilog° Embedded in Life An∎IXYS Company

186

| Assembly      |                          | Add<br>Mc |      | _ Opcode(s) |   | Flags |   |   |   | _ Fetch | Instr. |        |

|---------------|--------------------------|-----------|------|-------------|---|-------|---|---|---|---------|--------|--------|

| Mnemonic      | Symbolic Operation       | dst       | src  | (Hex)       | С | Ζ     | S | ۷ | D | Н       |        | Cycles |

| LD dst, rc    | $dst \leftarrow src$     | r         | IM   | 0C-FC       | - | _     | - | - | - | _       | 2      | 2      |

|               |                          | r         | X(r) | C7          | - |       |   |   |   |         | 3      | 3      |

|               |                          | X(r)      | r    | D7          | - |       |   |   |   |         | 3      | 4      |

|               |                          | r         | lr   | E3          | - |       |   |   |   |         | 2      | 3      |

|               |                          | R         | R    | E4          | - |       |   |   |   |         | 3      | 2      |

|               |                          | R         | IR   | E5          | - |       |   |   |   |         | 3      | 4      |

|               |                          | R         | IM   | E6          | - |       |   |   |   |         | 3      | 2      |

|               |                          | IR        | IM   | E7          | - |       |   |   |   |         | 3      | 3      |

|               |                          | lr        | r    | F3          | - |       |   |   |   |         | 2      | 3      |

|               |                          | IR        | R    | F5          | - |       |   |   |   |         | 3      | 3      |

| LDC dst, src  | $dst \gets src$          | r         | Irr  | C2          | - | _     | _ | - | _ | -       | 2      | 5      |

|               |                          | lr        | Irr  | C5          | - |       |   |   |   |         | 2      | 9      |

|               |                          | Irr       | r    | D2          | - |       |   |   |   |         | 2      | 5      |

| LDCI dst, src | $dst \gets src$          | lr        | Irr  | C3          | - | _     | _ | _ | - | -       | 2      | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr       | lr   | D3          | - |       |   |   |   |         | 2      | 9      |

| LDE dst, src  | $dst \leftarrow src$     | r         | Irr  | 82          | - | _     | _ | - | - | -       | 2      | 5      |

|               |                          | Irr       | r    | 92          | - |       |   |   |   |         | 2      | 5      |

| LDEI dst, src | dst $\leftarrow$ src     | lr        | Irr  | 83          | _ | _     | _ | - | - | _       | 2      | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr       | lr   | 93          | - |       |   |   |   |         | 2      | 9      |

| LDWX dst, src | dst $\leftarrow$ src     | ER        | ER   | 1FE8        | _ | _     | _ | _ | _ | _       | 5      | 4      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

#### ilog<sup>°</sup> Embedded in Life An IXYS Company 206

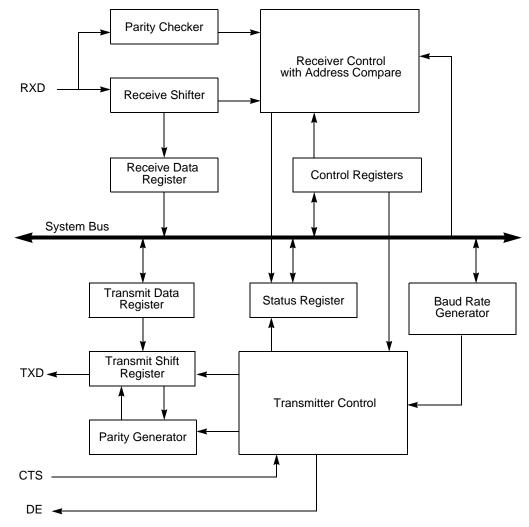

## General Purpose I/O Port Output Timing

Figure 30 and Table 131 provide timing information for GPIO Port pins.

|                |                                                 | Delay (ns) |         |  |  |

|----------------|-------------------------------------------------|------------|---------|--|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |  |

| GPIO Port p    | bins                                            |            |         |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _          | 15      |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |  |  |

#### Table 131. GPIO Port Output Timing

209

0g

■IXYS Company

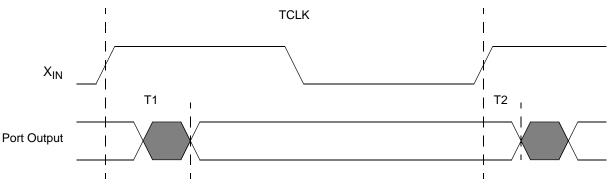

Figure 33 and Table 134 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

|                |                                                                        | Delay (ns)                 |            |  |  |  |  |

|----------------|------------------------------------------------------------------------|----------------------------|------------|--|--|--|--|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |  |  |  |  |

| UART           |                                                                        |                            |            |  |  |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |  |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5                        |            |  |  |  |  |

UARTx control 1 (UxCTL1) 113 UARTx receive data (UxRXD) 109 UARTx status 0 (UxSTAT0) 110 UARTx status 1 (UxSTAT1) 111 UARTx transmit data (UxTXD) 109 Watchdog Timer control (WDTCTL) 94, 133 watch-dog timer control (WDTCTL) 172 Watchdog Timer reload high byte (WDTH) 95 Watchdog Timer reload low byte (WDTL) 95 Watchdog Timer reload upper byte (WDTU) 95 register file 13 register pair 177 register pointer 177 reset and stop mode characteristics 21 and stop mode recovery 21 carry flag 179 sources 23 **RET 181** return 181 RL 181 **RLC 181** rotate and shift instructions 181 rotate left 181 rotate left through carry 181 rotate right 182 rotate right through carry 182 RP 177 RR 177, 182 rr 177 **RRC 182**

## S

SBC 179 SCF 179, 180 second opcode map after 1FH 195 set carry flag 179, 180 set register pointer 180 shift right arithmetic 182 shift right logical 182 signal descriptions 9 single-sho conversion (ADC) 123 software trap 181 source operand 177 SP 177 **SRA 182** src 177 **SRL 182 SRP 180** stack pointer 177 **STOP 180** STOP mode 30, 180 Stop Mode Recovery sources 26 using a GPIO port pin transition 27, 28 using Watchdog Timer time-out 27 **SUB 179** subtract 179 subtract - extended addressing 179 subtract with carry 179 subtract with carry - extended addressing 179 **SUBX 179 SWAP 182** swap nibbles 182 symbols, additional 177

## Т

**TCM 179 TCMX 179** test complement under mask 179 test complement under mask - extended addressing 179 test under mask 179 test under mask - extended addressing 179 timer signals 9 timers 69 architecture 70 block diagram 70 CAPTURE mode 78, 79, 89 CAPTURE/COMPARE mode 82, 89 COMPARE mode 80, 89 CONTINUOUS mode 71, 88 COUNTER mode 72, 73 **COUNTER modes 89** GATED mode 81, 89