# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413hh005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 30. | GPIO Port Output Timing | 206 |

|------------|-------------------------|-----|

| Figure 31. | On-Chip Debugger Timing | 207 |

| Figure 32. | UART Timing With CTS    | 208 |

| Figure 33. | UART Timing Without CTS | 209 |

### ilog<sup>°</sup> Embedded in Life An ∎IXYS Company

5

## **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

# **10-Bit Analog-to-Digital Converter**

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

### **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

# **Reset Controller**

Z8 Encore!  $XP^{\text{(B)}}$  F0823 Series products can be reset using the RESET pin, POR, WDT time-out, STOP Mode exit, or Voltage Brown-Out warning signal. The RESET pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

#### ilog Embedded in Life An 🛙 IXYS Company

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 8-pin devices.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                         | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up<br>or Pull-<br>down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                    |

|--------------------|-----------|----------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if<br>key<br>sequence<br>detected) | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O<br>(defaults<br><u>to</u><br>RESET)                                    | N/A                                   | Yes                | Program-<br>mable for<br>PA2;<br>always<br>on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

| VSS                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

### Table 5. Pin Characteristics (8-Pin Devices)

returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the Z8 Encore! XP F0823 Series products.

| Program Memory Address (Hex) | Function                 |

|------------------------------|--------------------------|

| Z8F0823 and Z8F0813 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0423 and Z8F0413 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0223 and Z8F0213 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-07FF                    | Program Memory           |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps

Note: \*See the <u>Trap and Interrupt Vectors in Order of Priority section on page 55</u> for a list of the interrupt vectors and traps.

Embedded in Life An IXYS Company

ilog<sup>®</sup> Embedded in Life

ilog° Embedded in Life An∎IXYS Company 18

| Address (Hex)    | Register Description     | Mnemonic       | Reset (Hex) | Page<br>No. |

|------------------|--------------------------|----------------|-------------|-------------|

| LED Controller   | (cont'd)                 |                |             |             |

| F84              | LED Drive Level Low Byte | LEDLVLL        | 00          | <u>53</u>   |

| F85              | Reserved                 | —              | XX          |             |

| Oscillator Conti | rol                      |                |             |             |

| F86              | Oscillator Control       | OSCCTL         | A0          | <u>172</u>  |

| F87–F8F          | Reserved                 | —              | XX          |             |

| Comparator 0     |                          |                |             |             |

| F90              | Comparator 0 Control     | CMP0           | 14          | <u>133</u>  |

| F91–FBF          | Reserved                 | _              | XX          |             |

| Interrupt Contro | oller                    |                |             |             |

| FC0              | Interrupt Request 0      | IRQ0           | 00          | <u>59</u>   |

| FC1              | IRQ0 Enable High Bit     | IRQ0ENH        | 00          | <u>62</u>   |

| FC2              | IRQ0 Enable Low Bit      | <b>IRQ0ENL</b> | 00          | <u>62</u>   |

| FC3              | Interrupt Request 1      | IRQ1           | 00          | <u>60</u>   |

| FC4              | IRQ1 Enable High Bit     | IRQ1ENH        | 00          | <u>64</u>   |

| FC5              | IRQ1 Enable Low Bit      | IRQ1ENL        | 00          | <u>64</u>   |

| FC6              | Interrupt Request 2      | IRQ2           | 00          | <u>61</u>   |

| FC7              | IRQ2 Enable High Bit     | IRQ2ENH        | 00          | <u>65</u>   |

| FC8              | IRQ2 Enable Low Bit      | IRQ2ENL        | 00          | <u>66</u>   |

| FC9–FCC          | Reserved                 | —              | XX          |             |

| FCD              | Interrupt Edge Select    | IRQES          | 00          | <u>67</u>   |

| FCE              | Shared Interrupt Select  | IRQSS          | 00          | <u>67</u>   |

| FCF              | Interrupt Control        | IRQCTL         | 00          | <u>68</u>   |

| GPIO Port A      |                          |                |             |             |

| FD0              | Port A Address           | PAADDR         | 00          | <u>40</u>   |

| FD1              | Port A Control           | PACTL          | 00          | <u>42</u>   |

| FD2              | Port A Input Data        | PAIN           | XX          | <u>43</u>   |

| FD3              | Port A Output Data       | PAOUT          | 00          | <u>43</u>   |

| GPIO Port B      |                          |                |             |             |

| FD4              | Port B Address           | PBADDR         | 00          | <u>40</u>   |

| FD5              | Port B Control           | PBCTL          | 00          | <u>42</u>   |

### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

# Embedded in Life

23

# **Reset Sources**

Table 10 lists the possible sources of a System Reset.

| Operating Mode       | Reset Source                                       | Special Conditions                                                                                                                 |

|----------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-<br>Out.              | Reset delay begins after supply voltage exceeds POR level.                                                                         |

|                      | Watchdog Timer time-out when configured for Reset. | None.                                                                                                                              |

|                      | RESET pin assertion.                               | All reset pulses less than three system clocks in width are ignored.                                                               |

|                      | OCD initiated Reset (OCDCTL[0] set to 1).          | System Reset, except the OCD is unaffected by the reset.                                                                           |

| STOP Mode            | Power-On Reset/Voltage Brown-<br>Out.              | Reset delay begins after supply voltage exceeds POR level.                                                                         |

|                      | RESET pin assertion.                               | All reset pulses less than the specified analog delay are ignored. See the <u>Electrical Characteris</u> tics chapter on page 196. |

|                      | DBG pin driven Low.                                | None.                                                                                                                              |

### Table 10. Reset Sources and Resulting Reset Type

### **Power-On Reset**

Each device in the Z8 Encore! XP F0823 Series contains an internal POR circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F0823 Series device exits the POR state, the eZ8 CPU fetches the Reset vector. Following the POR, the POR status bit in Watchdog Timer Control (WDTCTL) Register is set to 1.

Figure 5 displays POR operation. For the POR threshold voltage ( $V_{POR}$ ), see the <u>Electrical Characteristics</u> chapter on page 196.

# nbedded in Life

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The WDT is a retriggerable one-shot timer that resets or interrupts F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 59 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10kHz typical WDT oscillator frequency) |                        |  |  |  |

|------------------|------------------|-----------------------------------------------------------------------------|------------------------|--|--|--|

| (Hex) (Decimal)  |                  | Typical                                                                     | Description            |  |  |  |

| 000004           | 4                | 400 μs                                                                      | Minimum time-out delay |  |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                                  | Maximum time-out delay |  |  |  |

### Table 59. Watchdog Timer Approximate Time-Out Delays

ilog<sup>°</sup> Embedded in Life An∎IXYS Company 95

### Table 61. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit                                                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|--|

| Field                                                                                         |      | WDTU |      |      |      |      |      |      |  |

| RESET                                                                                         | 00H  |      |      |      |      |      |      |      |  |

| R/W                                                                                           | R/W* |  |

| Address                                                                                       | FF1H |      |      |      |      |      |      |      |  |

| Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |      |  |

|                                                                                               |      |      |      |      |      |      |      |      |  |

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

### Table 62. Watchdog Timer Reload High Byte Register (WDTH)

| Bit                                                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Field                                                                                         | WDTH |      |      |      |      |      |      |      |

| RESET                                                                                         |      | 04H  |      |      |      |      |      |      |

| R/W                                                                                           | R/W* |

| Address                                                                                       | FF2H |      |      |      |      |      |      |      |

| Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |      |

| Bit   | Description                                              |

|-------|----------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                     |

| WDTH  | Middle byte, Bits[15:8], of the 24-bit WDT reload value. |

### Table 63. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit       | 7                                                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|

| Field     | WDTL                                                                                          |      |      |      |      |      |      |      |  |

| RESET     | 00H                                                                                           |      |      |      |      |      |      |      |  |

| R/W       | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |

| Address   | FF3H                                                                                          |      |      |      |      |      |      |      |  |

| Note: R/W | Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |  |

# Embedded in Life An IXYS Company 97

# Universal Asynchronous Receiver/ Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. The features of UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) Mode with three configurable interrupt schemes

- BRG can be configured and used as a basic 16-bit timer

- Driver Enable output for external bus transceivers

# Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

#### ILOG Embedded in Life IXYS Company 104

scheme is enabled, the UART Address Compare register holds the network address of the device.

### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR Mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes

- Interrupt on matched address bytes and correctly framed data bytes

- Interrupt only on correctly framed data bytes

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare register. This mode introduces additional hard-ware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second

### **Baud Rate Generator Interrupts**

If the Baud Rate Generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Observe the following steps to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) × BRG[15:0]

# **UART Control Register Definitions**

The UART control registers support the UART and the associated infrared encoder/decoders. For more information about the infrared operation, see the <u>Infrared Encoder/Decoder</u> chapter on page 117.

116

dded in Life

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 73 provides information about data rate errors for a 5.5296MHz System Clock.

|                          | 5.5296MHz S              | ystem Clock          |           |  |  |

|--------------------------|--------------------------|----------------------|-----------|--|--|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |  |  |

| 1250.0                   | N/A                      | N/A                  | N/A       |  |  |

| 625.0                    | N/A                      | N/A                  | N/A       |  |  |

| 250.0                    | 1                        | 345.6                | 38.24     |  |  |

| 115.2                    | 3                        | 115.2                | 0.00      |  |  |

| 57.6                     | 6                        | 57.6                 | 0.00      |  |  |

| 38.4                     | 9                        | 38.4                 | 0.00      |  |  |

| 19.2                     | 18                       | 19.2                 | 0.00      |  |  |

| 9.60                     | 36                       | 9.60                 | 0.00      |  |  |

| 4.80                     | 72                       | 4.80                 | 0.00      |  |  |

| 2.40                     | 144                      | 2.40                 | 0.00      |  |  |

| 1.20                     | 288                      | 1.20                 | 0.00      |  |  |

| 0.60                     | 576                      | 0.60                 | 0.00      |  |  |

| 0.30                     | 1152                     | 0.30                 | 0.00      |  |  |

### Table 73. UART Baud Rates

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

Figure 21 displays a basic Flash Controller flow. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

> ILO <u>G</u> Embedded in Life An **D**IXYS Company 142

| Bit     | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|---|---|----|----|---|---|---|

| Field   |   |   |   | FC | MD |   |   |   |

| RESET   | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W     | W | W | W | W  | W  | W | W | W |

| Address |   |   |   | FF | 8H |   |   |   |

### Table 81. Flash Control Register (FCTL)

Bit

Description

[7:0]

Flash Command

FCMD

73H = First unlock command.

8CH = Second unlock command.

95H = Page Erase command (must be third command in sequence to initiate Page Erase).

63H = Mass Erase command (must be third command in sequence to initiate Mass Erase).

5EH = Enable Flash Sector Protect Register Access.

### ilog<sup>\*</sup> Embedded in Life An IXYS Company 157

# Operation

The following section describes the operation of the OCD.

# **OCD** Interface

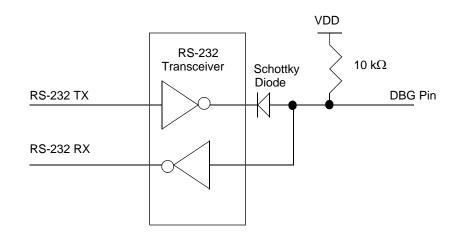

The OCD uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface from the F0823 Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 23 and Figure 24. The recommended method is the buffered implementation depicted in Figure 24. The DBG pin has a internal pull-up resistor which is sufficient for some applications (for more details about the pullup current, see the <u>Electrical Characteristics</u> chapter on page 196). For OCD operation at higher data rates or in noisy systems, Zilog recommends an external pull-up resistor.

**Caution:** For operation of the OCD, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power, and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is opendrain and may require an external pull-up resistor to ensure proper operation.

ilog Embedded in Life An IXYS Company 172

### Table 105. Oscillator Control Register (OSCCTL)

| Bit             | 7                                                                                                                                                                                       | 6                                             | 5          | 4            | 3     | 2   | 1      | 0   |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------|--------------|-------|-----|--------|-----|--|--|

| Field           | INTEN                                                                                                                                                                                   | Reserved                                      | WDTEN      | POFEN        | WDFEN |     | SCKSEL |     |  |  |

| RESET           | 1                                                                                                                                                                                       | 0                                             | 1          | 0            | 0     | 0   | 0      | 0   |  |  |

| R/W             | R/W                                                                                                                                                                                     | R/W                                           | R/W        | R/W          | R/W   | R/W | R/W    | R/W |  |  |

| Address         | F86H                                                                                                                                                                                    |                                               |            |              |       |     |        |     |  |  |

| Bit             | Description                                                                                                                                                                             |                                               |            |              |       |     |        |     |  |  |

| [7]<br>INTEN    | Internal Precision Oscillator Enable<br>1 = Internal precision oscillator is enabled.<br>0 = Internal precision oscillator is disabled.                                                 |                                               |            |              |       |     |        |     |  |  |

| [6]             | <b>Reserved</b><br>This bit is reserved and must be programmed to 0 during writes and to 0 when read.                                                                                   |                                               |            |              |       |     |        |     |  |  |

| [5]<br>WDTEN    | Watchdog Timer Oscillator Enable<br>1 = Watchdog Timer oscillator is enabled.<br>0 = Watchdog Timer oscillator is disabled.                                                             |                                               |            |              |       |     |        |     |  |  |

| [4]<br>POFEN    | 1 = Failure                                                                                                                                                                             | scillator Fai<br>detection ar<br>detection ar | d recovery | of primary o |       |     |        |     |  |  |

| [3]<br>WDFEN    | Watchdog Timer Oscillator Failure Detection Enable<br>1 = Failure detection of Watchdog Timer oscillator is enabled.<br>0 = Failure detection of Watchdog Timer oscillator is disabled. |                                               |            |              |       |     |        |     |  |  |

| [2:0]<br>SCKSEL | • •                                                                                                                                                                                     |                                               |            |              |       |     |        |     |  |  |

### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                       |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data<br>; value 01H, is the source. The value 01H is written into the<br>; Register at address 234H. |

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

### Example 1

If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 106.

### Table 106. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 107.

ilog° Embedded in Life An∎IXYS Company

188

| Assembly  |                                                |     | lress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch  | Instr. |

|-----------|------------------------------------------------|-----|--------------|-------------|---|---|-----|-----|---|---|--------|--------|

| Mnemonic  | Symbolic Operation                             | dst | src          | (Hex)       | С | Ζ | S   | ۷   | D | Н | Cycles |        |

| POPX dst  | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1 | ER  |              | D8          | - | - | -   | -   | - | _ | 3      | 2      |

| PUSH src  | $SP \leftarrow SP - 1$                         | R   |              | 70          | - | - | _   | _   | _ | - | 2      | 2      |

|           | $@SP \leftarrow src$                           | IR  |              | 71          | • |   |     |     |   |   | 2      | 3      |

|           | -                                              | IM  |              | IF70        |   |   |     |     |   |   | 3      | 2      |

| PUSHX src | $SP \leftarrow SP - 1$<br>@SP ← src            | ER  |              | C8          | _ | _ | _   | _   | _ | - | 3      | 2      |

| RCF       | C ← 0                                          |     |              | CF          | 0 | _ | -   | _   | _ | _ | 1      | 2      |

| RET       | $PC \leftarrow @SP \\ SP \leftarrow SP + 2$    |     |              | AF          | _ | - | -   | _   | _ | _ | 1      | 4      |

| RL dst    |                                                | R   |              | 90          | * | * | *   | *   | _ | - | 2      | 2      |

|           | C                                              | IR  |              | 91          | • |   |     |     |   |   | 2      | 3      |

| RLC dst   |                                                | R   |              | 10          | * | * | *   | *   | _ | _ | 2      | 2      |

|           | C ← D7 D6 D5 D4 D3 D2 D1 D0 ← dst              | IR  |              | 11          |   |   |     |     |   |   | 2      | 3      |

| RR dst    |                                                | R   |              | E0          | * | * | *   | *   | - | _ | 2      | 2      |

|           | ► <u>D7D6D5D4D3D2D1D0</u> C<br>dst             | IR  |              | E1          |   |   |     |     |   |   | 2      | 3      |

| RRC dst   |                                                | R   |              | C0          | * | * | *   | *   | _ | _ | 2      | 2      |

|           | ► D7 D6 D5 D4 D3 D2 D1 D0 - C dst              | IR  |              | C1          | • |   |     |     |   |   | 2      | 3      |

### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

208

### UART Timing

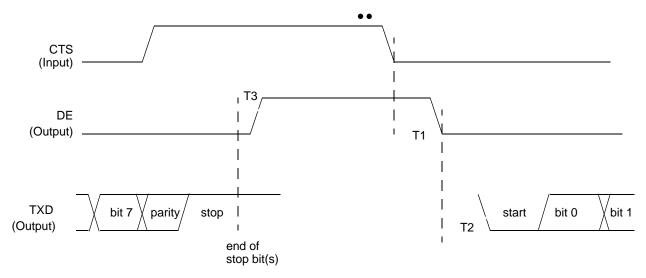

Figure 32 and Table 133 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

Figure 32. UART Timing With CTS

|                |                                                    | Delay (ns)                 |                                            |  |  |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|--|--|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |  |  |  |

| UART           |                                                    |                            |                                            |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | Ŧ                          | : 5                                        |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ± 5                        |                                            |  |  |  |

| Table | 133  | UART | Timing  | With   | CTS |

|-------|------|------|---------|--------|-----|

| Table | 155. |      | rinning | WWILII | 010 |

209

0g

■IXYS Company

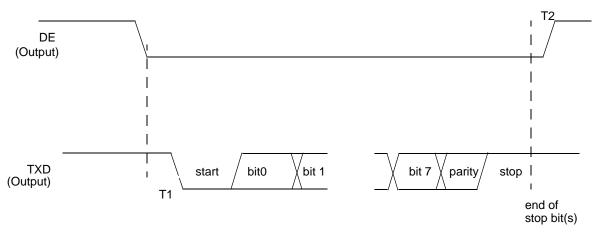

Figure 33 and Table 134 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

|                |                                                                        | Delay (ns)                 |            |  |  |  |

|----------------|------------------------------------------------------------------------|----------------------------|------------|--|--|--|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |  |  |  |

| UART           |                                                                        |                            |            |  |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5                        |            |  |  |  |