Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

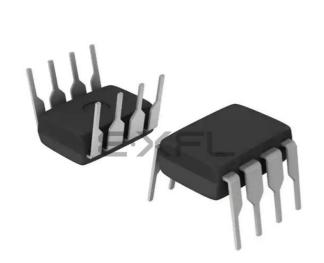

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betails                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413pb005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Embedded in Life An TXYS Company

# **Table of Contents**

| Revision History                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures x                                                                                                                                                                                                                                                                                                   |

| List of Tables xii                                                                                                                                                                                                                                                                                                  |

| Overview1Features1Part Selection Guide2Block Diagram3CPU and Peripheral Overview4General-Purpose I/O4Flash Controller4Internal Precision Oscillator510-Bit Analog-to-Digital Converter5Analog Comparator5Universal Asynchronous Receiver/Transmitter5Timers5Interrupt Controller5Reset Controller5On-Chip Debugger6 |

| Pin Description7Available Packages7Pin Configurations7Signal Descriptions9Pin Characteristics11Address Space13Register File13Program Memory13                                                                                                                                                                       |

| Data Memory15Flash Information Area15                                                                                                                                                                                                                                                                               |

| Register Map                                                                                                                                                                                                                                                                                                        |

| Reset and Stop Mode Recovery21Reset Types21Reset Sources23Power-On Reset23Voltage Brown-Out Reset24Watchdog Timer Reset25                                                                                                                                                                                           |

#### ilog<sup>°</sup> Embedded in Life An ∎IXYS Company

5

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

# **10-Bit Analog-to-Digital Converter**

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

## **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

#### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

## **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

# **Reset Controller**

Z8 Encore!  $XP^{\text{(B)}}$  F0823 Series products can be reset using the RESET pin, POR, WDT time-out, STOP Mode exit, or Voltage Brown-Out warning signal. The RESET pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

7

# **Pin Description**

Z8 Encore! XP F0823 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and pin configurations available for each of the package styles. For information about physical package specifications, see the Packaging chapter on page 210.

# **Available Packages**

Table 2 lists the package styles that are available for each device in the F0823 Series product line.

| Part<br>Number | ADC | 8-pin<br>PDIP | 8-pin<br>SOIC | 20-pin<br>PDIP | 20-pin<br>SOIC | 20-pin<br>SSOP | 28-pin<br>PDIP | 28-pin<br>SOIC | 28-pin<br>SSOP | 8-pin QFN/<br>MLF-S |

|----------------|-----|---------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------|

| Z8F0823        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0813        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0423        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0413        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0223        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0213        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0123        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0113        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

Table 2. F0823 Series Package Options

# **Pin Configurations**

Figures 2 through 4 display the pin configurations for all packages available in the F0823 Series. For description of signals, see Table 3. The analog input alternate functions (ANAx) are not available on the Z8F0x13 devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all pins of Ports A, B, and C default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general-purpose input ports until programmed otherwise.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see **the** <u>Port A–C Control Registers</u> **section on page 42**), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overrightarrow{\text{RESET}}$  pin Low. The  $\overrightarrow{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

# **Stop Mode Recovery**

The device enters into STOP Mode when eZ8 CPU executes a STOP instruction. For more details about STOP Mode, see **the** Low-Power Modes **section on page 30**. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the capture occurs on a rising edge or a falling edge of the Timer Input signal. When the capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL1 Register clears indicating the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture or a reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both

ILOG<sup>°</sup> Embedded in Life IXYS Company **79**

input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) = (Capture Value – Start Value) × Prescale System Clock Frequency (Hz)

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the capture occurs on a rising edge or a falling edge of the Timer Input signal. When the capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is because of an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not caused by an input capture event.

Observe the following steps to configure a timer for CAPTURE RESTART Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode; setting the mode also involves writing to TMODEHI bit in TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

# Embedded in Life An IXYS Company 97

# Universal Asynchronous Receiver/ Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. The features of UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) Mode with three configurable interrupt schemes

- BRG can be configured and used as a basic 16-bit timer

- Driver Enable output for external bus transceivers

# Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

nbedded in Life

101

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) performs the following:

1. Write the UART Control 1 Register to select the multiprocessor bit for the byte to be transmitted:

Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 3. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 4. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data Register to again become empty.

#### **Receiving Data Using the Polled Method**

Observe the following steps to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set an acceptable baud rate for the incoming data stream.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable MULTIPROCESSOR Mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if Multiprocessor mode is not enabled, and select either even or odd parity

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to <u>Step 6</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

- 6. Read data from the UART Receive Data Register. If operating in MULTIPROCES-SOR (9-bit) Mode, further actions may be required depending on the MULTIPRO-CESSOR Mode bits MPMD[1:0].

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

Embedded in Life

# **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 68 and Table 69) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

| Bit     | 7           | 6    | 5    | 4   | 3    | 2    | 1    | 0    |  |  |

|---------|-------------|------|------|-----|------|------|------|------|--|--|

| Field   | TEN         | REN  | CTSE | PEN | PSEL | SBRK | STOP | LBEN |  |  |

| RESET   | 0           | 0    | 0    | 0   | 0    | 0    | 0    | 0    |  |  |

| R/W     | R/W         | R/W  | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |  |  |

| Address |             | F42H |      |     |      |      |      |      |  |  |

| Bit     | Description | n    |      |     |      |      |      |      |  |  |

#### Table 68. UART Control 0 Register (U0CTL0)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TEN  | Transmit EnableThis bit enables or disables the transmitter. The enable is also controlled by the $\overline{CTS}$ signaland the CTSE bit. If the $\overline{CTS}$ signal is low and the CTSE bit is 1, the transmitter is enabled.0 = Transmitter disabled.1 = Transmitter enabled.                                                                   |

| [6]<br>REN  | Receive Enable<br>This bit enables or disables the receiver.<br>0 = Receiver disabled.<br>1 = Receiver enabled.                                                                                                                                                                                                                                        |

| [5]<br>CTSE | <b>CTSE—CTS Enable</b><br>0 = The CTS signal has no effect on the transmitter.<br>1 = The UART recognizes the CTS signal as an enable control from the transmitter.                                                                                                                                                                                    |

| [4]<br>PEN  | <ul> <li>Parity Enable</li> <li>This bit enables or disables parity. Even or odd is determined by the PSEL bit.</li> <li>0 = Parity is disabled.</li> <li>1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit .</li> </ul>                                                                 |

| [3]<br>PSEL | <ul> <li>Parity Select</li> <li>0 = Even parity is transmitted and expected on all received data.</li> <li>1 = Odd parity is transmitted and expected on all received data.</li> </ul>                                                                                                                                                                 |

| [2]<br>SBRK | <ul> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = Forces a break condition by setting the output of the transmitter to zero.</li> </ul> |

#### ilog Embedded in Life An IXYS Company 113

| Bit         | Description (Continued)                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>STOP | <ul> <li>Stop Bit Select</li> <li>0 = The transmitter sends one stop bit.</li> <li>1 = The transmitter sends two stop bits.</li> </ul> |

| [0]<br>LBEN | Loop Back Enable<br>0 = Normal operation.<br>1 = All transmitted data is looped back to the receiver.                                  |

#### Table 69. UART Control 1 Register (U0CTL1)

| Bit               | 7        | 6            | 5                       | 4            | 3             | 2            | 1             | 0          |  |

|-------------------|----------|--------------|-------------------------|--------------|---------------|--------------|---------------|------------|--|

| Field             | MPMD[1]  | MPEN         | MPMD[0]                 | MPBT         | DEPOL         | BRGCTL       | RDAIRQ        | IREN       |  |

| RESET             | 0        | 0            | 0                       | 0            | 0             | 0            | 0             | 0          |  |

| R/W               | R/W      | R/W          | R/W                     | R/W          | R/W           | R/W          | R/W           | R/W        |  |

| Address           |          | F43H         |                         |              |               |              |               |            |  |

|                   |          |              |                         |              |               |              |               |            |  |

| Bit               | Descript | tion         |                         |              |               |              |               |            |  |

| [7,5]<br>MPMD[1:0 |          | ROCESSO      | R Mode<br>DR (9-bit) Mo | nde is enabl | ed            |              |               |            |  |

|                   | -        |              | · · ·                   |              |               | aived bytes  | (data and a   | ddrooo)    |  |

|                   |          | -            | erates an int           | • •          |               | •            | •             | aaress).   |  |

|                   |          | •            | erates an int           |              |               |              | •             |            |  |

|                   |          | •            | erates an int           |              |               |              |               |            |  |

|                   | valu     | le stored in | the Address             | Compare R    | egister and   | on all succe | ssive data b  | ytes until |  |

|                   | an a     | address mis  | match occur             | S.           |               |              |               |            |  |

|                   | 11 – Tho |              | arates an inte          | errunt reque | st on all rec | d etch havia | vtes for whic | h the most |  |

| 11 = The UART generates an interrupt request on all received data bytes for which the most |

|--------------------------------------------------------------------------------------------|

| recent address byte matched the value in the Address Compare Register.                     |

| [6]<br>MPEN  | MULTIPROCESSOR (9-bit) Enable<br>This bit is used to enable MULTIPROCESSOR (9-bit) Mode.<br>0 = Disable MULTIPROCESSOR (9-bit) Mode.<br>1 = Enable MULTIPROCESSOR (9-bit) Mode.                                                                                                                                                                                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>MPBT  | <ul> <li>Multiprocessor Bit Transmit</li> <li>This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.</li> <li>0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).</li> <li>1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li> </ul> |

| [3]<br>DEPOL | Driver Enable Polarity<br>0 = DE signal is Active High.<br>1 = DE signal is Active Low.                                                                                                                                                                                                                                                                                                                                                |

edded in Life

132

# Comparator

Z8 Encore! XP F0823 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex.

The features of the comparator include:

- Two inputs which can be connected up using the GPIO multiplex (MUX)

- One input can be connected to a programmable internal reference

- One input can be connected to the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

# Operation

One of the comparator inputs can be connected to an internal reference which is a user selectable reference that is user programmable with 200 mV resolution.

The comparator can be powered down to save on supply current. For details, see the <u>Power</u> <u>Control Register 0</u> section on page 31.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

The following example shows how to safely enable the comparator:

```

di

ld cmp0

nop

i, wait for output to settle

clr irq0; clear any spurious interrupts pending

ei

```

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20kHz or above 20MHz.

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   |      |     |     | FFR | EQH |     |     |     |  |

| RESET   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | FFAH |     |     |     |     |     |     |     |  |

#### Table 85. Flash Frequency High Byte Register (FFREQH)

| Bit    | Description                                    |

|--------|------------------------------------------------|

| [7:0]  | Flash Frequency High Byte                      |

| FFREQH | High byte of the 16-bit Flash Frequency value. |

#### Table 86. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|--------|---|---|---|---|---|---|---|

| Field   | FFREQL |   |   |   |   |   |   |   |

| RESET   |        | 0 |   |   |   |   |   |   |

| R/W     | R/W    |   |   |   |   |   |   |   |

| Address | FFBH   |   |   |   |   |   |   |   |

| Bit    | Description                                   |

|--------|-----------------------------------------------|

| [7:0]  | Flash Frequency Low Byte                      |

| FFREQL | Low byte of the 16-bit Flash Frequency value. |

#### ILO 9<sup>°</sup> Inbedded in Life IIXYS Company 147

# **Option Bit Types**

This section describes the five types of Flash option bits offered in the F083A Series.

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 in program memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in a Flash memory information page. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

**Note:** The trim address range is from information address 20–3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

#### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in the <u>Flash Information Area</u> section on page 15.

#### **Serialization Bits**

As an optional feature, Zilog is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

# **ADC Calibration Data**

#### Table 94. ADC Calibration Bits

| Bit                                             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6 | 5 | 4 | 3 | 2 | 1 | 0   |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|-----|--|

| Field                                           | ADC_CAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   |   |   |   |   |     |  |

| RESET                                           | U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U | U | U | U | U | U | U   |  |

| R/W                                             | R/W         R/W <th>R/W</th> |   |   |   |   |   |   | R/W |  |

| Address                                         | s Information Page Memory 0060H–007DH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |   |   |   |   |   |     |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |   |   |   |   |   |     |  |

# Bit Description [7:0] Analog-to-Digital Converter Calibration Values ADC\_CAL Contains factory-calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in the Software Compensation Procedure section on page 126. The location of each calibration byte is provided in Table 95.

#### Table 95. ADC Calibration Data Location

| Info Page<br>Address | Memory<br>Address | Compensation<br>Usage | ADC Mode                | Reference<br>Type |

|----------------------|-------------------|-----------------------|-------------------------|-------------------|

| 60                   | FE60              | Offset                | Single-Ended Unbuffered | Internal 2.0V     |

| 08                   | FE08              | Gain High Byte        | Single-Ended Unbuffered | Internal 2.0V     |

| 09                   | FE09              | Gain Low Byte         | Single-Ended Unbuffered | Internal 2.0V     |

| 63                   | FE63              | Offset                | Single-Ended Unbuffered | Internal 1.0V     |

| 0A                   | FE0A              | Gain High Byte        | Single-Ended Unbuffered | Internal 1.0V     |

| 0B                   | FE0B              | Gain Low Byte         | Single-Ended Unbuffered | Internal 1.0V     |

| 66                   | FE66              | Offset                | Single-Ended Unbuffered | External 2.0V     |

| 0C                   | FE0C              | Gain High Byte        | Single-Ended Unbuffered | External 2.0V     |

| 0D                   | FE0D              | Gain Low Byte         | Single-Ended Unbuffered | External 2.0V     |

ilog° Embedded in Life An∎IXYS Company

190

| Assembly      |                                                                                                                        |     | dress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------|-------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic      | Symbolic Operation                                                                                                     | dst | src          | (Hex)       | С | Ζ | S   | ۷   | D | Н | Cycles  |        |

| TCM dst, src  | (NOT dst) AND src                                                                                                      | r   | r            | 62          | - | * | *   | 0   | - | _ | 2       | 3      |

|               |                                                                                                                        | r   | lr           | 63          | - |   |     |     |   |   | 2       | 4      |

|               |                                                                                                                        | R   | R            | 64          | - |   |     |     |   |   | 3       | 3      |

|               |                                                                                                                        | R   | IR           | 65          | - |   |     |     |   |   | 3       | 4      |

|               |                                                                                                                        | R   | IM           | 66          | - |   |     |     |   |   | 3       | 3      |

|               |                                                                                                                        | IR  | IM           | 67          | - |   |     |     |   |   | 3       | 4      |

| TCMX dst, src | (NOT dst) AND src                                                                                                      | ER  | ER           | 68          | - | * | *   | 0   | - | _ | 4       | 3      |

|               |                                                                                                                        | ER  | IM           | 69          | - |   |     |     |   |   | 4       | 3      |

| TM dst, src   | dst AND src                                                                                                            | r   | r            | 72          | - | * | *   | 0   | - | _ | 2       | 3      |

|               |                                                                                                                        | r   | lr           | 73          | - |   |     |     |   |   | 2       | 4      |

|               |                                                                                                                        | R   | R            | 74          | - |   |     |     |   |   | 3       | 3      |

|               |                                                                                                                        | R   | IR           | 75          | - |   |     |     |   |   | 3       | 4      |

|               |                                                                                                                        | R   | IM           | 76          | - |   |     |     |   |   | 3       | 3      |

|               |                                                                                                                        | IR  | IM           | 77          | - |   |     |     |   |   | 3       | 4      |

| TMX dst, src  | dst AND src                                                                                                            | ER  | ER           | 78          | - | * | *   | 0   | _ | _ | 4       | 3      |

|               |                                                                                                                        | ER  | IM           | 79          | - |   |     |     |   |   | 4       | 3      |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |     | Vector       | F2          | - | _ | -   | -   | - | _ | 2       | 6      |

| WDT           |                                                                                                                        |     |              | 5F          | _ | _ | _   | _   | _ | _ | 1       | 2      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

| Abbreviation | Description                             | Abbreviation                                   | Description            |

|--------------|-----------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                            | IRR                                            | Indirect Register Pair |

| СС           | Condition code                          | р                                              | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displace-<br>ment | r                                              | 4-bit Working Register |

| DA           | Destination address                     | R                                              | 8-bit register         |

| ER           | Extended Addressing register            | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                    | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| lr           | Indirect Working Register               | RA                                             | Relative               |

| IR           | Indirect register                       | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair          | RR                                             | Register Pair          |

#### Table 119. Opcode Map Abbreviations

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

|   |                                |                                  |                                      |                              |                                |                                  | Lo                            | ower Nil                                  | bble (He                          | x)                           |                            |                          |                           |                           |                         |                          |

|---|--------------------------------|----------------------------------|--------------------------------------|------------------------------|--------------------------------|----------------------------------|-------------------------------|-------------------------------------------|-----------------------------------|------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|--------------------------|

|   | 0                              | 1                                | 2                                    | 3                            | 4                              | 5                                | 6                             | 7                                         | 8                                 | 9                            | Α                          | В                        | С                         | D                         | Е                       | F                        |

| 0 | 1.1<br>BRK                     | 2.2<br>SRP<br>IM                 | 2.3<br><b>ADD</b><br>r1,r2           | 2.4<br><b>ADD</b><br>r1,lr2  | 3.3<br><b>ADD</b><br>R2,R1     | 3.4<br><b>ADD</b><br>IR2,R1      | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM                      | 4.3<br>ADDX<br>ER2,ER1            | 4.3<br>ADDX<br>IM,ER1        | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1        | 2.3<br><b>RLC</b><br>IR1         | 2.3<br>ADC<br>r1,r2                  | 2.4<br>ADC<br>r1,lr2         | 3.3<br>ADC<br>R2,R1            | 3.4<br>ADC<br>IR2,R1             | 3.3<br>ADC<br>R1,IM           | 3.4<br>ADC<br>IR1,IM                      | 4.3<br>ADCX<br>ER2,ER1            | 4.3<br>ADCX<br>IM,ER1        |                            |                          |                           |                           |                         | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1               | 2.3<br>INC<br>IR1                | 2.3<br><b>SUB</b><br>r1,r2           | 2.4<br>SUB<br>r1,lr2         | 3.3<br><b>SUB</b><br>R2,R1     | 3.4<br>SUB<br>IR2,R1             | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br>SUB<br>IR1,IM                      | 4.3<br><b>SUBX</b><br>ER2,ER1     | 4.3<br><b>SUBX</b><br>IM,ER1 |                            |                          |                           |                           |                         | 1                        |

| 3 | 2.2<br>DEC<br>R1               | 2.3<br>DEC<br>IR1                | 2.3<br>SBC<br>r1,r2                  | 2.4<br>SBC<br>r1,lr2         | 3.3<br>SBC<br>R2,R1            | 3.4<br>SBC<br>IR2,R1             | 3.3<br>SBC<br>R1,IM           | 3.4<br>SBC<br>IR1,IM                      | 4.3<br><b>SBCX</b><br>ER2,ER1     | 4.3<br>SBCX                  |                            |                          |                           |                           |                         |                          |

| 4 | 2.2<br>DA<br>R1                | 2.3<br>DA<br>IR1                 | 2.3<br><b>OR</b>                     | 2.4<br>OR                    | 3.3<br>OR<br>R2,R1             | 3.4<br><b>OR</b>                 | 3.3<br><b>OR</b>              | 3.4<br><b>OR</b>                          | 4.3<br>ORX<br>ER2,ER1             | 4.3<br>ORX                   |                            |                          |                           |                           |                         |                          |

| 5 | 2.2<br><b>POP</b><br>R1        | 2.3<br><b>POP</b>                | r1,r2<br>2.3<br>AND                  | r1,lr2<br>2.4<br>AND         | 3.3<br>AND<br>R2,R1            | 3.4<br>AND                       | 81,IM<br>3.3<br><b>AND</b>    | 3.4<br>AND                                | 4.3<br>ANDX                       | 4.3<br>ANDX                  |                            |                          |                           |                           |                         | 1.2<br>WDT               |

| 6 | 2.2<br>COM                     | IR1<br>2.3<br>COM                | r1,r2<br>2.3<br>TCM                  | r1,lr2<br>2.4<br>TCM         | 3.3<br>TCM                     | 3.4<br>TCM                       | 81,IM<br>3.3<br><b>TCM</b>    | 3.4<br>TCM                                | 4.3<br><b>TCMX</b>                | 4.3<br><b>TCMX</b>           |                            |                          |                           |                           |                         | 1.2<br>STOP              |

| 7 | R1<br>2.2<br><b>PUSH</b><br>R2 | IR1<br>2.3<br><b>PUSH</b><br>IR2 | r1,r2<br>2.3<br><b>TM</b>            | r1,lr2<br>2.4<br><b>TM</b>   | R2,R1<br>3.3<br><b>TM</b>      | IR2,R1<br>3.4<br><b>TM</b>       | R1,IM<br>3.3<br><b>TM</b>     | IR1,IM<br>3.4<br><b>TM</b>                | ER2,ER1<br>4.3<br><b>TMX</b>      | 4.3<br><b>TMX</b>            |                            |                          |                           |                           |                         | 1.2<br>HALT              |

| 8 | 2.5<br>DECW<br>RR1             | 2.6<br>DECW<br>IRR1              | r1,r2<br>2.5<br>LDE                  | r1,lr2<br>2.9<br><b>LDEI</b> | R2,R1<br>3.2<br>LDX            | IR2,R1<br>3.3<br>LDX             | R1,IM<br>3.4<br>LDX           | IR1,IM<br>3.5<br><b>LDX</b>               | 3.4<br>LDX                        | IM,ER1<br>3.4<br>LDX         |                            |                          |                           |                           |                         | 1.2<br><b>DI</b>         |

| 9 | 2.2<br>RL<br>R1                | 2.3<br>RL<br>IR1                 | r1,Irr2<br>2.5<br>LDE                | 2.9<br>LDEI<br>Ir2,Irr1      | r1,ER2<br>3.2<br>LDX<br>r2,ER1 | Ir1,ER2<br>3.3<br>LDX<br>Ir2,ER1 | 3.4<br>LDX<br>R2,IRR1         | IRR2,IR1<br>3.5<br><b>LDX</b><br>IR2,IRR1 | r1,rr2,X<br>3.3<br>LEA<br>r1,r2,X | 3.5<br><b>LEA</b>            |                            |                          |                           |                           |                         | 1.2<br>El                |

| A | 2.5<br>INCW<br>RR1             | 2.6<br>INCW                      | r2,Irr1<br>2.3<br><b>CP</b><br>r1,r2 | 2.4<br><b>CP</b><br>r1,lr2   | 3.3<br><b>CP</b><br>R2,R1      | 3.4<br><b>CP</b><br>IR2,R1       | 3.3<br>CP<br>R1,IM            | 3.4<br>CP<br>IR1,IM                       | 4.3<br>CPX<br>ER2,ER1             | 4.3<br>CPX<br>IM,ER1         |                            |                          |                           |                           |                         | 1.4<br>RET               |

| в | 2.2<br>CLR<br>R1               | 2.3<br>CLR<br>IR1                | 2.3<br>XOR<br>r1,r2                  | 2.4<br>XOR<br>r1,lr2         | 3.3<br>XOR<br>R2,R1            | 3.4<br>XOR<br>IR2,R1             | 3.3<br>XOR<br>R1,IM           | 3.4<br>XOR<br>IR1,IM                      | 4.3<br><b>XORX</b><br>ER2,ER1     | 4.3<br><b>XORX</b><br>IM,ER1 |                            |                          |                           |                           |                         | 1.5<br>IRET              |

| С | 2.2<br>RRC<br>R1               | 2.3<br>RRC<br>IR1                | 2.5<br>LDC<br>r1,lrr2                | 2.9<br>LDCI<br>lr1,lrr2      | 2.3<br>JP<br>IRR1              | 2.9<br>LDC<br>lr1,lrr2           | IXT,IW                        | 3.4<br>LD<br>r1,r2,X                      | 3.2<br>PUSHX<br>ER2               |                              |                            |                          |                           |                           |                         | 1.2<br>RCF               |

| D | 2.2<br>SRA<br>R1               | 2.3<br>SRA<br>IR1                | 2.5<br>LDC<br>r2,Irr1                | 2.9<br>LDCI<br>lr2,lrr1      | 2.6                            | 2.2<br>BSWAP<br>R1               | 3.3<br>CALL<br>DA             | 3.4<br>LD<br>r2,r1,X                      | 3.2<br><b>POPX</b><br>ER1         |                              |                            |                          |                           |                           |                         | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1         | 2.3<br><b>RR</b><br>IR1          | 2.2<br>BIT<br>p,b,r1                 | 2.3<br>LD<br>r1,lr2          | 3.2<br>LD<br>R2,R1             | 3.3<br>LD<br>IR2,R1              | 3.2<br>LD<br>R1,IM            | 3.3<br>LD<br>IR1,IM                       | 4.2<br>LDX<br>ER2,ER1             | 4.2<br>LDX<br>IM,ER1         |                            |                          |                           |                           |                         | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1              | 2.3<br>SWAP<br>IR1               | 2.6<br>TRAP<br>Vector                | 2.3<br>LD<br>lr1,r2          | 2.8<br>MULT<br>RR1             | 3.3<br>LD<br>R2,IR1              | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X            |                                   |                              | V                          | ┥                        | V                         | ▼                         | V                       |                          |

Figure 27. First Opcode Map

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Embedded in Life An IXYS Company 197

# **DC Characteristics**

Table 121 lists the DC characteristics of the Z8 Encore! XP F0823 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

|                  | T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise specified) |                     |                |                      |       |                                                                                                                                                                |  |  |  |

|------------------|------------------------------------------------------------------|---------------------|----------------|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol           | Parameter                                                        | Minimum             | Typical        | Maximum              | Units | Conditions                                                                                                                                                     |  |  |  |

| V <sub>DD</sub>  | Supply Voltage                                                   | 2.7                 | _              | 3.6                  | V     |                                                                                                                                                                |  |  |  |

| V <sub>IL1</sub> | Low Level Input<br>Voltage                                       | -0.3                | -              | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                                |  |  |  |

| V <sub>IH1</sub> | High Level Input<br>Voltage                                      | 0.7*V <sub>DD</sub> | -              | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all sig-<br>nal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |  |  |  |

| V <sub>IH2</sub> | High Level Input<br>Voltage                                      | 0.7*V <sub>DD</sub> | -              | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when pro-<br>grammable pull-ups are<br>enabled.                          |  |  |  |

| V <sub>OL1</sub> | Low Level Output<br>Voltage                                      | -                   | -              | 0.4                  | V     | I <sub>OL</sub> = 2mA; V <sub>DD</sub> = 3.0V<br>High Output Drive disabled.                                                                                   |  |  |  |

| V <sub>OH1</sub> | High Level Output<br>Voltage                                     | 2.4                 | -              | -                    | V     | $I_{OH} = -2mA; V_{DD} = 3.0V$<br>High Output Drive disabled.                                                                                                  |  |  |  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage                                      | -                   | -              | 0.6                  | V     | $I_{OL}$ = 20mA; $V_{DD}$ = 3.3 V<br>High Output Drive enabled.                                                                                                |  |  |  |

| V <sub>OH2</sub> | High Level Output<br>Voltage                                     | 2.4                 | -              | -                    | V     | I <sub>OH</sub> = -20mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                                 |  |  |  |

| I <sub>IH</sub>  | Input Leakage Cur-<br>rent                                       | -                   | <u>+</u> 0.002 | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V$                                                                                                                          |  |  |  |

| I <sub>IL</sub>  | Input Leakage Cur-<br>rent                                       | -                   | <u>+</u> 0.007 | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V$                                                                                                                          |  |  |  |

| I <sub>TL</sub>  | Tristate Leakage<br>Current                                      | -                   | -              | <u>+</u> 5           | μA    |                                                                                                                                                                |  |  |  |

| Table 121. | DC | Characteristics |

|------------|----|-----------------|

|            |    | •               |

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

## G

GATED mode 89 general-purpose I/O 33 GPIO 4.33 alternate functions 34 architecture 34 control register definitions 40 input data sample timing 204 interrupts 40 port A-C pull-up enable sub-registers 47, 48, 49 port A-H address registers 41 port A-H alternate function sub-registers 43 port A-H control registers 42 port A-H data direction sub-registers 43 port A-H high drive enable sub-registers 45 port A-H input data registers 50 port A-H output control sub-registers 44 port A-H output data registers 51 port A-H stop mode recovery sub-registers 46 port availability by device 33 port input timing 205 port output timing 206

# Η

H 177 HALT 180 halt mode 31, 180 hexadecimal number prefix/suffix 177

# I

I2C 4 IM 176 immediate data 176 immediate operand prefix 177 INC 178 increment 178 increment word 178 INCW 178 indexed 177 indirect address prefix 177 indirect register 176 indirect register pair 176 indirect working register 176 indirect working register pair 176 infrared encoder/decoder (IrDA) 117 Instruction Set 174 instruction set, eZ8 CPU 174 instructions ADC 178 **ADCX 178** ADD 178 **ADDX 178** AND 181 **ANDX 181** arithmetic 178 **BCLR 179 BIT 179** bit manipulation 179 block transfer 179 **BRK 181 BSET 179** BSWAP 179, 181 BTJ 181 **BTJNZ 181 BTJZ 181 CALL 181** CCF 179, 180 **CLR 180** COM 181 CP 178 **CPC 178 CPCX 178** CPU control 180 **CPX 178** DA 178 **DEC 178 DECW 178** DI 180 DJNZ 181 EI 180 **HALT 180 INC 178 INCW 178 IRET 181** JP 181