Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u> </u>                                                  |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413pj005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 34. | LED Drive Level Low Register (LEDLVLL)           | 53  |

|-----------|--------------------------------------------------|-----|

| Table 35. | Trap and Interrupt Vectors in Order of Priority  |     |

| Table 36. | Interrupt Request 0 Register (IRQ0)              |     |

| Table 37. | Interrupt Request 1 Register (IRQ1)              |     |

| Table 38. | Interrupt Request 2 Register (IRQ2)              |     |

| Table 39. | IRQ0 Enable and Priority Encoding                |     |

| Table 40. | IRQ0 Enable High Bit Register (IRQ0ENH)          |     |

| Table 41. | IRQ0 Enable Low Bit Register (IRQ0ENL)           |     |

| Table 42. | IRQ1 Enable and Priority Encoding                | 63  |

| Table 43. | IRQ1 Enable Low Bit Register (IRQ1ENL)           | 64  |

| Table 44. | IRQ1 Enable High Bit Register (IRQ1ENH)          | 64  |

| Table 45. | IRQ2 Enable and Priority Encoding                | 65  |

| Table 46. | IRQ2 Enable High Bit Register (IRQ2ENH)          | 65  |

| Table 47. | IRQ2 Enable Low Bit Register (IRQ2ENL)           | 66  |

| Table 48. | Interrupt Edge Select Register (IRQES)           | 66  |

| Table 49. | Shared Interrupt Select Register (IRQSS)         | 67  |

| Table 50. | Interrupt Control Register (IRQCTL)              | 68  |

| Table 51. | Timer 0–1 High Byte Register (TxH)               | 84  |

| Table 52. | Timer 0–1 Low Byte Register (TxL)                | 84  |

| Table 53. | Timer 0–1 Reload High Byte Register (TxRH)       | 85  |

| Table 54. | Timer 0–1 Reload Low Byte Register (TxRL)        | 85  |

| Table 55. | Timer 0–1 PWM High Byte Register (TxPWMH)        | 86  |

| Table 56. | Timer 0–1 PWM Low Byte Register (TxPWML)         | 86  |

| Table 57. | Timer 0–1 Control Register 0 (TxCTL0)            | 87  |

| Table 58. | Timer 0–1 Control Register 1 (TxCTL1)            | 88  |

| Table 59. | Watchdog Timer Approximate Time-Out Delays       | 91  |

| Table 60. | Watchdog Timer Control Register (WDTCTL)         | 94  |

| Table 61. | Watchdog Timer Reload Upper Byte Register (WDTU) | 95  |

| Table 62. | Watchdog Timer Reload High Byte Register (WDTH)  | 95  |

| Table 63. | Watchdog Timer Reload Low Byte Register (WDTL)   | 95  |

| Table 64. | UART Transmit Data Register (U0TXD)              | 109 |

| Table 65. | UART Receive Data Register (U0RXD)               | 109 |

| Table 66. | UART Status 0 Register (U0STAT0)                 | 110 |

| Table 67. | UART Status 1 Register (U0STAT1)                 | 111 |

| Table 68. | UART Control 0 Register (U0CTL0)                 |     |

| Table 69. | UART Control 1 Register (U0CTL1)                 | 113 |

| Table 106. | Assembly Language Syntax Example 1 175                                |

|------------|-----------------------------------------------------------------------|

| Table 107. | Assembly Language Syntax Example 2                                    |

|            | Notational Shorthand                                                  |

| Table 109. | Additional Symbols                                                    |

| Table 110. | Arithmetic Instructions                                               |

| Table 111. | Bit Manipulation Instructions                                         |

| Table 112. | Block Transfer Instructions 179                                       |

| Table 113. | CPU Control Instructions 180                                          |

| Table 114. | Load Instructions                                                     |

| Table 115. | Logical Instructions                                                  |

| Table 116. | Program Control Instructions                                          |

| Table 117. | Rotate and Shift Instructions                                         |

| Table 118. | eZ8 CPU Instruction Summary 182                                       |

|            | Opcode Map Abbreviations 193                                          |

| Table 120. | Absolute Maximum Ratings 196                                          |

| Table 121. | DC Characteristics                                                    |

| Table 122. | Power Consumption                                                     |

| Table 123. | AC Characteristics                                                    |

| Table 124. | Internal Precision Oscillator Electrical Characteristics              |

| Table 125. | Power-On Reset and Voltage Brown-Out Electrical Characteristics       |

|            | and Timing 201                                                        |

|            | Flash Memory Electrical Characteristics and Timing 202                |

|            | Watchdog Timer Electrical Characteristics and Timing 202              |

|            | Analog-to-Digital Converter Electrical Characteristics and Timing 203 |

|            | Comparator Electrical Characteristics                                 |

|            | GPIO Port Input Timing 205                                            |

|            | GPIO Port Output Timing 206                                           |

|            | On-Chip Debugger Timing                                               |

|            | UART Timing With CTS 208                                              |

|            | UART Timing Without CTS 209                                           |

| Table 135. | Z8 Encore! XP F0823 Series Ordering Matrix 211                        |

16

n 🗖 IXYS Company

# **Register Map**

Table 8 lists an address map of the Z8 Encore! XP F0823 Series Register File. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, nor all GPIO ports. Consider registers for unimplemented peripherals to be reserved.

| Address (Hex)  | Register Description              | Mnemonic      | Reset (Hex) | Page<br>No. |

|----------------|-----------------------------------|---------------|-------------|-------------|

| General-Purpos | e RAM                             |               |             |             |

| Z8F0823/Z8F081 | 13 Devices                        |               |             |             |

| 000–3FF        | General-Purpose Register File RAM | _             | XX          |             |

| 400-EFF        | Reserved                          | _             | XX          |             |

| Z8F0423/Z8F041 | 13 Devices                        |               |             |             |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |             |

| 400–EFF        | Reserved                          | _             | XX          |             |

| Z8F0223/Z8F021 | 13 Devices                        |               |             |             |

| 000–1FF        | General-Purpose Register File RAM |               | XX          |             |

| 200–EFF        | Reserved                          | _             | XX          |             |

| Z8F0123/Z8F011 | 13 Devices                        |               |             |             |

| 000–0FF        | General-Purpose Register File RAM |               | XX          |             |

| 100-EFF        | Reserved                          | _             | XX          |             |

| Timer 0        |                                   |               |             |             |

| F00            | Timer 0 High Byte                 | T0H           | 00          | <u>84</u>   |

| F01            | Timer 0 Low Byte                  | TOL           | 01          | <u>84</u>   |

| F02            | Timer 0 Reload High Byte          | TORH          | FF          | <u>85</u>   |

| F03            | Timer 0 Reload Low Byte           | TORL          | FF          | <u>85</u>   |

| F04            | Timer 0 PWM High Byte             | <b>T0PWMH</b> | 00          | <u>86</u>   |

| F05            | Timer 0 PWM Low Byte              | TOPWML        | 00          | <u>86</u>   |

| F06            | Timer 0 Control 0                 | TOCTLO        | 00          | <u>87</u>   |

| F07            | Timer 0 Control 1                 | T0CTL1        | 00          | <u>88</u>   |

| Timer 1        |                                   |               |             |             |

| F08            | Timer 1 High Byte                 | T1H           | 00          | <u>84</u>   |

| F09            | Timer 1 Low Byte                  | T1L           | 01          | <u>84</u>   |

#### Table 8. Register File Address Map

Note: XX=Undefined.

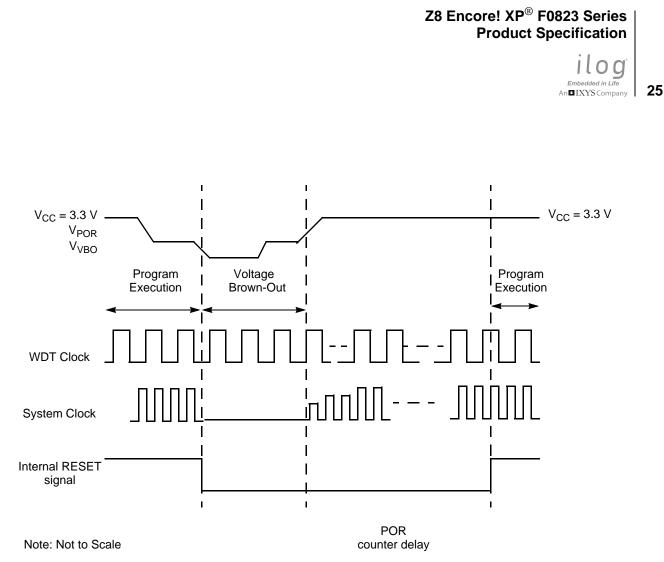

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

### Watchdog Timer Reset

If the device is in NORMAL or STOP Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT status bit in the WDT Control Register is set to signify that the reset was initiated by the Watchdog Timer.

### **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system

### ILOG<sup>°</sup> Embedded in Life

### HALT Mode

Executing the eZ8 CPU's HALT instruction places the device into HALT Mode, which powers down the CPU but leaves all other peripherals active. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

### **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F0823 Series devices. Disabling a given peripheral minimizes its power consumption.

## **Power Control Register Definitions**

The following sections describe the power control registers.

### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

| Z8 Encore! XP <sup>®</sup> F082<br>Product Spec |      |

|-------------------------------------------------|------|

|                                                 | ilog |

Embedded in Life An IXYS Company 70

## Architecture

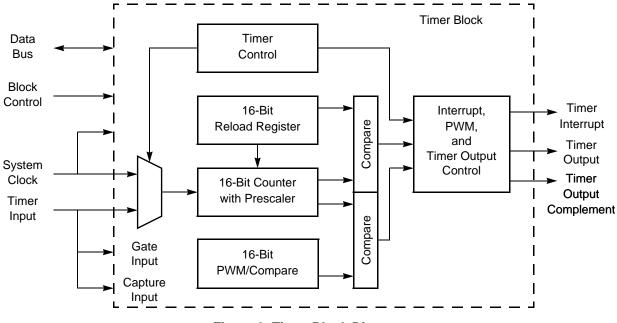

Figure 9 displays the architecture of the timers.

Figure 9. Timer Block Diagram

## Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

### **Timer Operating Modes**

The timers can be configured to operate in the following modes:

### **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

nbedded in Life

7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

### **Timer Pin Signal Operation**

Timer Output is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

### **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

Timer 0-1 High and Low Byte Registers: see page 83

Timer Reload High and Low Byte Registers: see page 84

Timer 0-1 PWM High and Low Byte Registers: see page 86

Timer 0-1 Control Registers: see page 86

### Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers (Table 51 and Table 52) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH

### ILOG<sup>°</sup> Inbedded in Life

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

### Operation

The WDT is a retriggerable one-shot timer that resets or interrupts F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 59 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10kHz typical WDT oscillator frequ |                        |  |

|------------------|------------------|------------------------------------------------------------------------|------------------------|--|

| (Hex)            | (Decimal)        | Typical                                                                | Description            |  |

| 000004           | 4                | 400 μs                                                                 | Minimum time-out delay |  |

| FFFFF            | 16,777,215       | 28 minutes                                                             | Maximum time-out delay |  |

#### Table 59. Watchdog Timer Approximate Time-Out Delays

ilog<sup>°</sup> Embedded in Life An∎IXYS Company 95

### Table 61. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit       | 7           | 6             | 5            | 4              | 3             | 2             | 1         | 0    |

|-----------|-------------|---------------|--------------|----------------|---------------|---------------|-----------|------|

| Field     |             | WDTU          |              |                |               |               |           |      |

| RESET     |             | 00H           |              |                |               |               |           |      |

| R/W       | R/W*        | R/W*          | R/W*         | R/W*           | R/W*          | R/W*          | R/W*      | R/W* |

| Address   |             |               |              | FF             | 1H            |               |           |      |

| Note: R/W | *—Read retu | rns the curre | nt WDT count | t value. Write | sets the appr | opriate Reloa | id Value. |      |

|           |             |               |              |                |               |               |           |      |

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

### Table 62. Watchdog Timer Reload High Byte Register (WDTH)

| Bit       | 7           | 6             | 5            | 4            | 3             | 2             | 1        | 0    |

|-----------|-------------|---------------|--------------|--------------|---------------|---------------|----------|------|

| Field     |             |               |              | WD           | TH            |               |          |      |

| RESET     | 04H         |               |              |              |               |               |          |      |

| R/W       | R/W*        | R/W*          | R/W*         | R/W*         | R/W*          | R/W*          | R/W*     | R/W* |

| Address   |             |               |              | FF           | 2H            |               |          |      |

| Note: R/W | *—Read retu | rns the curre | nt WDT count | value. Write | sets the appr | opriate Reloa | d Value. |      |

| Bit   | Description                                              |

|-------|----------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                     |

| WDTH  | Middle byte, Bits[15:8], of the 24-bit WDT reload value. |

#### Table 63. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit                                                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Field                                                                                         |      | WDTL |      |      |      |      |      |      |

| RESET                                                                                         | 00H  |      |      |      |      |      |      |      |

| R/W                                                                                           | R/W* |

| Address                                                                                       | FF3H |      |      |      |      |      |      |      |

| Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |      |

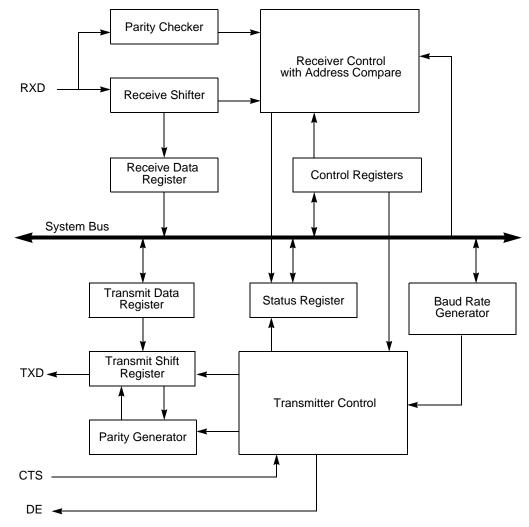

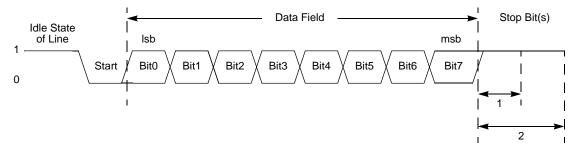

## Operation

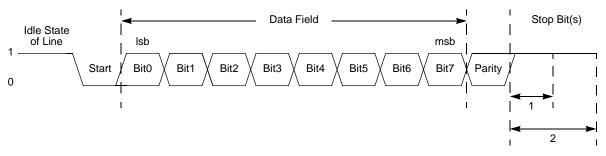

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

#### ilog° Embedded in Life An∎IXYS Company 99

Figure 11. UART Asynchronous Data Format without Parity

Figure 12. UART Asynchronous Data Format with Parity

### **Transmitting Data Using the Polled Method**

Observe the following steps to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register, if MULTIPROCESSOR Mode is appropriate, to enable MULTIPROCESSOR (9-bit) Mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR Mode.

- 5. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR Mode is not enabled, and select either even or odd parity (PSEL)

#### ilog<sup>°</sup> Embedded in Life An TIXYS Company

111

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | <ul> <li>Transmitter Data Register Empty</li> <li>This bit indicates that the UART Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the UART Transmit Data Register resets this bit.</li> <li>0 = Do not write to the UART Transmit Data Register.</li> <li>1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted.</li> </ul> |

| [1]<br>TXE  | <b>Transmitter Empty</b><br>This bit indicates that the transmit shift register is empty and character transmission is finished.<br>0 = Data is currently transmitting.<br>1 = Transmission is complete.                                                                                                                                                                                               |

| [0]<br>CTS  | <b>CTS</b> Signal When this bit is read, it returns the level of the $\overline{\text{CTS}}$ signal. This signal is active Low.                                                                                                                                                                                                                                                                        |

## **UART Status 1 Register**

This register contains multiprocessor control and status bits.

| Table 67. UART Stat | us 1 Register (U0STAT1) |

|---------------------|-------------------------|

|---------------------|-------------------------|

| Bit     | 7 | 6      | 5    | 4  | 3   | 2   | 1 | 0 |

|---------|---|--------|------|----|-----|-----|---|---|

| Field   |   | NEWFRM | MPRX |    |     |     |   |   |

| RESET   | 0 | 0      | 0    | 0  | 0   | 0   | 0 | 0 |

| R/W     | R | R      | R    | R  | R/W | R/W | R | R |

| Address |   |        |      | F4 | 4H  |     |   |   |

| Bit           | Description                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | <b>Reserved</b><br>These bits are reserved; R/W bits must be programmed to 000000 during writes and 000000 when read.                                                                                                                                                                             |

| [1]<br>NEWFRM | <ul> <li>New Frame</li> <li>A status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.</li> <li>0 = The current byte is not the first data byte of a new frame.</li> <li>1 = The current byte is the first data byte of a new frame.</li> </ul> |

| [0]<br>MPRX   | Multiprocessor Receive<br>Returns the value of the most recent multiprocessor bit received. Reading from the UART<br>Receive Data Register resets this bit to 0.                                                                                                                                  |

dded in Life

118

passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

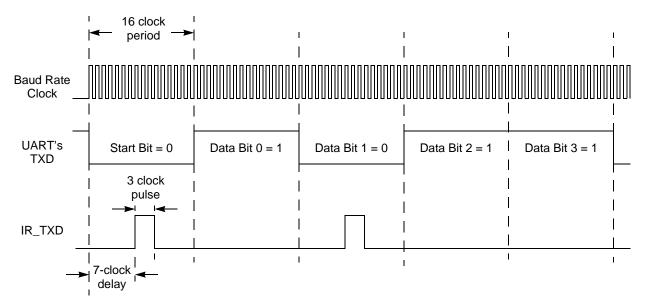

The baud rate is set by the UART's baud rate generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the infrared endec is enabled, the UART's TXD signal is internal to Z8 Encore! XP F0823 Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

#### illog<sup>®</sup> Ibedded in Life IXYS Company 138

## Table 80. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code program-<br>ming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-<br>Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                    |

### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

### **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F0823 Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 79</u> on page 134.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

ilog Embedded in Life

IXYS Company

149

## **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits.

| Bit     | 7                    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|---------|----------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|

| Field   | TRMDR: Trim Bit Data |     |     |     |     |     |     |     |  |  |  |  |

| RESET   | 0                    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| R/W     | R/W                  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address |                      |     |     | FF  | 7H  |     |     |     |  |  |  |  |

#### Table 88. Trim Bit Data Register (TRMDR)

## Flash Option Bit Address Space

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

#### Table 89. Flash Option Bits at Program Memory Address 0000H

| Bit       | 7            | 6           | 5            | 4              | 3          | 2   | 1        | 0   |

|-----------|--------------|-------------|--------------|----------------|------------|-----|----------|-----|

| Field     | WDT_RES      | WDT_AO      | Reserved     |                | VBO_AO     | FRP | Reserved | FWP |

| RESET     | U            | U           | U            | U              | U          | U   | U        | U   |

| R/W       | R/W          | R/W         | R/W          | R/W R/W R/W R/ |            | R/W | R/W      | R/W |

| Address   |              |             | Р            | rogram Mer     | nory 0000H |     |          |     |

| Note: U = | Unchanged by | Reset R/W = | = Read/Write |                |            |     |          |     |

U = Unchanged by Reset. R/W = Read/Write.

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>WDT_RES | <ul> <li>Watchdog Timer Reset</li> <li>0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.</li> <li>1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                           |

| [6]<br>WDT_AO  | <ul> <li>Watchdog Timer Always ON</li> <li>0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.</li> <li>1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.</li> </ul> |

| [5:4]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 11 during writes, and to 11 when read.                                                                                                                                                                                                                                                                                                |

PS024315-1011

> ilog Embedded in Life An IXYS Company 152

#### Table 92. Trim Option Bits at 0001H

| Bit       | 7                             | 6            | 5              | 4   | 3   | 2   | 0   |     |  |  |  |  |

|-----------|-------------------------------|--------------|----------------|-----|-----|-----|-----|-----|--|--|--|--|

| Field     | Reserved                      |              |                |     |     |     |     |     |  |  |  |  |

| RESET     | U                             | U            | U              | U   | U   | U   | UU  |     |  |  |  |  |

| R/W       | R/W                           | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address   | Information Page Memory 0021H |              |                |     |     |     |     |     |  |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W | / = Read/Write | э.  |     |     |     |     |  |  |  |  |

| Bit   | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                  |

|       | These bits are reserved. Altering this register may result in incorrect device operation. |

#### Table 93. Trim Option Bits at 0002H (TIPO)

| Bit       | 7                             | 6            | 5              | 4  | 3 | 2 | 1 | 0 |  |  |  |  |

|-----------|-------------------------------|--------------|----------------|----|---|---|---|---|--|--|--|--|

| Field     | IPO_TRIM                      |              |                |    |   |   |   |   |  |  |  |  |

| RESET     | U                             |              |                |    |   |   |   |   |  |  |  |  |

| R/W       | R/W                           |              |                |    |   |   |   |   |  |  |  |  |

| Address   | Information Page Memory 0022H |              |                |    |   |   |   |   |  |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W | / = Read/Write | э. |   |   |   |   |  |  |  |  |

| Bit      | Description                                                   |

|----------|---------------------------------------------------------------|

| [7:0]    | Internal Precision Oscillator Trim Byte                       |

| IPO_TRIM | Contains trimming bits for the Internal Precision Oscillator. |

## **Zilog Calibration Data**

This section briefly describes the features of the following Flash Option Bit calibration registers.

ADC Calibration Data: see page 153

Serialization Data: see page 154

Randomized Lot Identifier: see page 154

ilog° Embedded in Life An∎IXYS Company

188

| Assembly  |                                                | Address<br>Mode |     | _ Opcode(s) |   |   | Flags |   |   |   | Fetch  | Instr. |

|-----------|------------------------------------------------|-----------------|-----|-------------|---|---|-------|---|---|---|--------|--------|

| Mnemonic  | Symbolic Operation                             | dst             | src | (Hex)       | С | Ζ | S     | ۷ | D | Н | Cycles |        |

| POPX dst  | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1 | ER              |     | D8          | - | - | -     | - | _ | _ | 3      | 2      |

| PUSH src  | $SP \leftarrow SP - 1$                         | R               |     | 70          | - | - | _     | _ | _ | - | 2      | 2      |

|           | $@SP \leftarrow src$                           | IR              |     | 71          | • |   |       |   |   |   | 2      | 3      |

|           | -                                              | IM              |     | IF70        |   |   |       |   |   |   | 3      | 2      |

| PUSHX src | $SP \leftarrow SP - 1$<br>@SP ← src            | ER              |     | C8          | _ | _ | _     | _ | _ | - | 3      | 2      |

| RCF       | C ← 0                                          |                 |     | CF          | 0 | _ | -     | _ | _ | _ | 1      | 2      |

| RET       | $PC \leftarrow @SP \\ SP \leftarrow SP + 2$    |                 |     | AF          | _ | - | -     | _ | _ | _ | 1      | 4      |

| RL dst    |                                                | R               |     | 90          | * | * | *     | * | _ | - | 2      | 2      |

|           | C                                              | IR              |     | 91          | • |   |       |   |   |   | 2      | 3      |

| RLC dst   |                                                | R               |     | 10          | * | * | *     | * | _ | _ | 2      | 2      |

|           | C ← D7 D6 D5 D4 D3 D2 D1 D0 ← dst              | IR              |     | 11          |   |   |       |   |   |   | 2      | 3      |

| RR dst    |                                                | R               |     | E0          | * | * | *     | * | - | _ | 2      | 2      |

|           | ► <u>D7D6D5D4D3D2D1D0</u> C<br>dst             | IR              |     | E1          |   |   |       |   |   |   | 2      | 3      |

| RRC dst   |                                                | R               |     | C0          | * | * | *     | * | _ | _ | 2      | 2      |

|           | ► D7 D6 D5 D4 D3 D2 D1 D0 - C C                | IR              |     | C1          | • |   |       |   |   |   | 2      | 3      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Abbreviation | Description                             | Abbreviation                                   | Description            |

|--------------|-----------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                            | IRR                                            | Indirect Register Pair |

| СС           | Condition code                          | р                                              | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displace-<br>ment | r                                              | 4-bit Working Register |

| DA           | Destination address                     | R                                              | 8-bit register         |

| ER           | Extended Addressing register            | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                    | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| lr           | Indirect Working Register               | RA                                             | Relative               |

| IR           | Indirect register                       | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair          | RR                                             | Register Pair          |

#### Table 119. Opcode Map Abbreviations

## Embedded in Life An IXYS Company

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F0823 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 120 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                       | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                  | -40     | +105    | °C    |       |

| Storage temperature                                             | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>              | -0.3    | +5.5    | V     | 1     |

|                                                                 | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$                | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin             | -5      | +5      | μA    |       |

| Maximum output current from active output pin                   | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0°C to 70°C                   |         |         |       |       |

| Total power dissipation                                         |         | 220     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                  |         |         |       |       |

| Total power dissipation                                         |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                  |         |         |       |       |

| Total power dissipation                                         |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 125     | mA    |       |

| Natas, Operating temperature is enacified in DC Characteristics |         |         |       |       |

| Table 1 | 20. Ab | solute N | laximum | Ratings |

|---------|--------|----------|---------|---------|

|---------|--------|----------|---------|---------|

Notes: Operating temperature is specified in DC Characteristics.

This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

2. This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

## Embedded in Life An IXYS Company

## **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                   |                        | V <sub>DD</sub> = 2.7V to 3.6V<br>T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise<br>stated) |                   |       |                                         |  |

|-------------------|------------------------|----------------------------------------------------------------------------------------------------|-------------------|-------|-----------------------------------------|--|

| Symbol            | Parameter              | Minimum                                                                                            | Maximum           | Units | Conditions                              |  |

| FSYSCLK           | System Clock Frequency | _                                                                                                  | 20.0*             | MHz   | Read-only from Flash memory.            |  |

|                   |                        | 0.032768                                                                                           | 20.0 <sup>1</sup> | MHz   | Program or erasure of the Flash memory. |  |

| T <sub>XIN</sub>  | System Clock Period    | 50                                                                                                 | -                 | ns    | $T_{CLK} = 1/F_{SYSCLK}$ .              |  |

| T <sub>XINH</sub> | System Clock High Time | 20                                                                                                 | 30                | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINL</sub> | System Clock Low Time  | 20                                                                                                 | 30                | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINR</sub> | System Clock Rise Time | _                                                                                                  | 3                 | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINF</sub> | System Clock Fall Time | _                                                                                                  | 3                 | ns    | Т <sub>СІ К</sub> = 50ns.               |  |

| Table ' | 123. AC | Characteristics |

|---------|---------|-----------------|

|---------|---------|-----------------|

#### Table 124. Internal Precision Oscillator Electrical Characteristics

|                    |                                                         | V <sub>DD</sub> = 2.7V to 3.6V<br>T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise stated) |            |            |       |                                                 |

|--------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------|------------|-------|-------------------------------------------------|

| Symbol             | Parameter                                               | Minimum                                                                                         | Typical    | Maximum    | Units | Conditions                                      |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |                                                                                                 | 5.53       |            | MHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |                                                                                                 | 32.7       |            | kHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |                                                                                                 | <u>+</u> 1 | <u>+</u> 4 | %     |                                                 |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |                                                                                                 | 3          |            | μs    |                                                 |