Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decails                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413qb005sg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 30. | GPIO Port Output Timing | 206 |

|------------|-------------------------|-----|

| Figure 31. | On-Chip Debugger Timing | 207 |

| Figure 32. | UART Timing With CTS    | 208 |

| Figure 33. | UART Timing Without CTS | 209 |

## List of Tables

| Table 1.  | F0823 Series Family Part Selection Guide                           |

|-----------|--------------------------------------------------------------------|

| Table 2.  | F0823 Series Package Options7                                      |

| Table 3.  | Signal Descriptions                                                |

| Table 4.  | Pin Characteristics (20- and 28-pin Devices)* 11                   |

| Table 5.  | Pin Characteristics (8-Pin Devices) 12                             |

| Table 6.  | Z8 Encore! XP F0823 Series Program Memory Maps 14                  |

| Table 7.  | F0823 Series Flash Memory Information Area Map 15                  |

| Table 8.  | Register File Address Map 16                                       |

| Table 9.  | Reset and Stop Mode Recovery Characteristics and Latency 21        |

| Table 10. | Reset Sources and Resulting Reset Type                             |

| Table 11. | Stop Mode Recovery Sources and Resulting Action 27                 |

| Table 12. | Reset Status Register (RSTSTAT)                                    |

| Table 13. | POR Indicator Values                                               |

| Table 14. | Power Control Register 0 (PWRCTL0) 32                              |

| Table 15. | Port Availability by Device and Package Type                       |

| Table 16. | Port Alternate Function Mapping (8-Pin Parts)                      |

| Table 17. | Port Alternate Function Mapping (Non 8-Pin Parts)                  |

| Table 18. | GPIO Port Registers and Subregisters                               |

| Table 19. | Port A–C GPIO Address Registers (PxADDR) 41                        |

| Table 20. | PADDR[7:0] Subregister Functions                                   |

| Table 21. | Port A–C Control Registers (PxCTL) 42                              |

| Table 22. | Port A–C Data Direction Subregisters (PxDD) 43                     |

| Table 23. | Port A–C Alternate Function Subregisters (PxAF)                    |

| Table 24. | Port A–C Output Control Subregisters (PxOC) 44                     |

| Table 25. | Port A–C High Drive Enable Subregisters (PHDEx) 45                 |

| Table 26. | Port A-C Stop Mode Recovery Source Enable Subregisters (PSMREx) 46 |

| Table 27. | Port A–C Pull-Up Enable Subregisters (PPUEx)                       |

| Table 28. | Port A–C Alternate Function Set 1 Subregisters (PAFS1x) 48         |

| Table 29. | Port A–C Alternate Function Set 2 Subregisters (PxAFS2) 49         |

| Table 30. | Port A–C Input Data Registers (PxIN) 50                            |

| Table 31. | Port A–C Output Data Register (PxOUT) 51                           |

| Table 32. | LED Drive Enable (LEDEN) 51                                        |

| Table 33. | LED Drive Level High Register (LEDLVLH)                            |

| Program Memory Address (Hex)                                                                          | Function                 |

|-------------------------------------------------------------------------------------------------------|--------------------------|

| Z8F0123 and Z8F0113 Products                                                                          |                          |

| 0000–0001                                                                                             | Flash Option Bits        |

| 0002–0003                                                                                             | Reset Vector             |

| 0004–0005                                                                                             | WDT Interrupt Vector     |

| 0006–0007                                                                                             | Illegal Instruction Trap |

| 0008–0037                                                                                             | Interrupt Vectors*       |

| 0038–003D                                                                                             | Oscillator Fail Traps*   |

| 003E-03FF                                                                                             | Program Memory           |

| Note: *See the <u>Trap and Interrupt Vectors in C</u><br>for a list of the interrupt vectors and trap |                          |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

## **Data Memory**

Z8 Encore! XP F0823 Series does not use the eZ8 CPU's 64KB Data Memory address space.

## **Flash Information Area**

Table 7 lists the F0823 Series Flash Information Area. This 128B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory<br>Address (Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00–FE3F                       | Zilog Option Bits.                                                                         |

| FE40–FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60–FE7F                       | Zilog Calibration Data.                                                                    |

| FE80–FFFF                       | Reserved.                                                                                  |

Table 7. F0823 Series Flash Memory Information Area Map

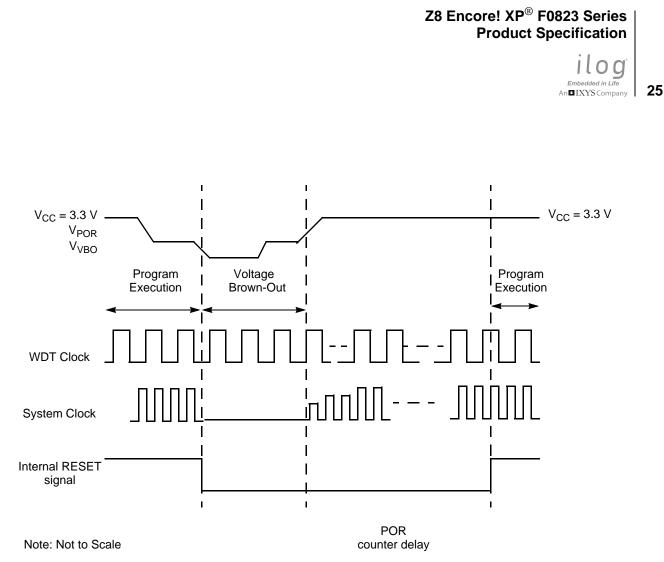

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

## Watchdog Timer Reset

If the device is in NORMAL or STOP Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT status bit in the WDT Control Register is set to signify that the reset was initiated by the Watchdog Timer.

## **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system

### ilog Embedded in Life An IXYS Company 45

## Port A–C High Drive Enable Subregisters

The Port A–C High Drive Enable Subregister (Table 25) is accessed through the Port A–C Control Register by writing 04H to the Port A–C Address Register. Setting the bits in the Port A–C High Drive Enable subregisters to 1 configures the specified port pins for high-current output drive operation. The Port A–C High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

| Table 25. Port A–C High Drive Enable Subregiste | ers (PHDEx) |

|-------------------------------------------------|-------------|

|-------------------------------------------------|-------------|

| Bit     | 7                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Field   | PHDE7                                                                                 | PHDE6 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | If 04H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |       |

### Bit Description

[7:0] **Port High Drive Enabled.**

PHDEx 0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

Note: x indicates the specific GPIO port pin number (7–0).

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

## **Software Interrupt Assertion**

Program code generates interrupts directly. Writing a 1 to the correct bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

Caution: Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

## Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the timeout condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

## **Timers**

Z8 Encore! XP F0823 Series products contain up to two 16-bit reloadable timers that are used for timing, event counting or generation of PWM signals. The timers' features include:

- 16-bit reload counter

- Programmable prescaler with prescale values from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating, or capture signal; external input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

In addition to the timers described in this chapter, the baud rate generator of the UART (if unused) also provides basic timing functionality. For information about using the baud rate generator as an additional timer, see the <u>Universal Asynchronous Receiver/Transmitter</u> chapter on page 97.

### ilog Embedded in Life An∎IXYS Company 80

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture or a reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) = (Capture Value – Start Value) × Prescale System Clock Frequency (Hz)

### **COMPARE Mode**

In COMPARE Mode, the timer counts up to the 16-bit maximum compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting. Observe the following steps to configure a timer for COMPARE Mode and to initiate the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

## Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers (Table 55 and Table 56) control pulse-width modulator (PWM) operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Field   |     |     |     | PW    | MH   |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F04H, | F0CH |     |     |     |

### Table 55. Timer 0–1 PWM High Byte Register (TxPWMH)

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Field   |     |     |     | PW    | /ML  |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F05H, | F0DH |     |     |     |

| Bit           | Description                                                                                                                                                                                                                                                      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]         | Pulse-Width Modulator High and Low Bytes                                                                                                                                                                                                                         |

| PWMH,<br>PWML | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register. |

These TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

## **Timer 0–1 Control Registers**

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

## Timer 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode. It also includes a programmable PWM deadband delay,

### ilog° Embedded in Life An∎IXYS Company 106

### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error

Embedded in Life

n IXYS Company

107

occurred, this byte cannot contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data Register must be read again to clear the error bits is the UART Status 0 Register. Updates to the Receive Data Register occur only when the next data word is received.

## **UART Data and Error Handling Procedure**

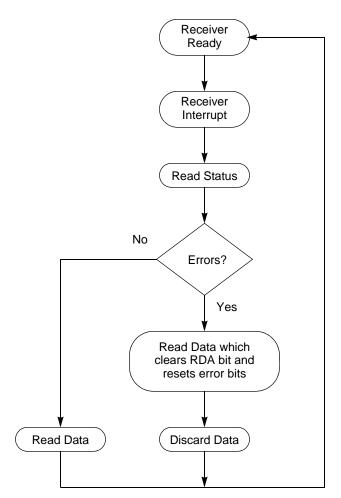

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

Figure 15. UART Receiver Interrupt Service Routine Flow

#### illog<sup>®</sup> Ibedded in Life IXYS Company 138

## Table 80. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code program-<br>ming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-<br>Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                    |

## Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

## **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F0823 Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 79</u> on page 134.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

### ILOG Embedded in Life An IXYS Company 140

## Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

## **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

## **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the Zilog application note titled, <u>Third-Party Flash Programming Support for Z8 Encore! MCUs (AN0117)</u>, available for download at <u>www.zilog.com</u>.

## Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

### ilog<sup>\*</sup> Embedded in Life An∎IXYS Company 154

## **Serialization Data**

### Table 96. Serial Number at 001C–001F (S\_NUM)

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| Field     | S_NUM                                           |     |     |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Information Page Memory 001C–001F               |     |     |     |     |     |     |     |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |

# Bit Description [7:0] Serial Number Byte S\_NUM The serial number is a unique four-byte binary value; see Table 97.

### **Table 97. Serialization Data Locations**

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

## **Randomized Lot Identifier**

### Table 98. Lot Identification Number (RAND\_LOT)

| Bit       | 7                                               | 6            | 5              | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-----------|-------------------------------------------------|--------------|----------------|-----|-----|-----|-----|-----|--|--|--|--|

| Field     | RAND_LOT                                        |              |                |     |     |     |     |     |  |  |  |  |

| RESET     | U                                               | U            | U              | U   | U   | U   | U   | U   |  |  |  |  |

| R/W       | R/W                                             | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address   | Interspersed throughout Information Page Memory |              |                |     |     |     |     |     |  |  |  |  |

| Note: U = | Unchanged b                                     | y Reset. R/M | / = Read/Write | ə.  |     |     |     |     |  |  |  |  |

| Bit             | Description                                                                                                                        |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>RAND_LOT | <b>Randomized Lot ID</b><br>The randomized lot ID is a 32-byte binary value that changes for each production lot; see<br>Table 99. |

155

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 3C                   | FE3C              | Randomized Lot ID Byte 31 (most significant) |

| 3D                   | FE3D              | Randomized Lot ID Byte 30                    |

| 3E                   | FE3E              | Randomized Lot ID Byte 29                    |

| 3F                   | FE3F              | Randomized Lot ID Byte 28                    |

| 58                   | FE58              | Randomized Lot ID Byte 27                    |

| 59                   | FE59              | Randomized Lot ID Byte 26                    |

| 5A                   | FE5A              | Randomized Lot ID Byte 25                    |

| 5B                   | FE5B              | Randomized Lot ID Byte 24                    |

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

### Table 99. Randomized Lot ID Locations

nbedded in Life

171

conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

## Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

## **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control Register.

### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

ilog° Embedded in Life An∎IXYS Company

185

| Assembly     |                                                                                                                   |     | ress<br>ode | _ Opcode(s)          | Flags |   |   |   |   |   | Fetch  | lu at a          |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----|-------------|----------------------|-------|---|---|---|---|---|--------|------------------|

| Mnemonic     | Symbolic Operation                                                                                                | dst | src         | _ Opcode(s)<br>(Hex) |       | Ζ | S | V | D | н | Cycles | Instr.<br>Cycles |

| DA dst       | $dst \gets DA(dst)$                                                                                               | R   |             | 40                   | *     | * | * | Х | - | _ | 2      | 2                |

|              |                                                                                                                   | IR  |             | 41                   | •     |   |   |   |   |   | 2      | 3                |

| DEC dst      | dst ← dst - 1                                                                                                     | R   |             | 30                   | -     | * | * | * | - | _ | 2      | 2                |

|              |                                                                                                                   | IR  |             | 31                   | •     |   |   |   |   |   | 2      | 3                |

| DECW dst     | dst ← dst - 1                                                                                                     | RR  |             | 80                   | _     | * | * | * | _ | _ | 2      | 5                |

|              |                                                                                                                   | IRR |             | 81                   | •     |   |   |   |   |   | 2      | 6                |

| DI           | IRQCTL[7] ← 0                                                                                                     |     |             | 8F                   | -     | - | _ | - | - | _ | 1      | 2                |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                             | r   |             | 0A-FA                | -     | _ | - | - | - | _ | 2      | 3                |

| EI           | IRQCTL[7] ← 1                                                                                                     |     |             | 9F                   | _     | _ | _ | - | _ | _ | 1      | 2                |

| HALT         | HALT Mode                                                                                                         |     |             | 7F                   | -     | _ | _ | - | _ | _ | 1      | 2                |

| INC dst      | dst ← dst + 1                                                                                                     | R   |             | 20                   | _     | * | * | - | _ | _ | 2      | 2                |

|              |                                                                                                                   | IR  |             | 21                   | •     |   |   |   |   |   | 2      | 3                |

|              |                                                                                                                   | r   |             | 0E-FE                | •     |   |   |   |   |   | 1      | 2                |

| INCW dst     | dst ← dst + 1                                                                                                     | RR  |             | A0                   | _     | * | * | * | _ | _ | 2      | 5                |

|              |                                                                                                                   | IRR |             | A1                   | •     |   |   |   |   |   | 2      | 6                |

| IRET         | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |     |             | BF                   | *     | * | * | * | * | * | 1      | 5                |

| JP dst       | $PC \leftarrow dst$                                                                                               | DA  |             | 8D                   | _     | _ | _ | _ | _ | _ | 3      | 2                |

|              |                                                                                                                   | IRR |             | C4                   | •     |   |   |   |   |   | 2      | 3                |

| JP cc, dst   | if cc is true<br>PC $\leftarrow$ dst                                                                              | DA  |             | 0D-FD                | _     | - | - | - | - | - | 3      | 2                |

| JR dst       | $PC \leftarrow PC + X$                                                                                            | DA  |             | 8B                   | -     | - | _ | _ | _ | _ | 2      | 2                |

| JR cc, dst   | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA  |             | 0B-FB                | _     | - | _ | _ | _ | _ | 2      | 2                |

### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

ilog° Embedded in Life An∎IXYS Company

186

| Assembly      |                          | Address<br>Mode |      | _ Opcode(s) | Flags |   |   |   |   |   | _ Fetch | Instr. |

|---------------|--------------------------|-----------------|------|-------------|-------|---|---|---|---|---|---------|--------|

| Mnemonic      | Symbolic Operation       | dst             | src  | (Hex)       | С     | Ζ | S | ۷ | D | Н | Cycles  | Cycles |

| LD dst, rc    | $dst \leftarrow src$     | r               | IM   | 0C-FC       | -     | _ | - | - | - | _ | 2       | 2      |

|               |                          | r               | X(r) | C7          | -     |   |   |   |   |   | 3       | 3      |

|               |                          | X(r)            | r    | D7          | -     |   |   |   |   |   | 3       | 4      |

|               |                          | r               | lr   | E3          | -     |   |   |   |   |   | 2       | 3      |

|               |                          | R               | R    | E4          | -     |   |   |   |   |   | 3       | 2      |

|               |                          | R               | IR   | E5          | -     |   |   |   |   |   | 3       | 4      |

|               |                          | R               | IM   | E6          | -     |   |   |   |   |   | 3       | 2      |

|               |                          | IR              | IM   | E7          | -     |   |   |   |   |   | 3       | 3      |

|               |                          | lr              | r    | F3          | -     |   |   |   |   |   | 2       | 3      |

|               |                          | IR              | R    | F5          | -     |   |   |   |   |   | 3       | 3      |

| LDC dst, src  | $dst \gets src$          | r               | Irr  | C2          | -     | _ | _ | - | _ | - | 2       | 5      |

|               |                          | lr              | Irr  | C5          | -     |   |   |   |   |   | 2       | 9      |

|               |                          | Irr             | r    | D2          | -     |   |   |   |   |   | 2       | 5      |

| LDCI dst, src | $dst \gets src$          | lr              | Irr  | C3          | -     | _ | _ | _ | - | - | 2       | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr             | lr   | D3          | -     |   |   |   |   |   | 2       | 9      |

| LDE dst, src  | $dst \leftarrow src$     | r               | Irr  | 82          | -     | _ | _ | - | - | - | 2       | 5      |

|               |                          | Irr             | r    | 92          | -     |   |   |   |   |   | 2       | 5      |

| LDEI dst, src | dst $\leftarrow$ src     | lr              | Irr  | 83          | _     | _ | _ | - | - | _ | 2       | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr             | lr   | 93          | -     |   |   |   |   |   | 2       | 9      |

| LDWX dst, src | dst $\leftarrow$ src     | ER              | ER   | 1FE8        | _     | _ | _ | _ | _ | _ | 5       | 4      |

## Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

UARTx control 1 (UxCTL1) 113 UARTx receive data (UxRXD) 109 UARTx status 0 (UxSTAT0) 110 UARTx status 1 (UxSTAT1) 111 UARTx transmit data (UxTXD) 109 Watchdog Timer control (WDTCTL) 94, 133 watch-dog timer control (WDTCTL) 172 Watchdog Timer reload high byte (WDTH) 95 Watchdog Timer reload low byte (WDTL) 95 Watchdog Timer reload upper byte (WDTU) 95 register file 13 register pair 177 register pointer 177 reset and stop mode characteristics 21 and stop mode recovery 21 carry flag 179 sources 23 **RET 181** return 181 RL 181 **RLC 181** rotate and shift instructions 181 rotate left 181 rotate left through carry 181 rotate right 182 rotate right through carry 182 RP 177 RR 177, 182 rr 177 **RRC 182**

## S

SBC 179 SCF 179, 180 second opcode map after 1FH 195 set carry flag 179, 180 set register pointer 180 shift right arithmetic 182 shift right logical 182 signal descriptions 9 single-sho conversion (ADC) 123 software trap 181 source operand 177 SP 177 **SRA 182** src 177 **SRL 182 SRP 180** stack pointer 177 **STOP 180** STOP mode 30, 180 Stop Mode Recovery sources 26 using a GPIO port pin transition 27, 28 using Watchdog Timer time-out 27 **SUB 179** subtract 179 subtract - extended addressing 179 subtract with carry 179 subtract with carry - extended addressing 179 **SUBX 179 SWAP 182** swap nibbles 182 symbols, additional 177

## Т

**TCM 179 TCMX 179** test complement under mask 179 test complement under mask - extended addressing 179 test under mask 179 test under mask - extended addressing 179 timer signals 9 timers 69 architecture 70 block diagram 70 CAPTURE mode 78, 79, 89 CAPTURE/COMPARE mode 82, 89 COMPARE mode 80, 89 CONTINUOUS mode 71, 88 COUNTER mode 72, 73 **COUNTER modes 89** GATED mode 81, 89

part selection guide 2