# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423hh005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ilog<sup>®</sup>

ii

### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2011 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

#### ilog° Embedded in Life An∎IXYS Company 47

## Port A–C Pull-up Enable Subregisters

The Port A–C Pull-up Enable Subregister (Table 27) is accessed through the Port A–C Control Register by writing 06H to the Port A–C Address Register. Setting the bits in the Port A–C Pull-up Enable subregisters enables a weak internal resistive pull-up on the specified Port pins.

| Bit             | 7                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-----------------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Field           | PPUE7                                                                                 | PPUE6 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |

| RESET           | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W             | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address         | If 06H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |       |

| Bit Description |                                                                                       |       |       |       |       |       |       |       |

#### Table 27. Port A–C Pull-Up Enable Subregisters (PPUEx)

| BIt                                                        | Description                                       |  |  |  |  |

|------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| [7:0]                                                      | Port Pull-up Enabled                              |  |  |  |  |

| PPUEx                                                      | 0 = The weak pull-up on the Port pin is disabled. |  |  |  |  |

|                                                            | 1 = The weak pull-up on the Port pin is enabled.  |  |  |  |  |

| Note: x indicates the specific GPIO port pin number (7–0). |                                                   |  |  |  |  |

#### ilog Embedded in Life An∎IXYS Company 80

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture or a reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) = (Capture Value – Start Value) × Prescale System Clock Frequency (Hz)

### **COMPARE Mode**

In COMPARE Mode, the timer counts up to the 16-bit maximum compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting. Observe the following steps to configure a timer for COMPARE Mode and to initiate the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

## CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

## ILOG<sup>°</sup> Inbedded in Life

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

## Operation

The WDT is a retriggerable one-shot timer that resets or interrupts F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 59 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10kHz typical WDT oscillator frequency) |                        |  |  |

|------------------|------------------|-----------------------------------------------------------------------------|------------------------|--|--|

| (Hex)            | (Decimal)        | Typical                                                                     | Description            |  |  |

| 000004           | 4                | 400 μs                                                                      | Minimum time-out delay |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                                  | Maximum time-out delay |  |  |

#### Table 59. Watchdog Timer Approximate Time-Out Delays

nbedded in Life

101

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) performs the following:

1. Write the UART Control 1 Register to select the multiprocessor bit for the byte to be transmitted:

Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 3. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 4. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data Register to again become empty.

## **Receiving Data Using the Polled Method**

Observe the following steps to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set an acceptable baud rate for the incoming data stream.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable MULTIPROCESSOR Mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if Multiprocessor mode is not enabled, and select either even or odd parity

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to <u>Step 6</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

- 6. Read data from the UART Receive Data Register. If operating in MULTIPROCES-SOR (9-bit) Mode, further actions may be required depending on the MULTIPRO-CESSOR Mode bits MPMD[1:0].

# **Analog-to-Digital Converter**

The Analog-to-Digital Converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 10-bit resolution

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Bandgap generated internal voltage reference generator with two selectable levels

- Factory offset and gain calibration

# Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

> ILOG<sup>°</sup> Embedded in Life An IXYS Company 142

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|---|---|---|---|---|---|---|

| Field   | FCMD |   |   |   |   |   |   |   |

| RESET   | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W     | W    | W | W | W | W | W | W | W |

| Address | FF8H |   |   |   |   |   |   |   |

#### Table 81. Flash Control Register (FCTL)

Bit

Description

[7:0]

Flash Command

FCMD

73H = First unlock command.

8CH = Second unlock command.

95H = Page Erase command (must be third command in sequence to initiate Page Erase).

63H = Mass Erase command (must be third command in sequence to initiate Mass Erase).

5EH = Enable Flash Sector Protect Register Access.

ilog Embedded in Life An IXYS Company 172

## Table 105. Oscillator Control Register (OSCCTL)

| Bit             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                                                                                                                                       | 5               | 4            | 3            | 2            | 1           | 0   |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|--------------|--------------|-------------|-----|--|--|

| Field           | INTEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Reserved                                                                                                                                                                                | WDTEN           | POFEN        | WDFEN        |              | SCKSEL      |     |  |  |

| RESET           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                       | 1               | 0            | 0            | 0            | 0           | 0   |  |  |

| R/W             | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W                                                                                                                                                                                     | R/W             | R/W          | R/W          | R/W          | R/W         | R/W |  |  |

| Address         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                         |                 | F8           | 6H           |              |             |     |  |  |

| Bit             | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | n                                                                                                                                                                                       |                 |              |              |              |             |     |  |  |

| [7]<br>INTEN    | 1 = Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ecision Oso<br>precision os<br>precision os                                                                                                                                             | scillator is er | nabled.      |              |              |             |     |  |  |

| [6]             | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | eserved and                                                                                                                                                                             | must be pro     | ogrammed t   | o 0 during w | rites and to | 0 when read | 1.  |  |  |

| [5]<br>WDTEN    | 1 = Watchd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Watchdog Timer Oscillator Enable<br>1 = Watchdog Timer oscillator is enabled.<br>0 = Watchdog Timer oscillator is disabled.                                                             |                 |              |              |              |             |     |  |  |

| [4]<br>POFEN    | 1 = Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | scillator Fai<br>detection ar<br>detection ar                                                                                                                                           | d recovery      | of primary o |              |              |             |     |  |  |

| [3]<br>WDFEN    | 1 = Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Watchdog Timer Oscillator Failure Detection Enable<br>1 = Failure detection of Watchdog Timer oscillator is enabled.<br>0 = Failure detection of Watchdog Timer oscillator is disabled. |                 |              |              |              |             |     |  |  |

| [2:0]<br>SCKSEL | <ul> <li>0 = Failure detection of Watchdog Timer oscillator is disabled.</li> <li>System Clock Oscillator Select</li> <li>000 = Internal precision oscillator functions as system clock at 5.53 MHz.</li> <li>001 = Internal precision oscillator functions as system clock at 32kHz.</li> <li>010 = Reserved.</li> <li>011 = Watchdog Timer oscillator functions as system clock.</li> <li>100 = External clock signal on PB3 functions as system clock.</li> <li>101 = Reserved.</li> <li>110 = Reserved.</li> <li>111 = Reserved.</li> </ul> |                                                                                                                                                                                         |                 |              |              |              |             |     |  |  |

#### Table 110. Arithmetic Instructions (Continued)

| Operands | Instruction                                   |

|----------|-----------------------------------------------|

| dst      | Multiply                                      |

| dst, src | Subtract with Carry                           |

| dst, src | Subtract with Carry using Extended Addressing |

| dst, src | Subtract                                      |

| dst, src | Subtract using Extended Addressing            |

|          | dst<br>dst, src<br>dst, src<br>dst, src       |

#### Table 111. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                             |

|----------|-------------|---------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                               |

| BIT      | p, bit, dst | Bit Set or Clear                                        |

| BSET     | bit, dst    | Bit Set                                                 |

| BSWAP    | dst         | Bit Swap                                                |

| CCF      | —           | Complement Carry Flag                                   |

| RCF      | —           | Reset Carry Flag                                        |

| SCF      | —           | Set Carry Flag                                          |

| ТСМ      | dst, src    | Test Complement Under Mask                              |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended<br>Addressing |

| ТМ       | dst, src    | Test Under Mask                                         |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing               |

|          |             |                                                         |

#### Table 112. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

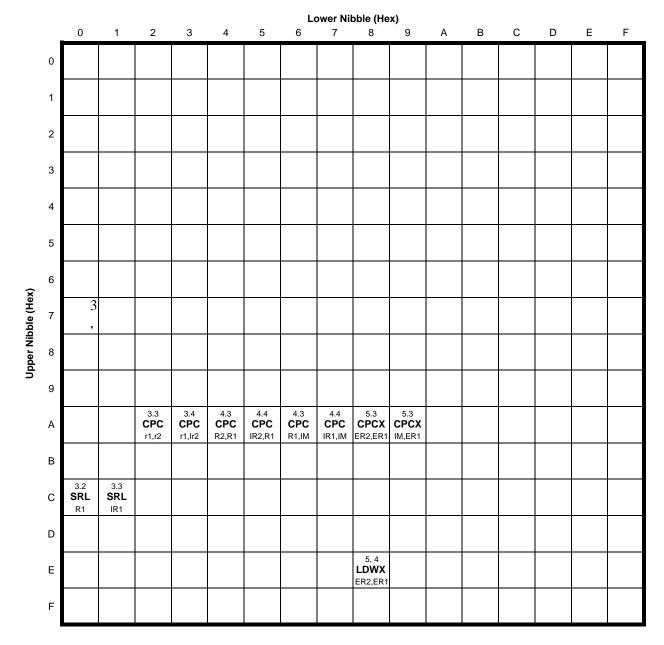

Figure 28. Second Opcode Map after 1FH

# Embedded in Life An IXYS Company 197

# **DC Characteristics**

Table 121 lists the DC characteristics of the Z8 Encore! XP F0823 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

|                  |                              |                     | -40°C to -<br>otherwise | ⊦105°C<br>specified) |       |                                                                                                                                                                |

|------------------|------------------------------|---------------------|-------------------------|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                    | Minimum             | Typical                 | Maximum              | Units | Conditions                                                                                                                                                     |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                       | 3.6                  | V     |                                                                                                                                                                |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -                       | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                                |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                       | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all sig-<br>nal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                       | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when pro-<br>grammable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | -                       | 0.4                  | V     | I <sub>OL</sub> = 2mA; V <sub>DD</sub> = 3.0V<br>High Output Drive disabled.                                                                                   |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | -                       | -                    | V     | $I_{OH} = -2mA; V_{DD} = 3.0V$<br>High Output Drive disabled.                                                                                                  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -                       | 0.6                  | V     | $I_{OL}$ = 20mA; $V_{DD}$ = 3.3 V<br>High Output Drive enabled.                                                                                                |

| V <sub>OH2</sub> | High Level Output<br>Voltage | 2.4                 | -                       | -                    | V     | I <sub>OH</sub> = -20mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                                 |

| I <sub>IH</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.002          | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>IL</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.007          | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>TL</sub>  | Tristate Leakage<br>Current  | -                   | -                       | <u>+</u> 5           | μA    |                                                                                                                                                                |

| Table 121. | DC | Characteristics |

|------------|----|-----------------|

|            |    | •               |

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

205

An∎IXYS Company

| Table 130. GPIO Port Input Timing |  |

|-----------------------------------|--|

|                                   |  |

|                     | Abbreviation                                                                                       | Delay (ns) |         |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|

| Parameter           |                                                                                                    | Minimum    | Maximum |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (Not pictured)                            | 5          | _       |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (Not pictured)                             | 0          | _       |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO Port Pins enabled as SMR sources) | 1 μs       |         |

edded in Life

An∎IXYS Company

207

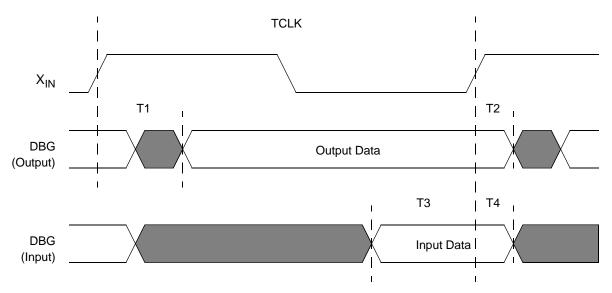

# **On-Chip Debugger Timing**

Figure 31 and Table 132 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

|                |                                              | Delay (ns) |         |

|----------------|----------------------------------------------|------------|---------|

| Parameter      | Abbreviation                                 | Minimum    | Maximum |

| DBG            |                                              |            |         |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | _          | 15      |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2          | -       |

| T <sub>3</sub> | DBG to X <sub>IN</sub> Rise Input Setup Time | 5          | _       |

| T <sub>4</sub> | DBG to X <sub>IN</sub> Rise Input Hold Time  | 5          | _       |

#### Table 132. On-Chip Debugger Timing

209

0g

■IXYS Company

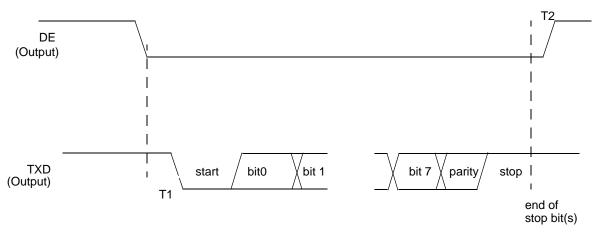

Figure 33 and Table 134 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

|                | Abbreviation                                                           | Delay (ns)                 |            |

|----------------|------------------------------------------------------------------------|----------------------------|------------|

| Parameter      |                                                                        | Minimum                    | Maximum    |

| UART           |                                                                        |                            |            |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5                        |            |

# Embedded in Life

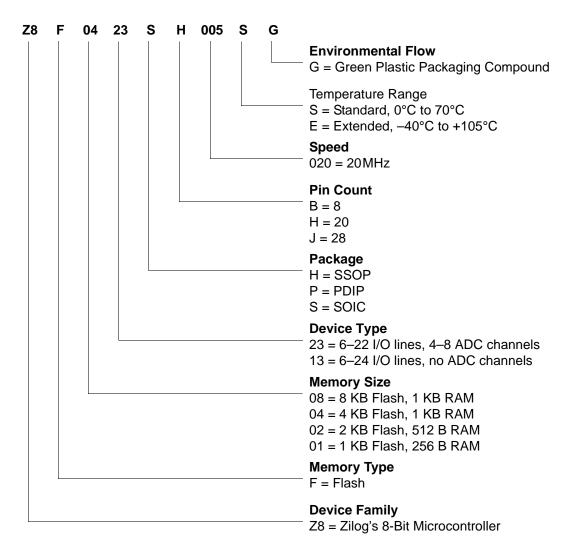

# Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0423SH005SG is an 8-bit 20MHz Flash MCU with 4KB of Program Memory and equipped with 6–22 I/O lines and 4–8 ADC channels in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

## G

GATED mode 89 general-purpose I/O 33 GPIO 4.33 alternate functions 34 architecture 34 control register definitions 40 input data sample timing 204 interrupts 40 port A-C pull-up enable sub-registers 47, 48, 49 port A-H address registers 41 port A-H alternate function sub-registers 43 port A-H control registers 42 port A-H data direction sub-registers 43 port A-H high drive enable sub-registers 45 port A-H input data registers 50 port A-H output control sub-registers 44 port A-H output data registers 51 port A-H stop mode recovery sub-registers 46 port availability by device 33 port input timing 205 port output timing 206

## Η

H 177 HALT 180 halt mode 31, 180 hexadecimal number prefix/suffix 177

## I

I2C 4 IM 176 immediate data 176 immediate operand prefix 177 INC 178 increment 178 increment word 178 INCW 178 indexed 177 indirect address prefix 177 indirect register 176 indirect register pair 176 indirect working register 176 indirect working register pair 176 infrared encoder/decoder (IrDA) 117 Instruction Set 174 instruction set, eZ8 CPU 174 instructions ADC 178 **ADCX 178** ADD 178 **ADDX 178** AND 181 **ANDX 181** arithmetic 178 **BCLR 179 BIT 179** bit manipulation 179 block transfer 179 **BRK 181 BSET 179** BSWAP 179, 181 BTJ 181 **BTJNZ 181 BTJZ 181 CALL 181** CCF 179, 180 **CLR 180** COM 181 CP 178 **CPC 178 CPCX 178** CPU control 180 **CPX 178** DA 178 **DEC 178 DECW 178** DI 180 DJNZ 181 EI 180 **HALT 180 INC 178 INCW 178 IRET 181** JP 181

225

LDEI 179, 180 LDX 180 LEA 180 load 180 load constant 179 load constant to/from program memory 180 load constant with auto-increment addresses 180 load effective address 180 load external data 180 load external data to/from data memory and autoincrement addresses 179 load external to/from data memory and auto-increment addresses 180 load instructions 180 load using extended addressing 180 logical AND 181 logical AND/extended addressing 181 logical exclusive OR 181 logical exclusive OR/extended addressing 181 logical instructions 181 logical OR 181 logical OR/extended addressing 181 low power modes 30

## Μ

master interrupt enable 56 memory data 15 program 13 mode CAPTURE 89 **CAPTURE/COMPARE 89 CONTINUOUS 88 COUNTER 89** GATED 89 **ONE-SHOT 88 PWM 89** modes 89 **MULT 179** multiply 179 MULTIPROCESSOR mode, UART 103

## Ν

NOP (no operation) 180 notation b 176 cc 176 DA 176 ER 176 IM 176 IR 176 Ir 176 **IRR 176** Irr 176 p 176 R 176 r 176 RA 177 RR 177 rr 177 vector 177 X 177 notational shorthand 176

# 0

OCD architecture 156 auto-baud detector/generator 159 baud rate limits 160 block diagram 156 breakpoints 161 commands 162 control register 166 data format 159 DBG pin to RS-232 Interface 157 DEBUG mode 158 debugger break 181 interface 157 serial errors 160 status register 168 timing 207 **OCD** commands execute instruction (12H) 166 read data memory (0DH) 165 read OCD control register (05H) 163

nbedded in Life

read OCD revision (00H) 163 read OCD status register (02H) 163 read program counter (07H) 164 read program memory (0BH) 164 read program memory CRC (0EH) 165 read register (09H) 164 read runtime counter (03H) 163 step instruction (10H) 165 stuff instruction (11H) 166 write data memory (0CH) 165 write OCD control register (04H) 163 write program counter (06H) 163 write program memory (0AH) 164 write register (08H) 164 on-chip debugger (OCD) 156 on-chip debugger signals 10 ONE-SHOT mode 88 opcode map abbreviations 193 cell description 192 first 194 second after 1FH 195 Operational Description 21, 30, 33, 69, 91, 97, 117, 121, 132, 134, 146, 156, 169, 173 OR 181 ordering information 211 **ORX 181**

## Ρ

p 176 Packaging 210 part selection guide 2 PC 177 peripheral AC and DC electrical characteristics 201 pin characteristics 11 Pin Descriptions 7 polarity 176 POP 180 pop using extended addressing 180 POPX 180 port availability, device 33 port input timing (GPIO) 205 port output timing, GPIO 206 power supply signals 10

Power-on and Voltage Brownout electrical characteristics and timing 201

Power-On Reset (POR) 23

program control instructions 181

program counter 177

program memory 13

PUSH 180

push using extended addressing 180

PUSHX 180

PWM mode 89

PxADDR register 41

PxCTL register 42

# R

R 176 r 176 RA register address 177 RCF 179. 180 receive IrDA data 119 receiving UART data-interrupt-driven method 102 receiving UART data-polled method 101 register 176 ADC control (ADCCTL) 126, 129 ADC data high byte (ADCDH) 130 ADC data low bits (ADCDL) 131 flash control (FCTL) 141, 148, 149 flash high and low byte (FFREQH and FRE-EQL) 144 flash page select (FPS) 142, 144 flash status (FSTAT) 142 GPIO port A-H address (PxADDR) 41 GPIO port A-H alternate function sub-registers 44 GPIO port A-H control address (PxCTL) 42 GPIO port A-H data direction sub-registers 43 OCD control 166 OCD status 168 UARTx baud rate high byte (UxBRH) 115 UARTx baud rate low byte (UxBRL) 115 UARTx Control 0 (UxCTL0) 112, 115

part selection guide 2