Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 5MHz                                                      |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 6                                                         |  |

| Program Memory Size        | 4KB (4K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 1K x 8                                                    |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | A/D 4x10b                                                 |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |

| Mounting Type              | Through Hole                                              |  |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423pb005sg |  |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

νi

| Interrupt Assertion                                      | . 57 |

|----------------------------------------------------------|------|

| Software Interrupt Assertion                             | . 58 |

| Watchdog Timer Interrupt Assertion                       | . 58 |

| Interrupt Control Register Definitions                   | . 59 |

| Interrupt Request 0 Register                             | . 59 |

| Interrupt Request 1 Register                             | . 60 |

| Interrupt Request 2 Register                             | . 61 |

| IRQ0 Enable High and Low Bit Registers                   | . 61 |

| IRQ1 Enable High and Low Bit Registers                   | . 63 |

| IRQ2 Enable High and Low Bit Registers                   | . 65 |

| Interrupt Edge Select Register                           | . 66 |

| Shared Interrupt Select Register                         | . 67 |

| Interrupt Control Register                               | . 68 |

| Timers                                                   | 69   |

| Architecture                                             |      |

| Operation                                                |      |

| Timer Operating Modes                                    |      |

| Reading the Timer Count Values                           |      |

| Timer Pin Signal Operation                               |      |

| Timer Control Register Definitions                       |      |

| Timer 0–1 High and Low Byte Registers                    |      |

| Timer Reload High and Low Byte Registers                 |      |

| Timer 0–1 PWM High and Low Byte Registers                |      |

| Timer 0–1 Control Registers                              |      |

| <u> </u>                                                 |      |

| Watchdog Timer                                           |      |

| Operation                                                |      |

| Watchdog Timer Refresh                                   |      |

| Watchdog Timer Time-Out Response                         |      |

| Watchdog Timer Reload Unlock Sequence                    |      |

| Watchdog Timer Control Register Definitions              |      |

| Watchdog Timer Control Register                          |      |

| Watchdog Timer Reload Upper, High and Low Byte Registers | . 94 |

| Universal Asynchronous Receiver/Transmitter              | . 97 |

| Architecture                                             | . 97 |

| Operation                                                | . 98 |

| Transmitting Data Using the Polled Method                | . 99 |

| Transmitting Data Using the Interrupt-Driven Method      | 100  |

| Receiving Data Using the Polled Method                   | 101  |

| Receiving Data Using the Interrupt-Driven Method         |      |

| Clear To Send (CTS) Operation                            |      |

| •                                                        |      |

# Address Space

The eZ8 CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O Port Control Registers

- The Program Memory contains addresses for all memory locations having executable code and/or data

- The Data Memory contains addresses for all memory locations that contain data only

These three address spaces are covered briefly in the following subsections. For more detailed information regarding the eZ8 CPU and its address space, refer to the eZ8 CPU Core User Manual (UM0128), available for download at www.zilog.com.

# **Register File**

The Register File address space in the Z8 Encore! XP<sup>TM</sup> MCU is 4KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address <code>000H</code> in the Register File address space. Z8 Encore! XP F0823 Series devices contain 256B–1KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

# **Program Memory**

The eZ8 CPU supports 64KB of Program Memory address space. F0823 Series devices contain 1KB to 8KB of on-chip Flash memory in the Program Memory address space. Reading from Program Memory addresses outside the available Flash memory addresses

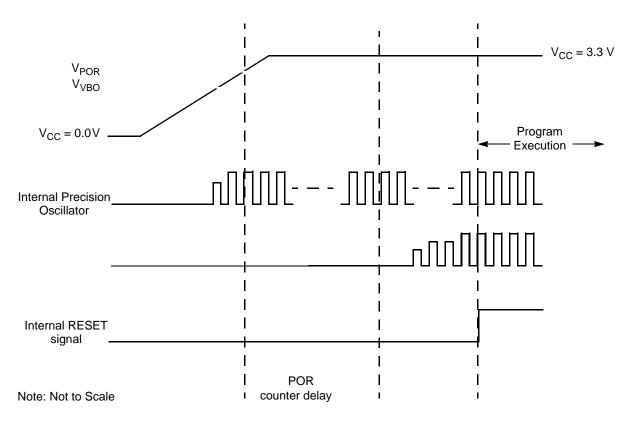

Figure 5. Power-On Reset Operation

### Voltage Brown-Out Reset

The devices in the Z8 Encore! XP F0823 Series provide low VBO protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO threshold voltage) and forces the device into the Reset state. While the supply voltage remains below the POR voltage threshold  $(V_{POR})$ , the VBO block holds the device in the Reset.

After the supply voltage again exceeds the Power-On Reset voltage threshold, the device progresses through a full System Reset sequence, as described in the <u>Power-On Reset</u> section on page 23. Following POR, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 6 displays Voltage Brown-Out operation. For the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ), see the <u>Electrical Characteristics</u> chapter on page 196.

The VBO circuit can be either enabled or disabled during STOP Mode. Operation during STOP Mode is set by the VBO\_AO Flash Option bit. For information about configuring VBO AO, see the Flash Option Bits chapter on page 146.

Table 35. Trap and Interrupt Vectors in Order of Priority

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

|          | 0004H                               | Watchdog Timer (see the Watchdog Timer section on page 91)                 |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          | 0036H                               | Port C Pin 0, both input edges                                             |

| owest    | 0038H                               | Reserved                                                                   |

### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 38) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

Table 38. Interrupt Request 2 Register (IRQ2)

| Bit     | 7        | 6    | 5   | 4   | 3    | 2    | 1    | 0    |

|---------|----------|------|-----|-----|------|------|------|------|

| Field   | Reserved |      |     |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0        | 0    | 0   | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W      | R/W  | R/W | R/W | R/W  | R/W  | R/W  | R/W  |

| Address |          | FC6H |     |     |      |      |      |      |

| Bit   | Description                                                          |  |

|-------|----------------------------------------------------------------------|--|

| [7:4] | Reserved                                                             |  |

|       | These bits are reserved and must be programmed to 0000.              |  |

| [3:0] | Port C Pin x Interrupt Request                                       |  |

| PCxI  | 0 = No interrupt request is pending for GPIO Port C pin x.           |  |

|       | 1 = An interrupt request from GPIO Port C pin x is awaiting service. |  |

| Note: | x indicates the specific GPIO Port C pin number (3–0).               |  |

# IRQ0 Enable High and Low Bit Registers

Table 39 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 40 and Table 41) form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register. Priority is generated by setting bits in each register.

Table 39. IRQ0 Enable and Priority Encoding

| IRQ0ENL[x] | Priority         | Description                    |

|------------|------------------|--------------------------------|

| 0          | Disabled         | Disabled                       |

| 1          | Level 1          | Low                            |

| 0          | Level 2          | Nominal                        |

| 1          | Level 3          | High                           |

|            | 0<br>1<br>0<br>1 | 0 Disabled 1 Level 1 0 Level 2 |

Note: where *x* indicates the register bits from 0–7.

PWM Period (s) =

$$\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period. If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =

$$\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =

$$\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$$

#### **PWM Dual Output Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a PWM output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Observe the following steps to configure a timer for PWM DUAL OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode. Setting the mode also involves writing to the TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H); this write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM dead band delay value. The dead-band delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) =

$$\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

| Bit                      | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6]<br>TPOL<br>(cont'd.) | COMPARATOR COUNTER Mode When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer reload.                                                                                                                                                                                                                                                                              |

|                          | <b>Caution:</b> When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, TxOUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.                                                                              |

| [5:3]<br>PRES            | Prescale Value The timer input clock is divided by 2 <sup>PRES</sup> , where PRES can be set from 0 to 7. The prescaler is reset each time the timer is disabled. This reset ensures proper clock division each time the timer is restarted.  000 = Divide by 1.  001 = Divide by 2.  010 = Divide by 4.  011 = Divide by 8.  100 = Divide by 16.  101 = Divide by 32.  110 = Divide by 64.  111 = Divide by 128.                                                               |

| [2:0]<br>TMODE           | Timer Mode This field, along with the TMODEHI bit in TxCTL0 Register, determines the operating mode of the timer. TMODEHI is the most significant bit of the timer mode selection value.  0000 = ONE-SHOT Mode. 0001 = CONTINUOUS Mode. 0010 = COUNTER Mode. 0011 = PWM SINGLE OUTPUT Mode. 0100 = CAPTURE Mode. 0101 = COMPARE Mode. 0110 = GATED Mode. 0111 = CAPTURE/COMPARE Mode. 1000 = PWM DUAL OUTPUT Mode. 1001 = CAPTURE RESTART Mode. 1010 = COMPARATOR COUNTER Mode. |

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <a href="Step 7">Step 7</a>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled,.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

#### Transmitting Data Using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's baud rate generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =

$$\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$$

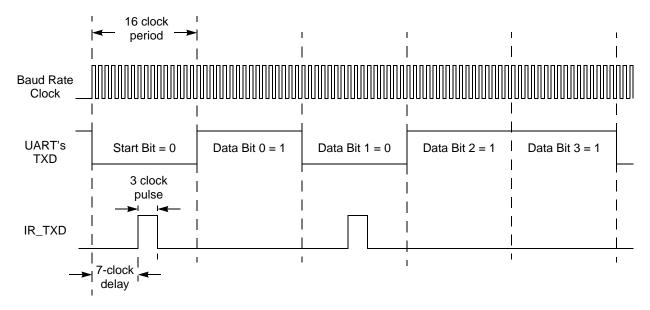

#### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the infrared endec is enabled, the UART's TXD signal is internal to Z8 Encore! XP F0823 Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

#### **Serialization Data**

Table 96. Serial Number at 001C-001F (S\_NUM)

| Bit       | 7                                            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field     |                                              |     |     | S_N | IUM |     |     |     |

| RESET     | U                                            | U   | U   | U   | U   | U   | U   | U   |

| R/W       | R/W                                          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address   | Information Page Memory 001C-001F            |     |     |     |     |     |     |     |

| Note: U = | e: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |

| Bit   | Description                                                         |

|-------|---------------------------------------------------------------------|

| [7:0] | Serial Number Byte                                                  |

| S_NUM | The serial number is a unique four-byte binary value; see Table 97. |

**Table 97. Serialization Data Locations**

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

#### **Randomized Lot Identifier**

Table 98. Lot Identification Number (RAND\_LOT)

| Bit       | 7                                               | 6   | 5   | 4    | 3    | 2   | 1   | 0   |

|-----------|-------------------------------------------------|-----|-----|------|------|-----|-----|-----|

| Field     |                                                 |     |     | RAND | _LOT |     |     |     |

| RESET     | U                                               | U   | U   | U    | U    | U   | U   | U   |

| R/W       | R/W                                             | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Address   | Interspersed throughout Information Page Memory |     |     |      |      |     |     |     |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |      |      |     |     |     |

| Bit      | Description                                                                                         |

|----------|-----------------------------------------------------------------------------------------------------|

| [7]      | Randomized Lot ID                                                                                   |

| RAND_LOT | The randomized lot ID is a 32-byte binary value that changes for each production lot; see Table 99. |

**Table 99. Randomized Lot ID Locations**

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 3C                   | FE3C              | Randomized Lot ID Byte 31 (most significant) |

| 3D                   | FE3D              | Randomized Lot ID Byte 30                    |

| 3E                   | FE3E              | Randomized Lot ID Byte 29                    |

| 3F                   | FE3F              | Randomized Lot ID Byte 28                    |

| 58                   | FE58              | Randomized Lot ID Byte 27                    |

| 59                   | FE59              | Randomized Lot ID Byte 26                    |

| 5A                   | FE5A              | Randomized Lot ID Byte 25                    |

| 5B                   | FE5B              | Randomized Lot ID Byte 24                    |

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

# **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of Z8 Encore! XP F0823 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 101 is a summary of the OCD commands. Each OCD command is described in further detail in the pages that follow this table. <u>Table 102</u> on page 167 also indicates those commands that operate when the device is not in DEBUG Mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

**Table 101. OCD Commands**

| Debug Command              | Command<br>Byte | Enabled when not in DEBUG Mode? | Disabled by Flash Read Protect Option Bit                                                                                                                        |

|----------------------------|-----------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                             | -                                                                                                                                                                |

| Reserved                   | 01H             | _                               | _                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                             | _                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                               | _                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                             | Cannot clear DBGMODE bit.                                                                                                                                        |

| Read OCD Control Register  | 05H             | Yes                             | _                                                                                                                                                                |

| Write Program Counter      | 06H             | _                               | Disabled.                                                                                                                                                        |

| Read Program Counter       | 07H             | _                               | Disabled.                                                                                                                                                        |

| Write Register             | 08H             | -                               | Only writes of the Flash Memory Control registers are allowed. Additionally, only the Mass Erase command is allowed to be written to the Flash Control Register. |

| Read Register              | 09H             | _                               | Disabled.                                                                                                                                                        |

| Write Program Memory       | 0AH             | -                               | Disabled.                                                                                                                                                        |

| Read Program Memory        | 0BH             | _                               | Disabled.                                                                                                                                                        |

| Write Data Memory          | 0CH             | _                               | Yes.                                                                                                                                                             |

| Read Data Memory           | 0DH             | -                               | _                                                                                                                                                                |

| Read Program Memory CRC    | 0EH             | _                               | _                                                                                                                                                                |

| Reserved                   | 0FH             | _                               | _                                                                                                                                                                |

| Step Instruction           | 10H             | _                               | Disabled.                                                                                                                                                        |

| Stuff Instruction          | 11H             |                                 | Disabled.                                                                                                                                                        |

| Execute Instruction        | 12H             | _                               | Disabled.                                                                                                                                                        |

| Reserved                   | 13H-FFH         | _                               | _                                                                                                                                                                |

Stuff Instruction (11H). The Stuff command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0–4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG ← 11H

DBG \leftarrow opcode[7:0]

```

**Execute Instruction (12H).** The Execute command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

```

DBG ← 12H

DBG ← 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

### OCD Control Register

The OCD Control Register controls the state of the OCD. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It also resets Z8 Encore! XP F0823 Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

Table 118. eZ8 CPU Instruction Summary (Continued)

| Assembly        |                                     |       | ress<br>ode | _ Opcode(s) |   |   | Fla | ags     | _ Fetch | Instr. |        |   |

|-----------------|-------------------------------------|-------|-------------|-------------|---|---|-----|---------|---------|--------|--------|---|

| Mnemonic        | Symbolic Operation                  | dst   | src         | (Hex)       |   | Z | S   | S V D H |         |        | Cycles |   |

| LDX dst, src    | dst ← src                           | r     | ER          | 84          | - | _ | _   | -       | _       | _      | 3      | 2 |

|                 |                                     | Ir    | ER          | 85          |   |   |     |         |         |        | 3      | 3 |

|                 |                                     | R     | IRR         | 86          |   |   |     |         |         |        | 3      | 4 |

|                 |                                     | IR    | IRR         | 87          |   |   |     |         |         |        | 3      | 5 |

|                 |                                     | r     | X(rr)       | 88          | • |   |     |         |         |        | 3      | 4 |

|                 |                                     | X(rr) | r           | 89          | • |   |     |         |         |        | 3      | 4 |

|                 |                                     | ER    | r           | 94          | • |   |     |         |         |        | 3      | 2 |

|                 |                                     | ER    | lr          | 95          | • |   |     |         |         |        | 3      | 3 |

|                 |                                     | IRR   | R           | 96          | • |   |     |         |         |        | 3      | 4 |

|                 |                                     | IRR   | IR          | 97          | • |   |     |         |         |        | 3      | 5 |

|                 |                                     | ER    | ER          | E8          | • |   |     |         |         |        | 4      | 2 |

|                 |                                     | ER    | IM          | E9          | • |   |     |         |         |        | 4      | 2 |

| LEA dst, X(src) | $dst \leftarrow src + X$            | r     | X(r)        | 98          | _ | _ | _   | -       | _       | -      | 3      | 3 |

|                 |                                     | rr    | X(rr)       | 99          |   |   |     |         |         |        | 3      | 5 |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR    |             | F4          | - | - | -   | -       | -       | -      | 2      | 8 |

| NOP             | No operation                        |       |             | 0F          | _ | _ | _   | -       | _       | -      | 1      | 2 |

| OR dst, src     | $dst \leftarrow dst \; OR \; src$   | r     | r           | 42          | - | * | *   | 0       | -       | -      | 2      | 3 |

|                 |                                     | r     | lr          | 43          |   |   |     |         |         |        | 2      | 4 |

|                 |                                     | R     | R           | 44          | _ |   |     |         |         |        | 3      | 3 |

|                 |                                     | R     | IR          | 45          | _ |   |     |         |         |        | 3      | 4 |

|                 |                                     | R     | IM          | 46          |   |   |     |         |         |        | 3      | 3 |

|                 |                                     | IR    | IM          | 47          |   |   |     |         |         |        | 3      | 4 |

| ORX dst, src    | $dst \leftarrow dst \; OR \; src$   | ER    | ER          | 48          | _ | * | *   | 0       | -       | -      | 4      | 3 |

|                 |                                     | ER    | IM          | 49          |   |   |     |         |         |        | 4      | 3 |

| POP dst         | dst ← @SP                           | R     |             | 50          | - | - | -   | -       | _       | _      | 2      | 2 |

|                 | SP ← SP + 1                         | IR    |             | 51          |   |   |     |         |         |        | 2      | 3 |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Table 118. eZ8 CPU Instruction Summary (Continued)

| Assembly  |                           |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|-----------|---------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic  | Symbolic Operation        | dst | src         | (Hex)       |   | Z | S   | ٧   | D | Н | Cycles  |        |

| POPX dst  | dst ← @SP<br>SP ← SP + 1  | ER  |             | D8          | _ | - | _   | -   | - | - | 3       | 2      |

| PUSH src  | SP ← SP – 1               | R   |             | 70          | - | - | -   | -   | - | - | 2       | 2      |

|           | @SP ← src                 | IR  |             | 71          | • |   |     |     |   |   | 2       | 3      |

|           |                           | IM  |             | IF70        |   |   |     |     |   |   | 3       | 2      |

| PUSHX src | SP ← SP − 1<br>@SP ← src  | ER  |             | C8          | _ | _ | _   | _   | _ | _ | 3       | 2      |

| RCF       | C ← 0                     |     |             | CF          | 0 | _ | _   | _   | _ | _ | 1       | 2      |

| RET       | PC ← @SP<br>SP ← SP + 2   |     |             | AF          | - | - | -   | -   | - | - | 1       | 4      |

| RL dst    |                           | R   |             | 90          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 91          | - |   |     |     |   |   | 2       | 3      |

| RLC dst   | <u> </u>                  | R   |             | 10          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 11          | - |   |     |     |   |   | 2       | 3      |

| RR dst    |                           | R   |             | E0          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  |             | E1          | - |   |     |     |   |   | 2       | 3      |

| RRC dst   |                           | R   |             | C0          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  |             | C1          | • |   |     |     |   |   | 2       | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

|                    |   |                          |                          |                              |                              |                             |                             | Lo                         | ower Nil                    | bble (He                      | x)                    |                            |                          |                           |                           |                         |                          |

|--------------------|---|--------------------------|--------------------------|------------------------------|------------------------------|-----------------------------|-----------------------------|----------------------------|-----------------------------|-------------------------------|-----------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|--------------------------|

|                    |   | 0                        | 1                        | 2                            | 3                            | 4                           | 5                           | 6                          | 7                           | 8                             | 9                     | Α                          | В                        | С                         | D                         | Е                       | F                        |

|                    | 0 | 1.1<br>BRK               | 2.2<br><b>SRP</b><br>IM  | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br><b>ADD</b><br>r1,lr2  | 3.3<br><b>ADD</b><br>R2,R1  | 3.4<br><b>ADD</b><br>IR2,R1 | 3.3<br><b>ADD</b><br>R1,IM | 3.4<br><b>ADD</b><br>IR1,IM | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1 | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br><b>NOP</b>        |

|                    | 1 | 2.2<br><b>RLC</b><br>R1  | 2.3<br><b>RLC</b><br>IR1 | 2.3<br><b>ADC</b><br>r1,r2   | 2.4<br><b>ADC</b><br>r1,lr2  | 3.3<br><b>ADC</b><br>R2,R1  | 3.4<br><b>ADC</b><br>IR2,R1 | 3.3<br><b>ADC</b><br>R1,IM | 3.4<br><b>ADC</b><br>IR1,IM | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1 |                            |                          |                           |                           |                         | See 2nd<br>Opcode<br>Map |

|                    | 2 | 2.2<br><b>INC</b><br>R1  | 2.3<br><b>INC</b><br>IR1 | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br><b>SUB</b><br>r1,lr2  | 3.3<br><b>SUB</b><br>R2,R1  | 3.4<br><b>SUB</b><br>IR2,R1 | 3.3<br><b>SUB</b><br>R1,IM | 3.4<br><b>SUB</b><br>IR1,IM | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br>SUBX<br>IM,ER1 |                            |                          |                           |                           |                         | 1                        |

|                    | 3 | 2.2<br><b>DEC</b><br>R1  | 2.3<br><b>DEC</b><br>IR1 | 2.3<br><b>SBC</b><br>r1,r2   | 2.4<br><b>SBC</b><br>r1,lr2  | 3.3<br><b>SBC</b><br>R2,R1  | 3.4<br><b>SBC</b><br>IR2,R1 | 3.3<br><b>SBC</b><br>R1,IM | 3.4<br>SBC<br>IR1,IM        | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br>SBCX<br>IM,ER1 |                            |                          |                           |                           |                         |                          |

|                    | 4 | 2.2<br><b>DA</b>         | 2.3<br><b>DA</b>         | 2.3<br><b>OR</b>             | 2.4<br><b>OR</b>             | 3.3<br><b>OR</b>            | 3.4<br><b>OR</b>            | 3.3<br><b>OR</b>           | 3.4<br><b>OR</b>            | 4.3<br><b>ORX</b>             | 4.3<br><b>ORX</b>     |                            |                          |                           |                           |                         |                          |

|                    | 5 | 2.2<br><b>POP</b>        | 2.3<br><b>POP</b>        | 2.3<br>AND                   | 2.4<br><b>AND</b>            | 3.3<br><b>AND</b>           | 3.4<br><b>AND</b>           | 3.3<br><b>AND</b>          | 3.4<br><b>AND</b>           | 4.3<br><b>ANDX</b>            | 4.3<br>ANDX           |                            |                          |                           |                           |                         | 1.2<br><b>WDT</b>        |

|                    | 6 | 2.2<br>COM               | 2.3<br><b>COM</b>        | 2.3<br><b>TCM</b>            | 2.4<br><b>TCM</b>            | 3.3<br><b>TCM</b>           | 3.4<br><b>TCM</b>           | 3.3<br><b>TCM</b>          | 3.4<br><b>TCM</b>           | 4.3<br>TCMX                   | 4.3<br><b>TCMX</b>    |                            |                          |                           |                           |                         | 1.2<br><b>STOP</b>       |

| Upper Nibble (Hex) | 7 | 2.2<br><b>PUSH</b>       | 2.3<br><b>PUSH</b>       | 2.3<br><b>TM</b>             | r1,lr2<br>2.4<br><b>TM</b>   | 3.3<br><b>TM</b>            | 3.4<br><b>TM</b>            | 3.3<br><b>TM</b>           | 3.4<br><b>TM</b>            | 4.3<br><b>TMX</b>             | 4.3<br><b>TMX</b>     |                            |                          |                           |                           |                         | 1.2<br><b>HALT</b>       |

| er Nibb            | 8 | 2.5<br><b>DECW</b>       | 2.6<br><b>DECW</b>       | 2.5<br><b>LDE</b>            | r1,lr2<br>2.9<br><b>LDEI</b> | 3.2<br><b>LDX</b>           | 3.3<br><b>LDX</b>           | 3.4<br><b>LDX</b>          | 3.5<br><b>LDX</b>           | 3.4<br><b>LDX</b>             | 3.4<br><b>LDX</b>     |                            |                          |                           |                           |                         | 1.2<br><b>DI</b>         |

| Opp                | 9 | 2.2<br><b>RL</b>         | 2.3<br><b>RL</b>         | 2.5<br><b>LDE</b>            | 2.9<br>LDEI                  | 3.2<br><b>LDX</b>           | 3.3<br><b>LDX</b>           | 3.4<br><b>LDX</b>          | 3.5<br><b>LDX</b>           | 3.3<br><b>LEA</b>             | 3.5<br><b>LEA</b>     |                            |                          |                           |                           |                         | 1.2<br><b>El</b>         |

|                    | Α | 2.5<br>INCW              | 2.6<br>INCW              | 2.3<br><b>CP</b>             | 2.4<br><b>CP</b>             | 3.3<br><b>CP</b>            | 3.4<br><b>CP</b>            | 3.3<br><b>CP</b>           | 3.4<br><b>CP</b>            | r1,r2,X<br>4.3<br><b>CPX</b>  | 4.3<br><b>CPX</b>     |                            |                          |                           |                           |                         | 1.4<br><b>RET</b>        |

|                    | В | 2.2<br><b>CLR</b>        | 2.3<br><b>CLR</b>        | r1,r2<br>2.3<br><b>XOR</b>   | r1,lr2<br>2.4<br><b>XOR</b>  | 3.3<br><b>XOR</b>           | 3.4<br><b>XOR</b>           | 3.3<br><b>XOR</b>          | 3.4<br><b>XOR</b>           | 4.3<br><b>XORX</b>            | 4.3<br>XORX           |                            |                          |                           |                           |                         | 1.5<br>IRET              |

|                    | С | 2.2<br><b>RRC</b>        | 2.3<br><b>RRC</b>        | r1,r2<br>2.5<br><b>LDC</b>   | r1,lr2<br>2.9<br><b>LDCI</b> | 2.3<br><b>JP</b>            | 2.9<br><b>LDC</b>           | R1,IM                      | 3.4<br><b>LD</b>            | 3.2<br>PUSHX                  | IM,ER1                |                            |                          |                           |                           |                         | 1.2<br><b>RCF</b>        |

|                    | D | 2.2<br><b>SRA</b>        | 2.3<br><b>SRA</b>        | 2.5<br><b>LDC</b>            | 2.9<br><b>LDCI</b>           | 2.6<br>CALL                 | lr1,lrr2<br>2.2<br>BSWAP    | 3.3<br>CALL                | r1,r2,X<br>3.4<br><b>LD</b> | 3.2<br><b>POPX</b>            |                       |                            |                          |                           |                           |                         | 1.2<br><b>SCF</b>        |

|                    | E | 2.2<br><b>RR</b>         | 2.3<br><b>RR</b>         | r2,Irr1<br>2.2<br><b>BIT</b> | 2.3<br><b>LD</b>             | 3.2<br><b>LD</b>            | R1<br>3.3<br><b>LD</b>      | 3.2<br><b>LD</b>           | r2,r1,X<br>3.3<br><b>LD</b> | 4.2<br><b>LDX</b>             | 4.2<br><b>LDX</b>     |                            |                          |                           |                           |                         | 1.2<br><b>CCF</b>        |

|                    | F | R1<br>2.2<br><b>SWAP</b> | 2.3<br><b>SWAP</b>       | p,b,r1<br>2.6<br><b>TRAP</b> | r1,lr2<br>2.3<br><b>LD</b>   | R2,R1<br>2.8<br><b>MULT</b> | 3.3<br><b>LD</b>            | 3.3<br><b>BTJ</b>          | 3.4<br><b>BTJ</b>           | ER2,ER1                       | IM,ER1                |                            |                          |                           |                           |                         |                          |

|                    | ٢ | R1                       | IR1                      | Vector                       | Ir1,r2                       | RR1                         | R2,IR1                      |                            | p,b,lr1,X                   |                               |                       | <b>V</b>                   | <b>V</b>                 | <b>V</b>                  | <b>V</b>                  | ▼                       |                          |

Figure 27. First Opcode Map

# On-Chip Peripheral AC and DC Electrical Characteristics

Table 125 tabulates the electrical characteristics of the POR and VBO blocks.

Table 125. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                   |                                                                                  | $T_A = $ | –40°C to +      |         |       |                                                                                                               |

|-------------------|----------------------------------------------------------------------------------|----------|-----------------|---------|-------|---------------------------------------------------------------------------------------------------------------|

| Symbol            | Parameter                                                                        | Minimum  | Typical*        | Maximum | Units | Conditions                                                                                                    |

| V <sub>POR</sub>  | Power-On Reset Voltage<br>Threshold                                              | 2.20     | 2.45            | 2.70    | V     | $V_{DD} = V_{POR}$                                                                                            |

| $V_{VBO}$         | Voltage Brown-Out Reset Voltage Threshold                                        | 2.15     | 2.40            | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                            |

|                   | V <sub>POR</sub> to V <sub>VBO</sub> hysteresis                                  |          | 50              | 75      | mV    |                                                                                                               |

|                   | Starting V <sub>DD</sub> voltage to ensure valid Power-On Reset.                 | -        | V <sub>SS</sub> | _       | V     |                                                                                                               |

| T <sub>ANA</sub>  | Power-On Reset Analog Delay                                                      | -        | 70              | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ;<br>T <sub>POR</sub> Digital<br>Reset delay fol-<br>lows T <sub>ANA</sub> |

| T <sub>POR</sub>  | Power-On Reset Digital Delay                                                     |          | 16              |         | μs    | 66 Internal Precision Oscillator cycles + IPO startup time (T <sub>IPOST</sub> )                              |

| T <sub>SMR</sub>  | Stop Mode Recovery                                                               |          | 16              |         | μs    | 66 Internal Precision Oscillator cycles                                                                       |

| T <sub>VBO</sub>  | Voltage Brown-Out Pulse<br>Rejection Period                                      | -        | 10              | -       | μs    | Period of time in which V <sub>DD</sub> < V <sub>VBO</sub> without generating a Reset.                        |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to transition from $V_{SS}$ to $V_{POR}$ to ensure valid Reset | 0.10     | -               | 100     | ms    |                                                                                                               |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                    |          | 20              |         | ns    | For any SMR pin or for the Reset pin when it is asserted in STOP Mode.                                        |

Note: \*Data in the typical column is from characterization at 3.3 V and 30°C. These values are provided for design guidance only and are not tested in production.

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

| Part Number                       | Flash<br>RAM    | VO Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |  |  |  |

|-----------------------------------|-----------------|----------|------------|------------------------|---------------------|----------------|---------------------|--|--|--|--|--|

| Z8 Encore! XP F0823               | Series with 1   | KB FI    | ash        |                        |                     |                |                     |  |  |  |  |  |

| Standard Temperature: 0°C to 70°C |                 |          |            |                        |                     |                |                     |  |  |  |  |  |

| Z8F0113PB005SG                    | 1 KB 256 B      | 6        | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |  |  |  |

| Z8F0113QB005SG                    | 1 KB 256 B      | 6        | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |  |  |  |

| Z8F0113SB005SG                    | 1 KB 256 B      | 6        | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |  |  |  |

| Z8F0113SH005SG                    | 1 KB 256 B      | 16       | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |  |  |  |

| Z8F0113HH005SG                    | 1 KB 256 B      | 16       | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |  |  |  |

| Z8F0113PH005SG                    | 1 KB 256 B      | 16       | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |  |  |  |

| Z8F0113SJ005SG                    | 1 KB 256 B      | 24       | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |  |  |  |

| Z8F0113HJ005SG                    | 1 KB 256 B      | 24       | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |  |  |  |

| Z8F0113PJ005SG                    | 1 KB 256 B      | 24       | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |  |  |  |

| Extended Temperatu                | ure: -40°C to 1 | 05°C     |            |                        |                     |                |                     |  |  |  |  |  |

| Z8F0113PB005EG                    | 1 KB 256 B      | 6        | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |  |  |  |

| Z8F0113QB005EG                    | 1 KB 256 B      | 6        | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |  |  |  |

| Z8F0113SB005EG                    | 1 KB 256 B      | 6        | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |  |  |  |

| Z8F0113SH005EG                    | 1 KB 256 B      | 16       | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |  |  |  |

| Z8F0113HH005EG                    | 1 KB 256 B      | 16       | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |  |  |  |

| Z8F0113PH005EG                    | 1 KB 256 B      | 16       | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |  |  |  |

| Z8F0113SJ005EG                    | 1 KB 256 B      | 24       | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |  |  |  |

| Z8F0113HJ005EG                    | 1 KB 256 B      | 24       | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |  |  |  |

| Z8F0113PJ005EG                    | 1 KB 256 B      | 24       | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |  |  |  |

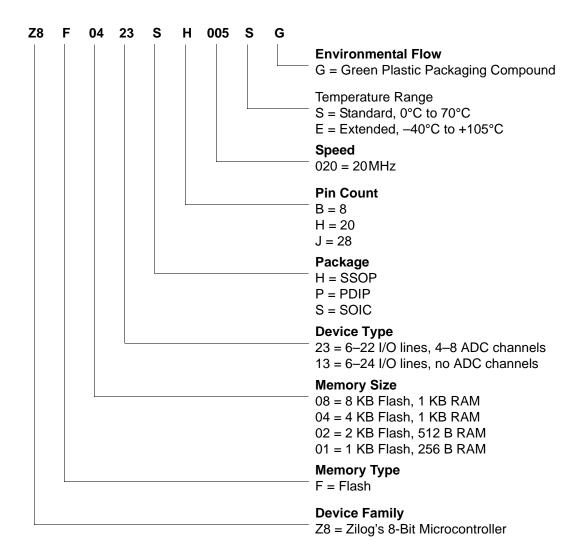

## **Part Number Suffix Designations**

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0423SH005SG is an 8-bit 20MHz Flash MCU with 4KB of Program Memory and equipped with 6–22 I/O lines and 4–8 ADC channels in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.