Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423qb005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| External Reset Input                                | . 25 |

|-----------------------------------------------------|------|

| External Reset Indicator                            | . 26 |

| On-Chip Debugger Initiated Reset                    | . 26 |

| Stop Mode Recovery                                  | . 26 |

| Stop Mode Recovery Using Watchdog Timer Time-Out    | . 27 |

| Stop Mode Recovery Using a GPIO Port Pin Transition | . 27 |

| Stop Mode Recovery Using the External RESET Pin     | . 28 |

| Reset Register Definitions                          | . 28 |

| Low-Power Modes                                     | . 30 |

| STOP Mode                                           | . 30 |

| HALT Mode                                           | . 31 |

| Peripheral-Level Power Control                      | . 31 |

| Power Control Register Definitions                  | . 31 |

| General-Purpose Input/Output                        | 33   |

| GPIO Port Availability By Device                    |      |

| Architecture                                        |      |

| GPIO Alternate Functions                            |      |

| Direct LED Drive                                    |      |

| Shared Reset Pin                                    |      |

| Shared Debug Pin                                    |      |

| Crystal Oscillator Override                         |      |

| 5V Tolerance                                        |      |

| External Clock Setup                                |      |

| GPIO Interrupts                                     |      |

| GPIO Control Register Definitions                   |      |

| Port A–C Address Registers                          |      |

| Port A–C Control Registers                          |      |

| Port A–C Data Direction Subregisters                |      |

| Port A–C Alternate Function Subregisters            | . 43 |

| Port A–C Input Data Registers                       | . 50 |

| Port A–C Output Data Register                       | . 51 |

| LED Drive Enable Register                           | . 51 |

| LED Drive Level High Register                       |      |

| LED Drive Level Low Register                        |      |

| Interrupt Controller                                | . 54 |

| Interrupt Vector Listing                            |      |

| Architecture                                        |      |

| Operation                                           | . 56 |

| Master Interrupt Enable                             |      |

| Interrupt Vectors and Priority                      | . 57 |

|                                                     |      |

ilog Embedded in Life An IXYS Company 17

| Address (Hex)    | Register Description      | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------|----------|-------------|-------------|

| Timer 1 (cont'd) |                           |          |             |             |

| F0A              | Timer 1 Reload High Byte  | T1RH     | FF          | <u>85</u>   |

| F0B              | Timer 1 Reload Low Byte   | T1RL     | FF          | <u>85</u>   |

| F0C              | Timer 1 PWM High Byte     | T1PWMH   | 00          | <u>86</u>   |

| F0D              | Timer 1 PWM Low Byte      | T1PWML   | 00          | <u>86</u>   |

| F0E              | Timer 1 Control 0         | T1CTL0   | 00          | <u>87</u>   |

| F0F              | Timer 1 Control 1         | T1CTL1   | 00          | <u>84</u>   |

| F10–F3F          | Reserved                  | —        | XX          |             |

| UART             |                           |          |             |             |

| F40              | UART0 Transmit Data       | U0TXD    | XX          | <u>109</u>  |

|                  | UART0 Receive Data        | U0RXD    | XX          | <u>109</u>  |

| F41              | UART0 Status 0            | U0STAT0  | 0000011Xb   | <u>110</u>  |

| F42              | UART0 Control 0           | U0CTL0   | 00          | <u>112</u>  |

| F43              | UART0 Control 1           | U0CTL1   | 00          | <u>112</u>  |

| F44              | UART0 Status 1            | U0STAT1  | 00          | <u>111</u>  |

| F45              | UART0 Address Compare     | U0ADDR   | 00          | <u>115</u>  |

| F46              | UART0 Baud Rate High Byte | U0BRH    | FF          | <u>115</u>  |

| F47              | UART0 Baud Rate Low Byte  | U0BRL    | FF          | <u>115</u>  |

| F48–F6F          | Reserved                  | —        | XX          |             |

| Analog-to-Digita | al Converter (ADC)        |          |             |             |

| F70              | ADC Control 0             | ADCCTL0  | 00          | <u>127</u>  |

| F71              | ADC Control 1             | ADCCTL1  | 80          | <u>127</u>  |

| F72              | ADC Data High Byte        | ADCD_H   | XX          | <u>130</u>  |

| F73              | ADC Data Low Bits         | ADCD_L   | XX          | <u>130</u>  |

| F74–F7F          | Reserved                  | —        | XX          |             |

| Low Power Con    | trol                      |          |             |             |

| F80              | Power Control 0           | PWRCTL0  | 80          | <u>32</u>   |

| F81              | Reserved                  | _        | XX          |             |

| LED Controller   |                           |          |             |             |

| F82              | LED Drive Enable          | LEDEN    | 00          | <u>51</u>   |

| F83              | LED Drive Level High Byte | LEDLVLH  | 00          | <u>52</u>   |

| Note: XX=Undefi  |                           |          |             |             |

#### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

# 28

nbedded in Life

# Stop Mode Recovery Using the External RESET Pin

When a Z8 Encore! XP F0823 Series device is in STOP Mode and the external  $\overline{\text{RESET}}$  pin is driven Low, a system reset occurs. Because of a glitch filter operating on the  $\overline{\text{RESET}}$  pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For more details, see the <u>Electrical Characteristics</u> chapter on page 196.

# **Reset Register Definitions**

The following sections define the Reset registers.

#### **Reset Status Register**

The Reset Status (RSTSTAT) Register is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer Control Register, which is writeonly; see Table 12.

| Bit     | 7                            | 6    | 5   | 4   | 3 | 2    | 1     | 0 |

|---------|------------------------------|------|-----|-----|---|------|-------|---|

| Field   | POR                          | STOP | WDT | EXT |   | Rese | erved |   |

| RESET   | See descriptions in Table 13 |      |     | 0   | 0 | 0    | 0     | 0 |

| R/W     | R                            | R    | R   | R   | R | R    | R     | R |

| Address |                              | FF0H |     |     |   |      |       |   |

Table 12. Reset Status Register (RSTSTAT)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>POR  | <b>Power-On Reset Indicator</b><br>If this bit is set to 1, a Power-On Reset event has occurred. This bit is reset to 0 if a WDT time-<br>out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read. For<br>POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                                                                                                   |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery is occurred. If the STOP and WDT bits are both set<br>to 1, the Stop Mode Recovery occurred because of a WDT time-out. If the STOP bit is 1 and<br>the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset<br>by a POR or a WDT time-out that occurred while not in STOP Mode. Reading this register also<br>resets this bit. For POR/Stop Mode Recover event values, please see Table 13. |

| [5]<br>WDT  | <b>Watchdog Timer Time-Out Indicator</b><br>If this bit is set to 1, a WDT time-out has occurred. A POR resets this pin. A Stop Mode Recov-<br>ery from a change in an input pin also resets this bit. Reading this register resets this bit; this<br>read must occur before clearing the WDT interrupt. For POR/Stop Mode Recover event values,<br>please see Table 13.                                                                                                                                             |

#### ilog° Embedded in Life An∎IXYS Company

#### 29

| Bit        | Description (Continued)                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>EXT | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset<br>or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register |

|            | resets this bit. For POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                               |

| [3:0]      | Reserved                                                                                                                                                                                                                    |

These bits are reserved and must be programmed to 0000 when read.

#### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

#### ilog Embedded in Life An ∎IXYS Company 51

# Port A–C Output Data Register

The Port A–C Output Data Register (Table 31) controls the output data to the pins.

#### Table 31. Port A–C Output Data Register (PxOUT)

| Bit     | 7     | 6     | 5     | 4        | 3        | 2     | 1     | 0     |

|---------|-------|-------|-------|----------|----------|-------|-------|-------|

| Field   | POUT7 | POUT6 | POUT5 | POUT4    | POUT3    | POUT2 | POUT1 | POUT0 |

| RESET   | 0     | 0     | 0     | 0        | 0        | 0     | 0     | 0     |

| R/W     | R/W   | R/W   | R/W   | R/W      | R/W      | R/W   | R/W   | R/W   |

| Address |       |       |       | FD3H, FD | 7H, FDBH |       |       |       |

#### Bit Description

[7:0] **Port Output Data**

PxOUT These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 = Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.

Note: x indicates the specific GPIO port pin number (7–0).

# **LED Drive Enable Register**

The LED Drive Enable Register, shown in Table 32, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7   | 6               | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|

| Field   |     | LEDEN[7:0]      |     |     |     |     |     |     |

| RESET   | 0   | 0 0 0 0 0 0 0 0 |     |     |     |     |     |     |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F82H            |     |     |     |     |     |     |

#### Table 32. LED Drive Enable (LEDEN)

| [7:0] | LED Drive Enable |  |

|-------|------------------|--|

Description

LEDEN These bits determine which Port C pins are connected to an internal current sink.

1= Connect controlled current sink to the Port C pin.

Bit

<sup>0 =</sup> Tristate the Port C pin.

# LED Drive Level High Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 33). These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit     | 7   | 6               | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|

| Field   |     | LEDLVLH[7:0]    |     |     |     |     |     |     |

| RESET   | 0   | 0 0 0 0 0 0 0 0 |     |     |     |     |     |     |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |                 |     | F8  | 3H  |     |     |     |

#### Table 33. LED Drive Level High Register (LEDLVLH)

| Bit     | Description                                                                             |

|---------|-----------------------------------------------------------------------------------------|

| [7:0]   | LED Level High Bit                                                                      |

| LEDLVLH | {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C |

|         | pin.                                                                                    |

|         | 00 = 3 mA.                                                                              |

|         | 01= 7 mA.                                                                               |

|         | 10= 13mA.                                                                               |

|         | 11= 20mA.                                                                               |

52

Embedded in Life

n 🖬 IXYS Company

| <b>Z</b> 8 | Encore! XP <sup>®</sup> | F0823  | Series  |

|------------|-------------------------|--------|---------|

|            | Product                 | Specif | ication |

|            |                         |        |         |

nbedded in Life

n 🗖 IXYS Company

56

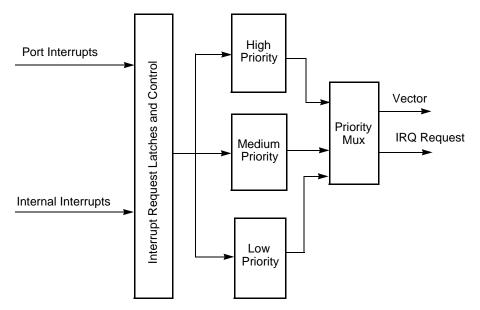

# Architecture

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

# Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 56

Interrupt Vectors and Priority: see page 57

Interrupt Assertion: see page 57

Software Interrupt Assertion: see page 58

Watchdog Timer Interrupt Assertion: see page 58

# **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

• Execution of an Enable Interrupt (EI) instruction

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

# Embedded in Life

two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

Table 57. Timer 0–1 Control Register 0 (TxCTL0)

| Table 57. Timer 0–1 Control Register 0 (TxCTL0) |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                  |             |             |     |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------|-------------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Bit                                             | 7                                                                                                                                                                                                                                                                                                                                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                             | 4                                | 3           | 2           | 1   | 0                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Field                                           | TMODEHI                                                                                                                                                                                                                                                                                                                                                 | TICO                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NFIG                          | Reserved                         |             | PWMD        |     | INPCAP                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| RESET                                           | 0                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                             | 0                                | 0           | 0           | 0   | 0                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| R/W                                             | R/W                                                                                                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W                           | R/W                              | R/W         | R/W         | R/W | R/W                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Address                                         |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               | F06H,                            | F0EH        | ·           |     |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Bit                                             | Descript                                                                                                                                                                                                                                                                                                                                                | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                                  |             |             |     |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| [7]<br>TMODEHI                                  | This bit a                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e TMODE f                     | ield in TxCTL<br>icant bit of th |             |             |     | ng mode of                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| [6:5]<br>TICONFIG                               | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined reload, compare and input events.</li> <li>10 = Timer Interrupt only on defined input capture/deassertion events.</li> <li>11 = Timer Interrupt only on defined reload/compare events.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                  |             |             |     |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| [4]                                             | <b>Reserve</b><br>This bit is                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | and must be                   | programme                        | d to 0.     |             |     |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| [3:1]<br>PWMD                                   | This field<br>before th<br>000 = Nc<br>001 = 2 c<br>010 = 4 c<br>011 = 8 c<br>100 = 16<br>101 = 32<br>110 = 64                                                                                                                                                                                                                                          | This bit is reserved and must be programmed to 0.<br><b>PWMD—PWM Delay value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>110 = 64 cycles delay.<br>111 = 128 cycles delay. |                               |                                  |             |             |     |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| [0]<br>INPCAP                                   | This bit i<br>0 = Previ                                                                                                                                                                                                                                                                                                                                 | ndicates if th                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ne most rec<br>iterrupt is no | ot a result of                   | Timer Input | capture eve | •   | <ul> <li>111 = 128 cycles delay.</li> <li>Input Capture Event</li> <li>This bit indicates if the most recent timer interrupt is caused by a Timer Input capture event.</li> <li>0 = Previous timer interrupt is not a result of Timer Input capture event.</li> <li>1 = Previous timer interrupt is a result of Timer Input capture event.</li> </ul> |  |  |  |  |  |  |  |  |

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

nbedded in Life

100

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled,.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

#### Transmitting Data Using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

00

105

scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

#### **External Driver Enable**

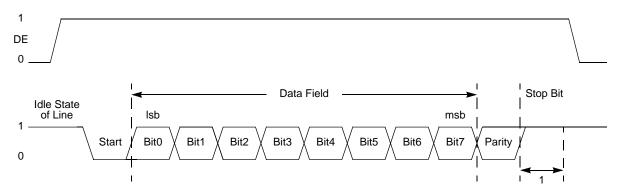

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data Register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

Figure 14. UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity)

The Driver Enable to Start bit setup time is calculated as follows:

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

Figure 21 displays a basic Flash Controller flow. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

150

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>VBO_AO | <ul> <li>Voltage Brown-Out Protection Always ON</li> <li>0 = Voltage Brown-Out Protection can be disabled in STOP Mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see the <u>Power Control Register 0</u> section on page 31).</li> <li>1 = Voltage Brown-Out Protection is always enabled including during STOP Mode. This setting is the default for unprogrammed (erased) Flash.</li> </ul> |

| [2]<br>FRP    | <ul> <li>Flash Read Protect</li> <li>0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.</li> <li>1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                         |

| [1]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                                                                                                                                      |

| [0]<br>FWP    | <ul> <li>Flash Write Protect</li> <li>This Option Bit provides Flash Program Memory protection:</li> <li>0 = Programming and erasure disabled for all of Flash Program Memory. Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.</li> <li>1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.</li> </ul>                                                    |

#### Table 90. Flash Options Bits at Program Memory Address 0001H

| Bit       | 7                    | 6            | 5              | 4      | 3        | 2   | 1   | 0   |  |  |  |

|-----------|----------------------|--------------|----------------|--------|----------|-----|-----|-----|--|--|--|

| Field     | Reserved             |              |                | XTLDIS | Reserved |     |     |     |  |  |  |

| RESET     | U                    | U            | U              | U      | U        | U   | U   | U   |  |  |  |

| R/W       | R/W                  | R/W          | R/W            | R/W    | R/W      | R/W | R/W | R/W |  |  |  |

| Address   | Program Memory 0001H |              |                |        |          |     |     |     |  |  |  |

| Note: U = | Unchanged b          | y Reset. R/W | ' = Read/Write | e.     |          |     |     |     |  |  |  |

## **ADC Calibration Data**

#### Table 94. ADC Calibration Bits

| Bit       | 7                                   | 6            | 5              | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------|--------------|----------------|-----|-----|-----|-----|-----|--|--|--|

| Field     | ADC_CAL                             |              |                |     |     |     |     |     |  |  |  |

| RESET     | U                                   | U            | U              | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                 | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Information Page Memory 0060H–007DH |              |                |     |     |     |     |     |  |  |  |

| Note: U = | Unchanged b                         | y Reset. R/M | / = Read/Write | е.  |     |     |     |     |  |  |  |

# Bit Description [7:0] Analog-to-Digital Converter Calibration Values ADC\_CAL Contains factory-calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in the Software Compensation Procedure section on page 126. The location of each calibration byte is provided in Table 95.

#### Table 95. ADC Calibration Data Location

| Info Page<br>Address | Memory<br>Address | Compensation<br>Usage | ADC Mode                | Reference<br>Type |

|----------------------|-------------------|-----------------------|-------------------------|-------------------|

| 60                   | FE60              | Offset                | Single-Ended Unbuffered | Internal 2.0V     |

| 08                   | FE08              | Gain High Byte        | Single-Ended Unbuffered | Internal 2.0V     |

| 09                   | FE09              | Gain Low Byte         | Single-Ended Unbuffered | Internal 2.0V     |

| 63                   | FE63              | Offset                | Single-Ended Unbuffered | Internal 1.0V     |

| 0A                   | FE0A              | Gain High Byte        | Single-Ended Unbuffered | Internal 1.0V     |

| 0B                   | FE0B              | Gain Low Byte         | Single-Ended Unbuffered | Internal 1.0V     |

| 66                   | FE66              | Offset                | Single-Ended Unbuffered | External 2.0V     |

| 0C                   | FE0C              | Gain High Byte        | Single-Ended Unbuffered | External 2.0V     |

| 0D                   | FE0D              | Gain Low Byte         | Single-Ended Unbuffered | External 2.0V     |

#### ilog<sup>\*</sup> Embedded in Life An∎IXYS Company 154

# **Serialization Data**

#### Table 96. Serial Number at 001C–001F (S\_NUM)

| Bit       | 7                                 | 6            | 5              | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-----------------------------------|--------------|----------------|-----|-----|-----|-----|-----|--|--|--|

| Field     | S_NUM                             |              |                |     |     |     |     |     |  |  |  |

| RESET     | U                                 | U            | U              | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                               | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Information Page Memory 001C–001F |              |                |     |     |     |     |     |  |  |  |

| Note: U = | Unchanged b                       | y Reset. R/W | / = Read/Write | е.  |     |     |     |     |  |  |  |

# Bit Description [7:0] Serial Number Byte S\_NUM The serial number is a unique four-byte binary value; see Table 97.

#### **Table 97. Serialization Data Locations**

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

# **Randomized Lot Identifier**

#### Table 98. Lot Identification Number (RAND\_LOT)

| Bit       | 7                                               | 6            | 5              | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|--------------|----------------|-----|-----|-----|-----|-----|--|--|--|

| Field     | RAND_LOT                                        |              |                |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U            | U              | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                             | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Interspersed throughout Information Page Memory |              |                |     |     |     |     |     |  |  |  |

| Note: U = | Unchanged b                                     | y Reset. R/M | / = Read/Write | ə.  |     |     |     |     |  |  |  |

| Bit             | Description                                                                                                                        |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>RAND_LOT | <b>Randomized Lot ID</b><br>The randomized lot ID is a 32-byte binary value that changes for each production lot; see<br>Table 99. |

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# **OCD Unlock Sequence (8-Pin Devices Only)**

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5 ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

\begin{array}{l} \text{DBG} \leftarrow 80\text{H} \text{ (autobaud)} \\ \\ \text{DBG} \leftarrow \text{EBH} \\ \\ \text{DBG} \leftarrow 5\text{AH} \\ \\ \\ \text{DBG} \leftarrow 70\text{H} \\ \\ \\ \\ \text{DBG} \leftarrow \text{CDH} \text{ (32-bit unlock key)} \end{array}

```

Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20- or 28-pin device. To enter DEBUG Mode, reautobaud and write 80H to the OCD Control Register (see the <u>On-Chip Debugger Commands</u> section on page 162).

#### **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

#### **Runtime Counter**

The OCD contains a 16-bit Runtime Counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

# Embedded in Life An IXYS Company

# **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

| Table 103. OCD Status | Register (OCDSTAT) |

|-----------------------|--------------------|

|-----------------------|--------------------|

| Bit   | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |

|-------|-----|------|--------|----------|---|---|---|---|--|

| Field | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |

|       |     |      | I      |          |   | I |   |   |  |

| Bit           | Description                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBG    | Debug Status<br>0 = NORMAL Mode.<br>1 = DEBUG Mode.                                                                                |

| [6]<br>HALT   | HALT Mode<br>0 = Not in HALT Mode.<br>1 = In HALT Mode.                                                                            |

| [5]<br>FRPENB | Flash Read Protect Option Bit Enable<br>0 = FRP bit enabled to allow disabling of many OCD commands.<br>1 = FRP bit has no effect. |

| [4:0]         | Reserved<br>These bits are reserved and must be 00000 when read.                                                                   |

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                       |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data<br>; value 01H, is the source. The value 01H is written into the<br>; Register at address 234H. |

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

#### Example 1

If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 106.

#### Table 106. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

#### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 107.

| Abbreviation | Description                             | Abbreviation                                   | Description            |

|--------------|-----------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                            | IRR                                            | Indirect Register Pair |

| СС           | Condition code                          | р                                              | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displace-<br>ment | r                                              | 4-bit Working Register |

| DA           | Destination address                     | R                                              | 8-bit register         |

| ER           | Extended Addressing register            | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                    | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| lr           | Indirect Working Register               | RA                                             | Relative               |

| IR           | Indirect register                       | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair          | RR                                             | Register Pair          |

#### Table 119. Opcode Map Abbreviations

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Embedded in Life An IXYS Company

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F0823 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 120 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                       | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                  | -40     | +105    | °C    |       |

| Storage temperature                                             | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>              | -0.3    | +5.5    | V     | 1     |

|                                                                 | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$                | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin             | -5      | +5      | μA    |       |

| Maximum output current from active output pin                   | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0°C to 70°C                   |         |         |       |       |

| Total power dissipation                                         |         | 220     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                  |         |         |       |       |

| Total power dissipation                                         |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                  |         |         |       |       |

| Total power dissipation                                         |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 125     | mA    |       |

| Natas, Operating temperature is enacified in DC Characteristics |         |         |       |       |

| Table 1 | 20. Ab | solute N | laximum | Ratings |

|---------|--------|----------|---------|---------|

|---------|--------|----------|---------|---------|

Notes: Operating temperature is specified in DC Characteristics.

This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

2. This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).