# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423sh005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

8

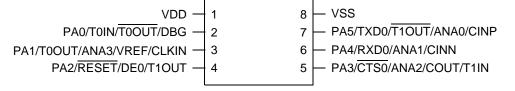

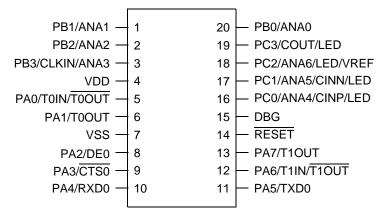

Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

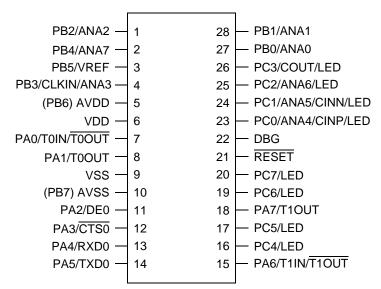

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

#### ilog<sup>°</sup> Embedded in Life 10 An∎IXYS Company

| Signal Mnemonic               | I/O | Description                                                                                                                                                                                                           |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COUT                          | 0   | Comparator Output. This is the output of the comparator.                                                                                                                                                              |

| Analog                        |     |                                                                                                                                                                                                                       |

| ANA[7:0]                      | I   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                          | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                   |     |                                                                                                                                                                                                                       |

| CLKIN                         | Ι   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                   |     |                                                                                                                                                                                                                       |

| LED                           | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programma ble drive strengths set by the GPIO block.                          |

| On-Chip Debugger              |     |                                                                                                                                                                                                                       |

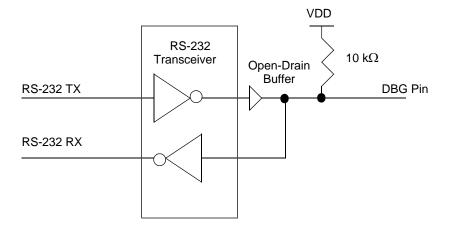

| DBG                           | I/O | Debug. This signal is the control and data input and output to and from the OCD.<br><b>Caution:</b> The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                   |

| Reset                         |     |                                                                                                                                                                                                                       |

| RESET                         | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                  |     |                                                                                                                                                                                                                       |

| V <sub>DD</sub>               | I   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> <sup>2</sup> | I   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>               | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>              | I   | Analog Ground.                                                                                                                                                                                                        |

### Table 3. Signal Descriptions (Continued)

replaced by AV<sub>DD</sub> and AV<sub>SS</sub>.

The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

#### ilog Embedded in Life An 🗆 IXYS Company

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 8-pin devices.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                         | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up<br>or Pull-<br>down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                    |

|--------------------|-----------|----------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if<br>key<br>sequence<br>detected) | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O<br>(defaults<br><u>to</u><br>RESET)                                    | N/A                                   | Yes                | Program-<br>mable for<br>PA2;<br>always<br>on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

| VSS                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

#### Table 5. Pin Characteristics (8-Pin Devices)

ILOG<sup>°</sup> Embedded in Life □IXYS Company 22

During a System Reset or Stop Mode Recovery, the IPO requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

## **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see **the** <u>Port A–C Control Registers</u> **section on page 42**), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overrightarrow{\text{RESET}}$  pin Low. The  $\overrightarrow{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

# **Stop Mode Recovery**

The device enters into STOP Mode when eZ8 CPU executes a STOP instruction. For more details about STOP Mode, see **the** Low-Power Modes **section on page 30**. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

#### ilog° Embedded in Life An∎IXYS Company

#### 29

| Bit        | Description (Continued)                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>EXT | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset<br>or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register |

|            | resets this bit. For POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                               |

| [3:0]      | Reserved                                                                                                                                                                                                                    |

These bits are reserved and must be programmed to 0000 when read.

#### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

# Embedded in Life

two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

Table 57. Timer 0–1 Control Register 0 (TxCTL0)

|                   | Table 57. Timer 0–1 Control Register 0 (TxCTL0)                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                                                    |             |             |     |              |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------|-------------|-------------|-----|--------------|--|--|--|

| Bit               | 7                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                             | 4                                                  | 3           | 2           | 1   | 0            |  |  |  |

| Field             | TMODEHI                                                                                                        | TICO                                                                                                                                                                                                                                                                                                                                                                                                                     | NFIG                          | Reserved                                           |             | PWMD        |     | INPCAP       |  |  |  |

| RESET             | 0                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                             | 0                                                  | 0           | 0           | 0   | 0            |  |  |  |

| R/W               | R/W                                                                                                            | R/W                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W                           | R/W                                                | R/W         | R/W         | R/W | R/W          |  |  |  |

| Address           |                                                                                                                | F06H, F0EH                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                                    |             |             |     |              |  |  |  |

| Bit               | Descript                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                              |                               |                                                    |             |             |     |              |  |  |  |

| [7]<br>TMODEHI    | This bit a                                                                                                     | <b>Timer Mode High Bit</b><br>This bit along with the TMODE field in TxCTL1 Register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value.                                                                                                                                                                                                                     |                               |                                                    |             |             |     |              |  |  |  |

| [6:5]<br>TICONFIG | 6 This field<br>0x = Tim<br>10 = Tim                                                                           | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined reload, compare and input events.</li> <li>10 = Timer Interrupt only on defined input capture/deassertion events.</li> <li>11 = Timer Interrupt only on defined reload/compare events.</li> </ul>                                                                  |                               |                                                    |             |             |     |              |  |  |  |

| [4]               | <b>Reserve</b><br>This bit is                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                          | and must be                   | programme                                          | d to 0.     |             |     |              |  |  |  |

| [3:1]<br>PWMD     | This field<br>before th<br>000 = Nc<br>001 = 2 c<br>010 = 4 c<br>011 = 8 c<br>100 = 16<br>101 = 32<br>110 = 64 | <b>PWMD—PWM Delay value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>110 = 64 cycles delay.<br>111 = 128 cycles delay. |                               |                                                    |             |             |     |              |  |  |  |

| [0]<br>INPCAP     | This bit i<br>0 = Previ                                                                                        | ious timer in                                                                                                                                                                                                                                                                                                                                                                                                            | ne most rec<br>iterrupt is no | ent timer inte<br>ot a result of<br>result of Time | Timer Input | capture eve | •   | pture event. |  |  |  |

### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

#### ilog° Embedded in Life An∎IXYS Company 99

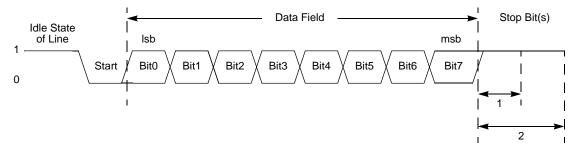

Figure 11. UART Asynchronous Data Format without Parity

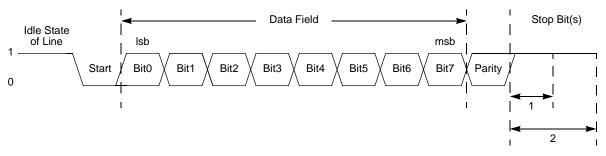

Figure 12. UART Asynchronous Data Format with Parity

## **Transmitting Data Using the Polled Method**

Observe the following steps to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register, if MULTIPROCESSOR Mode is appropriate, to enable MULTIPROCESSOR (9-bit) Mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR Mode.

- 5. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR Mode is not enabled, and select either even or odd parity (PSEL)

nbedded in Life

100

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled,.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

### Transmitting Data Using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

#### ilog<sup>°</sup> Embedded in Life An TIXYS Company

111

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | <ul> <li>Transmitter Data Register Empty</li> <li>This bit indicates that the UART Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the UART Transmit Data Register resets this bit.</li> <li>0 = Do not write to the UART Transmit Data Register.</li> <li>1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted.</li> </ul> |

| [1]<br>TXE  | <b>Transmitter Empty</b><br>This bit indicates that the transmit shift register is empty and character transmission is finished.<br>0 = Data is currently transmitting.<br>1 = Transmission is complete.                                                                                                                                                                                               |

| [0]<br>CTS  | <b>CTS</b> Signal When this bit is read, it returns the level of the $\overline{\text{CTS}}$ signal. This signal is active Low.                                                                                                                                                                                                                                                                        |

# **UART Status 1 Register**

This register contains multiprocessor control and status bits.

| Table 67. UART Stat | us 1 Register (U0STAT1) |

|---------------------|-------------------------|

|---------------------|-------------------------|

| Bit     | 7 | 6                    | 5 | 4  | 3   | 2   | 1 | 0 |  |

|---------|---|----------------------|---|----|-----|-----|---|---|--|

| Field   |   | Reserved NEWFRM MPRX |   |    |     |     |   |   |  |

| RESET   | 0 | 0                    | 0 | 0  | 0   | 0   | 0 | 0 |  |

| R/W     | R | R                    | R | R  | R/W | R/W | R | R |  |

| Address |   |                      |   | F4 | 4H  |     |   |   |  |

| Bit           | Description                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | <b>Reserved</b><br>These bits are reserved; R/W bits must be programmed to 000000 during writes and 000000 when read.                                                                                                                                                                             |

| [1]<br>NEWFRM | <ul> <li>New Frame</li> <li>A status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.</li> <li>0 = The current byte is not the first data byte of a new frame.</li> <li>1 = The current byte is the first data byte of a new frame.</li> </ul> |

| [0]<br>MPRX   | Multiprocessor Receive<br>Returns the value of the most recent multiprocessor bit received. Reading from the UART<br>Receive Data Register resets this bit to 0.                                                                                                                                  |

nbedded in Life

125

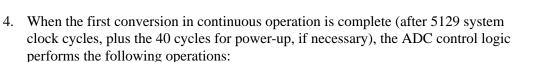

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 11-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:5]}

- An interrupt request to the Interrupt Controller denoting conversion complete

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

#### Interrupts

The ADC is able to interrupt the CPU whenever a conversion has been completed and the ADC is enabled.

When the ADC is disabled, an interrupt is not asserted; however, an interrupt pending when the ADC is disabled is not cleared.

### **Calibration and Compensation**

Z8 Encore! XP F0823 Series ADC can be factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, user code can perform its own calibration, storing the values into Flash themselves.

#### **Factory Calibration**

Devices that have been factory calibrated contain nine bytes of calibration data in the Flash option bit space. This data consists of three bytes for each reference type. For a list of input modes for which calibration data exists, see the <u>Zilog Calibration Data</u> section on page 152. There is 1 byte for offset, and there are 2 bytes for gain correction.

#### User Calibration

If you have precision references available, its own external calibration can be performed, storing the values into Flash themselves.

edded in Life

132

# Comparator

Z8 Encore! XP F0823 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex.

The features of the comparator include:

- Two inputs which can be connected up using the GPIO multiplex (MUX)

- One input can be connected to a programmable internal reference

- One input can be connected to the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

## Operation

One of the comparator inputs can be connected to an internal reference which is a user selectable reference that is user programmable with 200 mV resolution.

The comparator can be powered down to save on supply current. For details, see the <u>Power</u> <u>Control Register 0</u> section on page 31.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

The following example shows how to safely enable the comparator:

```

di

ld cmp0

nop

i, wait for output to settle

clr irq0; clear any spurious interrupts pending

ei

```

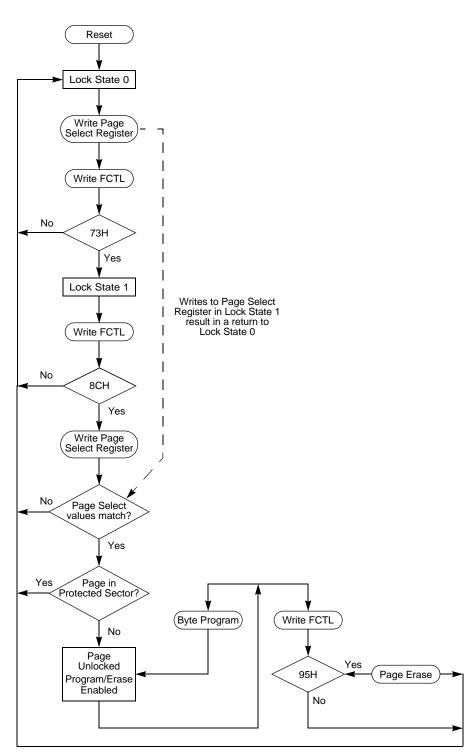

Figure 21. Flash Controller Operation Flowchart

| Bit           | Description                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 111 during writes and to 111 when read.                                                                                                                                                                                                                                                                |

| [4]<br>XTLDIS | <ul> <li>State of Crystal Oscillator at Reset</li> <li>This bit only enables the crystal oscillator. Its selection as a system clock must be performed manually.</li> <li>0 = The crystal oscillator is enabled during reset, resulting in longer reset timing.</li> <li>1 = The crystal oscillator is disabled during reset, resulting in shorter reset timing.</li> </ul> |

|               | <b>Caution:</b> Programming the XTLDIS bit to zero on 8-pin versions of F0823 Series devices prevents any further communication via the debug pin due to the $X_{IN}$ and DBG functions being shared on pin 2 of the 8-pin package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.                          |

| [3:0]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 1111 during writes and to 1111 when read                                                                                                                                                                                                                                                               |

# Trim Bit Address Space

All available trim bit addresses and their functions are listed in Tables 91 through 93.

| Bit       | 7                                               | 6                             | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|-------------------------------|-----|-----|-----|-----|-----|-----|--|--|

| Field     |                                                 | Reserved                      |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U                             | U   | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                                             | R/W                           | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address   |                                                 | Information Page Memory 0020H |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                               |     |     |     |     |     |     |  |  |

#### Table 91. Trim Options Bits at Address 0000H

| Bit   | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                  |

|       | These bits are reserved. Altering this register may result in incorrect device operation. |

ilog Ibedded in Life

156

# **On-Chip Debugger**

Z8 Encore! XP F0823 Series devices contain an integrated On-Chip Debugger (OCD) which provides advanced debugging features that include:

- Single pin interface

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

- Debug pin sharing with general-purpose input-output function to maximize the pins available

# Architecture

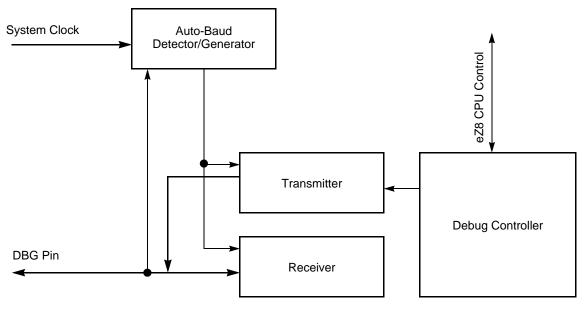

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator, and debug controller. Figure 22 displays the architecture of the OCD.

Figure 22. On-Chip Debugger Block Diagram

#### ilog<sup>°</sup> Embedded in Life An TIXYS Company 158

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 2 of 2

## **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The device enters DEBUG Mode following the operations below:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (breakpoint) instruction

- If the DBG pin is held Low during the most recent clock cycle of System Reset, the part enters DEBUG Mode upon exiting System Reset

• Note: Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an autobaud sequence (see the <u>OCD Autobaud Detector/</u><u>Generator section on page 159</u>).

#### ilog Embedded in Life An IXYS Company 162

# **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of Z8 Encore! XP F0823 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 101 is a summary of the OCD commands. Each OCD command is described in further detail in the pages that follow this table. <u>Table 102</u> on page 167 also indicates those commands that operate when the device is not in DEBUG Mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                                     |  |  |  |  |  |

|----------------------------|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Read OCD Revision          | 00H             | Yes                                | -                                                                                                                                                                                |  |  |  |  |  |

| Reserved                   | 01H             | _                                  | -                                                                                                                                                                                |  |  |  |  |  |

| Read OCD Status Register   | 02H             | Yes                                | -                                                                                                                                                                                |  |  |  |  |  |

| Read Runtime Counter       | 03H             | _                                  | -                                                                                                                                                                                |  |  |  |  |  |

| Write OCD Control Register | 04H             | Yes                                | Cannot clear DBGMODE bit.                                                                                                                                                        |  |  |  |  |  |

| Read OCD Control Register  | 05H             | Yes                                | -                                                                                                                                                                                |  |  |  |  |  |

| Write Program Counter      | 06H             | _                                  | Disabled.                                                                                                                                                                        |  |  |  |  |  |

| Read Program Counter       | 07H             | _                                  | Disabled.                                                                                                                                                                        |  |  |  |  |  |

| Write Register             | 08H             | _                                  | Only writes of the Flash Memory Con-<br>trol registers are allowed. Additionally,<br>only the Mass Erase command is<br>allowed to be written to the Flash Con-<br>trol Register. |  |  |  |  |  |

| Read Register              | 09H             | _                                  | Disabled.                                                                                                                                                                        |  |  |  |  |  |

| Write Program Memory       | 0AH             | _                                  | Disabled.                                                                                                                                                                        |  |  |  |  |  |

| Read Program Memory        | 0BH             | _                                  | Disabled.                                                                                                                                                                        |  |  |  |  |  |

| Write Data Memory          | 0CH             | _                                  | Yes.                                                                                                                                                                             |  |  |  |  |  |

| Read Data Memory           | 0DH             | _                                  | -                                                                                                                                                                                |  |  |  |  |  |

| Read Program Memory CRC    | 0EH             | _                                  | -                                                                                                                                                                                |  |  |  |  |  |

| Reserved                   | 0FH             | _                                  | -                                                                                                                                                                                |  |  |  |  |  |

| Step Instruction           | 10H             | _                                  | Disabled.                                                                                                                                                                        |  |  |  |  |  |

| Stuff Instruction          | 11H             | _                                  | Disabled.                                                                                                                                                                        |  |  |  |  |  |

| Execute Instruction        | 12H             | _                                  | Disabled.                                                                                                                                                                        |  |  |  |  |  |

| Reserved                   | 13H–FFH         | _                                  | -                                                                                                                                                                                |  |  |  |  |  |

#### Table 101. OCD Commands

ilog° Embedded in Life An∎IXYS Company

184

| Assembly        |                                           |     | ress<br>ode | _ Opcode(s) | Flags |   |     |   |    | _ Fetch | Instr. |   |

|-----------------|-------------------------------------------|-----|-------------|-------------|-------|---|-----|---|----|---------|--------|---|

| Mnemonic        | Symbolic Operation                        | dst | src         | (Hex)       | С     | Ζ | s v |   | DΗ |         | Cycles |   |

| BTJNZ bit, src, | if src[bit] = 1                           |     | r           | F6          | _     | _ | -   | - | -  | _       | 3      | 3 |

| dst             | $PC \gets PC + X$                         |     | Ir          | F7          |       |   |     |   |    |         | 3      | 4 |

| BTJZ bit, src,  | if src[bit] = 0<br>PC $\leftarrow$ PC + X |     | r           | F6          | _     | _ | -   | - | -  | _       | 3      | 3 |

| dst             |                                           |     | Ir          | F7          |       |   |     |   |    |         | 3      | 4 |

| CALL dst        | $SP \leftarrow SP -2$                     | IRR |             | D4          | -     | - | _   | - | _  | -       | 2      | 6 |

|                 | @SP ← PC<br>PC ← dst                      | DA  |             | D6          |       |   |     |   |    |         | 3      | 3 |

| CCF             | $C \leftarrow \simC$                      |     |             | EF          | *     | _ | -   | - | -  |         | 1      | 2 |

| CLR dst         | dst ← 00H                                 | R   |             | B0          | _     | - | _   | _ | -  | -       | 2      | 2 |

|                 |                                           | IR  |             | B1          |       |   |     |   |    |         | 2      | 3 |

| COM dst         | dst ← ~dst                                | R   |             | 60          | -     | * | *   | 0 | _  | _       | 2      | 2 |

|                 |                                           | IR  |             | 61          |       |   |     |   |    |         | 2      | 3 |

| CP dst, src     | dst - src                                 | r   | r           | A2          | *     | * | *   | * | _  | _       | 2      | 3 |

|                 |                                           | r   | lr          | A3          |       |   |     |   |    |         | 2      | 4 |

|                 |                                           | R   | R           | A4          | •     |   |     |   |    |         | 3      | 3 |

|                 |                                           | R   | IR          | A5          |       |   |     |   |    |         | 3      | 4 |

|                 |                                           | R   | IM          | A6          | •     |   |     |   |    |         | 3      | 3 |

|                 |                                           | IR  | IM          | A7          | •     |   |     |   |    |         | 3      | 4 |

| CPC dst, src    | dst - src - C                             | r   | r           | 1F A2       | *     | * | *   | * | _  | -       | 3      | 3 |

|                 |                                           | r   | lr          | 1F A3       |       |   |     |   |    |         | 3      | 4 |

|                 |                                           | R   | R           | 1F A4       |       |   |     |   |    |         | 4      | 3 |

|                 |                                           | R   | IR          | 1F A5       |       |   |     |   |    |         | 4      | 4 |

|                 |                                           | R   | IM          | 1F A6       |       |   |     |   |    |         | 4      | 3 |

|                 |                                           | IR  | IM          | 1F A7       |       |   |     |   |    |         | 4      | 4 |

| CPCX dst, src   | dst - src - C                             | ER  | ER          | 1F A8       | *     | * | *   | * | -  | _       | 5      | 3 |

|                 |                                           | ER  | IM          | 1F A9       |       |   |     |   |    |         | 5      | 3 |

| CPX dst, src    | dst - src                                 | ER  | ER          | A8          | *     | * | *   | * | -  | _       | 4      | 3 |

|                 |                                           | ER  | IM          | A9          |       |   |     |   |    |         | 4      | 3 |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

ilog<sup>®</sup> Embedded in Life 191 An∎IXYS Company

| Assembly      | Symbolic Operation          | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   | _ Fetch | Instr. |   |

|---------------|-----------------------------|-----------------|-----|-------------|-------|---|---|---|---|---------|--------|---|

| Mnemonic      |                             | dst             | src | (Hex)       | С     | Ζ | S | ۷ | D | Н       | Cycles |   |

| XOR dst, src  | $dst \gets dst \ XOR \ src$ | r               | r   | B2          | _     | * | * | 0 | _ | _       | 2      | 3 |

|               |                             | r               | lr  | B3          |       |   |   |   |   |         | 2      | 4 |

|               |                             | R               | R   | B4          |       |   |   |   |   |         | 3      | 3 |

|               |                             | R               | IR  | B5          |       |   |   |   |   |         | 3      | 4 |

|               |                             | R               | IM  | B6          |       |   |   |   |   |         | 3      | 3 |

|               |                             | IR              | IM  | B7          |       |   |   |   |   |         | 3      | 4 |

| XORX dst, src | $dst \gets dst \ XOR \ src$ | ER              | ER  | B8          | _     | * | * | 0 | _ | _       | 4      | 3 |

|               |                             | ER              | IM  | B9          |       |   |   |   |   |         | 4      | 3 |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

PS024315-1011

> ilog<sup>®</sup> Embedded in Life

■IXYS Company

211

# **Ordering Information**

Order your F0823 Series products from Zilog using the part numbers shown in Table 135. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

|                                                                                | Table 155. 20    | LIICO     |            | 1 0025 0               |                     | Oraci          |                     |  |  |  |  |

|--------------------------------------------------------------------------------|------------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|--|--|--|

| Part Number                                                                    | Flash<br>RAM     | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |  |  |

| Z8 Encore! XP F0823 Series with 8 KB Flash, 10-Bit Analog-to-Digital Converter |                  |           |            |                        |                     |                |                     |  |  |  |  |

| Standard Temperature: 0°C to 70°C                                              |                  |           |            |                        |                     |                |                     |  |  |  |  |

| Z8F0823PB005SG                                                                 | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |  |

| Z8F0823QB005SG                                                                 | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |  |

| Z8F0823SB005SG                                                                 | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |  |

| Z8F0823SH005SG                                                                 | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |  |

| Z8F0823HH005SG                                                                 | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |  |

| Z8F0823PH005SG                                                                 | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |  |

| Z8F0823SJ005SG                                                                 | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |  |

| Z8F0823HJ005SG                                                                 | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |  |

| Z8F0823PJ005SG                                                                 | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |  |

| Extended Temperatu                                                             | ıre: –40°C to 10 | )5°C      |            |                        |                     |                |                     |  |  |  |  |

| Z8F0823PB005EG                                                                 | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |  |

| Z8F0823QB005EG                                                                 | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |  |

| Z8F0823SB005EG                                                                 | 8 KB 1 KB        | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |  |

| Z8F0823SH005EG                                                                 | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |  |

| Z8F0823HH005EG                                                                 | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |  |

| Z8F0823PH005EG                                                                 | 8 KB 1 KB        | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |  |

| Z8F0823SJ005EG                                                                 | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |  |

| Z8F0823HJ005EG                                                                 | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |  |

| Z8F0823PJ005EG                                                                 | 8 KB 1 KB        | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |  |

#### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix