Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | ·                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813ph005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

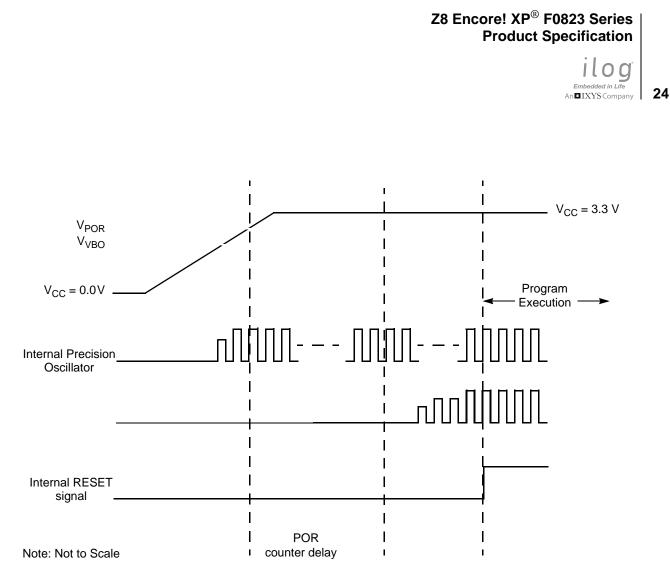

Figure 5. Power-On Reset Operation

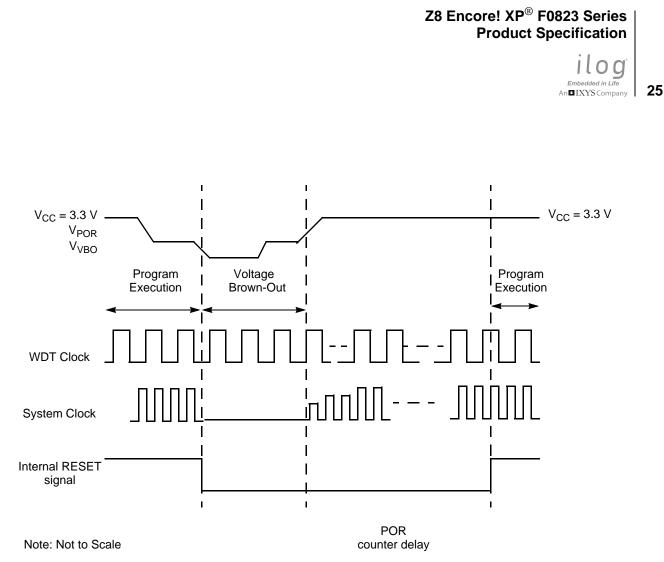

# Voltage Brown-Out Reset

The devices in the Z8 Encore! XP F0823 Series provide low VBO protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO threshold voltage) and forces the device into the Reset state. While the supply voltage remains below the POR voltage threshold ( $V_{POR}$ ), the VBO block holds the device in the Reset.

After the supply voltage again exceeds the Power-On Reset voltage threshold, the device progresses through a full System Reset sequence, as described in the <u>Power-On Reset</u> section on page 23. Following POR, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 6 displays Voltage Brown-Out operation. For the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ), see the <u>Electrical Characteristics</u> chapter on page 196.

The VBO circuit can be either enabled or disabled during STOP Mode. Operation during STOP Mode is set by the VBO\_AO Flash Option bit. For information about configuring VBO\_AO, see the <u>Flash Option Bits</u> chapter on page 146.

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

# Watchdog Timer Reset

If the device is in NORMAL or STOP Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT status bit in the WDT Control Register is set to signify that the reset was initiated by the Watchdog Timer.

# **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system

# Port A–C Data Direction Subregisters

The Port A–C Data Direction Subregister is accessed through the Port A–C Control Register by writing 01H to the Port A–C Address Register; see Table 22.

| Bit     | 7         | 6                                                                                      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----------|----------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   | DD7       | DD6                                                                                    | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |  |  |

| RESET   | 1         | 1                                                                                      | 1   | 1   | 1   | 1   | 1   | 1   |  |  |  |

| R/W     | R/W       | R/W                                                                                    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address | lf 01H ir | If 01H in Port A–C Address Register, accessible through the Port A–C Control Register. |     |     |     |     |     |     |  |  |  |

|         |           |                                                                                        |     |     |     |     |     |     |  |  |  |

Table 22. Port A–C Data Direction Subregisters (PxDD)

| Bit   | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                                                                                                                                                                                                                                                                         |

| DDx   | <ul> <li>These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.</li> <li>0 = Output. Data in the Port A–C Output Data Register is driven onto the port pin.</li> <li>1 = Input. The port pin is sampled and the value written into the Port A–C Input Data Register. The output driver is tristated.</li> </ul> |

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–C Alternate Function Subregisters

The Port A–C Alternate Function Subregister (Table 23) is accessed through the Port A–C Control Register by writing 02H to the Port A–C Address Register. The Port A–C Alternate Function subregisters enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the the <u>Port A–C Alternate Function Set 1</u> <u>Subregisters</u> section on page 48 and the <u>Port A–C Alternate Function Set 2 Subregisters</u> section on page 49. See the <u>GPIO Alternate Functions</u> section on page 34 to determine the alternate function associated with each port pin.

**Caution:** Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

#### ILOG<sup>°</sup> hbedded in Life IXYS Company 54

# Interrupt Controller

The interrupt controller on the Z8 Encore! XP F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u> available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 35 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

60

| Bit          | Description (Continued)                                                                                                                                                                                              |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>U0RXI | <ul> <li>UART 0 Receiver Interrupt Request</li> <li>0 = No interrupt request is pending for the UART 0 receiver.</li> <li>1 = An interrupt request from the UART 0 receiver is awaiting service.</li> </ul>          |

| [3]<br>UOTXI | <ul> <li>UART 0 Transmitter Interrupt Request</li> <li>0 = No interrupt request is pending for the UART 0 transmitter.</li> <li>1 = An interrupt request from the UART 0 transmitter is awaiting service.</li> </ul> |

| [2:1]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 00.                                                                                                                                             |

| [0]<br>ADCI  | <ul> <li>ADC Interrupt Request</li> <li>0 = No interrupt request is pending for the ADC.</li> <li>1 = An interrupt request from the ADC is awaiting service.</li> </ul>                                              |

# **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 37) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 1 Register to determine if any interrupt requests are pending.

| Bit     | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|---------|-------|-------|------|------|------|------|------|------|--|--|--|

| Field   | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |  |  |

| RESET   | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |  |  |  |

| R/W     | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |  |

| Address |       | FC3H  |      |      |      |      |      |      |  |  |  |

Table 37. Interrupt Request 1 Register (IRQ1)

| Bit           | Description                                                                                                                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7V   | Port A7 Interrupt Request<br>0 = No interrupt request is pending for GPIO Port A.<br>1 = An interrupt request from GPIO Port A.                                                                      |

| [6]<br>PA6C   | Port A6 or Comparator Interrupt Request<br>0 = No interrupt request is pending for GPIO Port A or Comparator.<br>1 = An interrupt request from GPIO Port A or Comparator.                            |

| [5:0]<br>PAxI | <ul> <li>Port A Pin x Interrupt Request</li> <li>0 = No interrupt request is pending for GPIO Port A pin x.</li> <li>1 = An interrupt request from GPIO Port A pin x is awaiting service.</li> </ul> |

| Note:         | x indicates the specific GPIO Port pin number (0–5).                                                                                                                                                 |

#### ilog Embedded in Life An IXYS Company 65

# **IRQ2 Enable High and Low Bit Registers**

Table 45 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers (Table 46 and Table 47) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register.

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

|            |            |          |             |

#### Table 45. IRQ2 Enable and Priority Encoding

Note: where x indicates the register bits from 0–7.

#### Table 46. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |  |

|---------|-----|------|-------|-----|-------|-------|-------|-------|--|--|

| Field   |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |  |  |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |     | FC7H |       |     |       |       |       |       |  |  |

| Bit          | Description                                             |

|--------------|---------------------------------------------------------|

| [7:4]        | Reserved                                                |

|              | These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENH | Port C3 Interrupt Request Enable High Bit               |

| [2]<br>C2ENH | Port C2 Interrupt Request Enable High Bit               |

| [1]<br>C1ENH | Port C1 Interrupt Request Enable High Bit               |

| [0]<br>C0ENH | Port C0 Interrupt Request Enable High Bit               |

nbedded in Life

81

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The compare time can be calculated by the following equation:

COMPARE Mode Time (s) = (Compare Value – Start Value) × Prescale System Clock Frequency (Hz)

#### **GATED Mode**

In GATED Mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following steps to configure a timer for GATED Mode and to initiate the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL1 Register.

# Embedded in Life

two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

Table 57. Timer 0–1 Control Register 0 (TxCTL0)

| Table 57. Timer 0–1 Control Register 0 (TxCTL0) |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                                    |             |             |     |              |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------|-------------|-------------|-----|--------------|--|--|

| Bit                                             | 7                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                             | 4                                                  | 3           | 2           | 1   | 0            |  |  |

| Field                                           | TMODEHI                                                                                                        | TICO                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NFIG                          | Reserved                                           |             | PWMD        |     | INPCAP       |  |  |

| RESET                                           | 0                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                             | 0                                                  | 0           | 0           | 0   | 0            |  |  |

| R/W                                             | R/W                                                                                                            | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W                           | R/W                                                | R/W         | R/W         | R/W | R/W          |  |  |

| Address                                         |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               | F06H,                                              | F0EH        | ·           |     |              |  |  |

| Bit                                             | Descript                                                                                                       | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                                                    |             |             |     |              |  |  |

| [7]<br>TMODEHI                                  | This bit a                                                                                                     | <b>Timer Mode High Bit</b><br>This bit along with the TMODE field in TxCTL1 Register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value.                                                                                                                                                                                                                                                                          |                               |                                                    |             |             |     |              |  |  |

| [6:5]<br>TICONFIG                               | 6 This field<br>0x = Tim<br>10 = Tim                                                                           | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined reload, compare and input events.</li> <li>10 = Timer Interrupt only on defined input capture/deassertion events.</li> <li>11 = Timer Interrupt only on defined reload/compare events.</li> </ul>                                                                                                                       |                               |                                                    |             |             |     |              |  |  |

| [4]                                             | <b>Reserve</b><br>This bit is                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | and must be                   | programme                                          | d to 0.     |             |     |              |  |  |

| [3:1]<br>PWMD                                   | This field<br>before th<br>000 = Nc<br>001 = 2 c<br>010 = 4 c<br>011 = 8 c<br>100 = 16<br>101 = 32<br>110 = 64 | This bit is reserved and must be programmed to 0.<br><b>PWMD—PWM Delay value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>110 = 64 cycles delay.<br>111 = 128 cycles delay. |                               |                                                    |             |             |     |              |  |  |

| [0]<br>INPCAP                                   | This bit i<br>0 = Previ                                                                                        | ious timer in                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ne most rec<br>iterrupt is no | ent timer inte<br>ot a result of<br>result of Time | Timer Input | capture eve | •   | pture event. |  |  |

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

nbedded in Life

102

# **Receiving Data Using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Observe the following steps to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR Mode

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

00

105

scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

# **External Driver Enable**

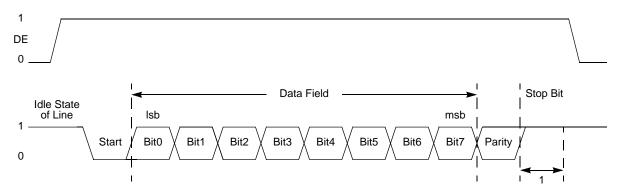

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data Register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

Figure 14. UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity)

The Driver Enable to Start bit setup time is calculated as follows:

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

nbedded in Life

124

- CEN resets to 0 to indicate the conversion is complete

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

#### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS Mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Observe the following steps for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

> ilog Embedded in Life An∎IXYS Company

> 127

| Bit            | 7                                                                                                                                                                                                                                         | 6                                                                                                                                                                                                                                                                                                                                                                                      | 5                                                                                | 4                                                                  | 3                                            | 2                           | 1                           | 0   |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------|-----------------------------|-----------------------------|-----|--|--|

| Field          | CEN                                                                                                                                                                                                                                       | REFSELL                                                                                                                                                                                                                                                                                                                                                                                | REFEXT                                                                           | CONT                                                               |                                              | ANAI                        | N[3:0]                      |     |  |  |

| RESET          | 0                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                | 0                                                                  | 0                                            | 0 0 0                       |                             |     |  |  |

| R/W            | R/W                                                                                                                                                                                                                                       | R/W                                                                                                                                                                                                                                                                                                                                                                                    | R/W                                                                              | R/W                                                                | R/W                                          | R/W                         | R/W                         | R/W |  |  |

| Address        |                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  | F7                                                                 | ОH                                           |                             | 1                           |     |  |  |

| Bit            | Descrip                                                                                                                                                                                                                                   | tion                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |                                                                    |                                              |                             |                             |     |  |  |

| [7]<br>CEN     | 0 = Conv<br>this t<br>1 = Begi                                                                                                                                                                                                            | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul> |                                                                                  |                                                                    |                                              |                             |                             |     |  |  |

| [6]<br>REFSELL | In conjur<br>mines th<br>SELH, R<br>00 = Inte<br>01 = Inte                                                                                                                                                                                | Reference<br>Inction with the<br>level of the<br>REFSELL}. T<br>ernal Reference<br>ernal Reference<br>ernal Reference                                                                                                                                                                                                                                                                  | he High bit (l<br>e internal vo<br>his referenc<br>nce Disableo<br>nce set to 1. | REFSELH) i<br>ltage referer<br>e is indeper<br>d, reference<br>0V. | nce; the follo<br>ident of the<br>comes from | owing details<br>Comparator | s the effects<br>reference. |     |  |  |

| [5]<br>REFEXT  | 0 = Exte                                                                                                                                                                                                                                  | <b>External Reference Select</b><br>0 = External reference buffer is disabled; $V_{REF}$ pin is available for GPIO functions.<br>1 = The internal ADC reference is buffered and connected to the V <sub>REF</sub> pin.                                                                                                                                                                 |                                                                                  |                                                                    |                                              |                             |                             |     |  |  |

| [4]<br>CONT    | <ul> <li>Continuous Conversion</li> <li>0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.</li> <li>1 = Continuous conversion. ADC data updated every 256 system clock cycles.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |                                                                    |                                              |                             |                             |     |  |  |

#### Table 74. ADC Control Register 0 (ADCCTL0)

# **ADC Calibration Data**

#### Table 94. ADC Calibration Bits

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| Field     | ADC_CAL                                         |     |     |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Information Page Memory 0060H–007DH             |     |     |     |     |     |     |     |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |

# Bit Description [7:0] Analog-to-Digital Converter Calibration Values ADC\_CAL Contains factory-calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in the Software Compensation Procedure section on page 126. The location of each calibration byte is provided in Table 95.

#### Table 95. ADC Calibration Data Location

| Info Page<br>Address | Memory<br>Address | Compensation<br>Usage | ADC Mode                | Reference<br>Type |

|----------------------|-------------------|-----------------------|-------------------------|-------------------|

| 60                   | FE60              | Offset                | Single-Ended Unbuffered | Internal 2.0V     |

| 08                   | FE08              | Gain High Byte        | Single-Ended Unbuffered | Internal 2.0V     |

| 09                   | FE09              | Gain Low Byte         | Single-Ended Unbuffered | Internal 2.0V     |

| 63                   | FE63              | Offset                | Single-Ended Unbuffered | Internal 1.0V     |

| 0A                   | FE0A              | Gain High Byte        | Single-Ended Unbuffered | Internal 1.0V     |

| 0B                   | FE0B              | Gain Low Byte         | Single-Ended Unbuffered | Internal 1.0V     |

| 66                   | FE66              | Offset                | Single-Ended Unbuffered | External 2.0V     |

| 0C                   | FE0C              | Gain High Byte        | Single-Ended Unbuffered | External 2.0V     |

| 0D                   | FE0D              | Gain Low Byte         | Single-Ended Unbuffered | External 2.0V     |

ILO O hbedded in Life IXYS Company

166

**Stuff Instruction (11H).** The Stuff command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0–4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

**Execute Instruction (12H).** The Execute command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

# **OCD Control Register**

The OCD Control Register controls the state of the OCD. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It also resets Z8 Encore! XP F0823 Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

nbedded in Life

171

conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control Register.

#### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions are divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

Tables 110 through 117 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| СР       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| СРХ      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

| INCW     | dst      | Increment Word                               |

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| ATM      | _        | Atomic Execution       |

| CCF      | —        | Complement Carry Flag  |

| DI       | —        | Disable Interrupts     |

| EI       | _        | Enable Interrupts      |

| HALT     | _        | HALT Mode              |

| NOP      | —        | No Operation           |

| RCF      | —        | Reset Carry Flag       |

| SCF      | —        | Set Carry Flag         |

| SRP      | src      | Set Register Pointer   |

| STOP     | —        | STOP Mode              |

| WDT      | _        | Watchdog Timer Refresh |

#### Table 113. CPU Control Instructions

#### Table 114. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

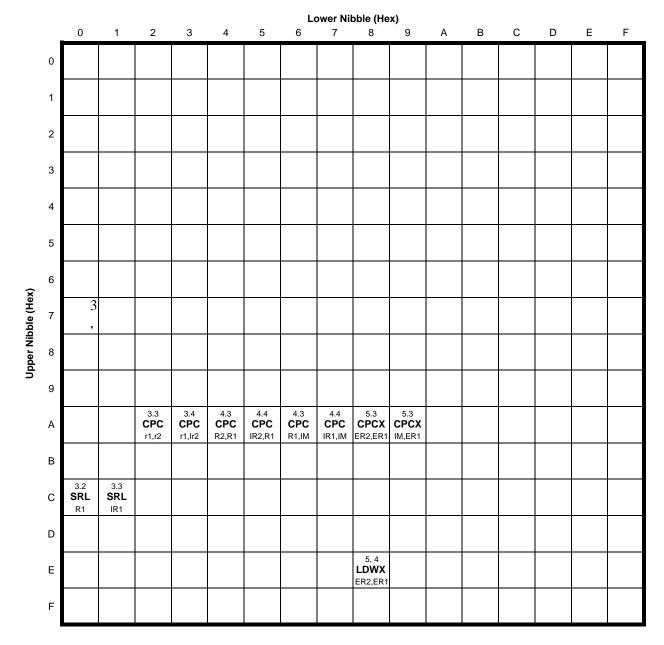

Figure 28. Second Opcode Map after 1FH

# Embedded in Life An IXYS Company

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                   |                        | V <sub>DD</sub> = 2.7V to 3.6V<br>T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise<br>stated) |                   |       |                                         |  |

|-------------------|------------------------|----------------------------------------------------------------------------------------------------|-------------------|-------|-----------------------------------------|--|

| Symbol Parameter  |                        | Minimum                                                                                            | Maximum           | Units | Conditions                              |  |

| FSYSCLK           | System Clock Frequency | _                                                                                                  | 20.0*             | MHz   | Read-only from Flash memory.            |  |

|                   |                        | 0.032768                                                                                           | 20.0 <sup>1</sup> | MHz   | Program or erasure of the Flash memory. |  |

| T <sub>XIN</sub>  | System Clock Period    | 50                                                                                                 | _                 | ns    | $T_{CLK} = 1/F_{SYSCLK}$ .              |  |

| T <sub>XINH</sub> | System Clock High Time | 20                                                                                                 | 30                | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINL</sub> | System Clock Low Time  | 20                                                                                                 | 30                | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINR</sub> | System Clock Rise Time | _                                                                                                  | 3                 | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINF</sub> | System Clock Fall Time | _                                                                                                  | 3                 | ns    | Т <sub>СІ К</sub> = 50ns.               |  |

| Table ' | 123. AC | Characteristics |

|---------|---------|-----------------|

|---------|---------|-----------------|

#### Table 124. Internal Precision Oscillator Electrical Characteristics

|                    |                                                         | V <sub>DD</sub> = 2.7V to 3.6V<br>T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise stated) |            |            |       |                                                 |

|--------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------|------------|-------|-------------------------------------------------|

| Symbol             | Parameter                                               | Minimum                                                                                         | Typical    | Maximum    | Units | Conditions                                      |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |                                                                                                 | 5.53       |            | MHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |                                                                                                 | 32.7       |            | kHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |                                                                                                 | <u>+</u> 1 | <u>+</u> 4 | %     |                                                 |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |                                                                                                 | 3          |            | μs    |                                                 |

#### ilog<sup>°</sup> Embedded in Life An IXYS Company 206

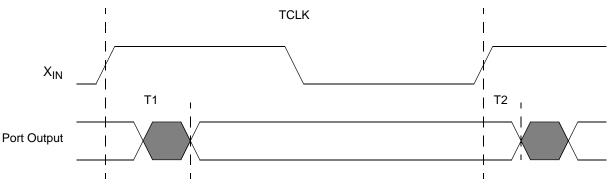

# General Purpose I/O Port Output Timing

Figure 30 and Table 131 provide timing information for GPIO Port pins.

|                |                                                 | Delay (ns) |         |

|----------------|-------------------------------------------------|------------|---------|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |

| GPIO Port p    | bins                                            |            |         |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _          | 15      |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |

#### Table 131. GPIO Port Output Timing