Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813qb005eg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ilog° Embedded in Life An IXYS Company

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                                                         | Description                                                                                                                                                                                                                          | Page<br>No.                                                         |

|-------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Sep         | 15                | LED Drive Enable Register                                                                                                                               | Clarified statement surrounding the Alternate<br>Function Register as it relates to the LED<br>function; revised Flash Sector Protect Regis-<br>ter description; revised Packaging chapter.                                          | <u>51,</u><br><u>144,</u><br><u>210</u>                             |

| Mar<br>2008 | 14                | n/a                                                                                                                                                     | Changed branding to <i>Z8 Encore! XP F0823</i><br><i>Series</i> where appropriate.                                                                                                                                                   | All                                                                 |

| Dec<br>2007 | 13                | Pin Description, General-Pur-<br>pose Input/Output, Interrupt<br>Controller, Watchdog Timer,<br>Electrical Characteristics, and<br>Ordering Information | Updated title from <i>Z8 Encore! 8K and 4K</i><br><i>Series</i> to <i>Z8 Encore! XP Z8F0823 Series</i> .<br>Updated Figure 3, Table 15, Table 35, Tables<br>59 through 61, Table 119 and Part Number<br>Suffix Designations section. | <u>8, 36,</u><br><u>60, 95,</u><br><u>199,</u><br>and<br><u>220</u> |

| Aug<br>2007 | 12                | Part Selection Guide, External<br>Clock Setup, and Program<br>Memory                                                                                    | Updated Table 1, Table 16, and Program Memory section.                                                                                                                                                                               | <u>2, 35,</u><br>and <u>13</u>                                      |

| Jun<br>2007 | 11                | n/a                                                                                                                                                     | Updated to combine Z8 Encore! 8K and Z8 Encore! 4K Series.                                                                                                                                                                           | All                                                                 |

| Dec<br>2006 | 10                | Ordering Information                                                                                                                                    | Updated Ordering Information chapter.                                                                                                                                                                                                | <u>211</u>                                                          |

| OCD Status Register                                                                                                                                                                             | 168                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Oscillator Control                                                                                                                                                                              | 169<br>169<br>170                             |

| Internal Precision Oscillator Operation                                                                                                                                                         | 173                                           |

| eZ8 CPU Instruction Set<br>Assembly Language Programming Introduction<br>Assembly Language Syntax<br>eZ8 CPU Instruction Notation<br>eZ8 CPU Instruction Classes<br>eZ8 CPU Instruction Summary | 174<br>175<br>176<br>178                      |

| Opcode Maps                                                                                                                                                                                     | 192                                           |

| Electrical Characteristics                                                                                                                                                                      | 196<br>197<br>200<br>201<br>204<br>206<br>207 |

| Packaging                                                                                                                                                                                       | 210                                           |

| Ordering Information                                                                                                                                                                            |                                               |

| Index                                                                                                                                                                                           | 221                                           |

| Customer Support                                                                                                                                                                                | 230                                           |

## **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit central processing unit (CPU), meets the continuing demand for faster and code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access of up to 4 KB

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>) available for download at <u>www.zilog.com</u>.

### **General-Purpose I/O**

F0823 Series features 6 to 24 port pins (Ports A–C) for general-purpose I/O (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable. 5 V-tolerant input pins are available on all I/Os on 8-pin devices, most I/Os on other package types.

## **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports protection against accidental program and erasure, as well as factory serialization and read protection.

An IXYS Company 6

## **On-Chip Debugger**

F0823 Series products feature an integrated On-Chip Debugger. The OCD provides a richset of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

### ILOG<sup>°</sup> Embedded in Life

## HALT Mode

Executing the eZ8 CPU's HALT instruction places the device into HALT Mode, which powers down the CPU but leaves all other peripherals active. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

## **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F0823 Series devices. Disabling a given peripheral minimizes its power consumption.

## **Power Control Register Definitions**

The following sections describe the power control registers.

### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

## Embedded in Life An TIXYS Company

## Port A–C Input Data Registers

Reading from the Port A–C Input Data registers (Table 30) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

| Bit     | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------------------|------|------|------|------|------|------|------|

| Field   | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET   | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W     | R                | R    | R    | R    | R    | R    | R    | R    |

| Address | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |

| Bit     | Description                                         |

|---------|-----------------------------------------------------|

| [7:0]   | Port Input Data                                     |

| PxIN    | Sampled data from the corresponding port pin input. |

|         | 0 = Input data is logical 0 (Low).                  |

|         | 1 = Input data is logical 1 (High).                 |

| Note: x | indicates the specific GPIO port pin number (7–0).  |

#### Table 40. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit           | 7                                                                        | 6           | 5          | 4             | 3       | 2        | 1 | 0      |  |  |

|---------------|--------------------------------------------------------------------------|-------------|------------|---------------|---------|----------|---|--------|--|--|

| Field         | Reserved                                                                 | T1ENH       | T0ENH      | <b>U0RENH</b> | U0TENH  | Reserved |   | ADCENH |  |  |

| RESET         | 0                                                                        | 0           | 0          | 0             | 0       | (        | ) | 0      |  |  |

| R/W           | R/W                                                                      | R/W         | R/W        | R/W           | R/W     | R/       | W | R/W    |  |  |

| Address       |                                                                          | FC1H        |            |               |         |          |   |        |  |  |

| Bit           | Description                                                              |             |            |               |         |          |   |        |  |  |

| [7]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.     |             |            |               |         |          |   |        |  |  |

| [6]<br>T1ENH  | Timer 1 Interrupt Request Enable High Bit                                |             |            |               |         |          |   |        |  |  |

| [5]<br>T0ENH  | Timer 0 Interrupt Request Enable High Bit                                |             |            |               |         |          |   |        |  |  |

| [4]<br>U0RENH | UART 0 Re                                                                | ceive Inter | rupt Reque | st Enable H   | igh Bit |          |   |        |  |  |

| [3]<br>U0TENH | UART 0 Transmit Interrupt Request Enable High Bit                        |             |            |               |         |          |   |        |  |  |

| [2:1]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |             |            |               |         |          |   |        |  |  |

| [0]           | ADC Interrupt Request Enable High Bit                                    |             |            |               |         |          |   |        |  |  |

[0] ADCENH

#### Table 41. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7               | 6     | 5            | 4             | 3             | 2        | 1 | 0      |  |

|---------|-----------------|-------|--------------|---------------|---------------|----------|---|--------|--|

| Field   | Reserved        | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved |   | ADCENL |  |

| RESET   | 0               | 0     | 0            | 0             | 0             | 0        |   | 0      |  |

| R/W     | R R/W R/W R/W R |       |              |               |               | R/W      |   |        |  |

| Address |                 | FC2H  |              |               |               |          |   |        |  |

| Bit          | Description                                                             |

|--------------|-------------------------------------------------------------------------|

| [7]          | Reserved<br>This bit is reserved and must be programmed to 0 when read. |

| [6]<br>T1ENL | Timer 1 Interrupt Request Enable Low Bit                                |

Observe the following steps to configure a timer for PWM DUAL OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode. Setting the mode also involves writing to the TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H); this write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) =  $\frac{\text{Reload Value } \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

ilog° Embedded in Life An∎IXYS Company 95

#### Table 61. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit                                                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|--|--|

| Field                                                                                         | WDTU |      |      |      |      |      |      |      |  |  |

| RESET                                                                                         | 00H  |      |      |      |      |      |      |      |  |  |

| R/W                                                                                           | R/W* |  |  |

| Address                                                                                       | FF1H |      |      |      |      |      |      |      |  |  |

| Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |      |  |  |

|                                                                                               |      |      |      |      |      |      |      |      |  |  |

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

### Table 62. Watchdog Timer Reload High Byte Register (WDTH)

| Bit                                                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Field                                                                                         |      |      |      | WD   | TH   |      |      |      |

| RESET                                                                                         | 04H  |      |      |      |      |      |      |      |

| R/W                                                                                           | R/W* |

| Address                                                                                       | FF2H |      |      |      |      |      |      |      |

| Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |      |

| Bit   | Description                                              |

|-------|----------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                     |

| WDTH  | Middle byte, Bits[15:8], of the 24-bit WDT reload value. |

#### Table 63. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit       | 7                                                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Field     | WDTL                                                                                          |      |      |      |      |      |      |      |  |  |  |

| RESET     | 00H                                                                                           |      |      |      |      |      |      |      |  |  |  |

| R/W       | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |  |

| Address   | FF3H                                                                                          |      |      |      |      |      |      |      |  |  |  |

| Note: R/W | Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |  |  |  |

#### ilog° Embedded in Life An∎IXYS Company 106

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error

Embedded in Life

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 68 and Table 69) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

| Bit     | 7           | 6    | 5    | 4   | 3    | 2    | 1    | 0    |  |  |  |

|---------|-------------|------|------|-----|------|------|------|------|--|--|--|

| Field   | TEN         | REN  | CTSE | PEN | PSEL | SBRK | STOP | LBEN |  |  |  |

| RESET   | 0           | 0    | 0    | 0   | 0    | 0    | 0    | 0    |  |  |  |

| R/W     | R/W         | R/W  | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |  |  |  |

| Address |             | F42H |      |     |      |      |      |      |  |  |  |

| Bit     | Description | n    |      |     |      |      |      |      |  |  |  |

#### Table 68. UART Control 0 Register (U0CTL0)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TEN  | Transmit EnableThis bit enables or disables the transmitter. The enable is also controlled by the $\overline{CTS}$ signaland the CTSE bit. If the $\overline{CTS}$ signal is low and the CTSE bit is 1, the transmitter is enabled.0 = Transmitter disabled.1 = Transmitter enabled.                                                                   |

| [6]<br>REN  | Receive Enable<br>This bit enables or disables the receiver.<br>0 = Receiver disabled.<br>1 = Receiver enabled.                                                                                                                                                                                                                                        |

| [5]<br>CTSE | <b>CTSE—CTS Enable</b><br>0 = The CTS signal has no effect on the transmitter.<br>1 = The UART recognizes the CTS signal as an enable control from the transmitter.                                                                                                                                                                                    |

| [4]<br>PEN  | <ul> <li>Parity Enable</li> <li>This bit enables or disables parity. Even or odd is determined by the PSEL bit.</li> <li>0 = Parity is disabled.</li> <li>1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit .</li> </ul>                                                                 |

| [3]<br>PSEL | <ul> <li>Parity Select</li> <li>0 = Even parity is transmitted and expected on all received data.</li> <li>1 = Odd parity is transmitted and expected on all received data.</li> </ul>                                                                                                                                                                 |

| [2]<br>SBRK | <ul> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = Forces a break condition by setting the output of the transmitter to zero.</li> </ul> |

nbedded in Life IXYS Company 120

The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the endec clock counter is reset, resynchronizing the endec to the incoming signal, allowing the endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

## Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART control registers as defined in the <u>Universal Asynchronous Receiver/Transmitter</u> chapter on page 97.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the endec before enabling the GPIO port alternate function for the corresponding pin.

ILOG abedded in Life

169

# **Oscillator Control**

Z8 Encore! XP F0823 Series devices uses three possible clocking schemes, each userselectable. These three schemes are:

- On-chip precision trimmed RC oscillator

- External clock drive

- On-chip low power Watchdog Timer oscillator

In addition, F0823 Series devices contain clock failure detection and recovery circuitry, which allow continued operation despite a failure of the primary oscillator.

## Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document.

### **System Clock Selection**

The oscillator control block selects from the available clocks. Table 104 details each clock source and its usage.

| Clock Source                          | Characteristics                                                                                                                | Required Setup                                                                                                                                                                                                  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8kHz or 5.53MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>            | <ul> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator at either 5.53MHz or<br/>32.8kHz</li> </ul>                                                              |

| External Clock<br>Drive               | <ul> <li>0 to 20MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul> |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Very Low power consumption</li> </ul> | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>            |

Table 104. Oscillator Configuration and Selection

nbedded in Life

170

ages to the Oscillator Control Desistor can actually stor the ship by

**Caution:** Unintentional accesses to the Oscillator Control Register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

### **OSC Control Register Unlocking/Locking**

To write to the Oscillator Control Register, unlock it by making two writes to the OSC-CTL Register with the values E7H followed by 18H. A third write to the OSCCTL Register changes the value of the actual register and returns the register to a locked state. Any other sequence of Oscillator Control Register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

## **Clock Failure Detection and Recovery**

Should an oscillator or timer fail, there are methods of recovery, as this section describes.

### **Primary Oscillator Failure**

Z8 Encore! XP F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the the <u>Watchdog Timer</u> section on page 91.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below  $1 \text{ kHz} \pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these

I

> Embedded in Life An IXYS Company 181

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

#### Table 115. Logical Instructions

#### Table 116. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | —               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

#### Table 117. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction               |

|----------|----------|---------------------------|

| BSWAP    | dst      | Bit Swap                  |

| RL       | dst      | Rotate Left               |

| RLC      | dst      | Rotate Left through Carry |

ilog° Embedded in Life An∎IXYS Company

190

| Assembly      |                                                                                                                        | Ado<br>M | _ Opcode(s) | s) Flags |   |   |   |   |   | _ Fetch | Instr. |   |

|---------------|------------------------------------------------------------------------------------------------------------------------|----------|-------------|----------|---|---|---|---|---|---------|--------|---|

| Mnemonic      | Symbolic Operation                                                                                                     | dst      | src         | (Hex)    | С | Ζ | S | ۷ | D | Н       | Cycles |   |

| TCM dst, src  | (NOT dst) AND src                                                                                                      | r        | r           | 62       | - | * | * | 0 | - | _       | 2      | 3 |

|               |                                                                                                                        | r        | lr          | 63       | - |   |   |   |   |         | 2      | 4 |

|               |                                                                                                                        | R        | R           | 64       | - |   |   |   |   |         | 3      | 3 |

|               |                                                                                                                        | R        | IR          | 65       | - |   |   |   |   |         | 3      | 4 |

|               |                                                                                                                        | R        | IM          | 66       | - |   |   |   |   |         | 3      | 3 |

|               |                                                                                                                        | IR       | IM          | 67       | - |   |   |   |   |         | 3      | 4 |

| TCMX dst, src | (NOT dst) AND src                                                                                                      | ER       | ER          | 68       | - | * | * | 0 | - | _       | 4      | 3 |

|               |                                                                                                                        | ER       | IM          | 69       | - |   |   |   |   |         | 4      | 3 |

| TM dst, src   | dst AND src                                                                                                            | r        | r           | 72       | - | * | * | 0 | - | _       | 2      | 3 |

|               |                                                                                                                        | r        | lr          | 73       | - |   |   |   |   |         | 2      | 4 |

|               |                                                                                                                        | R        | R           | 74       | - |   |   |   |   |         | 3      | 3 |

|               |                                                                                                                        | R        | IR          | 75       | - |   |   |   |   |         | 3      | 4 |

|               |                                                                                                                        | R        | IM          | 76       | - |   |   |   |   |         | 3      | 3 |

|               |                                                                                                                        | IR       | IM          | 77       | - |   |   |   |   |         | 3      | 4 |

| TMX dst, src  | dst AND src                                                                                                            | ER       | ER          | 78       | - | * | * | 0 | _ | _       | 4      | 3 |

|               |                                                                                                                        | ER       | IM          | 79       | - |   |   |   |   |         | 4      | 3 |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |          | Vector      | F2       | - | _ | - | - | - | _       | 2      | 6 |

| WDT           |                                                                                                                        |          |             | 5F       | _ | _ | _ | _ | _ | _       | 1      | 2 |

### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

ilog Embedded in Life An IXYS Company 202

|                                               | $T_A = -$ | = 2.7V to<br>-40°C to +<br>otherwise | 105°C   |        |                                                                                                                                                                  |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  | Notes                                                                                                                                                            |

| Flash Byte Read Time                          | 100       | _                                    | _       | ns     |                                                                                                                                                                  |

| Flash Byte Program Time                       | 20        | _                                    | 40      | μs     |                                                                                                                                                                  |

| Flash Page Erase Time                         | 10        | _                                    | _       | ms     |                                                                                                                                                                  |

| Flash Mass Erase Time                         | 200       | _                                    | _       | ms     |                                                                                                                                                                  |

| Writes to Single Address<br>Before Next Erase | -         | -                                    | 2       |        |                                                                                                                                                                  |

| Flash Row Program Time                        | -         | _                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This param-<br>eter is only an issue when<br>bypassing the Flash Controller. |

| Data Retention                                | 100       | _                                    | _       | years  | 25°C                                                                                                                                                             |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                             |

#### Table 126. Flash Memory Electrical Characteristics and Timing

#### Table 127. Watchdog Timer Electrical Characteristics and Timing

|                          |                          | T <sub>A</sub> = - | = 2.7V to<br>-40°C to +<br>otherwise | 105°C       |       |                                                                                              |  |

|--------------------------|--------------------------|--------------------|--------------------------------------|-------------|-------|----------------------------------------------------------------------------------------------|--|

| Symbol                   | Parameter                | Minimum            | Typical                              | Maximum     | Units | Conditions                                                                                   |  |

| F <sub>WDT</sub>         | WDT Oscillator Frequency |                    | 10                                   |             | kHz   |                                                                                              |  |

| F <sub>WDT</sub>         | WDT Oscillator Error     |                    |                                      | <u>+</u> 50 | %     |                                                                                              |  |

| T <sub>WDT-</sub><br>CAL | WDT Calibrated Timeout   | 0.98               | 1                                    | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30°C                                            |  |

|                          |                          | 0.70               | 1                                    | 1.30        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = 0^{\circ} C \text{ to } 70^{\circ} C$           |  |

|                          |                          | 0.50               | 1                                    | 1.50        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = -40^{\circ} \text{C to } +105^{\circ} \text{C}$ |  |

#### ILOG<sup>°</sup> Inbedded in Life IXYS Company **210**

# Packaging

Zilog's F0823 Series of MCUs includes the Z8F0113, Z8F0123, Z8F0213, Z8F0223, Z8F0413, Z8F0423, Z8F0813 and Z8F0823 devices, which are available in the following packages:

- 8-pin Plastic Dual Inline Package (PDIP)

- 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S<sup>1</sup>

- 20-pin Plastic Dual-Inline Package (PDIP)

- 20-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Small Shrink Outline Package (SSOP)

- 28-pin Plastic Dual-Inline Package (PDIP)

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Small Shrink Outline Package (SSOP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

<sup>1.</sup> The footprint of the QFN)/MLF-S package is identical to that of the 8-pin SOIC package, but with a lower profile.

# Embedded in Life

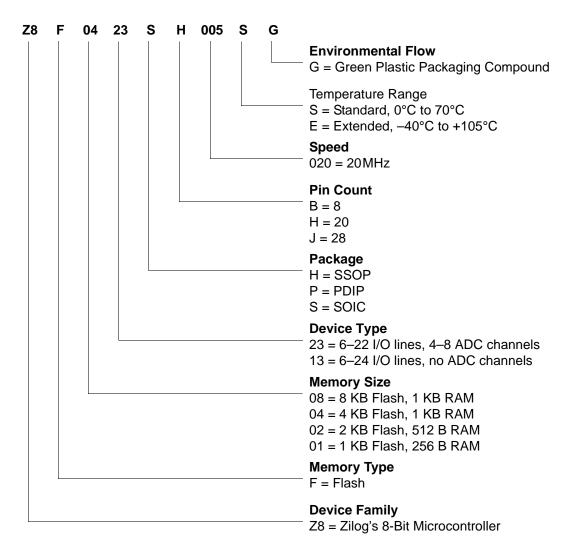

## Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0423SH005SG is an 8-bit 20MHz Flash MCU with 4KB of Program Memory and equipped with 6–22 I/O lines and 4–8 ADC channels in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

230

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.