Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 5MHz                                                      |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 6                                                         |  |

| Program Memory Size        | 8KB (8K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 1K x 8                                                    |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813sb005eg |  |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

νi

| Interrupt Assertion                                      | . 57 |

|----------------------------------------------------------|------|

| Software Interrupt Assertion                             | . 58 |

| Watchdog Timer Interrupt Assertion                       | . 58 |

| Interrupt Control Register Definitions                   | . 59 |

| Interrupt Request 0 Register                             | . 59 |

| Interrupt Request 1 Register                             | . 60 |

| Interrupt Request 2 Register                             | . 61 |

| IRQ0 Enable High and Low Bit Registers                   | . 61 |

| IRQ1 Enable High and Low Bit Registers                   | . 63 |

| IRQ2 Enable High and Low Bit Registers                   | . 65 |

| Interrupt Edge Select Register                           | . 66 |

| Shared Interrupt Select Register                         | . 67 |

| Interrupt Control Register                               | . 68 |

| Timers                                                   | 69   |

| Architecture                                             |      |

| Operation                                                |      |

| Timer Operating Modes                                    |      |

| Reading the Timer Count Values                           |      |

| Timer Pin Signal Operation                               |      |

| Timer Control Register Definitions                       |      |

| Timer 0–1 High and Low Byte Registers                    |      |

| Timer Reload High and Low Byte Registers                 |      |

| Timer 0–1 PWM High and Low Byte Registers                |      |

| Timer 0–1 Control Registers                              |      |

| <u> </u>                                                 |      |

| Watchdog Timer                                           |      |

| Operation                                                |      |

| Watchdog Timer Refresh                                   |      |

| Watchdog Timer Time-Out Response                         |      |

| Watchdog Timer Reload Unlock Sequence                    |      |

| Watchdog Timer Control Register Definitions              |      |

| Watchdog Timer Control Register                          |      |

| Watchdog Timer Reload Upper, High and Low Byte Registers | . 94 |

| Universal Asynchronous Receiver/Transmitter              | . 97 |

| Architecture                                             | . 97 |

| Operation                                                | . 98 |

| Transmitting Data Using the Polled Method                | . 99 |

| Transmitting Data Using the Interrupt-Driven Method      | 100  |

| Receiving Data Using the Polled Method                   | 101  |

| Receiving Data Using the Interrupt-Driven Method         |      |

| Clear To Send (CTS) Operation                            |      |

| •                                                        |      |

# Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| OCD Status Register                                     | 168 |

|---------------------------------------------------------|-----|

| Oscillator Control                                      | 169 |

| Operation                                               |     |

| System Clock Selection                                  |     |

| Clock Failure Detection and Recovery                    |     |

| Oscillator Control Register Definitions                 | 171 |

| Internal Precision Oscillator                           |     |

| Operation                                               | 173 |

| eZ8 CPU Instruction Set                                 | 174 |

| Assembly Language Programming Introduction              | 174 |

| Assembly Language Syntax                                | 175 |

| eZ8 CPU Instruction Notation                            |     |

| eZ8 CPU Instruction Classes                             |     |

| eZ8 CPU Instruction Summary                             | 182 |

| Opcode Maps                                             | 192 |

| Electrical Characteristics                              | 196 |

| Absolute Maximum Ratings                                | 196 |

| DC Characteristics                                      | 197 |

| AC Characteristics                                      |     |

| On-Chip Peripheral AC and DC Electrical Characteristics |     |

| General Purpose I/O Port Input Data Sample Timing       |     |

| General Purpose I/O Port Output Timing                  |     |

| On-Chip Debugger Timing                                 |     |

| UART Timing                                             | 208 |

| Packaging                                               | 210 |

| Ordering Information                                    | 211 |

| Part Number Suffix Designations                         | 220 |

| Index                                                   | 221 |

| Customer Support                                        | 230 |

| Customer Support                                        |     |

**Table 3. Signal Descriptions (Continued)**

| Signal Mnemonic               | I/O | Description                                                                                                                                                                                                           |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COUT                          | 0   | Comparator Output. This is the output of the comparator.                                                                                                                                                              |

| Analog                        |     |                                                                                                                                                                                                                       |

| ANA[7:0]                      | I   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                          | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                   |     |                                                                                                                                                                                                                       |

| CLKIN                         | I   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                   |     |                                                                                                                                                                                                                       |

| LED                           | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                           |

| On-Chip Debugger              |     |                                                                                                                                                                                                                       |

| DBG                           | I/O | Debug. This signal is the control and data input and output to and from the OCD.  Caution: The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                            |

| Reset                         |     |                                                                                                                                                                                                                       |

| RESET                         | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                  |     |                                                                                                                                                                                                                       |

| $V_{DD}$                      | ļ   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> <sup>2</sup> | I   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>               | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>              | I   | Analog Ground.                                                                                                                                                                                                        |

| Notos:                        |     |                                                                                                                                                                                                                       |

- 1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are

- replaced by AV<sub>DD</sub> and AV<sub>SS</sub>.

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

22

During a System Reset or Stop Mode Recovery, the IPO requires 4 µs to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

| Bit        | Description (Continued)                                                                                                                                                                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>EXT | External Reset Indicator  If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit. For POR/Stop Mode Recover event values, please see Table 13. |

| [3:0]      | Reserved These bits are reserved and must be programmed to 0000 when read.                                                                                                                                                                                                                           |

**Table 13. POR Indicator Values**

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

**Table 17. Port Alternate Function Mapping (Non 8-Pin Parts)**

| Port                | Pin | Mnemonic                | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-------------------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1</sup> | PA0 | T0IN/T0OUT              | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|                     |     | Reserved                |                                         | -                                       |

|                     | PA1 | T0OUT                   | Timer 0 Output                          | _                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA2 | DE0                     | UART 0 Driver Enable                    | _                                       |

|                     |     | Reserved                |                                         | -                                       |

|                     | PA3 | CTS0                    | UART 0 Clear to Send                    | -                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA4 | RXD0/IRRX0              | UART 0 / IrDA 0 Receive Data            | _                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA5 | TXD0/IRTX0              | UART 0 / IrDA 0 Transmit Data           | -                                       |

|                     |     | Reserved                |                                         | _                                       |

|                     | PA6 | T1IN/T1OUT <sup>2</sup> | Timer 1 Input/Timer 1 Output Complement | -                                       |

|                     |     | Reserved                |                                         | -                                       |

|                     | PA7 | T1OUT                   | Timer 1 Output                          |                                         |

|                     |     | Reserved                |                                         | -                                       |

#### Notes:

- 1. Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in the <a href="Port A—C Alternate Function">Port A—C Alternate Function</a> Subregisters section on page 43 automatically enables the associated alternate function.

- 2. Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in the <u>Timer Pin Signal Operation</u> section on page 83.

- 3. Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, alternate function selection as described in the <a href="Port A-C Alternate Function Subregisters">Port A-C Alternate Function Subregisters</a> section on page 43 must also be enabled.

- 4. V<sub>REF</sub> is available on PB5 in 28-pin products only.

- 5. Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in the <a href="Port A-C Alternate Function Subregisters">Port A-C Alternate Function Subregisters</a> section on page 43 must also be enabled.

- 6. V<sub>REF</sub> is available on PC2 in 20-pin parts only.

# Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers (Table 55 and Table 56) control pulse-width modulator (PWM) operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

Table 55. Timer 0–1 PWM High Byte Register (TxPWMH)

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Field   |     |     |     | PW    | MH   |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F04H, | F0CH |     |     |     |

Table 56. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7    | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|------|-----|-----|-------|------|-----|-----|-----|

| Field   | PWML |     |     |       |      |     |     |     |

| RESET   | 0    | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W     | R/W  | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |      |     |     | F05H, | F0DH |     |     |     |

| Bit                    | Description                                                                                                                                                                                                                                                                                               |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>PWMH,<br>PWML | Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register. |

|                        | These TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.                                                                                                                                                                          |

# Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

### Timer 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode. It also includes a programmable PWM deadband delay,

### **WDT Reset in NORMAL Operation**

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Watchdog Timer Control Register is set to 1. For more information about System Reset, see **the** Reset and Stop Mode Recovery chapter on page 21.

#### **WDT Reset in STOP Mode**

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following WDT time-out in STOP Mode. For more information, see **the** Reset and Stop Mode Recovery chapter on page 21.

### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer Control Register (WDTCTL) address unlocks the three Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. The following sequence is required to unlock the Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# **Watchdog Timer Control Register Definitions**

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register (WDTCTL): see page 94

Watchdog Timer Reload Upper Byte Register (WDTU): see page 95

### **Software Compensation Procedure**

The value read from the ADC high and low byte registers are uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following formula yields the compensated value:

$$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL)*GAINCAL)/2$$

where GAINCAL is the gain calibration byte, OFFCAL is the offset calibration byte and ADC<sub>uncomp</sub> is the uncompensated value read from the ADC. The OFFCAL value is in two's complement format, as are the compensated and uncompensated ADC values.

**Note:** The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits. Also note that in the second term, the multiplication must be performed before the division by 2<sup>16</sup>. Otherwise, the second term evaluates to zero incorrectly.

**Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit non-unity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

# **ADC Control Register Definitions**

The following sections define the ADC Control registers.

### **ADC Control Register 0**

The ADC Control Register selects the analog input channel and initiates the analog-to-digital conversion.

128

| Bit | Description | (Continued) |

|-----|-------------|-------------|

|-----|-------------|-------------|

#### [3:0] ANAIN

#### **Analog Input Select**

These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore! XP F0823 Series. For information about the port pins available with each package style, see **the** <u>Pin Description</u> section on page 7. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

#### Single-Ended:

0000 = ANA0.

0001 = ANA1.

0010 = ANA2.

0011 = ANA3.

0100 = ANA4.

0101 = ANA5.

0110 = ANA6.

0111 = ANA7.

1000 = Reserved.

1001 = Reserved.

1010 = Reserved.

1011 = Reserved.

1100 = Reserved.

1101 = Reserved.

1110 = Reserved. 1111 = Reserved.

#### Table 80. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code programming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                           |

### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

### **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F0823 Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 79</u> on page 134.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

### **Watchdog Timer Failure**

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control Register.

### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

### **Assembly Language Source Program Example**

JP START ; Everything after the semicolon is a comment.

START: ; A label called 'START'. The first instruction (JP START) in this

; example causes program execution to jump to the point within the

; program where the START label occurs.

LD R4, R7; A Load (LD) instruction with two operands. The first operand,

; Working Register R4, is the destination. The second operand, ; Working Register R7, is the source. The contents of R7 is

; written into R4.

LD 234H, #%01; Another Load (LD) instruction with two operands.

; The first operand, Extended Mode Register Address 234H, ; identifies the destination. The second operand, Immediate Data ; value 01H, is the source. The value 01H is written into the

; Register at address 234H.

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

### **Example 1**

If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 106.

Table 106. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 180 | (ADD dst, sro | ( د        |

|------------------------|-----|------|-----|---------------|------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst | <b>:</b> ) |

### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is shown in Table 107.

Table 118. eZ8 CPU Instruction Summary (Continued)

| Assembly     |                                                                                                                               |     | ress<br>de | _ Opcode(s)          |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|-----|------------|----------------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic     | Symbolic Operation                                                                                                            | dst | src        | _ Opcode(s)<br>(Hex) | С | Z | s   | ٧   | D | Н | Cycles  |        |

| DA dst       | dst ← DA(dst)                                                                                                                 | R   |            | 40                   | * | * | *   | Χ   | _ | _ | 2       | 2      |

|              |                                                                                                                               | IR  |            | 41                   |   |   |     |     |   |   | 2       | 3      |

| DEC dst      | dst ← dst - 1                                                                                                                 | R   |            | 30                   | - | * | *   | *   | - | _ | 2       | 2      |

|              |                                                                                                                               | IR  |            | 31                   | • |   |     |     |   |   | 2       | 3      |

| DECW dst     | dst ← dst - 1                                                                                                                 | RR  |            | 80                   | _ | * | *   | *   | _ | _ | 2       | 5      |

|              |                                                                                                                               | IRR |            | 81                   | • |   |     |     |   |   | 2       | 6      |

| DI           | IRQCTL[7] ← 0                                                                                                                 |     |            | 8F                   | _ | - | -   | -   | _ | _ | 1       | 2      |

| DJNZ dst, RA | $dst \leftarrow dst - 1$ if $dst \neq 0$ $PC \leftarrow PC + X$                                                               | r   |            | 0A-FA                | - | - | _   | -   | _ | _ | 2       | 3      |

| EI           | IRQCTL[7] ← 1                                                                                                                 |     |            | 9F                   | _ | - | -   | _   | _ | - | 1       | 2      |

| HALT         | HALT Mode                                                                                                                     |     |            | 7F                   | _ | - | _   | _   | _ | _ | 1       | 2      |

| INC dst      | dst ← dst + 1                                                                                                                 | R   |            | 20                   | - | * | *   | -   | _ | - | 2       | 2      |

|              |                                                                                                                               | IR  |            | 21                   | • |   |     |     |   |   | 2       | 3      |

|              |                                                                                                                               | r   |            | 0E-FE                | • |   |     |     |   |   | 1       | 2      |

| INCW dst     | dst ← dst + 1                                                                                                                 | RR  |            | A0                   | _ | * | *   | *   | _ | _ | 2       | 5      |

|              |                                                                                                                               | IRR |            | A1                   |   |   |     |     |   |   | 2       | 6      |

| IRET         | FLAGS $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 1<br>PC $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 2<br>IRQCTL[7] $\leftarrow$ 1 |     |            | BF                   | * | * | *   | *   | * | * | 1       | 5      |

| JP dst       | PC ← dst                                                                                                                      | DA  |            | 8D                   | _ | _ | _   | _   | _ | _ | 3       | 2      |

|              |                                                                                                                               | IRR |            | C4                   | • |   |     |     |   |   | 2       | 3      |

| JP cc, dst   | if cc is true<br>PC ← dst                                                                                                     | DA  |            | 0D-FD                | - | - | -   | _   | _ | - | 3       | 2      |

| JR dst       | $PC \leftarrow PC + X$                                                                                                        | DA  |            | 8B                   | - | - | -   | -   | - | _ | 2       | 2      |

| JR cc, dst   | if cc is true<br>PC ← PC + X                                                                                                  | DA  |            | 0B-FB                | - | - | -   | _   | _ | - | 2       | 2      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Table 118. eZ8 CPU Instruction Summary (Continued)

| Assembly  |                           |     | ress<br>ode | _ Opcode(s) |    |   | Fla | ags |   |   | _ Fetch | Instr. |

|-----------|---------------------------|-----|-------------|-------------|----|---|-----|-----|---|---|---------|--------|

| Mnemonic  | Symbolic Operation        | dst | src         | (Hex)       |    | Z | S   | ٧   | D | Н | Cycles  |        |

| POPX dst  | dst ← @SP<br>SP ← SP + 1  | ER  |             | D8          | _  | - | _   | -   | - | - | 3       | 2      |

| PUSH src  | SP ← SP – 1               | R   |             | 70          | -  | - | -   | -   | - | - | 2       | 2      |

|           | @SP ← src                 | IR  |             | 71          | •  |   |     |     |   |   | 2       | 3      |

|           |                           | IM  |             | IF70        |    |   |     |     |   |   | 3       | 2      |

| PUSHX src | SP ← SP − 1<br>@SP ← src  | ER  |             | C8          | _  | _ | _   | _   | _ | _ | 3       | 2      |

| RCF       | C ← 0                     |     |             | CF          | 0  | _ | _   | _   | _ | _ | 1       | 2      |

| RET       | PC ← @SP<br>SP ← SP + 2   |     |             | AF          | -  | - | -   | -   | - | - | 1       | 4      |

| RL dst    |                           | R   |             | 90          | *  | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 91          | -  |   |     |     |   |   | 2       | 3      |

| RLC dst   | <u> </u>                  | R   |             | 10          | *  | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 11          | -  |   |     |     |   |   | 2       | 3      |

| RR dst    |                           | R   |             | E0          | *  | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  | _           | E1          | =" |   |     |     |   |   | 2       | 3      |

| RRC dst   | <u> </u>                  | R   |             | C0          | *  | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  |             | C1          | •  |   |     |     |   |   | 2       | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

# **General Purpose I/O Port Output Timing**

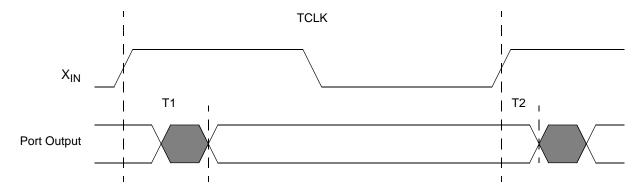

Figure 30 and Table 131 provide timing information for GPIO Port pins.

Figure 30. GPIO Port Output Timing

**Table 131. GPIO Port Output Timing**

|                |                                                 | Dela    | y (ns)  |

|----------------|-------------------------------------------------|---------|---------|

| Parameter      | Abbreviation                                    | Minimum | Maximum |

| GPIO Port p    | pins                                            |         |         |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _       | 15      |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2       | -       |

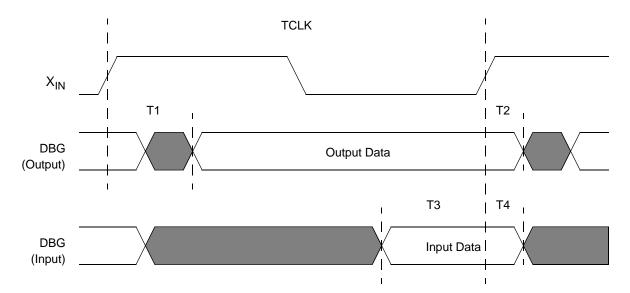

# **On-Chip Debugger Timing**

Figure 31 and Table 132 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 31. On-Chip Debugger Timing

Table 132. On-Chip Debugger Timing

|                |                                              | Dela    | y (ns)  |  |  |

|----------------|----------------------------------------------|---------|---------|--|--|

| Parameter      | Abbreviation                                 | Minimum | Maximum |  |  |

| DBG            |                                              |         |         |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | -       | 15      |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2       | _       |  |  |

| T <sub>3</sub> | DBG to X <sub>IN</sub> Rise Input Setup Time | 5       | _       |  |  |

| T <sub>4</sub> | DBG to X <sub>IN</sub> Rise Input Hold Time  | 5       | _       |  |  |

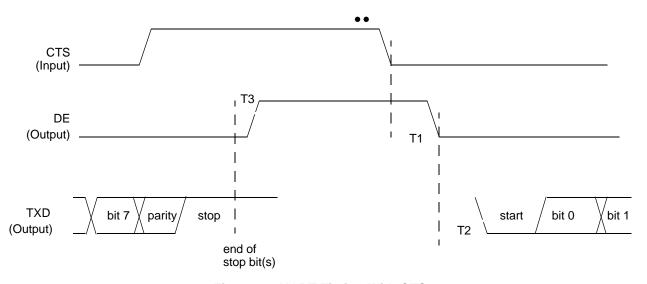

# **UART Timing**

Figure 32 and Table 133 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

Figure 32. UART Timing With CTS

**Table 133. UART Timing With CTS**

|                |                                                    | Dela                       | y (ns)                                     |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |

| UART           |                                                    |                            |                                            |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | +                          | : 5                                        |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ±                          | : 5                                        |

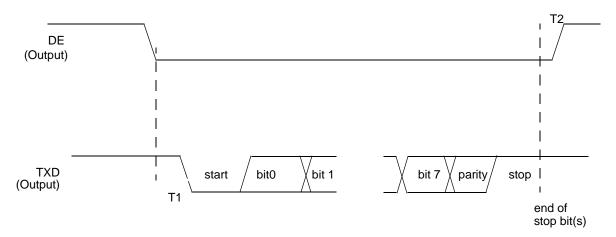

Figure 33 and Table 134 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 33. UART Timing Without CTS

**Table 134. UART Timing Without CTS**

|                |                                                                        | Delay                      | (ns)       |

|----------------|------------------------------------------------------------------------|----------------------------|------------|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |

| UART           |                                                                        |                            |            |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5                        |            |

214

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

| Table 100: 20 Endote: At 1 0020 defied of defining matrix (Contained) |           |         |           |            |                        |                     |                |                     |  |  |

|-----------------------------------------------------------------------|-----------|---------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|--|

| Part Number                                                           | Flash     | RAM     | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |

| Z8 Encore! XP F0823                                                   | Series v  | with 4  | KB Fla    | ash        |                        |                     |                |                     |  |  |

| Standard Temperature: 0°C to 70°C                                     |           |         |           |            |                        |                     |                |                     |  |  |

| Z8F0413PB005SG                                                        | 4 KB      | 1 KB    | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0413QB005SG                                                        | 4 KB      | 1 KB    | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |

| Z8F0413SB005SG                                                        | 4 KB      | 1 KB    | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0413SH005SG                                                        | 4 KB      | 1 KB    | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |

| Z8F0413HH005SG                                                        | 4 KB      | 1 KB    | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |

| Z8F0413PH005SG                                                        | 4 KB      | 1 KB    | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |

| Z8F0413SJ005SG                                                        | 4 KB      | 1 KB    | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |

| Z8F0413HJ005SG                                                        | 4 KB      | 1 KB    | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |

| Z8F0413PJ005SG                                                        | 4 KB      | 1 KB    | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |

| Extended Temperatu                                                    | ıre: –40° | C to 10 | 5°C       |            |                        |                     |                |                     |  |  |

| Z8F0413PB005EG                                                        | 4 KB      | 1 KB    | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0413QB005EG                                                        | 4 KB      | 1 KB    | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |

| Z8F0413SB005EG                                                        | 4 KB      | 1 KB    | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0413SH005EG                                                        | 4 KB      | 1 KB    | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |

| Z8F0413HH005EG                                                        | 4 KB      | 1 KB    | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |

| Z8F0413PH005EG                                                        | 4 KB      | 1 KB    | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |

| Z8F0413SJ005EG                                                        | 4 KB      | 1 KB    | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |

| Z8F0413HJ005EG                                                        | 4 KB      | 1 KB    | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |

| Z8F0413PJ005EG                                                        | 4 KB      | 1 KB    | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |