# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813sh005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Embedded in Life An TXYS Company

# **Table of Contents**

| Revision History                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures x                                                                                                                                                                                                                                                                                                   |

| List of Tables xii                                                                                                                                                                                                                                                                                                  |

| Overview1Features1Part Selection Guide2Block Diagram3CPU and Peripheral Overview4General-Purpose I/O4Flash Controller4Internal Precision Oscillator510-Bit Analog-to-Digital Converter5Analog Comparator5Universal Asynchronous Receiver/Transmitter5Timers5Interrupt Controller5Reset Controller5On-Chip Debugger6 |

| Pin Description7Available Packages7Pin Configurations7Signal Descriptions9Pin Characteristics11Address Space13Register File13Program Memory13                                                                                                                                                                       |

| Data Memory15Flash Information Area15                                                                                                                                                                                                                                                                               |

| Register Map                                                                                                                                                                                                                                                                                                        |

| Reset and Stop Mode Recovery21Reset Types21Reset Sources23Power-On Reset23Voltage Brown-Out Reset24Watchdog Timer Reset25                                                                                                                                                                                           |

An IXYS Company 6

## **On-Chip Debugger**

F0823 Series products feature an integrated On-Chip Debugger. The OCD provides a richset of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

ilog Embedded in Life An IXYS Company 17

| Address (Hex)    | Register Description      | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------|----------|-------------|-------------|

| Timer 1 (cont'd) |                           |          |             |             |

| F0A              | Timer 1 Reload High Byte  | T1RH     | FF          | <u>85</u>   |

| F0B              | Timer 1 Reload Low Byte   | T1RL     | FF          | <u>85</u>   |

| F0C              | Timer 1 PWM High Byte     | T1PWMH   | 00          | <u>86</u>   |

| F0D              | Timer 1 PWM Low Byte      | T1PWML   | 00          | <u>86</u>   |

| F0E              | Timer 1 Control 0         | T1CTL0   | 00          | <u>87</u>   |

| F0F              | Timer 1 Control 1         | T1CTL1   | 00          | <u>84</u>   |

| F10–F3F          | Reserved                  | —        | XX          |             |

| UART             |                           |          |             |             |

| F40              | UART0 Transmit Data       | U0TXD    | XX          | <u>109</u>  |

|                  | UART0 Receive Data        | U0RXD    | XX          | <u>109</u>  |

| F41              | UART0 Status 0            | U0STAT0  | 0000011Xb   | <u>110</u>  |

| F42              | UART0 Control 0           | U0CTL0   | 00          | <u>112</u>  |

| F43              | UART0 Control 1           | U0CTL1   | 00          | <u>112</u>  |

| F44              | UART0 Status 1            | U0STAT1  | 00          | <u>111</u>  |

| F45              | UART0 Address Compare     | U0ADDR   | 00          | <u>115</u>  |

| F46              | UART0 Baud Rate High Byte | U0BRH    | FF          | <u>115</u>  |

| F47              | UART0 Baud Rate Low Byte  | U0BRL    | FF          | <u>115</u>  |

| F48–F6F          | Reserved                  | —        | XX          |             |

| Analog-to-Digita | al Converter (ADC)        |          |             |             |

| F70              | ADC Control 0             | ADCCTL0  | 00          | <u>127</u>  |

| F71              | ADC Control 1             | ADCCTL1  | 80          | <u>127</u>  |

| F72              | ADC Data High Byte        | ADCD_H   | XX          | <u>130</u>  |

| F73              | ADC Data Low Bits         | ADCD_L   | XX          | <u>130</u>  |

| F74–F7F          | Reserved                  | _        | XX          |             |

| Low Power Con    | trol                      |          |             |             |

| F80              | Power Control 0           | PWRCTL0  | 80          | <u>32</u>   |

| F81              | Reserved                  | _        | XX          |             |

| LED Controller   |                           |          |             |             |

| F82              | LED Drive Enable          | LEDEN    | 00          | <u>51</u>   |

| F83              | LED Drive Level High Byte | LEDLVLH  | 00          | <u>52</u>   |

| Note: XX=Undefi  |                           |          |             |             |

## Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

34

# Architecture

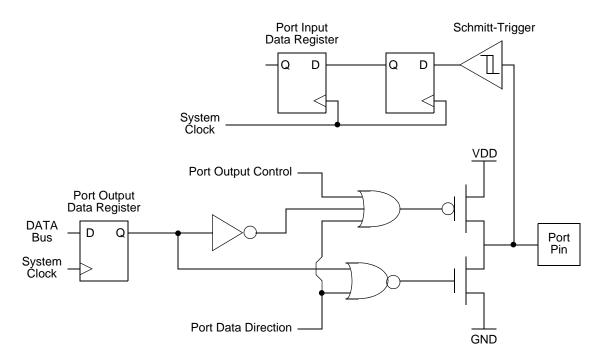

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

# **GPIO Alternate Functions**

Many of the GPIO port pins are used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The port A–D Alternate Function subregisters configure these pins for either GPIO or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Tables 16 and 17 list the alternate functions possible with each port pin for 8-pin and non-8-pin parts, respectively. The alternate function associated at a pin is defined through Alternate Function Sets subregisters AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

| Port                | Pin      | Mnemonic                      | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|----------|-------------------------------|--------------------------------|-----------------------------------------|

| Port B <sup>3</sup> | PB03     | Reserved                      |                                | AFS1[0]: 0                              |

|                     |          | ANA0                          | ADC Analog Input               | AFS1[0]: 1                              |

| PB1                 | Reserved |                               | AFS1[1]: 0                     |                                         |

|                     | ANA1     | ADC Analog Input              | AFS1[1]: 1                     |                                         |

|                     | PB2      | Reserved                      |                                | AFS1[2]: 0                              |

|                     |          | ANA2                          | ADC Analog Input               | AFS1[2]: 1                              |

|                     | PB3      | CLKIN                         | External Clock Input           | AFS1[3]: 0                              |

|                     |          | ANA3                          | ADC Analog Input               | AFS1[3]: 1                              |

|                     | PB4      | Reserved                      |                                | AFS1[4]: 0                              |

|                     |          | ANA7                          | ADC Analog Input               | AFS1[4]: 1                              |

|                     | PB5      | Reserved                      |                                | AFS1[5]: 0                              |

|                     |          | V <sub>REF</sub> <sup>4</sup> | ADC Voltage Reference          | AFS1[5]: 1                              |

|                     | PB6      | Reserved                      |                                | AFS1[6]: 0                              |

|                     |          | Reserved                      |                                | AFS1[6]: 1                              |

|                     | PB7      | Reserved                      |                                | AFS1[7]: 0                              |

|                     |          | Reserved                      |                                | AFS1[7]: 1                              |

#### Table 17. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in the <u>Port A–C Alternate Function</u> <u>Subregisters</u> section on page 43 automatically enables the associated alternate function.

2. Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in the <u>Timer Pin Signal Operation</u> section on page 83.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, alternate function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

4. V<sub>REF</sub> is available on PB5 in 28-pin products only.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

6. V<sub>REF</sub> is available on PC2 in 20-pin parts only.

### ilog° Embedded in Life An∎IXYS Company 47

### Port A–C Pull-up Enable Subregisters

The Port A–C Pull-up Enable Subregister (Table 27) is accessed through the Port A–C Control Register by writing 06H to the Port A–C Address Register. Setting the bits in the Port A–C Pull-up Enable subregisters enables a weak internal resistive pull-up on the specified Port pins.

| Bit     | 7                                                                                            | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |

|---------|----------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| Field   | PPUE7                                                                                        | PPUE6 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |  |  |

| RESET   | 0                                                                                            | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

| R/W     | R/W                                                                                          | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |  |

| Address | ddress If 06H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |       |  |  |  |

| Bit     | Description                                                                                  | n     |       |       |       |       |       |       |  |  |  |

### Table 27. Port A–C Pull-Up Enable Subregisters (PPUEx)

| BIt        | Description                                       |

|------------|---------------------------------------------------|

| [7:0]      | Port Pull-up Enabled                              |

| PPUEx      | 0 = The weak pull-up on the Port pin is disabled. |

|            | 1 = The weak pull-up on the Port pin is enabled.  |

| Note: x ir | ndicates the specific GPIO port pin number (7–0). |

#### ILOG<sup>°</sup> hbedded in Life IXYS Company 54

# Interrupt Controller

The interrupt controller on the Z8 Encore! XP F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u> available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 35 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

## **Software Interrupt Assertion**

Program code generates interrupts directly. Writing a 1 to the correct bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

Caution: Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

## Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the timeout condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

# Embedded in Life

## **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) register (Table 49) determines the source of the PADxS interrupts. The Shared Interrupt Select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit     | 7        | 6     | 5        | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|----------|-------|----------|-----|-----|-----|-----|-----|--|--|

| Field   | Reserved | PA6CS | Reserved |     |     |     |     |     |  |  |

| RESET   | 0        | 0     | 0        | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W      | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |          |       |          | FC  | EH  |     |     |     |  |  |

### Table 49. Shared Interrupt Select Register (IRQSS)

| Bit          | Description                                                                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]          | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                   |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The comparator is used as an interrupt for PA6CS interrupt requests.</li> </ul> |

| [5:0]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                           |

# Embedded in Life

### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a PWM output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps to configure a timer for PWM Single Output mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H); this write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 Register is set to indicate the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps to configure a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

#### ILOG Embedded in Life IXYS Company 104

scheme is enabled, the UART Address Compare register holds the network address of the device.

### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR Mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes

- Interrupt on matched address bytes and correctly framed data bytes

- Interrupt only on correctly framed data bytes

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare register. This mode introduces additional hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second

Figure 20. Flash Memory Arrangement

## **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

## Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

Figure 21 displays a basic Flash Controller flow. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

155

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 3C                   | FE3C              | Randomized Lot ID Byte 31 (most significant) |

| 3D                   | FE3D              | Randomized Lot ID Byte 30                    |

| 3E                   | FE3E              | Randomized Lot ID Byte 29                    |

| 3F                   | FE3F              | Randomized Lot ID Byte 28                    |

| 58                   | FE58              | Randomized Lot ID Byte 27                    |

| 59                   | FE59              | Randomized Lot ID Byte 26                    |

| 5A                   | FE5A              | Randomized Lot ID Byte 25                    |

| 5B                   | FE5B              | Randomized Lot ID Byte 24                    |

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

### Table 99. Randomized Lot ID Locations

ilog° Embedded in Life An∎IXYS Company

189

| Assembly      |                                            | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   |   | Fetch  | Instr. |

|---------------|--------------------------------------------|-----------------|-----|-------------|-------|---|---|---|---|---|--------|--------|

| Mnemonic      | Symbolic Operation                         | dst             | src | (Hex)       |       | Ζ | S | ۷ | D | Н | Cycles |        |

| SBC dst, src  | $dst \gets dst - src - C$                  | r               | r   | 32          | *     | * | * | * | 1 | * | 2      | 3      |

|               |                                            | r               | lr  | 33          | -     |   |   |   |   |   | 2      | 4      |

|               | -                                          | R               | R   | 34          | -     |   |   |   |   |   | 3      | 3      |

|               | -                                          | R               | IR  | 35          | -     |   |   |   |   |   | 3      | 4      |

|               |                                            | R               | IM  | 36          | _     |   |   |   |   |   | 3      | 3      |

|               | -                                          | IR              | IM  | 37          | -     |   |   |   |   |   | 3      | 4      |

| SBCX dst, src | $dst \gets dst - src - C$                  | ER              | ER  | 38          | *     | * | * | * | 1 | * | 4      | 3      |

|               | -                                          | ER              | IM  | 39          | -     |   |   |   |   |   | 4      | 3      |

| SCF           | C ← 1                                      |                 |     | DF          | 1     | _ | _ | - | _ | - | 1      | 2      |

| SRA dst       | **                                         | R               |     | D0          | *     | * | * | 0 | _ | - | 2      | 2      |

|               | D7_D6_D5_D4_D3_D2_D1_D0 ► C<br>dst         | IR              |     | D1          | -     |   |   |   |   |   | 2      | 3      |

| SRL dst       | 0 - <b>▶</b> D7 D6 D5 D4 D3 D2 D1 D0 - ▶ C | R               |     | 1F C0       | *     | * | 0 | * | _ | _ | 3      | 2      |

|               | dst                                        | IR              |     | 1F C1       | -     |   |   |   |   |   | 3      | 3      |

| SRP src       | $RP \leftarrow src$                        |                 | IM  | 01          | _     | _ | _ | _ | _ | _ | 2      | 2      |

| STOP          | STOP Mode                                  |                 |     | 6F          | -     | - | _ | - | _ | _ | 1      | 2      |

| SUB dst, src  | $dst \leftarrow dst - src$                 | r               | r   | 22          | *     | * | * | * | 1 | * | 2      | 3      |

|               | -                                          | r               | lr  | 23          | -     |   |   |   |   |   | 2      | 4      |

|               | -                                          | R               | R   | 24          | -     |   |   |   |   |   | 3      | 3      |

|               |                                            | R               | IR  | 25          | -     |   |   |   |   |   | 3      | 4      |

|               |                                            | R               | IM  | 26          | -     |   |   |   |   |   | 3      | 3      |

|               |                                            | IR              | IM  | 27          | -     |   |   |   |   |   | 3      | 4      |

| SUBX dst, src | $dst \gets dst - src$                      | ER              | ER  | 28          | *     | * | * | * | 1 | * | 4      | 3      |

|               |                                            | ER              | IM  | 29          | -     |   |   |   |   |   | 4      | 3      |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$        | R               |     | F0          | Х     | * | * | Х | - | _ | 2      | 2      |

|               | -                                          | IR              |     | F1          | -     |   |   |   |   |   | 2      | 3      |

### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

199

|                           |                                                   | VD                   | <sub>D</sub> = 2.7V to 3         | 8.6V                             |    |                                                                   |

|---------------------------|---------------------------------------------------|----------------------|----------------------------------|----------------------------------|----|-------------------------------------------------------------------|

| Symbol                    | Parameter                                         | Typical <sup>1</sup> | Maximum <sup>2</sup><br>Std Temp | Maximum <sup>3</sup><br>Ext Temp |    | Conditions                                                        |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                    | 0.1                  | 2                                | 7.5                              | μA | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}$ . |

| I <sub>DD</sub> Halt      | Supply Current in HALT                            | 35                   | 55                               | 65                               | μA | 32kHz.                                                            |

|                           | Mode (with all peripher-                          | 520                  | 630                              | 700                              | μA | 5.5MHz.                                                           |

| I <sub>DD</sub>           | Supply Current in                                 | 2.8                  | 4.5                              | 4.8                              | mA | 32kHz.                                                            |

|                           | ACTIVE Mode (with all peripherals disabled)       | 4.5                  | 5.2                              | 5.2                              | mA | 5.5MHz.                                                           |

| I <sub>DD</sub> WDT       | Watchdog Timer Sup-<br>ply Current                | 0.9                  | 1.0                              | 1.1                              | μA |                                                                   |

| I <sub>DD</sub> IPO       | Internal Precision Oscil-<br>lator Supply Current | 350                  | 500                              | 550                              | μA |                                                                   |

| I <sub>DD</sub> VBO       | Voltage Brown-Out Sup-<br>ply Current             | 50                   |                                  |                                  | μA | For 20-/28-pin devices (VBO only). <sup>4</sup>                   |

|                           | -                                                 |                      |                                  |                                  |    | For 8-pin devices. <sup>4</sup>                                   |

| I <sub>DD</sub> ADC       | Analog-to-Digital Con-                            | 2.8                  | 3.1                              | 3.2                              | mA | 32kHz.                                                            |

|                           | verter Supply Current                             | 3.1                  | 3.6                              | 3.7                              | mA | 5.5MHz.                                                           |

|                           | (with External Refer-                             | 3.3                  | 3.7                              | 3.8                              | mA | 10MHz.                                                            |

|                           | ,<br>-                                            | 3.7                  | 4.2                              | 4.3                              | mA | 20MHz.                                                            |

| I <sub>DD</sub><br>ADCRef | ADC Internal Refer-<br>ence Supply Current        | 0                    |                                  |                                  | μA | See Note 4.                                                       |

| I <sub>DD</sub> CMP       | Comparator supply Cur-<br>rent                    | 150                  | 180                              | 190                              | μA | See Note 4.                                                       |

| I <sub>DD</sub> BG        | Band Gap Supply Cur-                              | 320                  | 480                              | 500                              | μA | For 20-/28-pin devices.<br>For 8-pin devices.                     |

#### Table 122. Power Consumption

Notes:

1. Typical conditions are defined as  $V_{DD}$  = 3.3 V and +30°C.

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

ilog Embedded in Life An IXYS Company 202

|                                               | $T_A = -$ | = 2.7V to<br>-40°C to +<br>otherwise | 105°C   |        |                                                                                                                                                                  |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  | Notes                                                                                                                                                            |

| Flash Byte Read Time                          | 100       | _                                    | _       | ns     |                                                                                                                                                                  |

| Flash Byte Program Time                       | 20        | _                                    | 40      | μs     |                                                                                                                                                                  |

| Flash Page Erase Time                         | 10        | _                                    | _       | ms     |                                                                                                                                                                  |

| Flash Mass Erase Time                         | 200       | _                                    | _       | ms     |                                                                                                                                                                  |

| Writes to Single Address<br>Before Next Erase | -         | -                                    | 2       |        |                                                                                                                                                                  |

| Flash Row Program Time                        | -         | _                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This param-<br>eter is only an issue when<br>bypassing the Flash Controller. |

| Data Retention                                | 100       | _                                    | _       | years  | 25°C                                                                                                                                                             |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                             |

### Table 126. Flash Memory Electrical Characteristics and Timing

### Table 127. Watchdog Timer Electrical Characteristics and Timing

|                          | V <sub>DD</sub> = 2.7V to 3.6V<br>T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise stated) |         |         |             |       |                                                                                              |

|--------------------------|-------------------------------------------------------------------------------------------------|---------|---------|-------------|-------|----------------------------------------------------------------------------------------------|

| Symbol                   | Parameter                                                                                       | Minimum | Typical | Maximum     | Units | Conditions                                                                                   |

| F <sub>WDT</sub>         | WDT Oscillator Frequency                                                                        |         | 10      |             | kHz   |                                                                                              |

| F <sub>WDT</sub>         | WDT Oscillator Error                                                                            |         |         | <u>+</u> 50 | %     |                                                                                              |

| T <sub>WDT-</sub><br>CAL | WDT Calibrated Timeout                                                                          | 0.98    | 1       | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30°C                                            |

|                          |                                                                                                 | 0.70    | 1       | 1.30        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = 0^{\circ} C \text{ to } 70^{\circ} C$           |

|                          |                                                                                                 | 0.50    | 1       | 1.50        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = -40^{\circ} \text{C to } +105^{\circ} \text{C}$ |

### ilog<sup>°</sup> Embedded in Life An IXYS Company 206

# General Purpose I/O Port Output Timing

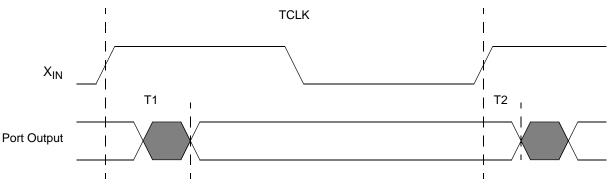

Figure 30 and Table 131 provide timing information for GPIO Port pins.

|                |                                                 | Delay (ns) |         |  |  |  |  |

|----------------|-------------------------------------------------|------------|---------|--|--|--|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |  |  |  |

| GPIO Port pins |                                                 |            |         |  |  |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _          | 15      |  |  |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |  |  |  |  |

### Table 131. GPIO Port Output Timing

208

## UART Timing

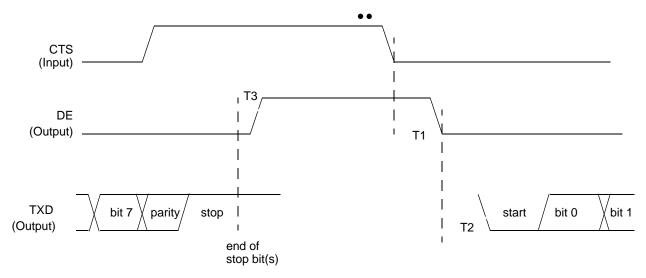

Figure 32 and Table 133 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

Figure 32. UART Timing With CTS

|                |                                                    | Delay (ns)                 |                                            |  |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|--|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |  |  |

| UART           |                                                    |                            |                                            |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | Ŧ                          | : 5                                        |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ±                          | : 5                                        |  |  |

| Table | 133  | UART | Timing  | With   | CTS |

|-------|------|------|---------|--------|-----|

| Table | 155. |      | rinning | WWILII | 010 |

> ilog Embedded in Life An IXYS Company 213

| Part Number                          | Flash<br>RAM  |        | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|--------------------------------------|---------------|--------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP F0823                  | Series with   | 4 KB F | ash, 10    | )-Bit Ar               | nalog-t             | o-Digi         | tal Converter       |

| Standard Temperatur                  | re: 0°C to 70 | °C     |            |                        |                     |                |                     |

| Z8F0423PB005SG                       | 4 KB 1 K      | B 6    | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005SG                       | 4 KB 1 K      | B 6    | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005SG                       | 4 KB 1 K      | B 6    | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005SG                       | 4 KB 1 K      | B 16   | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005SG                       | 4 KB 1 K      | B 16   | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005SG                       | 4 KB 1 K      | B 16   | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005SG                       | 4 KB 1 K      | B 22   | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005SG                       | 4 KB 1 K      | B 22   | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005SG                       | 4 KB 1 K      | B 22   | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: –40°C to 105°C |               |        |            |                        |                     |                |                     |

| Z8F0423PB005EG                       | 4 KB 1 K      | B 6    | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005EG                       | 4 KB 1 K      | B 6    | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005EG                       | 4 KB 1 K      | B 6    | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005EG                       | 4 KB 1 K      | B 16   | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005EG                       | 4 KB 1 K      | B 16   | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005EG                       | 4 KB 1 K      | B 16   | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005EG                       | 4 KB 1 K      | B 22   | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005EG                       | 4 KB 1 K      | B 22   | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005EG                       | 4 KB 1 K      | B 22   | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

## Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)