Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813sj005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ilog<sup>®</sup>

ii

## **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

## LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2011 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

# List of Figures

| Figure 1.  | Z8 Encore! XP F0823 Series Block Diagram 3                                           |

|------------|--------------------------------------------------------------------------------------|

| Figure 2.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package        |

| Figure 3.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package             |

| Figure 4.  | Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package             |

| Figure 5.  | Power-On Reset Operation                                                             |

| Figure 6.  | Voltage Brown-Out Reset Operation                                                    |

| Figure 7.  | GPIO Port Pin Block Diagram                                                          |

| Figure 8.  | Interrupt Controller Block Diagram                                                   |

| Figure 9.  | Timer Block Diagram                                                                  |

| Figure 10. | UART Block Diagram                                                                   |

| Figure 11. | UART Asynchronous Data Format without Parity                                         |

| Figure 12. | UART Asynchronous Data Format with Parity                                            |

| Figure 13. | UART Asynchronous MULTIPROCESSOR Mode Data Format 103                                |

| Figure 14. | UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity) 105              |

| Figure 15. | UART Receiver Interrupt Service Routine Flow                                         |

| Figure 16. | Infrared Data Communication System Block Diagram 117                                 |

| Figure 17. | Infrared Data Transmission                                                           |

| Figure 18. | IrDA Data Reception                                                                  |

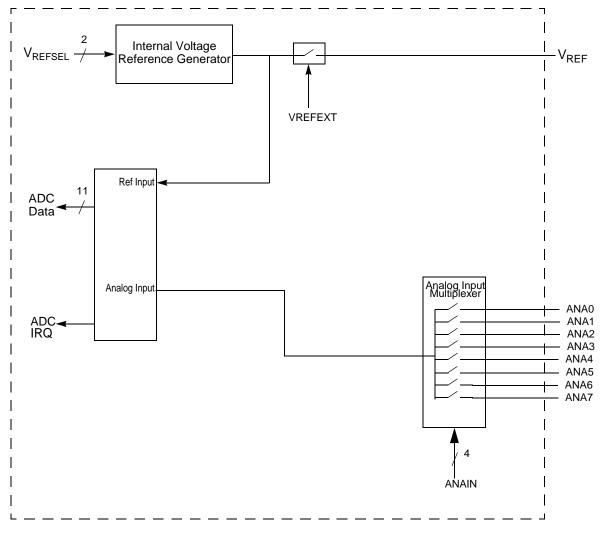

| Figure 19. | Analog-to-Digital Converter Block Diagram 122                                        |

| Figure 20. | Flash Memory Arrangement 135                                                         |

| Figure 21. | Flash Controller Operation Flowchart                                                 |

| Figure 22. | On-Chip Debugger Block Diagram 156                                                   |

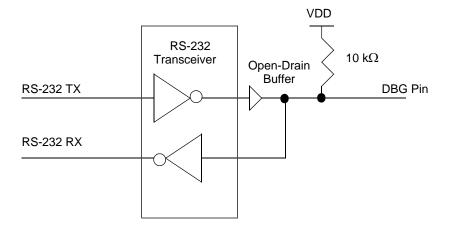

| Figure 23. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface,<br># 1 of 2 157 |

| Figure 24. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface,<br># 2 of 2     |

| Figure 25. | OCD Data Format                                                                      |

| Figure 26. | Opcode Map Cell Description 192                                                      |

| Figure 27. | First Opcode Map                                                                     |

| Figure 28. | Second Opcode Map after 1FH 195                                                      |

| Figure 29. | Port Input Sample Timing 205                                                         |

#### ilog<sup>°</sup> Embedded in Life An ∎IXYS Company

5

## **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

## **10-Bit Analog-to-Digital Converter**

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

## **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

## **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

## Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

## **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

## **Reset Controller**

Z8 Encore!  $XP^{\text{(B)}}$  F0823 Series products can be reset using the RESET pin, POR, WDT time-out, STOP Mode exit, or Voltage Brown-Out warning signal. The RESET pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

## **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see **the** <u>Port A–C Control Registers</u> **section on page 42**), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overrightarrow{\text{RESET}}$  pin Low. The  $\overrightarrow{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

## **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

## **Stop Mode Recovery**

The device enters into STOP Mode when eZ8 CPU executes a STOP instruction. For more details about STOP Mode, see **the** Low-Power Modes **section on page 30**. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

#### ilog° Embedded in Life An∎IXYS Company

#### 29

| Bit        | Description (Continued)                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>EXT | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset<br>or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register |

|            | resets this bit. For POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                               |

| [3:0]      | Reserved                                                                                                                                                                                                                    |

These bits are reserved and must be programmed to 0000 when read.

## Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

34

# Architecture

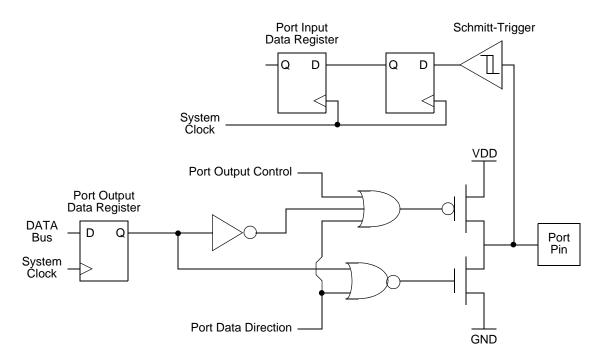

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

# **GPIO Alternate Functions**

Many of the GPIO port pins are used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The port A–D Alternate Function subregisters configure these pins for either GPIO or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Tables 16 and 17 list the alternate functions possible with each port pin for 8-pin and non-8-pin parts, respectively. The alternate function associated at a pin is defined through Alternate Function Sets subregisters AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

## ilog° Embedded in Life An TXYS Company

61

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 38) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit                                                          | 7                                                                   | 6                           | 5     | 4 | 3    | 2    | 1    | 0    |

|--------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------|-------|---|------|------|------|------|

| Field                                                        |                                                                     | Rese                        | erved |   | PC3I | PC2I | PC1I | PC0I |

| RESET                                                        | 0                                                                   | 0                           | 0     | 0 | 0    | 0    | 0    | 0    |

| R/W                                                          | R/W                                                                 | R/W R/W R/W R/W R/W R/W R/W |       |   |      |      |      |      |

| Address                                                      |                                                                     | FC6H                        |       |   |      |      |      |      |

| Bit                                                          | Description                                                         |                             |       |   |      |      |      |      |

| [7:4]                                                        | Reserved<br>These bits are reserved and must be programmed to 0000. |                             |       |   |      |      |      |      |

| [3:0]<br>PCxI                                                |                                                                     |                             |       |   |      |      |      |      |

| Note: x indicates the specific GPIO Port C pin number (3–0). |                                                                     |                             |       |   |      |      |      |      |

#### Table 38. Interrupt Request 2 Register (IRQ2)

## **IRQ0 Enable High and Low Bit Registers**

Table 39 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 40 and Table 41) form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register. Priority is generated by setting bits in each register.

| Table 39. IRQ0 Enable and Priority Encoding |

|---------------------------------------------|

|---------------------------------------------|

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Note: where x indicates the register bits from 0–7.

nbedded in Life

81

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The compare time can be calculated by the following equation:

COMPARE Mode Time (s) = (Compare Value – Start Value) × Prescale System Clock Frequency (Hz)

## **GATED Mode**

In GATED Mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following steps to configure a timer for GATED Mode and to initiate the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL1 Register.

00

103

- 1. Checks the UART Status 0 Register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data Register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) Mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

## **Clear To Send (CTS) Operation**

The CTS pin, if enabled by the CTSE bit of the UART Control 0 Register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

## **MULTIPROCESSOR (9-Bit) Mode**

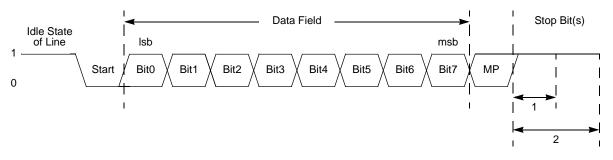

The UART has a MULTIPROCESSOR (9-bit) Mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTI-PROCESSOR Mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is given below:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) Mode, the parity bit location (9<sup>th</sup> bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPRO-CESSOR (9-bit) Mode control and status information. If an automatic address matching

#### ilog° Embedded in Life An∎IXYS Company 106

## **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

## **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error

Figure 19. Analog-to-Digital Converter Block Diagram

## Operation

The output of the ADC is an 11-bit, signed, two's-complement digital value. The output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers return 13 bits of data, but the two LSBs are intended for compensation use only. When the compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

edded in Life

132

# Comparator

Z8 Encore! XP F0823 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex.

The features of the comparator include:

- Two inputs which can be connected up using the GPIO multiplex (MUX)

- One input can be connected to a programmable internal reference

- One input can be connected to the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

## Operation

One of the comparator inputs can be connected to an internal reference which is a user selectable reference that is user programmable with 200 mV resolution.

The comparator can be powered down to save on supply current. For details, see the <u>Power</u> <u>Control Register 0</u> section on page 31.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

The following example shows how to safely enable the comparator:

```

di

ld cmp0

nop

i, wait for output to settle

clr irq0; clear any spurious interrupts pending

ei

```

ilog<sup>®</sup>

143

## Flash Status Register

The Flash Status Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

| Bit     | 7          | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|---------|------------|-------|-------|---|---|---|---|---|

| Field   | Rese       | erved | FSTAT |   |   |   |   |   |

| RESET   | 0          | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

| R/W     | R          | R     | R     | R | R | R | R | R |

| Address | FF8H       |       |       |   |   |   |   |   |

| Bit     | Descriptio | n     |       |   |   |   |   |   |

| Table 82 | . Flash | Status | Register | (FSTAT) |

|----------|---------|--------|----------|---------|

|----------|---------|--------|----------|---------|

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 0 when read.                                                                                                                                                                                                                                                                                           |

| [5:0]<br>FSTAT | Flash Controller Status000000 = Flash Controller locked.000001 = First unlock command received (73H written).000010 = Second unlock command received (8CH written).000011 = Flash Controller unlocked.000100 = Sector protect register selected.001xxx = Program operation in progress.010xxx = Page erase operation in progress.100xxx = Mass erase operation in progress. |

## Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

#### ilog<sup>°</sup> Embedded in Life An TIXYS Company 158

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 2 of 2

## **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled.

## **Entering DEBUG Mode**

The device enters DEBUG Mode following the operations below:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (breakpoint) instruction

- If the DBG pin is held Low during the most recent clock cycle of System Reset, the part enters DEBUG Mode upon exiting System Reset

• Note: Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an autobaud sequence (see the <u>OCD Autobaud Detector/</u><u>Generator section on page 159</u>).

#### ilog Embedded in Life An IXYS Company 162

# **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of Z8 Encore! XP F0823 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 101 is a summary of the OCD commands. Each OCD command is described in further detail in the pages that follow this table. <u>Table 102</u> on page 167 also indicates those commands that operate when the device is not in DEBUG Mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                                     |

|----------------------------|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                | -                                                                                                                                                                                |

| Reserved                   | 01H             | _                                  | -                                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                                | -                                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                                  | -                                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                                | Cannot clear DBGMODE bit.                                                                                                                                                        |

| Read OCD Control Register  | 05H             | Yes                                | -                                                                                                                                                                                |

| Write Program Counter      | 06H             | _                                  | Disabled.                                                                                                                                                                        |

| Read Program Counter       | 07H             | _                                  | Disabled.                                                                                                                                                                        |

| Write Register             | 08H             | _                                  | Only writes of the Flash Memory Con-<br>trol registers are allowed. Additionally,<br>only the Mass Erase command is<br>allowed to be written to the Flash Con-<br>trol Register. |

| Read Register              | 09H             | _                                  | Disabled.                                                                                                                                                                        |

| Write Program Memory       | 0AH             | _                                  | Disabled.                                                                                                                                                                        |

| Read Program Memory        | 0BH             | _                                  | Disabled.                                                                                                                                                                        |

| Write Data Memory          | 0CH             | _                                  | Yes.                                                                                                                                                                             |

| Read Data Memory           | 0DH             | _                                  | -                                                                                                                                                                                |

| Read Program Memory CRC    | 0EH             | _                                  | -                                                                                                                                                                                |

| Reserved                   | 0FH             | _                                  | -                                                                                                                                                                                |

| Step Instruction           | 10H             | _                                  | Disabled.                                                                                                                                                                        |

| Stuff Instruction          | 11H             | _                                  | Disabled.                                                                                                                                                                        |

| Execute Instruction        | 12H             | _                                  | Disabled.                                                                                                                                                                        |

| Reserved                   | 13H–FFH         | _                                  | -                                                                                                                                                                                |

#### Table 101. OCD Commands

## Embedded in Life An IXYS Company

# **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

| Table 103. OCD Status | Register (OCDSTAT) |

|-----------------------|--------------------|

|-----------------------|--------------------|

| Bit   | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |  |  |

|-------|-----|------|--------|----------|---|---|---|---|--|--|--|

| Field | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |  |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |  |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |  |  |

|       |     |      |        |          |   |   |   |   |  |  |  |

| Bit           | Description                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBG    | Debug Status<br>0 = NORMAL Mode.<br>1 = DEBUG Mode.                                                                                |

| [6]<br>HALT   | HALT Mode<br>0 = Not in HALT Mode.<br>1 = In HALT Mode.                                                                            |

| [5]<br>FRPENB | Flash Read Protect Option Bit Enable<br>0 = FRP bit enabled to allow disabling of many OCD commands.<br>1 = FRP bit has no effect. |

| [4:0]         | Reserved<br>These bits are reserved and must be 00000 when read.                                                                   |

Embedded in Life

ilog

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

| SRL      | dst      | Shift Right Logical        |

| SWAP     | dst      | Swap Nibbles               |

#### Table 117. Rotate and Shift Instructions (Continued)

# eZ8 CPU Instruction Summary

Table 118 summarizes the eZ8 CPU instruction set. The table identifies the addressing modes employed by the instruction, the effect upon the Flags Register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly      |                           | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   |   | _ Fetch | Instr. |

|---------------|---------------------------|-----------------|-----|-------------|-------|---|---|---|---|---|---------|--------|

| Mnemonic      | Symbolic Operation        | dst             | src | (Hex)       | С     | Ζ | S | ۷ | D | Н | Cycles  |        |

| ADC dst, src  | $dst \gets dst + src + C$ | r               | r   | 12          | *     | * | * | * | 0 | * | 2       | 3      |

|               |                           | r               | lr  | 13          |       |   |   |   |   |   | 2       | 4      |

|               |                           | R               | R   | 14          |       |   |   |   |   |   | 3       | 3      |

|               |                           | R               | IR  | 15          |       |   |   |   |   |   | 3       | 4      |

|               |                           | R               | IM  | 16          |       |   |   |   |   |   | 3       | 3      |

|               |                           | IR              | IM  | 17          |       |   |   |   |   |   | 3       | 4      |

| ADCX dst, src | $dst \gets dst + src + C$ | ER              | ER  | 18          | *     | * | * | * | 0 | * | 4       | 3      |

|               |                           | ER              | IM  | 19          |       |   |   |   |   |   | 4       | 3      |

#### Table 118. eZ8 CPU Instruction Summary

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

Embedded in Life

|                          |                                                    | $T_A =$    | = 3.0V to<br>= 0°C to +7<br>otherwise | ′0°C       |                                |                                                                                                |  |  |

|--------------------------|----------------------------------------------------|------------|---------------------------------------|------------|--------------------------------|------------------------------------------------------------------------------------------------|--|--|

| Symbol                   | Parameter                                          | Minimum    | Typical                               | Maximum    | Units                          | Conditions                                                                                     |  |  |

|                          | Resolution                                         | 10         |                                       | -          | bits                           |                                                                                                |  |  |

|                          | Differential Nonlinearity<br>(DNL)                 | -1.0       | -                                     | 1.0        | LSB <sup>3</sup>               | External V <sub>REF</sub> = 2.0V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$                |  |  |

|                          | Integral Nonlinearity (INL)                        | -3.0       | -                                     | 3.0        | LSB <sup>3</sup>               | External V <sub>REF</sub> = 2.0V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$                |  |  |

|                          | Offset Error with Calibration                      |            | <u>+</u> 1                            |            | LSB <sup>3</sup>               |                                                                                                |  |  |

|                          | Absolute Accuracy with Calibration                 |            | <u>+</u> 3                            |            | LSB <sup>3</sup>               |                                                                                                |  |  |

| V <sub>REF</sub>         | Internal Reference Voltage                         | 1.0<br>2.0 | 1.1<br>2.2                            | 1.2<br>2.4 | V                              | REFSEL=01<br>REFSEL=10                                                                         |  |  |

| V <sub>REF</sub>         | Internal Reference Varia-<br>tion with Temperature |            | <u>+</u> 1.0                          |            | %                              | Temperature variation with $V_{DD} = 3.0$                                                      |  |  |

| V <sub>REF</sub>         | Internal Reference Voltage Variation with $V_{DD}$ |            | <u>+</u> 0.5                          |            | %                              | Supply voltage varia-<br>tion with $T_A = 30^{\circ}C$                                         |  |  |

| R <sub>RE-</sub><br>FOUT | Reference Buffer Output<br>Impedance               |            | 850                                   |            | W                              | When the internal ref-<br>erence is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |  |  |

|                          | Single-Shot Conversion<br>Time                     | _          | 5129                                  | _          | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                        |  |  |

|                          |                                                    |            | 10258                                 |            |                                | Temperature sensor measurement                                                                 |  |  |

|                          | Continuous Conversion<br>Time                      | -          | 256                                   | -          | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                        |  |  |

|                          |                                                    |            | 512                                   |            |                                | Temperature sensor measurement                                                                 |  |  |

#### Table 128. Analog-to-Digital Converter Electrical Characteristics and Timing

Notes:

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- Devices are factory calibrated at V<sub>DD</sub> = 3.3 V and T<sub>A</sub> = +30°C, so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

#### ILOG<sup>°</sup> Inbedded in Life IXYS Company **210**

# Packaging

Zilog's F0823 Series of MCUs includes the Z8F0113, Z8F0123, Z8F0213, Z8F0223, Z8F0413, Z8F0423, Z8F0813 and Z8F0823 devices, which are available in the following packages:

- 8-pin Plastic Dual Inline Package (PDIP)

- 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S<sup>1</sup>

- 20-pin Plastic Dual-Inline Package (PDIP)

- 20-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Small Shrink Outline Package (SSOP)

- 28-pin Plastic Dual-Inline Package (PDIP)

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Small Shrink Outline Package (SSOP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

<sup>1.</sup> The footprint of the QFN)/MLF-S package is identical to that of the 8-pin SOIC package, but with a lower profile.

> ilog Embedded in Life An IXYS Company 217

|                                   |           |          |           |            |                        |                     | •              | · · · ·             |  |  |

|-----------------------------------|-----------|----------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|--|

| Part Number                       | Flash     | RAM      | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |

| Z8 Encore! XP F0823               | 3 Series  | with 1 I | KB Fla    | ash, 10    | -Bit An                | alog-1              | to-Digi        | tal Converter       |  |  |

| Standard Temperature: 0°C to 70°C |           |          |           |            |                        |                     |                |                     |  |  |

| Z8F0123PB005SG                    | 1 KB      | 256 B    | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0123QB005SG                    | 1 KB      | 256 B    | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |

| Z8F0123SB005SG                    | 1 KB      | 256 B    | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0123SH005SG                    | 1 KB      | 256 B    | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |

| Z8F0123HH005SG                    | 1 KB      | 256 B    | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |

| Z8F0123PH005SG                    | 1 KB      | 256 B    | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |

| Z8F0123SJ005SG                    | 1 KB      | 256 B    | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |

| Z8F0123HJ005SG                    | 1 KB      | 256 B    | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |

| Z8F0123PJ005SG                    | 1 KB      | 256 B    | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |

| Extended Temperatu                | ure: –40° | C to 10  | 5°C       |            |                        |                     |                |                     |  |  |

| Z8F0123PB005EG                    | 1 KB      | 256 B    | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0123QB005EG                    | 1 KB      | 256 B    | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |

| Z8F0123SB005EG                    | 1 KB      | 256 B    | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0123SH005EG                    | 1 KB      | 256 B    | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |

| Z8F0123HH005EG                    | 1 KB      | 256 B    | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |

| Z8F0123PH005EG                    | 1 KB      | 256 B    | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |

| Z8F0123SJ005EG                    | 1 KB      | 256 B    | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |

| Z8F0123HJ005EG                    | 1 KB      | 256 B    | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |

| Z8F0123PJ005EG                    | 1 KB      | 256 B    | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |

## Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)