Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | · .                                                       |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813sj005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

16

n 🗖 IXYS Company

# **Register Map**

Table 8 lists an address map of the Z8 Encore! XP F0823 Series Register File. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, nor all GPIO ports. Consider registers for unimplemented peripherals to be reserved.

| Address (Hex)  | Register Description              | Mnemonic      | Reset (Hex) | Page<br>No. |

|----------------|-----------------------------------|---------------|-------------|-------------|

| General-Purpos | e RAM                             |               |             |             |

| Z8F0823/Z8F081 | 13 Devices                        |               |             |             |

| 000–3FF        | General-Purpose Register File RAM | _             | XX          |             |

| 400-EFF        | Reserved                          | _             | XX          |             |

| Z8F0423/Z8F041 | 13 Devices                        |               |             |             |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |             |

| 400–EFF        | Reserved                          | _             | XX          |             |

| Z8F0223/Z8F021 | 13 Devices                        |               |             |             |

| 000–1FF        | General-Purpose Register File RAM |               | XX          |             |

| 200–EFF        | Reserved                          | _             | XX          |             |

| Z8F0123/Z8F011 | 13 Devices                        |               |             |             |

| 000–0FF        | General-Purpose Register File RAM |               | XX          |             |

| 100-EFF        | Reserved                          | _             | XX          |             |

| Timer 0        |                                   |               |             |             |

| F00            | Timer 0 High Byte                 | T0H           | 00          | <u>84</u>   |

| F01            | Timer 0 Low Byte                  | TOL           | 01          | <u>84</u>   |

| F02            | Timer 0 Reload High Byte          | TORH          | FF          | <u>85</u>   |

| F03            | Timer 0 Reload Low Byte           | TORL          | FF          | <u>85</u>   |

| F04            | Timer 0 PWM High Byte             | <b>T0PWMH</b> | 00          | <u>86</u>   |

| F05            | Timer 0 PWM Low Byte              | TOPWML        | 00          | <u>86</u>   |

| F06            | Timer 0 Control 0                 | TOCTLO        | 00          | <u>87</u>   |

| F07            | Timer 0 Control 1                 | T0CTL1        | 00          | <u>88</u>   |

| Timer 1        |                                   |               |             |             |

| F08            | Timer 1 High Byte                 | T1H           | 00          | <u>84</u>   |

| F09            | Timer 1 Low Byte                  | T1L           | 01          | <u>84</u>   |

#### Table 8. Register File Address Map

Note: XX=Undefined.

#### ilog° Embedded in Life An∎IXYS Company

#### 29

| Bit        | Description (Continued)                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>EXT | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A Power-On Reset<br>or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register |

|            | resets this bit. For POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                               |

| [3:0]      | Reserved                                                                                                                                                                                                                    |

These bits are reserved and must be programmed to 0000 when read.

#### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

#### ILOG<sup>°</sup> hbedded in Life IXYS Company 30

# Low-Power Modes

Z8 Encore! XP F0823 Series products contain power-saving features. The highest level of power reduction is provided by the STOP Mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT Mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in ACTIVE mode (defined as being in neither STOP nor HALT Mode).

## **STOP Mode**

Executing the eZ8 CPU's Stop instruction places the device into STOP Mode, powering down all peripherals except the Voltage Brown-Out detector, and the Watchdog Timer. These two blocks may also be disabled for additional power savings. In STOP Mode, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; X<sub>IN</sub> and X<sub>OUT</sub> (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers

- System clock is stopped

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control Register

- If enabled, the Watchdog Timer logic continues to operate

- If enabled for operation in STOP Mode by the associated Flash Option Bit, the Voltage Brown-Out protection circuit continues to operate

- All other on-chip peripherals are idle

To minimize current in STOP Mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP Mode using Stop Mode Recovery. For more information about Stop Mode Recovery, see the <u>Reset and Stop Mode Recovery</u> chapter on page 21.

| Z8 Encore! XP <sup>®</sup> F082<br>Product Spec |      |

|-------------------------------------------------|------|

|                                                 | ilog |

Embedded in Life An IXYS Company 70

## Architecture

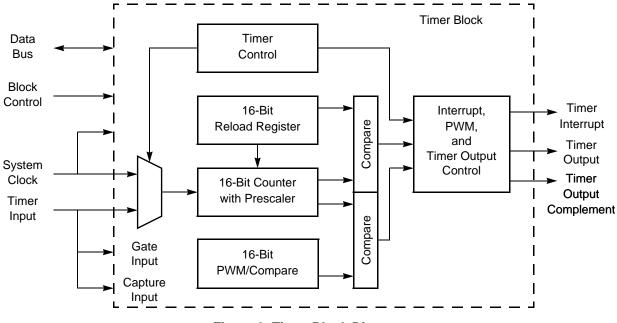

Figure 9 displays the architecture of the timers.

Figure 9. Timer Block Diagram

## Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

# Embedded in Life

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a PWM output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps to configure a timer for PWM Single Output mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H); this write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

#### ilog Embedded in Life An∎IXYS Company 80

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture or a reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) = (Capture Value – Start Value) × Prescale System Clock Frequency (Hz)

#### **COMPARE Mode**

In COMPARE Mode, the timer counts up to the 16-bit maximum compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting. Observe the following steps to configure a timer for COMPARE Mode and to initiate the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

nbedded in Life

7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

#### **Timer Pin Signal Operation**

Timer Output is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

## **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

Timer 0-1 High and Low Byte Registers: see page 83

Timer Reload High and Low Byte Registers: see page 84

Timer 0-1 PWM High and Low Byte Registers: see page 86

Timer 0-1 Control Registers: see page 86

#### Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers (Table 51 and Table 52) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH

#### WDT Reset in NORMAL Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Watchdog Timer Control Register is set to 1. For more information about System Reset, see **the** <u>Reset and Stop</u> <u>Mode Recovery</u> chapter on page 21.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following WDT time-out in STOP Mode. For more information, see **the** <u>Reset and Stop Mode Recovery</u> chapter on page 21.

#### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer Control Register (WDTCTL) address unlocks the three Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. The following sequence is required to unlock the Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register (WDTCTL): see page 94

Watchdog Timer Reload Upper Byte Register (WDTU): see page 95

## Embedded in Life An IXYS Company 97

# Universal Asynchronous Receiver/ Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. The features of UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) Mode with three configurable interrupt schemes

- BRG can be configured and used as a basic 16-bit timer

- Driver Enable output for external bus transceivers

## Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

#### ILOG Embedded in Life IXYS Company 104

scheme is enabled, the UART Address Compare register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR Mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes

- Interrupt on matched address bytes and correctly framed data bytes

- Interrupt only on correctly framed data bytes

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare register. This mode introduces additional hard-ware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### ilog Embedded in Life An IXYS Company 117

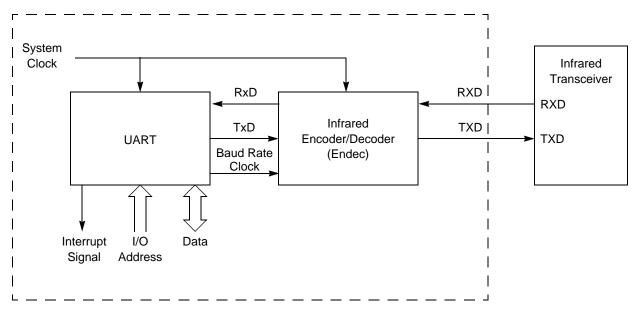

# Infrared Encoder/Decoder

Z8 Encore! XP F0823 Series products contain a fully-functional, high-performance UART with an infrared encoder/decoder (endec). The infrared endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

## Architecture

Figure 16 displays the architecture of the infrared endec.

Figure 16. Infrared Data Communication System Block Diagram

## Operation

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the infrared endec through the RXD pin, decoded by the infrared endec, and

# The second secon

## **Automatic Powerdown**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to powerup. The ADC powers up when a conversion is requested by the ADC Control Register.

## **Single-Shot Conversion**

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the acceptable analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### ilog Embedded in Life An IXYS Company 131

## ADC Data Low Bits Register

The ADC Data Low Byte register contains the lower bits of the ADC output as well as an overflow status bit. The output is a 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits Register.

| Bit     | 7     | 6    | 5 | 4        | 3 | 2 | 1 | 0   |

|---------|-------|------|---|----------|---|---|---|-----|

| Field   | ADCDL |      |   | Reserved |   |   |   | OVF |

| RESET   | Х     | Х    | Х | Х        | Х | Х | Х | Х   |

| R/W     | R     | R    | R | R        | R | R | R | R   |

| Address |       | F73H |   |          |   |   |   |     |

| Table 77. | ADC Data | Low Bits | Register ( | (ADCD L) |

|-----------|----------|----------|------------|----------|

|           |          |          |            |          |

| Bit            | Description                                                                                                                                                               |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]<br>ADCDL | ADC Data Low Bits<br>These bits are the least significant three bits of the 11-bits of the ADC output. These bits are<br>undefined after a Reset.                         |

| [4:1]          | Reserved<br>These bits are reserved and are undefined when read.                                                                                                          |

| [0]<br>OVF     | Overflow Status<br>0 = An overflow did not occur in the digital filter for the current sample.<br>1 = An overflow did occur in the digital filter for the current sample. |

ilog Embedded in Life

IXYS Company

149

## **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits.

| Bit     | 7                    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|----------------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | TRMDR: Trim Bit Data |     |     |     |     |     |     |     |

| RESET   | 0                    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W                  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FF7H                 |     |     |     |     |     |     |     |

#### Table 88. Trim Bit Data Register (TRMDR)

## Flash Option Bit Address Space

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

#### Table 89. Flash Option Bits at Program Memory Address 0000H

| Bit       | 7                    | 6           | 5            | 4     | 3      | 2   | 1        | 0   |

|-----------|----------------------|-------------|--------------|-------|--------|-----|----------|-----|

| Field     | WDT_RES              | WDT_AO      | Rese         | erved | VBO_AO | FRP | Reserved | FWP |

| RESET     | U                    | U           | U            | U     | U      | U   | U        | U   |

| R/W       | R/W                  | R/W         | R/W          | R/W   | R/W    | R/W | R/W      | R/W |

| Address   | Program Memory 0000H |             |              |       |        |     |          |     |

| Note: U = | Unchanged by         | Reset R/W = | = Read/Write |       |        |     |          |     |

U = Unchanged by Reset. R/W = Read/Write.

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>WDT_RES | <ul> <li>Watchdog Timer Reset</li> <li>0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.</li> <li>1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                           |

| [6]<br>WDT_AO  | <ul> <li>Watchdog Timer Always ON</li> <li>0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.</li> <li>1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.</li> </ul> |

| [5:4]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 11 during writes, and to 11 when read.                                                                                                                                                                                                                                                                                                |

PS024315-1011

## **ADC Calibration Data**

#### Table 94. ADC Calibration Bits

| Bit       | 7                                               | 6               | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------------------------|-----------------|-----|-----|-----|-----|-----|-----|

| Field     | ADC_CAL                                         |                 |     |     |     |     |     |     |

| RESET     | U                                               | U U U U U U U U |     |     |     |     |     |     |

| R/W       | R/W                                             | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |

| Address   | Information Page Memory 0060H–007DH             |                 |     |     |     |     |     |     |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                 |     |     |     |     |     |     |

# Bit Description [7:0] Analog-to-Digital Converter Calibration Values ADC\_CAL Contains factory-calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in the Software Compensation Procedure section on page 126. The location of each calibration byte is provided in Table 95.

#### Table 95. ADC Calibration Data Location

| Info Page<br>Address | Memory<br>Address | Compensation<br>Usage | ADC Mode                | Reference<br>Type |

|----------------------|-------------------|-----------------------|-------------------------|-------------------|

| 60                   | FE60              | Offset                | Single-Ended Unbuffered | Internal 2.0V     |

| 08                   | FE08              | Gain High Byte        | Single-Ended Unbuffered | Internal 2.0V     |

| 09                   | FE09              | Gain Low Byte         | Single-Ended Unbuffered | Internal 2.0V     |

| 63                   | FE63              | Offset                | Single-Ended Unbuffered | Internal 1.0V     |

| 0A                   | FE0A              | Gain High Byte        | Single-Ended Unbuffered | Internal 1.0V     |

| 0B                   | FE0B              | Gain Low Byte         | Single-Ended Unbuffered | Internal 1.0V     |

| 66                   | FE66              | Offset                | Single-Ended Unbuffered | External 2.0V     |

| 0C                   | FE0C              | Gain High Byte        | Single-Ended Unbuffered | External 2.0V     |

| 0D                   | FE0D              | Gain Low Byte         | Single-Ended Unbuffered | External 2.0V     |

DBG  $\leftarrow$  0BH DBG  $\leftarrow$  Program Memory Address[15:8] DBG  $\leftarrow$  Program Memory Address[7:0] DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\rightarrow$  1-65536 data bytes

Write Data Memory (0CH). The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option Bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Data Memory (0DH).** The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Read Program Memory CRC (0EH).** The Read Program Memory Cyclic Redundancy Check (CRC) command computes and returns the CRC of Program Memory using the 16bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

**Step Instruction (10H).** The Step Instruction steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG ← 10H

| Mnemonic | Operands | Instruction            |  |

|----------|----------|------------------------|--|

| ATM      | _        | Atomic Execution       |  |

| CCF      | —        | Complement Carry Flag  |  |

| DI       | —        | Disable Interrupts     |  |

| EI       | _        | Enable Interrupts      |  |

| HALT     | _        | HALT Mode              |  |

| NOP      | —        | No Operation           |  |

| RCF      | —        | Reset Carry Flag       |  |

| SCF      | —        | Set Carry Flag         |  |

| SRP      | src      | Set Register Pointer   |  |

| STOP     | —        | STOP Mode              |  |

| WDT      | _        | Watchdog Timer Refresh |  |

#### Table 113. CPU Control Instructions

#### Table 114. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### ilog<sup>°</sup> Embedded in Life An IXYS Company 206

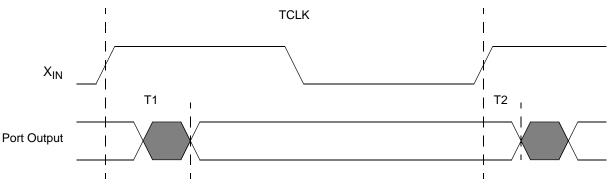

## **General Purpose I/O Port Output Timing**

Figure 30 and Table 131 provide timing information for GPIO Port pins.

|                |                                                 | Delay (ns) |         |  |

|----------------|-------------------------------------------------|------------|---------|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |

| GPIO Port pins |                                                 |            |         |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _          | 15      |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |  |

#### Table 131. GPIO Port Output Timing

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

> ilog Embedded in Life An IXYS Company 215

|                                                                                |                |           |            |                        |                     | U              | · · · ·             |

|--------------------------------------------------------------------------------|----------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                                                                    | Flash<br>RAM   | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP F0823 Series with 2 KB Flash, 10-Bit Analog-to-Digital Converter |                |           |            |                        |                     |                |                     |

| Standard Temperatu                                                             | re: 0°C to 70° | С         |            |                        |                     |                |                     |

| Z8F0223PB005SG                                                                 | 2 KB 512       | B 6       | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005SG                                                                 | 2 KB 512       | B 6       | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005SG                                                                 | 2 KB 512       | B 6       | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005SG                                                                 | 2 KB 512       | B 16      | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005SG                                                                 | 2 KB 512       | B 16      | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005SG                                                                 | 2 KB 512       | B 16      | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005SG                                                                 | 2 KB 512       | B 22      | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005SG                                                                 | 2 KB 512       | B 22      | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005SG                                                                 | 2 KB 512       | B 22      | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: –40°C to 105°C                                           |                |           |            |                        |                     |                |                     |

| Z8F0223PB005EG                                                                 | 2 KB 512       | B 6       | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005EG                                                                 | 2 KB 512       | B 6       | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005EG                                                                 | 2 KB 512       | B 6       | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005EG                                                                 | 2 KB 512       | B 16      | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005EG                                                                 | 2 KB 512       | B 16      | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005EG                                                                 | 2 KB 512       | B 16      | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005EG                                                                 | 2 KB 512       | B 22      | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005EG                                                                 | 2 KB 512       | B 22      | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005EG                                                                 | 2 KB 512       | B 22      | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

#### Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

230

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.