Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0823hj005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

nbedded in Life

1

# **Overview**

Zilog's Z8 Encore! XP microcontroller unit (MCU) family of products are the first Zilog microcontroller products based on the 8-bit eZ8 CPU core. Z8 Encore! XP F0823 Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8 instructions. The rich peripheral set of Z8 Encore! XP F0823 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

## **Features**

The key features of Z8 Encore! XP F0823 Series include:

- 5MHz eZ8 CPU

- 1KB, 2KB, 4KB, or 8KB Flash memory with in-circuit programming capability

- 256B, 512B, or 1KB register RAM

- 6 to 24 I/O pins depending upon package

- Internal precision oscillator (IPO)

- Full-duplex UART

- The universal asynchronous receiver/transmitter (UART) baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared data association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-Chip analog comparator

- Up to 20 vectored interrupts

- Direct LED drive with programmable drive strengths

- Voltage Brown-Out (VBO) protection

- Power-On Reset (POR)

7

# **Pin Description**

Z8 Encore! XP F0823 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and pin configurations available for each of the package styles. For information about physical package specifications, see the Packaging chapter on page 210.

## **Available Packages**

Table 2 lists the package styles that are available for each device in the F0823 Series product line.

| Part<br>Number | ADC | 8-pin<br>PDIP | 8-pin<br>SOIC | 20-pin<br>PDIP | 20-pin<br>SOIC | 20-pin<br>SSOP | 28-pin<br>PDIP | 28-pin<br>SOIC | 28-pin<br>SSOP | 8-pin QFN/<br>MLF-S |

|----------------|-----|---------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------|

| Z8F0823        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0813        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0423        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0413        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0223        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0213        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0123        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0113        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

Table 2. F0823 Series Package Options

# **Pin Configurations**

Figures 2 through 4 display the pin configurations for all packages available in the F0823 Series. For description of signals, see Table 3. The analog input alternate functions (ANAx) are not available on the Z8F0x13 devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all pins of Ports A, B, and C default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general-purpose input ports until programmed otherwise.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

#### ilog Embedded in Life An 🛙 IXYS Company

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 8-pin devices.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                         | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up<br>or Pull-<br>down                    | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                    |

|--------------------|-----------|----------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if<br>key<br>sequence<br>detected) | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O<br>(defaults<br><u>to</u><br>RESET)                                    | N/A                                   | Yes                | Program-<br>mable for<br>PA2;<br>always<br>on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | Ι                                                                          | N/A                                   | Yes                | Program-<br>mable<br>Pull-up                               | Yes                          | Yes,<br>Programmable                                 | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

| VSS                | N/A       | N/A                                                                        | N/A                                   | N/A                | N/A                                                        | N/A                          | N/A                                                  | N/A                                |

### Table 5. Pin Characteristics (8-Pin Devices)

| Address (Hex) | Register Description    | Mnemonic | Reset (Hex) | Page<br>No.                                                                   |

|---------------|-------------------------|----------|-------------|-------------------------------------------------------------------------------|

| eZ8 CPU       |                         |          |             |                                                                               |

| FFC           | Flags                   | _        | XX          | Refe                                                                          |

| FFD           | Register Pointer        | RP       | XX          | to the                                                                        |

| FFE           | Stack Pointer High Byte | SPH      | XX          | - <u>eZ8</u><br>CPU                                                           |

| FFF           | Stack Pointer Low Byte  | SPL      | XX          | <u>Core</u><br><u>User</u><br><u>Man-</u><br><u>ual</u><br>(UM0<br><u>28)</u> |

### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

ILOG<sup>°</sup> Embedded in Life □IXYS Company 22

During a System Reset or Stop Mode Recovery, the IPO requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

# LED Drive Level High Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 33). These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit     | 7   | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|---------|-----|-----|-----|

| Field   |     |     |     | LEDLV | LH[7:0] |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Address |     |     |     | F8    | 3H      |     |     |     |

## Table 33. LED Drive Level High Register (LEDLVLH)

| Bit     | Description                                                                             |

|---------|-----------------------------------------------------------------------------------------|

| [7:0]   | LED Level High Bit                                                                      |

| LEDLVLH | {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C |

|         | pin.                                                                                    |

|         | 00 = 3 mA.                                                                              |

|         | 01= 7 mA.                                                                               |

|         | 10= 13mA.                                                                               |

|         | 11= 20mA.                                                                               |

52

Embedded in Life

n 🖬 IXYS Company

| <b>Z</b> 8 | Encore! XP <sup>®</sup> | F0823  | Series  |

|------------|-------------------------|--------|---------|

|            | Product                 | Specif | ication |

|            |                         |        |         |

nbedded in Life

n 🗖 IXYS Company

56

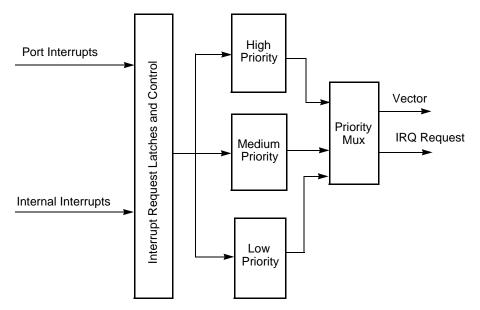

# Architecture

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

## Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 56

Interrupt Vectors and Priority: see page 57

Interrupt Assertion: see page 57

Software Interrupt Assertion: see page 58

Watchdog Timer Interrupt Assertion: see page 58

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

• Execution of an Enable Interrupt (EI) instruction

# Embedded in Life An IXYS Company 97

# Universal Asynchronous Receiver/ Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. The features of UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) Mode with three configurable interrupt schemes

- BRG can be configured and used as a basic 16-bit timer

- Driver Enable output for external bus transceivers

## Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

#### ilog Embedded in Life An IXYS Company 110

## **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 66 and Table 67) identify the current UART operating configuration and status.

| Bit         | 7                                         | 6                                               | 5                                         | 4                             | 3                                          | 2            | 1            | 0        |

|-------------|-------------------------------------------|-------------------------------------------------|-------------------------------------------|-------------------------------|--------------------------------------------|--------------|--------------|----------|

| Field       | RDA                                       | PE                                              | OE                                        | FE                            | BRKD                                       | TDRE         | TXE          | CTS      |

| RESET       | 0                                         | 0                                               | 0                                         | 0                             | 0                                          | 1            | 1            | Х        |

| R/W         | R                                         | R                                               | R                                         | R                             | R                                          | R            | R            | R        |

| Address     |                                           |                                                 |                                           | F4                            | 1H                                         |              |              |          |

| Bit         | Descriptio                                | n                                               |                                           |                               |                                            |              |              |          |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA | ita Register<br>RT Receive                      | he UART Re<br>clears this b<br>Data Regis |                               |                                            | received da  | ata. Reading | the UART |

| [6]<br>PE   | register clea<br>0 = No parit             | cates that a                                    | occurred.                                 | has occurre                   | d. Reading t                               | the UART R   | eceive Data  |          |

| [5]<br>OE   | received an<br>reading the<br>0 = No over | cates that a<br>d the UART                      | Receive Da<br>eive Data Re<br>curred.     |                               | urred. An ov<br>has not bee<br>s this bit. |              |              |          |

| [4]<br>FE   | Reading the<br>0 = No fram                | cates that a                                    | eive Data R<br>curred.                    | or (no Stop b<br>egister clea | bit following rs this bit.                 | data recepti | on) was dete | ected.   |

| [3]<br>BRKD | bit(s) are al                             | cates that a<br>I 0s this bit i<br>ak occurred. |                                           |                               | ata bits, pari<br>JART Recei               |              |              |          |

Embedded in Life

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 68 and Table 69) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

| Bit     | 7           | 6   | 5    | 4   | 3    | 2    | 1    | 0    |

|---------|-------------|-----|------|-----|------|------|------|------|

| Field   | TEN         | REN | CTSE | PEN | PSEL | SBRK | STOP | LBEN |

| RESET   | 0           | 0   | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W         | R/W | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

| Address |             |     |      | F4  | 2H   |      |      |      |

| Bit     | Description | n   |      |     |      |      |      |      |

### Table 68. UART Control 0 Register (U0CTL0)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TEN  | Transmit EnableThis bit enables or disables the transmitter. The enable is also controlled by the $\overline{CTS}$ signaland the CTSE bit. If the $\overline{CTS}$ signal is low and the CTSE bit is 1, the transmitter is enabled.0 = Transmitter disabled.1 = Transmitter enabled.                                                                   |

| [6]<br>REN  | Receive Enable<br>This bit enables or disables the receiver.<br>0 = Receiver disabled.<br>1 = Receiver enabled.                                                                                                                                                                                                                                        |

| [5]<br>CTSE | <b>CTSE—CTS Enable</b><br>0 = The CTS signal has no effect on the transmitter.<br>1 = The UART recognizes the CTS signal as an enable control from the transmitter.                                                                                                                                                                                    |

| [4]<br>PEN  | <ul> <li>Parity Enable</li> <li>This bit enables or disables parity. Even or odd is determined by the PSEL bit.</li> <li>0 = Parity is disabled.</li> <li>1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit .</li> </ul>                                                                 |

| [3]<br>PSEL | <ul> <li>Parity Select</li> <li>0 = Even parity is transmitted and expected on all received data.</li> <li>1 = Odd parity is transmitted and expected on all received data.</li> </ul>                                                                                                                                                                 |

| [2]<br>SBRK | <ul> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = Forces a break condition by setting the output of the transmitter to zero.</li> </ul> |

116

dded in Life

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 73 provides information about data rate errors for a 5.5296MHz System Clock.

|                          | 5.5296MHz S              | ystem Clock          |           |  |

|--------------------------|--------------------------|----------------------|-----------|--|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |  |

| 1250.0                   | N/A                      | N/A                  | N/A       |  |

| 625.0                    | N/A                      | N/A                  | N/A       |  |

| 250.0                    | 1                        | 345.6                | 38.24     |  |

| 115.2                    | 3                        | 115.2                | 0.00      |  |

| 57.6                     | 6                        | 57.6                 | 0.00      |  |

| 38.4                     | 9                        | 38.4                 | 0.00      |  |

| 19.2                     | 18                       | 19.2                 | 0.00      |  |

| 9.60                     | 36                       | 9.60                 | 0.00      |  |

| 4.80                     | 72                       | 4.80                 | 0.00      |  |

| 2.40                     | 144                      | 2.40                 | 0.00      |  |

| 1.20                     | 288                      | 1.20                 | 0.00      |  |

| 0.60                     | 576                      | 0.60                 | 0.00      |  |

| 0.30                     | 1152                     | 0.30                 | 0.00      |  |

#### Table 73. UART Baud Rates

edded in Life

IXYS Company

119

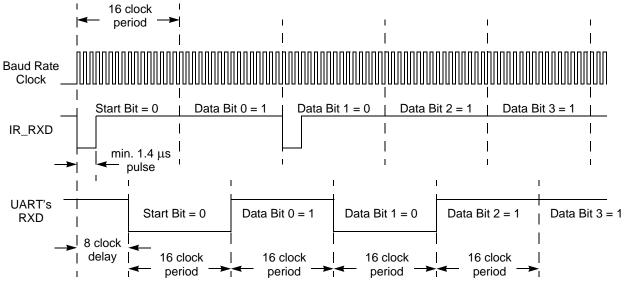

## **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the infrared endec and passed to the UART. The UART's baud rate clock is used by the infrared endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the infrared endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP F0823 Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

## **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0MHz to ensure proper reception of the 1.4µs minimum width pulses allowed by the IrDA standard.

## **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens.

#### ilog<sup>\*</sup> Embedded in Life An∎IXYS Company 129

## ADC Control/Status Register 1

The second ADC Control Register contains the voltage reference level selection bit.

## Table 75. ADC Control/Status Register 1 (ADCCTL1)

| Bit            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6               | 5           | 4            | 3           | 2      | 1   | 0   |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|--------------|-------------|--------|-----|-----|--|

| Field          | REFSELH                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EFSELH Reserved |             |              |             |        |     |     |  |

| RESET          | 1 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |             |              |             |        |     |     |  |

| R/W            | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W             | R/W         | R/W          | R/W         | R/W    | R/W | R/W |  |

| Address        | F71H                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |             |              |             |        |     |     |  |

| Bit            | Descript                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Description     |             |              |             |        |     |     |  |

| [7]<br>REFSELH | Voltage Reference Level Select High Bit<br>In conjunction with the Low bit (REFSELL) in ADC Control Register 0, this bit determines<br>the level of the internal voltage reference; the following details the effects of {REFSELH,<br>REFSELL}; this reference is independent of the Comparator reference.<br>00 = Internal Reference Disabled, reference comes from external pin.<br>01 = Internal Reference set to 1.0V.<br>10 = Internal Reference set to 2.0V (default). |                 |             |              |             |        |     |     |  |

| [6:0]          | <b>Reserve</b><br>These bit                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | /ed and mus | st be progra | mmed to 000 | 00000. |     |     |  |

#### ilog<sup>\*</sup> Embedded in Life An IXYS Company 157

# Operation

The following section describes the operation of the OCD.

## **OCD Interface**

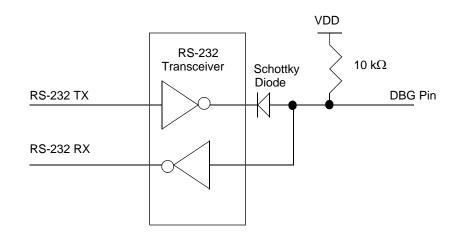

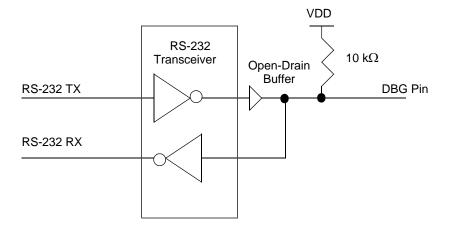

The OCD uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface from the F0823 Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 23 and Figure 24. The recommended method is the buffered implementation depicted in Figure 24. The DBG pin has a internal pull-up resistor which is sufficient for some applications (for more details about the pullup current, see the <u>Electrical Characteristics</u> chapter on page 196). For OCD operation at higher data rates or in noisy systems, Zilog recommends an external pull-up resistor.

**Caution:** For operation of the OCD, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power, and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is opendrain and may require an external pull-up resistor to ensure proper operation.

#### ilog<sup>°</sup> Embedded in Life An TIXYS Company 158

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, # 2 of 2

## **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled.

### **Entering DEBUG Mode**

The device enters DEBUG Mode following the operations below:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (breakpoint) instruction

- If the DBG pin is held Low during the most recent clock cycle of System Reset, the part enters DEBUG Mode upon exiting System Reset

• Note: Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an autobaud sequence (see the <u>OCD Autobaud Detector/</u><u>Generator section on page 159</u>).

ILO O hbedded in Life IXYS Company

166

**Stuff Instruction (11H).** The Stuff command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0–4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

**Execute Instruction (12H).** The Execute command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

## **OCD Control Register**

The OCD Control Register controls the state of the OCD. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It also resets Z8 Encore! XP F0823 Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

#### ilog<sup>\*</sup> Embedded in Life An IXYS Company

Table 107. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Z8 Encore! XP Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is noted in Table 108.

| Notation | Description                    | Operand                                      | Range                                                                                |

|----------|--------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|

| b        | Bit                            | b                                            | b represents a value from 0 to 7 (000B to 111B).                                     |

| CC       | Condition Code                 | _                                            | See the Condition Codes overview in the <u>eZ8 CPU</u><br>Core User Manual (UM0128). |

| DA       | Direct Address                 | rect Address Addrs Addrs represents to FFFH. |                                                                                      |

| ER       | Extended Addressing Register   | Reg                                          | Reg represents a number in the range of 000H to FFFH.                                |

| IM       | Immediate Data                 | #Data                                        | Data is a number between 00H to FFH.                                                 |

| lr       | Indirect Working Register      | @Rn                                          | n = 0–15.                                                                            |

| IR       | Indirect Register              | @Reg                                         | Reg. represents a number in the range of 00H to FFH.                                 |

| Irr      | Indirect Working Register Pair | @RRp                                         | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                    |

| IRR      | Indirect Register Pair         | @Reg                                         | Reg represents an even number in the range 00H to FEH                                |

| р        | Polarity                       | р                                            | Polarity is a single bit binary value of either 0B or 1B.                            |

| r        | Working Register               | Rn                                           | n = 0–15.                                                                            |

| R        | Register                       | Reg                                          | Reg. represents a number in the range of 00H to FFH.                                 |

#### Table 108. Notational Shorthand

|                   |                                       | T <sub>A</sub> = −40°C to +105°C<br>(unless otherwise specified) |                  |         |       |                                                                               |  |

|-------------------|---------------------------------------|------------------------------------------------------------------|------------------|---------|-------|-------------------------------------------------------------------------------|--|

| Symbol            | Parameter                             | Minimum                                                          | Typical          | Maximum | Units | Conditions                                                                    |  |

| I <sub>LED</sub>  | Controlled Current                    | 1.8                                                              | 3                | 4.5     | mA    | {AFS2,AFS1} = {0,0}.                                                          |  |

|                   | Drive                                 | 2.8                                                              | 7                | 10.5    | mA    | {AFS2,AFS1} = {0,1}.                                                          |  |

|                   |                                       | 7.8                                                              | 13               | 19.5    | mA    | {AFS2,AFS1} = {1,0}.                                                          |  |

|                   |                                       | 12                                                               | 20               | 30      | mA    | ${AFS2,AFS1} = {1,1}.$                                                        |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance          | -                                                                | 8.0 <sup>2</sup> | -       | pF    |                                                                               |  |

| C <sub>XIN</sub>  | X <sub>IN</sub> Pad Capaci-<br>tance  | -                                                                | 8.0 <sup>2</sup> | -       | pF    |                                                                               |  |

| C <sub>XOUT</sub> | X <sub>OUT</sub> Pad Capaci-<br>tance | -                                                                | 9.5 <sup>2</sup> | -       | pF    |                                                                               |  |

| I <sub>PU</sub>   | Weak Pull-up Cur-<br>rent             | 30                                                               | 100              | 350     | μA    | V <sub>DD</sub> = 3.0V–3.6V.                                                  |  |

| V <sub>RAM</sub>  | RAM Data Reten-<br>tion Voltage       | TBD                                                              |                  |         | V     | Voltage at which RAM retains static values; no reading or writing is allowed. |  |

#### Table 121. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

# Embedded in Life An IXYS Company

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                   |                        | T <sub>A</sub> = -40°C<br>(unless o | 'V to 3.6V<br>C to +105°C<br>otherwise<br>ted) |       |                                         |  |

|-------------------|------------------------|-------------------------------------|------------------------------------------------|-------|-----------------------------------------|--|

| Symbol Parameter  |                        | Minimum                             | Maximum                                        | Units | Conditions                              |  |

| FSYSCLK           | System Clock Frequency | _                                   | 20.0*                                          | MHz   | Read-only from Flash memory.            |  |

|                   |                        | 0.032768                            | 20.0 <sup>1</sup>                              | MHz   | Program or erasure of the Flash memory. |  |

| T <sub>XIN</sub>  | System Clock Period    | 50                                  | _                                              | ns    | $T_{CLK} = 1/F_{SYSCLK}$ .              |  |

| T <sub>XINH</sub> | System Clock High Time | 20                                  | 30                                             | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINL</sub> | System Clock Low Time  | 20                                  | 30                                             | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINR</sub> | System Clock Rise Time | _                                   | 3                                              | ns    | T <sub>CLK</sub> = 50ns.                |  |

| T <sub>XINF</sub> | System Clock Fall Time | _                                   | 3                                              | ns    | Т <sub>СІ К</sub> = 50ns.               |  |

| Table ' | 123. AC | Characteristics |

|---------|---------|-----------------|

|---------|---------|-----------------|

#### Table 124. Internal Precision Oscillator Electrical Characteristics

|                    |                                                         | $T_A = -$ | = 2.7V to<br>-40°C to +<br>otherwise |            |       |                                                 |

|--------------------|---------------------------------------------------------|-----------|--------------------------------------|------------|-------|-------------------------------------------------|

| Symbol             | Parameter                                               | Minimum   | Typical                              | Maximum    | Units | Conditions                                      |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |           | 5.53                                 |            | MHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |           | 32.7                                 |            | kHz   | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = 30°C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |           | <u>+</u> 1                           | <u>+</u> 4 | %     |                                                 |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |           | 3                                    |            | μs    |                                                 |

# Embedded in Life

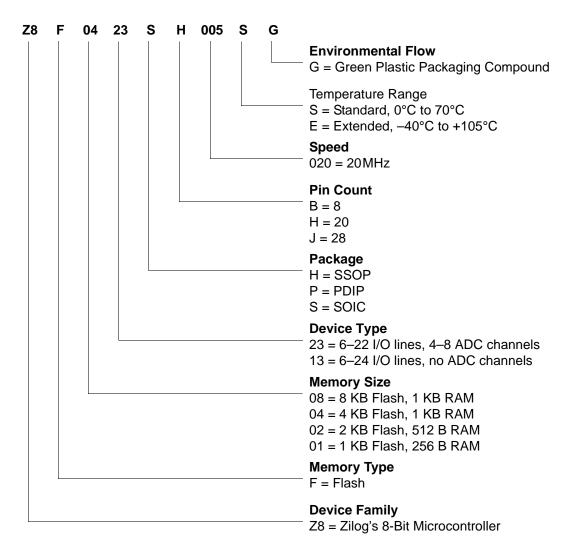

## Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0423SH005SG is an 8-bit 20MHz Flash MCU with 4KB of Program Memory and equipped with 6–22 I/O lines and 4–8 ADC channels in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.