Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0823ph005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address (Hex)    | Register Description     | Mnemonic       | Reset (Hex) | Page<br>No. |

|------------------|--------------------------|----------------|-------------|-------------|

| LED Controller   | (cont'd)                 |                |             |             |

| F84              | LED Drive Level Low Byte | LEDLVLL        | 00          | <u>53</u>   |

| F85              | Reserved                 | —              | XX          |             |

| Oscillator Conti | rol                      |                |             |             |

| F86              | Oscillator Control       | OSCCTL         | A0          | <u>172</u>  |

| F87–F8F          | Reserved                 | —              | XX          |             |

| Comparator 0     |                          |                |             |             |

| F90              | Comparator 0 Control     | CMP0           | 14          | <u>133</u>  |

| F91–FBF          | Reserved                 | _              | XX          |             |

| Interrupt Contro | oller                    |                |             |             |

| FC0              | Interrupt Request 0      | IRQ0           | 00          | <u>59</u>   |

| FC1              | IRQ0 Enable High Bit     | IRQ0ENH        | 00          | <u>62</u>   |

| FC2              | IRQ0 Enable Low Bit      | <b>IRQ0ENL</b> | 00          | <u>62</u>   |

| FC3              | Interrupt Request 1      | IRQ1           | 00          | <u>60</u>   |

| FC4              | IRQ1 Enable High Bit     | IRQ1ENH        | 00          | <u>64</u>   |

| FC5              | IRQ1 Enable Low Bit      | IRQ1ENL        | 00          | <u>64</u>   |

| FC6              | Interrupt Request 2      | IRQ2           | 00          | <u>61</u>   |

| FC7              | IRQ2 Enable High Bit     | IRQ2ENH        | 00          | <u>65</u>   |

| FC8              | IRQ2 Enable Low Bit      | IRQ2ENL        | 00          | <u>66</u>   |

| FC9–FCC          | Reserved                 | —              | XX          |             |

| FCD              | Interrupt Edge Select    | IRQES          | 00          | <u>67</u>   |

| FCE              | Shared Interrupt Select  | IRQSS          | 00          | <u>67</u>   |

| FCF              | Interrupt Control        | IRQCTL         | 00          | <u>68</u>   |

| GPIO Port A      |                          |                |             |             |

| FD0              | Port A Address           | PAADDR         | 00          | <u>40</u>   |

| FD1              | Port A Control           | PACTL          | 00          | <u>42</u>   |

| FD2              | Port A Input Data        | PAIN           | XX          | <u>43</u>   |

| FD3              | Port A Output Data       | PAOUT          | 00          | <u>43</u>   |

| GPIO Port B      |                          |                |             |             |

| FD4              | Port B Address           | PBADDR         | 00          | <u>40</u>   |

| FD5              | Port B Control           | PBCTL          | 00          | <u>42</u>   |

## Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

| Address (Hex) | Register Description    | Mnemonic | Reset (Hex) | Page<br>No.                                                                   |

|---------------|-------------------------|----------|-------------|-------------------------------------------------------------------------------|

| eZ8 CPU       |                         |          |             |                                                                               |

| FFC           | Flags                   | _        | XX          | Refe                                                                          |

| FFD           | Register Pointer        | RP       | XX          | to the                                                                        |

| FFE           | Stack Pointer High Byte | SPH      | XX          | - <u>eZ8</u><br>CPU                                                           |

| FFF           | Stack Pointer Low Byte  | SPL      | XX          | <u>Core</u><br><u>User</u><br><u>Man-</u><br><u>ual</u><br>(UM0<br><u>28)</u> |

## Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

#### ILOG<sup>°</sup> hbedded in Life IXYS Company 30

# Low-Power Modes

Z8 Encore! XP F0823 Series products contain power-saving features. The highest level of power reduction is provided by the STOP Mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT Mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in ACTIVE mode (defined as being in neither STOP nor HALT Mode).

# **STOP Mode**

Executing the eZ8 CPU's Stop instruction places the device into STOP Mode, powering down all peripherals except the Voltage Brown-Out detector, and the Watchdog Timer. These two blocks may also be disabled for additional power savings. In STOP Mode, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; X<sub>IN</sub> and X<sub>OUT</sub> (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers

- System clock is stopped

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control Register

- If enabled, the Watchdog Timer logic continues to operate

- If enabled for operation in STOP Mode by the associated Flash Option Bit, the Voltage Brown-Out protection circuit continues to operate

- All other on-chip peripherals are idle

To minimize current in STOP Mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP Mode using Stop Mode Recovery. For more information about Stop Mode Recovery, see the <u>Reset and Stop Mode Recovery</u> chapter on page 21.

## Port A–C Pull-up Enable Subregisters

The Port A–C Pull-up Enable Subregister (Table 27) is accessed through the Port A–C Control Register by writing 06H to the Port A–C Address Register. Setting the bits in the Port A–C Pull-up Enable subregisters enables a weak internal resistive pull-up on the specified Port pins.

| Bit     | 7           | 6            | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-------------|--------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | PPUE7       | PPUE6        | PPUE5       | PPUE4         | PPUE3        | PPUE2        | PPUE1        | PPUE0    |

| RESET   | 0           | 0            | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W     | R/W         | R/W          | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | If 06H ir   | n Port A–C A | Address Reg | jister, acces | sible throug | h the Port A | -C Control F | Register |

| Bit     | Description | n            |             |               |              |              |              |          |

#### Table 27. Port A–C Pull-Up Enable Subregisters (PPUEx)

| BIt        | Description                                       |

|------------|---------------------------------------------------|

| [7:0]      | Port Pull-up Enabled                              |

| PPUEx      | 0 = The weak pull-up on the Port pin is disabled. |

|            | 1 = The weak pull-up on the Port pin is enabled.  |

| Note: x ir | ndicates the specific GPIO port pin number (7–0). |

# Embedded in Life

## **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a PWM output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps to configure a timer for PWM Single Output mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H); this write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

nbedded in Life

101

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) performs the following:

1. Write the UART Control 1 Register to select the multiprocessor bit for the byte to be transmitted:

Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 3. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 4. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data Register to again become empty.

## **Receiving Data Using the Polled Method**

Observe the following steps to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set an acceptable baud rate for the incoming data stream.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable MULTIPROCESSOR Mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if Multiprocessor mode is not enabled, and select either even or odd parity

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to <u>Step 6</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

- 6. Read data from the UART Receive Data Register. If operating in MULTIPROCES-SOR (9-bit) Mode, further actions may be required depending on the MULTIPRO-CESSOR Mode bits MPMD[1:0].

#### ilog Embedded in Life An∎IXYS Company 110

# **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 66 and Table 67) identify the current UART operating configuration and status.

| Bit         | 7                                                                                                                                                                                                                                                                                                                               | 6                                                        | 5                                     | 4  | 3                                          | 2    | 0   |     |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------|----|--------------------------------------------|------|-----|-----|--|--|--|--|--|--|

| Field       | RDA                                                                                                                                                                                                                                                                                                                             | PE                                                       | OE                                    | FE | BRKD                                       | TDRE | TXE | CTS |  |  |  |  |  |  |

| RESET       | 0                                                                                                                                                                                                                                                                                                                               | 0                                                        | 0                                     | 0  | 0                                          | 1    |     |     |  |  |  |  |  |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                               | R                                                        | R                                     | R  | R                                          | R    | R   | R   |  |  |  |  |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                                 |                                                          |                                       | F4 | 1H                                         |      |     |     |  |  |  |  |  |  |

| Bit         | Description                                                                                                                                                                                                                                                                                                                     |                                                          |                                       |    |                                            |      |     |     |  |  |  |  |  |  |

| [7]<br>RDA  | <ul> <li>Receive Data Available</li> <li>This bit indicates that the UART Receive Data Register has received data. Reading the UAR Receive Data Register clears this bit.</li> <li>0 = The UART Receive Data Register is empty.</li> <li>1 = There is a byte in the UART Receive Data Register.</li> </ul>                      |                                                          |                                       |    |                                            |      |     |     |  |  |  |  |  |  |

| [6]<br>PE   | <ul> <li>Parity Error</li> <li>This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.</li> <li>0 = No parity error has occurred.</li> <li>1 = A parity error has occurred.</li> </ul>                                                                                     |                                                          |                                       |    |                                            |      |     |     |  |  |  |  |  |  |

| [5]<br>OE   | received an<br>reading the<br>0 = No over                                                                                                                                                                                                                                                                                       | cates that a<br>d the UART<br>UART Rece<br>rrun error oc | Receive Da<br>eive Data Re<br>curred. |    | urred. An ov<br>has not bee<br>s this bit. |      |     |     |  |  |  |  |  |  |

| [4]<br>FE   | <ul> <li>1 = An overrun error occurred.</li> <li>Framing Error</li> <li>This bit indicates that a framing error (no Stop bit following data reception) was detected.</li> <li>Reading the UART Receive Data Register clears this bit.</li> <li>0 = No framing error occurred.</li> <li>1 = A framing error occurred.</li> </ul> |                                                          |                                       |    |                                            |      |     |     |  |  |  |  |  |  |

| [3]<br>BRKD | bit(s) are al                                                                                                                                                                                                                                                                                                                   | cates that a<br>I 0s this bit i<br>ak occurred.          |                                       |    | ata bits, pari<br>JART Recei               |      |     |     |  |  |  |  |  |  |

### ilog<sup>\*</sup> Embedded in Life An∎IXYS Company 129

# **ADC Control/Status Register 1**

The second ADC Control Register contains the voltage reference level selection bit.

## Table 75. ADC Control/Status Register 1 (ADCCTL1)

| Bit            | 7                                                          | 6                                                                                 | 5                                                                 | 4                                                           | 3                                          | 2                                                                 | 1                   | 0 |  |  |  |  |  |  |  |

|----------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------|---------------------|---|--|--|--|--|--|--|--|

| Field          | REFSELH                                                    |                                                                                   |                                                                   |                                                             | Reserved                                   |                                                                   |                     | • |  |  |  |  |  |  |  |

| RESET          | 1                                                          | 0                                                                                 | 0 0 0 0 0 0 0                                                     |                                                             |                                            |                                                                   |                     |   |  |  |  |  |  |  |  |

| R/W            | R/W                                                        | R/W                                                                               | R/W                                                               | R/W                                                         | R/W                                        | R/W R/W R/W R                                                     |                     |   |  |  |  |  |  |  |  |

| Address        |                                                            | F71H                                                                              |                                                                   |                                                             |                                            |                                                                   |                     |   |  |  |  |  |  |  |  |

| Bit            | Descript                                                   | Description                                                                       |                                                                   |                                                             |                                            |                                                                   |                     |   |  |  |  |  |  |  |  |

| [7]<br>REFSELH | In conjun<br>the level<br>REFSEL<br>00 = Inte<br>01 = Inte | iction with th<br>of the interr<br>L}; this refer<br>rnal Referer<br>rnal Referer | nal voltage re<br>rence is inden<br>nce Disableo<br>nce set to 1. | REFSELL) in<br>eference; the<br>ependent of<br>d, reference | e following d<br>the Compara<br>comes from | ol Register (<br>letails the ef<br>ator reference<br>external pir | fects of {RE<br>ce. |   |  |  |  |  |  |  |  |

| [6:0]          | Reserve<br>These bit                                       |                                                                                   | ved and mus                                                       | st be progra                                                | nmed to 000                                | 00000.                                                            |                     |   |  |  |  |  |  |  |  |

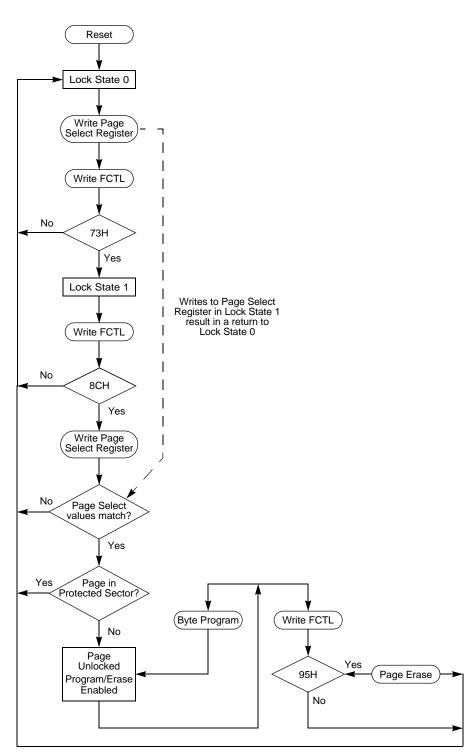

Figure 21. Flash Controller Operation Flowchart

#### ILOG Embedded in Life An IXYS Company 140

## Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

# **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

# **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the Zilog application note titled, <u>Third-Party Flash Programming Support for Z8 Encore! MCUs (AN0117)</u>, available for download at <u>www.zilog.com</u>.

# Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

ILO O hbedded in Life IXYS Company

166

**Stuff Instruction (11H).** The Stuff command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0–4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

**Execute Instruction (12H).** The Execute command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

## **OCD Control Register**

The OCD Control Register controls the state of the OCD. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It also resets Z8 Encore! XP F0823 Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

nbedded in Life

170

ages to the Oscillator Control Desistor can actually stor the ship by

**Caution:** Unintentional accesses to the Oscillator Control Register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

## **OSC Control Register Unlocking/Locking**

To write to the Oscillator Control Register, unlock it by making two writes to the OSC-CTL Register with the values E7H followed by 18H. A third write to the OSCCTL Register changes the value of the actual register and returns the register to a locked state. Any other sequence of Oscillator Control Register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

# **Clock Failure Detection and Recovery**

Should an oscillator or timer fail, there are methods of recovery, as this section describes.

## **Primary Oscillator Failure**

Z8 Encore! XP F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the the <u>Watchdog Timer</u> section on page 91.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below  $1 \text{ kHz} \pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these

I

185

| Assembly     |                                                                                                                   |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch  | Instr. |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|--------|--------|

| Mnemonic     | Symbolic Operation                                                                                                | dst | src         | (Hex)       |   | Ζ | S   | V   | D | н | Cycles |        |

| DA dst       | dst ← DA(dst)                                                                                                     | R   |             | 40          | * | * | *   | Х   | _ | _ | 2      | 2      |

|              |                                                                                                                   | IR  |             | 41          | • |   |     |     |   |   | 2      | 3      |

| DEC dst      | dst ← dst - 1                                                                                                     | R   |             | 30          | - | * | *   | *   | - | _ | 2      | 2      |

|              |                                                                                                                   | IR  |             | 31          | • |   |     |     |   |   | 2      | 3      |

| DECW dst     | dst ← dst - 1                                                                                                     | RR  |             | 80          | _ | * | *   | *   | _ | _ | 2      | 5      |

|              |                                                                                                                   | IRR |             | 81          | • |   |     |     |   |   | 2      | 6      |

| DI           | IRQCTL[7] ← 0                                                                                                     |     |             | 8F          | - | - | _   | -   | - | _ | 1      | 2      |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                             | r   |             | 0A-FA       | - | _ | -   | -   | - | _ | 2      | 3      |

| EI           | IRQCTL[7] ← 1                                                                                                     |     |             | 9F          | _ | _ | _   | -   | _ | _ | 1      | 2      |

| HALT         | HALT Mode                                                                                                         |     |             | 7F          | _ | _ | _   | -   | _ | _ | 1      | 2      |

| INC dst      | dst ← dst + 1                                                                                                     | R   |             | 20          | - | * | *   | -   | _ | _ | 2      | 2      |

|              |                                                                                                                   | IR  |             | 21          | • |   |     |     |   |   | 2      | 3      |

|              |                                                                                                                   | r   |             | 0E-FE       |   |   |     |     |   |   | 1      | 2      |

| INCW dst     | dst ← dst + 1                                                                                                     | RR  |             | A0          | - | * | *   | *   | _ | _ | 2      | 5      |

|              |                                                                                                                   | IRR |             | A1          | • |   |     |     |   |   | 2      | 6      |

| IRET         | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |     |             | BF          | * | * | *   | *   | * | * | 1      | 5      |

| JP dst       | PC ← dst                                                                                                          | DA  |             | 8D          | _ | _ | _   | _   | _ | _ | 3      | 2      |

|              |                                                                                                                   | IRR |             | C4          | • |   |     |     |   |   | 2      | 3      |

| JP cc, dst   | if cc is true<br>PC $\leftarrow$ dst                                                                              | DA  |             | 0D-FD       | _ | - | -   | -   | - | - | 3      | 2      |

| JR dst       | $PC \leftarrow PC + X$                                                                                            | DA  |             | 8B          | - | - | _   | _   | _ | _ | 2      | 2      |

| JR cc, dst   | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA  |             | 0B-FB       | _ | - | _   | _   | _ | _ | 2      | 2      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

189

| Assembly      |                                            |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch  | Instr. |

|---------------|--------------------------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|--------|--------|

| Mnemonic      | Symbolic Operation                         | dst | src         | (Hex)       |   | Ζ | S   | ۷   | D | Н | Cycles |        |

| SBC dst, src  | $dst \gets dst - src - C$                  | r   | r           | 32          | * | * | *   | *   | 1 | * | 2      | 3      |

|               |                                            | r   | lr          | 33          | - |   |     |     |   |   | 2      | 4      |

|               | -                                          | R   | R           | 34          | - |   |     |     |   |   | 3      | 3      |

|               | -                                          | R   | IR          | 35          | - |   |     |     |   |   | 3      | 4      |

|               |                                            | R   | IM          | 36          | _ |   |     |     |   |   | 3      | 3      |

|               | -                                          | IR  | IM          | 37          | - |   |     |     |   |   | 3      | 4      |

| SBCX dst, src | $dst \gets dst - src - C$                  | ER  | ER          | 38          | * | * | *   | *   | 1 | * | 4      | 3      |

|               | -                                          | ER  | IM          | 39          | - |   |     |     |   |   | 4      | 3      |

| SCF           | C ← 1                                      |     |             | DF          | 1 | _ | _   | -   | _ | - | 1      | 2      |

| SRA dst       | <b>*</b> *                                 | R   |             | D0          | * | * | *   | 0   | _ | - | 2      | 2      |

|               | D7_D6_D5_D4_D3_D2_D1_D0 ► C<br>dst         | IR  |             | D1          | - |   |     |     |   |   | 2      | 3      |

| SRL dst       | 0 - <b>▶</b> D7 D6 D5 D4 D3 D2 D1 D0 - ▶ C | R   |             | 1F C0       | * | * | 0   | *   | _ | _ | 3      | 2      |

|               | dst                                        | IR  |             | 1F C1       | - |   |     |     |   |   | 3      | 3      |

| SRP src       | $RP \leftarrow src$                        |     | IM          | 01          | _ | _ | _   | _   | _ | _ | 2      | 2      |

| STOP          | STOP Mode                                  |     |             | 6F          | - | - | _   | -   | _ | _ | 1      | 2      |

| SUB dst, src  | $dst \leftarrow dst - src$                 | r   | r           | 22          | * | * | *   | *   | 1 | * | 2      | 3      |

|               | -                                          | r   | lr          | 23          | - |   |     |     |   |   | 2      | 4      |

|               | -                                          | R   | R           | 24          | - |   |     |     |   |   | 3      | 3      |

|               |                                            | R   | IR          | 25          | - |   |     |     |   |   | 3      | 4      |

|               |                                            | R   | IM          | 26          | - |   |     |     |   |   | 3      | 3      |

|               |                                            | IR  | IM          | 27          | - |   |     |     |   |   | 3      | 4      |

| SUBX dst, src | $dst \leftarrow dst - src$                 | ER  | ER          | 28          | * | * | *   | *   | 1 | * | 4      | 3      |

|               |                                            | ER  | IM          | 29          | - |   |     |     |   |   | 4      | 3      |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$        | R   |             | F0          | Х | * | *   | Х   | - | _ | 2      | 2      |

|               | -                                          | IR  |             | F1          | - |   |     |     |   |   | 2      | 3      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

190

| Assembly      |                                                                                                                        |     | dress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch  | Instr. |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------|-------------|---|---|-----|-----|---|---|--------|--------|

| Mnemonic      | Symbolic Operation                                                                                                     | dst | src          | (Hex)       | С | Ζ | S   | ۷   | D | Н | Cycles |        |

| TCM dst, src  | (NOT dst) AND src                                                                                                      | r   | r            | 62          | - | * | *   | 0   | - | _ | 2      | 3      |

|               |                                                                                                                        | r   | lr           | 63          | • |   |     |     |   |   | 2      | 4      |

|               |                                                                                                                        | R   | R            | 64          | • |   |     |     |   |   | 3      | 3      |

|               |                                                                                                                        | R   | IR           | 65          | • |   |     |     |   |   | 3      | 4      |

|               |                                                                                                                        | R   | IM           | 66          | • |   |     |     |   |   | 3      | 3      |

|               |                                                                                                                        | IR  | IM           | 67          | • |   |     |     |   |   | 3      | 4      |

| TCMX dst, src | (NOT dst) AND src                                                                                                      | ER  | ER           | 68          | _ | * | *   | 0   | _ | - | 4      | 3      |

|               |                                                                                                                        | ER  | IM           | 69          | • |   |     |     |   |   | 4      | 3      |

| TM dst, src   | dst AND src                                                                                                            | r   | r            | 72          | _ | * | *   | 0   | _ | - | 2      | 3      |

|               |                                                                                                                        | r   | lr           | 73          | • |   |     |     |   |   | 2      | 4      |

|               |                                                                                                                        | R   | R            | 74          | • |   |     |     |   |   | 3      | 3      |

|               |                                                                                                                        | R   | IR           | 75          | • |   |     |     |   |   | 3      | 4      |

|               |                                                                                                                        | R   | IM           | 76          | • |   |     |     |   |   | 3      | 3      |

|               |                                                                                                                        | IR  | IM           | 77          | • |   |     |     |   |   | 3      | 4      |

| TMX dst, src  | dst AND src                                                                                                            | ER  | ER           | 78          | _ | * | *   | 0   | _ | - | 4      | 3      |

|               |                                                                                                                        | ER  | IM           | 79          | • |   |     |     |   |   | 4      | 3      |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |     | Vector       | F2          | - | _ | -   | -   | - | _ | 2      | 6      |

| WDT           |                                                                                                                        |     |              | 5F          | _ | _ | _   | _   | _ | _ | 1      | 2      |

## Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

ilog<sup>®</sup> Embedded in Life 191 An∎IXYS Company

| Assembly      |                             | Address<br>Mode |     | _ Opcode(s) |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|---------------|-----------------------------|-----------------|-----|-------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic      | Symbolic Operation          | dst             | src | (Hex)       | С | Ζ | S   | ۷   | D | Н | Cycles  |        |

| XOR dst, src  | $dst \gets dst \ XOR \ src$ | r               | r   | B2          | _ | * | *   | 0   | _ | _ | 2       | 3      |

|               |                             | r               | lr  | B3          |   |   |     |     |   |   | 2       | 4      |

|               |                             | R               | R   | B4          |   |   |     |     |   |   | 3       | 3      |

|               |                             | R               | IR  | B5          |   |   |     |     |   |   | 3       | 4      |

|               |                             | R               | IM  | B6          |   |   |     |     |   |   | 3       | 3      |

|               |                             | IR              | IM  | B7          |   |   |     |     |   |   | 3       | 4      |

| XORX dst, src | $dst \gets dst \ XOR \ src$ | ER              | ER  | B8          | _ | * | *   | 0   | _ | _ | 4       | 3      |

|               |                             | ER              | IM  | B9          |   |   |     |     |   |   | 4       | 3      |

### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

PS024315-1011

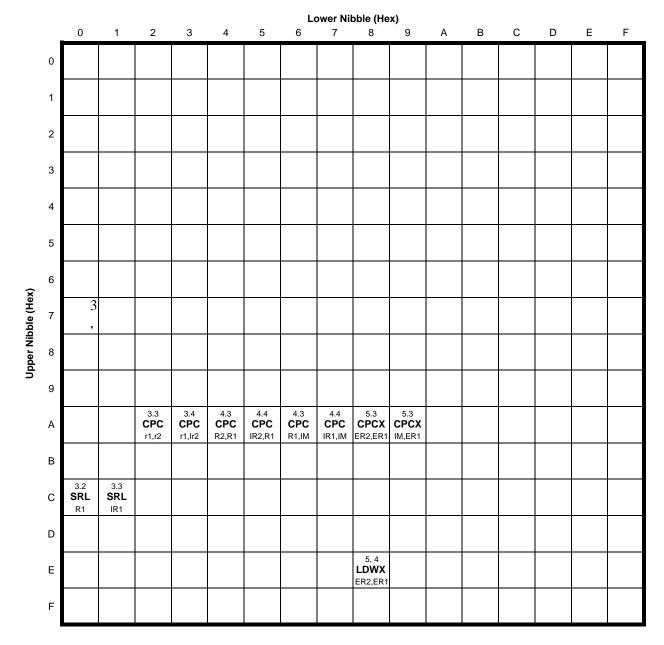

Figure 28. Second Opcode Map after 1FH

205

An∎IXYS Company

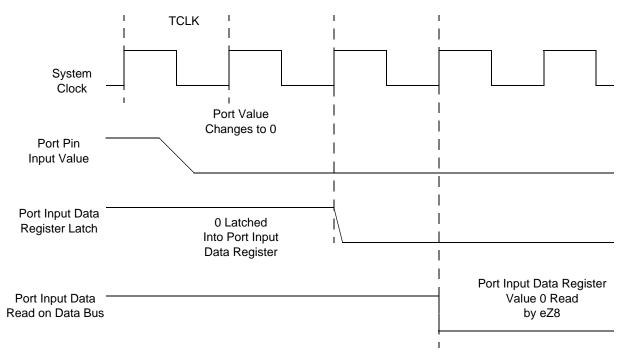

| Table 130. GPIO Port Input Timing |  |

|-----------------------------------|--|

|                                   |  |

|                     |                                                                                                    | Delay (ns) |         |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (Not pictured)                            | 5          | _       |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (Not pictured)                             | 0          | _       |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO Port Pins enabled as SMR sources) | 1 μs       |         |

edded in Life

An∎IXYS Company

207

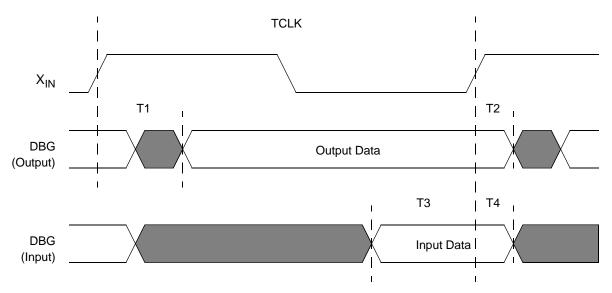

# **On-Chip Debugger Timing**

Figure 31 and Table 132 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

|                |                                              | Delay (ns) |                 |  |

|----------------|----------------------------------------------|------------|-----------------|--|

| Parameter      | Abbreviation                                 | Minimum    | linimum Maximum |  |

| DBG            |                                              |            |                 |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | _          | 15              |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2          | -               |  |

| T <sub>3</sub> | DBG to X <sub>IN</sub> Rise Input Setup Time | 5          | _               |  |

| T <sub>4</sub> | DBG to X <sub>IN</sub> Rise Input Hold Time  | 5          | _               |  |

#### Table 132. On-Chip Debugger Timing

nbedded in Life

read OCD revision (00H) 163 read OCD status register (02H) 163 read program counter (07H) 164 read program memory (0BH) 164 read program memory CRC (0EH) 165 read register (09H) 164 read runtime counter (03H) 163 step instruction (10H) 165 stuff instruction (11H) 166 write data memory (0CH) 165 write OCD control register (04H) 163 write program counter (06H) 163 write program memory (0AH) 164 write register (08H) 164 on-chip debugger (OCD) 156 on-chip debugger signals 10 ONE-SHOT mode 88 opcode map abbreviations 193 cell description 192 first 194 second after 1FH 195 Operational Description 21, 30, 33, 69, 91, 97, 117, 121, 132, 134, 146, 156, 169, 173 OR 181 ordering information 211 **ORX 181**

## Ρ

p 176 Packaging 210 part selection guide 2 PC 177 peripheral AC and DC electrical characteristics 201 pin characteristics 11 Pin Descriptions 7 polarity 176 POP 180 pop using extended addressing 180 POPX 180 port availability, device 33 port input timing (GPIO) 205 port output timing, GPIO 206 power supply signals 10

Power-on and Voltage Brownout electrical characteristics and timing 201

Power-On Reset (POR) 23

program control instructions 181

program counter 177

program memory 13

PUSH 180

push using extended addressing 180

PUSHX 180

PWM mode 89

PxADDR register 41

PxCTL register 42

# R

R 176 r 176 RA register address 177 RCF 179. 180 receive IrDA data 119 receiving UART data-interrupt-driven method 102 receiving UART data-polled method 101 register 176 ADC control (ADCCTL) 126, 129 ADC data high byte (ADCDH) 130 ADC data low bits (ADCDL) 131 flash control (FCTL) 141, 148, 149 flash high and low byte (FFREQH and FRE-EQL) 144 flash page select (FPS) 142, 144 flash status (FSTAT) 142 GPIO port A-H address (PxADDR) 41 GPIO port A-H alternate function sub-registers 44 GPIO port A-H control address (PxCTL) 42 GPIO port A-H data direction sub-registers 43 OCD control 166 OCD status 168 UARTx baud rate high byte (UxBRH) 115 UARTx baud rate low byte (UxBRL) 115 UARTx Control 0 (UxCTL0) 112, 115