Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0823pj005sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ilog° Embedded in Life An IXYS Company

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                                                         | Description                                                                                                                                                                                                                          | Page<br>No.                                                         |

|-------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Sep         | 15                | LED Drive Enable Register                                                                                                                               | Clarified statement surrounding the Alternate<br>Function Register as it relates to the LED<br>function; revised Flash Sector Protect Regis-<br>ter description; revised Packaging chapter.                                          | <u>51,</u><br><u>144,</u><br><u>210</u>                             |

| Mar<br>2008 | 14                | n/a                                                                                                                                                     | Changed branding to <i>Z8 Encore! XP F0823</i><br><i>Series</i> where appropriate.                                                                                                                                                   | All                                                                 |

| Dec<br>2007 | 13                | Pin Description, General-Pur-<br>pose Input/Output, Interrupt<br>Controller, Watchdog Timer,<br>Electrical Characteristics, and<br>Ordering Information | Updated title from <i>Z8 Encore! 8K and 4K</i><br><i>Series</i> to <i>Z8 Encore! XP Z8F0823 Series</i> .<br>Updated Figure 3, Table 15, Table 35, Tables<br>59 through 61, Table 119 and Part Number<br>Suffix Designations section. | <u>8, 36,</u><br><u>60, 95,</u><br><u>199,</u><br>and<br><u>220</u> |

| Aug<br>2007 | 12                | Part Selection Guide, External<br>Clock Setup, and Program<br>Memory                                                                                    | Updated Table 1, Table 16, and Program Memory section.                                                                                                                                                                               | <u>2, 35,</u><br>and <u>13</u>                                      |

| Jun<br>2007 | 11                | n/a                                                                                                                                                     | Updated to combine Z8 Encore! 8K and Z8 Encore! 4K Series.                                                                                                                                                                           | All                                                                 |

| Dec<br>2006 | 10                | Ordering Information                                                                                                                                    | Updated Ordering Information chapter.                                                                                                                                                                                                | <u>211</u>                                                          |

8

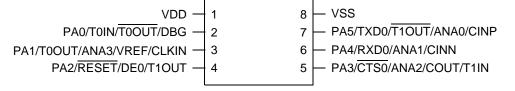

Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

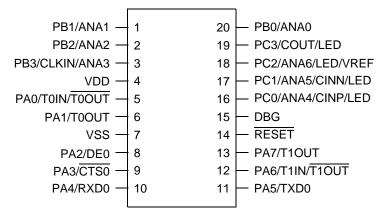

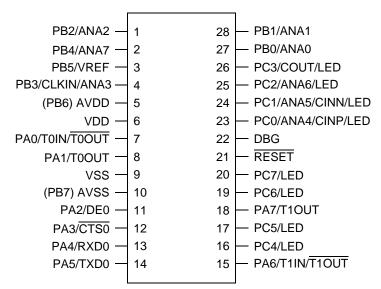

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

16

n 🗖 IXYS Company

# **Register Map**

Table 8 lists an address map of the Z8 Encore! XP F0823 Series Register File. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, nor all GPIO ports. Consider registers for unimplemented peripherals to be reserved.

| Address (Hex)  | Register Description              | Mnemonic | Reset (Hex) | Page<br>No. |

|----------------|-----------------------------------|----------|-------------|-------------|

| General-Purpos | e RAM                             |          |             |             |

| Z8F0823/Z8F081 | 13 Devices                        |          |             |             |

| 000–3FF        | General-Purpose Register File RAM | _        | XX          |             |

| 400-EFF        | Reserved                          | _        | XX          |             |

| Z8F0423/Z8F041 | 13 Devices                        |          |             |             |

| 000–3FF        | General-Purpose Register File RAM |          | XX          |             |

| 400–EFF        | Reserved                          | _        | XX          |             |

| Z8F0223/Z8F021 | 13 Devices                        |          |             |             |

| 000–1FF        | General-Purpose Register File RAM |          | XX          |             |

| 200–EFF        | Reserved                          | _        | XX          |             |

| Z8F0123/Z8F011 | 13 Devices                        |          |             |             |

| 000–0FF        | General-Purpose Register File RAM |          | XX          |             |

| 100-EFF        | Reserved                          | _        | XX          |             |

| Timer 0        |                                   |          |             |             |

| F00            | Timer 0 High Byte                 | T0H      | 00          | <u>84</u>   |

| F01            | Timer 0 Low Byte                  | TOL      | 01          | <u>84</u>   |

| F02            | Timer 0 Reload High Byte          | TORH     | FF          | <u>85</u>   |

| F03            | Timer 0 Reload Low Byte           | TORL     | FF          | <u>85</u>   |

| F04            | Timer 0 PWM High Byte             | TOPWMH   | 00          | <u>86</u>   |

| F05            | Timer 0 PWM Low Byte              | TOPWML   | 00          | <u>86</u>   |

| F06            | Timer 0 Control 0                 | TOCTLO   | 00          | <u>87</u>   |

| F07            | Timer 0 Control 1                 | T0CTL1   | 00          | <u>88</u>   |

| Timer 1        |                                   |          |             |             |

| F08            | Timer 1 High Byte                 | T1H      | 00          | <u>84</u>   |

| F09            | Timer 1 Low Byte                  | T1L      | 01          | <u>84</u>   |

#### Table 8. Register File Address Map

Note: XX=Undefined.

Embedded in Life

38

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>4</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

|                     |     | ANA6/V <sub>REF</sub> <sup>6</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

#### Table 17. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in the <u>Port A–C Alternate Function</u> Subregisters section on page 43 automatically enables the associated alternate function.

- 2. Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in the <u>Timer Pin Signal Operation</u> section on page 83.

- 3. Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, alternate function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

- 4. V<sub>REF</sub> is available on PB5 in 28-pin products only.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in the <u>Port A–C Alternate Function Subregisters</u> section on page 43 must also be enabled.

- 6. V<sub>REF</sub> is available on PC2 in 20-pin parts only.

# **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3mA, 7mA, 13mA, and 20mA. This mode is enabled through the LED control registers. The LED Drive Enable (LEDEN) register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

nbedded in Life

46

## Port A–C Stop Mode Recovery Source Enable Subregisters

The Port A–C Stop Mode Recovery Source Enable Subregister (Table 26) is accessed through the Port A–C Control Register by writing 05H to the Port A–C Address Register. Setting the bits in the Port A–C Stop Mode Recovery Source Enable subregisters to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

Table 26. Port A–C Stop Mode Recovery Source Enable Subregisters (PSMREx)

| Bit     | 7         | 6            | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | PSMRE7    | PSMRE6       | PSMRE5      | PSMRE4        | PSMRE3       | PSMRE2       | PSMRE1       | PSMRE0   |

| RESET   | 0         | 0            | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W     | R/W       | R/W          | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | If 05H ir | n Port A–C A | Address Reg | jister, acces | sible throug | h the Port A | -C Control F | Register |

#### Bit Description

| [7:0] | Port Stop Mode Recovery Source Enabled. |

|-------|-----------------------------------------|

|-------|-----------------------------------------|

PSMREx 0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7–0).

# LED Drive Level High Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 33). These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit     | 7   | 6    | 5   | 4     | 3       | 2   | 1   | 0   |

|---------|-----|------|-----|-------|---------|-----|-----|-----|

| Field   |     |      |     | LEDLV | LH[7:0] |     |     |     |

| RESET   | 0   | 0    | 0   | 0     | 0       | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Address |     | F83H |     |       |         |     |     |     |

## Table 33. LED Drive Level High Register (LEDLVLH)

| Bit     | Description                                                                             |

|---------|-----------------------------------------------------------------------------------------|

| [7:0]   | LED Level High Bit                                                                      |

| LEDLVLH | {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C |

|         | pin.                                                                                    |

|         | 00 = 3 mA.                                                                              |

|         | 01= 7 mA.                                                                               |

|         | 10= 13mA.                                                                               |

|         | 11= 20mA.                                                                               |

52

Embedded in Life

n 🖬 IXYS Company

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is

#### ilog Embedded in Life An IXYS Company 113

| Bit         | Description (Continued)                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>STOP | <ul> <li>Stop Bit Select</li> <li>0 = The transmitter sends one stop bit.</li> <li>1 = The transmitter sends two stop bits.</li> </ul> |

| [0]<br>LBEN | Loop Back Enable<br>0 = Normal operation.<br>1 = All transmitted data is looped back to the receiver.                                  |

### Table 69. UART Control 1 Register (U0CTL1)

| Bit                                                                                                                                                                                   | 7        | 6            | 5              | 4            | 3             | 2            | 1             | 0          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|----------------|--------------|---------------|--------------|---------------|------------|

| Field                                                                                                                                                                                 | MPMD[1]  | MPEN         | MPMD[0]        | MPBT         | DEPOL         | BRGCTL       | RDAIRQ        | IREN       |

| RESET                                                                                                                                                                                 | 0        | 0            | 0              | 0            | 0             | 0            | 0             | 0          |

| R/W                                                                                                                                                                                   | R/W      | R/W          | R/W            | R/W          | R/W           | R/W          | R/W           | R/W        |

| Address                                                                                                                                                                               |          |              | •              | F4           | 3H            | •            |               |            |

|                                                                                                                                                                                       |          |              |                |              |               |              |               |            |

| Bit                                                                                                                                                                                   | Descript | tion         |                |              |               |              |               |            |

| [7,5]     MULTIPROCESSOR Mode       MPMD[1:0]     If MULTIPROCESSOR (9-bit) Mode is enabled.                                                                                          |          |              |                |              |               |              |               |            |

|                                                                                                                                                                                       | -        |              | · · ·          |              |               | aived bytes  | (data and a   | ddrooo)    |

| 00 = The UART generates an interrupt request on all received bytes (data and addre                                                                                                    |          |              |                |              | aaress).      |              |               |            |

| <ul><li>01 = The UART generates an interrupt request only on received address bytes.</li><li>10 = The UART generates an interrupt request when a received address byte mate</li></ul> |          |              |                |              |               |              |               |            |

|                                                                                                                                                                                       |          |              |                |              |               |              |               |            |

|                                                                                                                                                                                       | valu     | le stored in | the Address    | Compare R    | egister and   | on all succe | ssive data b  | ytes until |

|                                                                                                                                                                                       | an a     | address mis  | match occur    | S.           |               |              |               |            |

|                                                                                                                                                                                       | 11 – Tho |              | arates an inte | errunt reque | st on all rec | d etch havia | vtes for whic | h the most |

| 11 = The UART generates an interrupt request on all received data bytes for which the most |

|--------------------------------------------------------------------------------------------|

| recent address byte matched the value in the Address Compare Register.                     |

| [6]<br>MPEN  | MULTIPROCESSOR (9-bit) Enable<br>This bit is used to enable MULTIPROCESSOR (9-bit) Mode.<br>0 = Disable MULTIPROCESSOR (9-bit) Mode.<br>1 = Enable MULTIPROCESSOR (9-bit) Mode.                                                                                                                                                                                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>MPBT  | <ul> <li>Multiprocessor Bit Transmit</li> <li>This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.</li> <li>0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).</li> <li>1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li> </ul> |

| [3]<br>DEPOL | Driver Enable Polarity<br>0 = DE signal is Active High.<br>1 = DE signal is Active Low.                                                                                                                                                                                                                                                                                                                                                |

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### ilog Embedded in Life An∎IXYS Company 115

# **UART Address Compare Register**

The UART Address Compare Register stores the multinode network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

| Bit     | 7         | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----------|------|-----|-----|-----|-----|-----|-----|

| Field   | COMP_ADDR |      |     |     |     |     |     |     |

| RESET   | 0         | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W       | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |           | F45H |     |     |     |     |     |     |

| Table 70. UART Address Compare Register (U0ADDR | Table 70. UART Address Com | npare Register (U0ADDR) |

|-------------------------------------------------|----------------------------|-------------------------|

|-------------------------------------------------|----------------------------|-------------------------|

| Bit       | Description                                             |

|-----------|---------------------------------------------------------|

| [7:0]     | Compare Address                                         |

| COMP_ADDR | This 8-bit value is compared to incoming address bytes. |

# **UART Baud Rate High and Low Byte Registers**

The UART Baud Rate High and Low Byte registers (Table 71 and Table 72) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------|-----|-----|-----|-----|-----|-----|

| Field   | BRH |      |     |     |     |     |     |     |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F46H |     |     |     |     |     |     |

Table 71. UART Baud Rate High Byte Register (U0BRH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------|-----|-----|-----|-----|-----|-----|

| Field   | BRL |      |     |     |     |     |     |     |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F47H |     |     |     |     |     |     |

### ilog<sup>®</sup> Embedded in Life An LIXYS Company 128

| Bit            | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3:0]<br>ANAIN | <ul> <li>Analog Input Select</li> <li>These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore! XP F0823 Series. For information about the port pins available with each package style, see the Pin Description section on page 7. Do not enable unavail able analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.</li> <li>For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.</li> </ul> |

|                | Single-Ended: $0000 = ANA0.$ $0001 = ANA1.$ $0010 = ANA2.$ $0011 = ANA3.$ $0100 = ANA4.$ $0101 = ANA5.$ $0110 = ANA6.$ $0111 = ANA7.$ $1000 = Reserved.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | 1000 = Reserved.<br>1001 = Reserved.<br>1010 = Reserved.<br>1011 = Reserved.<br>1100 = Reserved.<br>1101 = Reserved.<br>1110 = Reserved.<br>1111 = Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### illog<sup>®</sup> Ibedded in Life IXYS Company 138

# Table 80. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code program-<br>ming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-<br>Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                    |

## Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

## **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F0823 Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 79</u> on page 134.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

| Bit           | Description                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 111 during writes and to 111 when read.                                                                                                                                                                                                                                                                |

| [4]<br>XTLDIS | <ul> <li>State of Crystal Oscillator at Reset</li> <li>This bit only enables the crystal oscillator. Its selection as a system clock must be performed manually.</li> <li>0 = The crystal oscillator is enabled during reset, resulting in longer reset timing.</li> <li>1 = The crystal oscillator is disabled during reset, resulting in shorter reset timing.</li> </ul> |

|               | <b>Caution:</b> Programming the XTLDIS bit to zero on 8-pin versions of F0823 Series devices prevents any further communication via the debug pin due to the $X_{IN}$ and DBG functions being shared on pin 2 of the 8-pin package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.                          |

| [3:0]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 1111 during writes and to 1111 when read                                                                                                                                                                                                                                                               |

# Trim Bit Address Space

All available trim bit addresses and their functions are listed in Tables 91 through 93.

| Bit                                             | 7                             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field                                           | Reserved                      |     |     |     |     |     |     |     |

| RESET                                           | U                             | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 0020H |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |     |     |     |     |     |     |     |

#### Table 91. Trim Options Bits at Address 0000H

| Bit   | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                  |

|       | These bits are reserved. Altering this register may result in incorrect device operation. |

ILO<u>G</u> abedded in Life

169

# **Oscillator Control**

Z8 Encore! XP F0823 Series devices uses three possible clocking schemes, each userselectable. These three schemes are:

- On-chip precision trimmed RC oscillator

- External clock drive

- On-chip low power Watchdog Timer oscillator

In addition, F0823 Series devices contain clock failure detection and recovery circuitry, which allow continued operation despite a failure of the primary oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document.

## **System Clock Selection**

The oscillator control block selects from the available clocks. Table 104 details each clock source and its usage.

| Clock Source                          | Characteristics                                                                                                                | Required Setup                                                                                                                                                                                                  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8kHz or 5.53MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>            | <ul> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator at either 5.53MHz or<br/>32.8kHz</li> </ul>                                                              |

| External Clock<br>Drive               | <ul> <li>0 to 20MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul> |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Very Low power consumption</li> </ul> | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>            |

Table 104. Oscillator Configuration and Selection

nbedded in Life

170

ages to the Oscillator Control Desistor can actually stor the ship by

**Caution:** Unintentional accesses to the Oscillator Control Register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

## **OSC Control Register Unlocking/Locking**

To write to the Oscillator Control Register, unlock it by making two writes to the OSC-CTL Register with the values E7H followed by 18H. A third write to the OSCCTL Register changes the value of the actual register and returns the register to a locked state. Any other sequence of Oscillator Control Register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

## **Clock Failure Detection and Recovery**

Should an oscillator or timer fail, there are methods of recovery, as this section describes.

## **Primary Oscillator Failure**

Z8 Encore! XP F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the the <u>Watchdog Timer</u> section on page 91.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below  $1 \text{ kHz} \pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these

I

ilog Embedded in Life An IXYS Company 172

## Table 105. Oscillator Control Register (OSCCTL)

| Bit             | 7                                                                                                                                                                                                                                                                                                                                                                                                 | 6        | 5     | 4     | 3     | 2      | 1   | 0   |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------|-------|--------|-----|-----|--|--|--|--|--|

| Field           | INTEN                                                                                                                                                                                                                                                                                                                                                                                             | Reserved | WDTEN | POFEN | WDFEN | SCKSEL |     |     |  |  |  |  |  |

| RESET           | 1                                                                                                                                                                                                                                                                                                                                                                                                 | 0        | 1     | 0     | 0     | 0      | 0   | 0   |  |  |  |  |  |

| R/W             | R/W                                                                                                                                                                                                                                                                                                                                                                                               | R/W      | R/W   | R/W   | R/W   | R/W    | R/W | R/W |  |  |  |  |  |

| Address         | F86H                                                                                                                                                                                                                                                                                                                                                                                              |          |       |       |       |        |     |     |  |  |  |  |  |

| Bit             | Description                                                                                                                                                                                                                                                                                                                                                                                       |          |       |       |       |        |     |     |  |  |  |  |  |

| [7]<br>INTEN    | Internal Precision Oscillator Enable<br>1 = Internal precision oscillator is enabled.<br>0 = Internal precision oscillator is disabled.                                                                                                                                                                                                                                                           |          |       |       |       |        |     |     |  |  |  |  |  |

| [6]             | <b>Reserved</b><br>This bit is reserved and must be programmed to 0 during writes and to 0 when read.                                                                                                                                                                                                                                                                                             |          |       |       |       |        |     |     |  |  |  |  |  |

| [5]<br>WDTEN    | Watchdog Timer Oscillator Enable<br>1 = Watchdog Timer oscillator is enabled.<br>0 = Watchdog Timer oscillator is disabled.                                                                                                                                                                                                                                                                       |          |       |       |       |        |     |     |  |  |  |  |  |

| [4]<br>POFEN    | <ul> <li>Primary Oscillator Failure Detection Enable</li> <li>1 = Failure detection and recovery of primary oscillator is enabled.</li> <li>0 = Failure detection and recovery of primary oscillator is disabled.</li> </ul>                                                                                                                                                                      |          |       |       |       |        |     |     |  |  |  |  |  |

| [3]<br>WDFEN    | Watchdog Timer Oscillator Failure Detection Enable1 = Failure detection of Watchdog Timer oscillator is enabled.0 = Failure detection of Watchdog Timer oscillator is disabled.                                                                                                                                                                                                                   |          |       |       |       |        |     |     |  |  |  |  |  |

| [2:0]<br>SCKSEL | System Clock Oscillator Select<br>000 = Internal precision oscillator functions as system clock at 5.53MHz.<br>001 = Internal precision oscillator functions as system clock at 32kHz.<br>010 = Reserved.<br>011 = Watchdog Timer oscillator functions as system clock.<br>100 = External clock signal on PB3 functions as system clock.<br>101 = Reserved.<br>110 = Reserved.<br>111 = Reserved. |          |       |       |       |        |     |     |  |  |  |  |  |

ilog° Embedded in Life An∎IXYS Company

185

| Assembly     |                                                                                                                   |     | Address<br>Mode Opcode(s) |       |   |   |   | ags |   |   | _ Fetch | Instr. |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----|---------------------------|-------|---|---|---|-----|---|---|---------|--------|

| Mnemonic     | Symbolic Operation                                                                                                | dst | src                       | (Hex) |   | Ζ | S | V   | D | н | Cycles  |        |

| DA dst       | $dst \gets DA(dst)$                                                                                               | R   |                           | 40    | * | * | * | Х   | - | _ | 2       | 2      |

|              |                                                                                                                   | IR  |                           | 41    | • |   |   |     |   |   | 2       | 3      |

| DEC dst      | dst ← dst - 1                                                                                                     | R   |                           | 30    | - | * | * | *   | - | _ | 2       | 2      |

|              |                                                                                                                   | IR  |                           | 31    | • |   |   |     |   |   | 2       | 3      |

| DECW dst     | dst ← dst - 1                                                                                                     | RR  |                           | 80    | _ | * | * | *   | _ | _ | 2       | 5      |

|              |                                                                                                                   | IRR |                           | 81    | • |   |   |     |   |   | 2       | 6      |

| DI           | IRQCTL[7] ← 0                                                                                                     |     |                           | 8F    | - | - | _ | -   | - | _ | 1       | 2      |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                             | r   |                           | 0A-FA | - | _ | - | -   | - | _ | 2       | 3      |

| EI           | IRQCTL[7] ← 1                                                                                                     |     |                           | 9F    | _ | _ | _ | -   | _ | _ | 1       | 2      |

| HALT         | HALT Mode                                                                                                         |     |                           | 7F    | - | _ | _ | -   | _ | _ | 1       | 2      |

| INC dst      | dst ← dst + 1                                                                                                     | R   |                           | 20    | _ | * | * | -   | _ | _ | 2       | 2      |

|              |                                                                                                                   | IR  |                           | 21    | • |   |   |     |   |   | 2       | 3      |

|              |                                                                                                                   | r   |                           | 0E-FE | • |   |   |     |   |   | 1       | 2      |

| INCW dst     | dst ← dst + 1                                                                                                     | RR  |                           | A0    | _ | * | * | *   | _ | _ | 2       | 5      |

|              |                                                                                                                   | IRR |                           | A1    | • |   |   |     |   |   | 2       | 6      |

| IRET         | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |     |                           | BF    | * | * | * | *   | * | * | 1       | 5      |

| JP dst       | PC ← dst                                                                                                          | DA  |                           | 8D    | _ | _ | _ | _   | _ | _ | 3       | 2      |

|              |                                                                                                                   | IRR |                           | C4    | • |   |   |     |   |   | 2       | 3      |

| JP cc, dst   | if cc is true<br>PC $\leftarrow$ dst                                                                              | DA  |                           | 0D-FD | _ | - | - | -   | - | - | 3       | 2      |

| JR dst       | $PC \leftarrow PC + X$                                                                                            | DA  |                           | 8B    | - | - | _ | _   | _ | _ | 2       | 2      |

| JR cc, dst   | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA  |                           | 0B-FB | _ | - | _ | _   | _ | _ | 2       | 2      |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

edded in Life

An∎IXYS Company

207

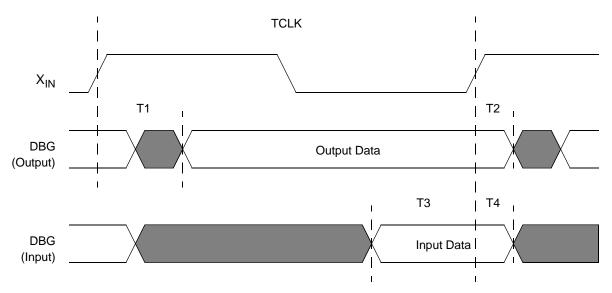

# **On-Chip Debugger Timing**

Figure 31 and Table 132 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

|                |                                              | Delay (ns) |         |  |  |  |

|----------------|----------------------------------------------|------------|---------|--|--|--|

| Parameter      | Abbreviation                                 | Minimum    | Maximum |  |  |  |

| DBG            |                                              |            |         |  |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | _          | 15      |  |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2          | -       |  |  |  |

| T <sub>3</sub> | DBG to X <sub>IN</sub> Rise Input Setup Time | 5          | _       |  |  |  |

| T <sub>4</sub> | DBG to X <sub>IN</sub> Rise Input Hold Time  | 5          | _       |  |  |  |

#### Table 132. On-Chip Debugger Timing

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

209

0g

■IXYS Company

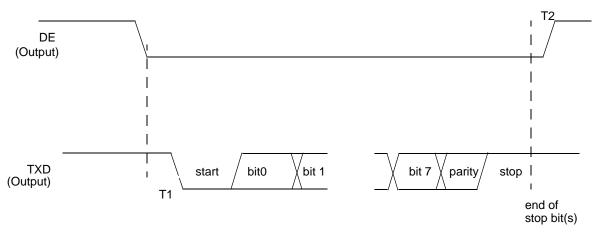

Figure 33 and Table 134 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

|                |                                                                        | Delay (ns)                 |            |  |  |  |

|----------------|------------------------------------------------------------------------|----------------------------|------------|--|--|--|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |  |  |  |

| UART           |                                                                        |                            |            |  |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5                        |            |  |  |  |

219

ilog<sup>®</sup> Embedded in Life

An∎IXYS Company

| Part Number                                | Flash                                                                       | RAM    | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description             |  |

|--------------------------------------------|-----------------------------------------------------------------------------|--------|-----------|------------|------------------------|---------------------|----------------|-------------------------|--|

| Z8 Encore! XP F0823 Series Development Kit |                                                                             |        |           |            |                        |                     |                |                         |  |

| Z8F08A28100KITG                            | Z8F08A28100KITG Z8 Encore! XP F082A Series Development Kit (20- and 28-Pin) |        |           |            |                        |                     |                | nt Kit (20- and 28-Pin) |  |

| Z8F04A28100KITG                            |                                                                             | Z8 En  | core! X   | P F04      | 2A Seri                | es Dev              | velopme        | nt Kit (20- and 28-Pin) |  |

| Z8F04A08100KITG                            |                                                                             | Z8 En  | core! X   | P F04      | 2A Seri                | es Dev              | velopme        | nt Kit (8-Pin)          |  |

| ZUSBSC00100ZACG                            |                                                                             | USB S  | Smart C   | Cable A    | Accesso                | ry Kit              |                |                         |  |

| ZUSBOPTSC01ZACG                            |                                                                             | Opto-I | solated   | USB        | Smart (                | Cable A             | Accesso        | ry Kit                  |  |

| ZENETSC0100ZACG                            |                                                                             | Etherr | net Sma   | art Cal    | ble Acce               | essory              | Kit            |                         |  |

## Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

## G

GATED mode 89 general-purpose I/O 33 GPIO 4.33 alternate functions 34 architecture 34 control register definitions 40 input data sample timing 204 interrupts 40 port A-C pull-up enable sub-registers 47, 48, 49 port A-H address registers 41 port A-H alternate function sub-registers 43 port A-H control registers 42 port A-H data direction sub-registers 43 port A-H high drive enable sub-registers 45 port A-H input data registers 50 port A-H output control sub-registers 44 port A-H output data registers 51 port A-H stop mode recovery sub-registers 46 port availability by device 33 port input timing 205 port output timing 206

## Η

H 177 HALT 180 halt mode 31, 180 hexadecimal number prefix/suffix 177

## I

I2C 4 IM 176 immediate data 176 immediate operand prefix 177 INC 178 increment 178 increment word 178 INCW 178 indexed 177 indirect address prefix 177 indirect register 176 indirect register pair 176 indirect working register 176 indirect working register pair 176 infrared encoder/decoder (IrDA) 117 Instruction Set 174 instruction set, eZ8 CPU 174 instructions ADC 178 **ADCX 178** ADD 178 **ADDX 178** AND 181 **ANDX 181** arithmetic 178 **BCLR 179 BIT 179** bit manipulation 179 block transfer 179 **BRK 181 BSET 179** BSWAP 179, 181 BTJ 181 **BTJNZ 181 BTJZ 181 CALL 181** CCF 179, 180 **CLR 180** COM 181 CP 178 **CPC 178 CPCX 178** CPU control 180 **CPX 178** DA 178 **DEC 178 DECW 178** DI 180 DJNZ 181 EI 180 **HALT 180 INC 178 INCW 178 IRET 181** JP 181