Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | ARM® Cortex®-M4                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, MMC/SD, SPI, UART/USART, USB OTG, USIC |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, Touch-Sense, WDT                                  |

| Number of I/O              | 73                                                                                 |

| Program Memory Size        | 256KB (256K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 128K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                      |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                              |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-LQFP Exposed Pad                                                               |

| Supplier Device Package    | PG-LQFP-100-25                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4300f100f256aaxqma1  |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 3.3.8.2  | Inter-IC (IIC) Interface Timing                      | 76 |

|----------|------------------------------------------------------|----|

| 3.3.8.3  | Inter-IC Sound (IIS) Interface Timing                | 78 |

| 3.3.8.4  | SDMMC Interface Timing                               | 80 |

| 3.3.9    | USB Interface Characteristics                        | 89 |

| 3.3.10   | Ethernet Interface (ETH) Characteristics             |    |

| 3.3.10.1 | ETH Measurement Reference Points                     | 90 |

| 3.3.10.2 | ETH Management Signal Parameters (ETH_MDC, ETH_MDIO) |    |

| 3.3.10.3 | ETH RMII Parameters                                  | 92 |

| 3.3.11   | EtherCAT (ECAT) Characteristics                      |    |

| 3.3.11.1 | ECAT Measurement Reference Points                    |    |

| 3.3.11.2 | ETH Management Signal Parameters (MCLK, MDIO)        | 93 |

| 3.3.11.3 | MII Timing TX Characteristics                        |    |

| 3.3.11.4 | MII Timing RX Characteristics                        |    |

| 3.3.11.5 | Sync/Latch Timings                                   | 97 |

| 4        | Package and Reliability                              | 98 |

| 4.1      | Package Parameters                                   | 98 |

| 4.1.1    | Thermal Considerations                               | 98 |

| 4.2      | Package Outlines                                     | 00 |

| 5        | Quality Declarations 1                               | 01 |

## **Summary of Features**

Table 2 Features of XMC4300 Device Types

| Derivative <sup>1)</sup> | LED<br>TS<br>Intf. | SD<br>MMC<br>Intf. | ETH<br>Intf. |         | USB<br>Intf. | USIC<br>Chan. | MultiCAN<br>Nodes, MO |

|--------------------------|--------------------|--------------------|--------------|---------|--------------|---------------|-----------------------|

| XMC4300-F100x256         | 1                  | 1                  | RMII         | 2 x MII | 1            | 2 x 2         | N0, N1<br>MO[063]     |

<sup>1)</sup> x is a placeholder for the supported temperature range.

## Table 3 Features of XMC4300 Device Types

| Derivative <sup>1)</sup> | ADC Chan. | DAC Chan. | CCU4 Slice | CCU8 Slice |

|--------------------------|-----------|-----------|------------|------------|

| XMC4300-F100x256         | 16        | 2         | 2 x 4      | 1 x 4      |

<sup>1)</sup> x is a placeholder for the supported temperature range.

#### 1.4 Definition of Feature Variants

The XMC4300 types are offered with several memory sizes and number of available VADC channels. **Table 4** describes the location of the available Flash memory, **Table 5** describes the location of the available SRAMs, **Table 6** the available VADC channels.

## Table 4 Flash Memory Ranges

| Total Flash Size | Cached Range                                    | <b>Uncached Range</b>                              |

|------------------|-------------------------------------------------|----------------------------------------------------|

| 256 Kbytes       | 0800 0000 <sub>H</sub> - 0803 FFFF <sub>H</sub> | 0C00 0000 <sub>H</sub> -<br>0C03 FFFF <sub>H</sub> |

## Table 5 SRAM Memory Ranges

| Total SRAM Size | Program SRAM             | System Data SRAM         |

|-----------------|--------------------------|--------------------------|

| 128 Kbytes      | 1FFF 0000 <sub>H</sub> - | 2000 0000 <sub>H</sub> - |

|                 | 1FFF FFFF <sub>H</sub>   | 2000 FFFF <sub>H</sub>   |

# Table 6 ADC Channels<sup>1)</sup>

| Package     | VADC G0 | VADC G1 |

|-------------|---------|---------|

| PG-LQFP-100 | CH0CH7  | CH0CH7  |

Some pins in a package may be connected to more than one channel. For the detailed mapping see the Port I/O Function table.

## **General Device Information**

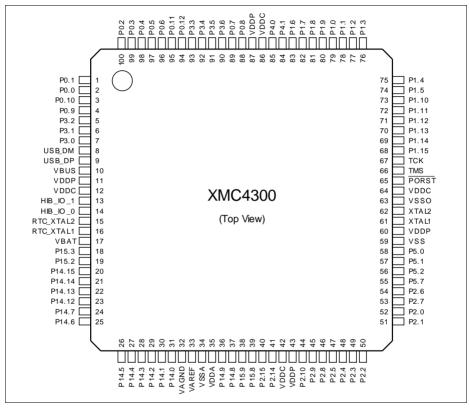

# 2.2 Pin Configuration and Definition

The following figures summarize all pins, showing their locations on the four sides of the different packages.

Figure 3 XMC4300 PG-LQFP-100 Pin Configuration (top view)

## **General Device Information**

Table 9 Package Pin Mapping (cont'd)

| Function | LQFP-100 | Pad Type      | Notes |

|----------|----------|---------------|-------|

| P3.2     | 5        | A2            |       |

| P3.3     | 93       | A1+           |       |

| P3.4     | 92       | A1+           |       |

| P3.5     | 91       | A2            |       |

| P3.6     | 90       | A2            |       |

| P4.0     | 85       | A2            |       |

| P4.1     | 84       | A2            |       |

| P5.0     | 58       | A1+           |       |

| P5.1     | 57       | A1+           |       |

| P5.2     | 56       | A1+           |       |

| P5.7     | 55       | A1+           |       |

| P14.0    | 31       | AN/DIG_IN     |       |

| P14.1    | 30       | AN/DIG_IN     |       |

| P14.2    | 29       | AN/DIG_IN     |       |

| P14.3    | 28       | AN/DIG_IN     |       |

| P14.4    | 27       | AN/DIG_IN     |       |

| P14.5    | 26       | AN/DIG_IN     |       |

| P14.6    | 25       | AN/DIG_IN     |       |

| P14.7    | 24       | AN/DIG_IN     |       |

| P14.8    | 37       | AN/DAC/DIG_IN |       |

| P14.9    | 36       | AN/DAC/DIG_IN |       |

| P14.12   | 23       | AN/DIG_IN     |       |

| P14.13   | 22       | AN/DIG_IN     |       |

| P14.14   | 21       | AN/DIG_IN     |       |

| P14.15   | 20       | AN/DIG_IN     |       |

| P15.2    | 19       | AN/DIG_IN     |       |

| P15.3    | 18       | AN/DIG_IN     |       |

| P15.8    | 39       | AN/DIG_IN     |       |

| P15.9    | 38       | AN/DIG_IN     |       |

## **General Device Information**

Table 9 Package Pin Mapping (cont'd)

| Function  | LQFP-100 | Pad Type   | Notes                                                                                                                                                                       |

|-----------|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIB_IO_0  | 14       | A1 special | At the first power-up and with every reset of the hibernate domain this pin is configured as open-drain output and drives "0".  As output the medium driver mode is active. |

| HIB_IO_1  | 13       | A1 special | At the first power-up and with every reset of the hibernate domain this pin is configured as input with no pull device active.  As output the medium driver mode is active. |

| USB_DP    | 9        | special    |                                                                                                                                                                             |

| USB_DM    | 8        | special    |                                                                                                                                                                             |

| TCK       | 67       | A1         | Weak pull-down active.                                                                                                                                                      |

| TMS       | 66       | A1+        | Weak pull-up active. As output the strong-soft driver mode is active.                                                                                                       |

| PORST     | 65       | special    | Weak pull-up permanently active, strong pull-down controlled by EVR.                                                                                                        |

| XTAL1     | 61       | clock_IN   |                                                                                                                                                                             |

| XTAL2     | 62       | clock_O    |                                                                                                                                                                             |

| RTC_XTAL1 | 16       | clock_IN   |                                                                                                                                                                             |

| RTC_XTAL2 | 15       | clock_O    |                                                                                                                                                                             |

| VBAT      | 17       | Power      | When VDDP is supplied VBAT has to be supplied as well.                                                                                                                      |

| VBUS      | 10       | special    |                                                                                                                                                                             |

| VAREF     | 33       | AN_Ref     |                                                                                                                                                                             |

| VAGND     | 32       | AN_Ref     |                                                                                                                                                                             |

| VDDA      | 35       | AN_Power   |                                                                                                                                                                             |

| VSSA      | 34       | AN_Power   |                                                                                                                                                                             |

| VDDC      | 12       | Power      |                                                                                                                                                                             |

| VDDC      | 42       | Power      |                                                                                                                                                                             |

| VDDC      | 64       | Power      |                                                                                                                                                                             |

| VDDC      | 86       | Power      |                                                                                                                                                                             |

| VDDP      | 11       | Power      |                                                                                                                                                                             |

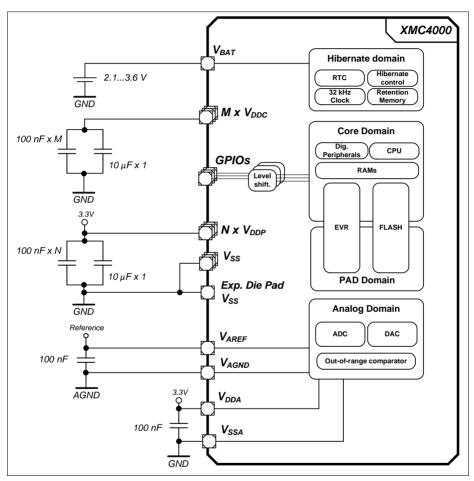

#### 2.3 Power Connection Scheme

Figure 5. shows a reference power connection scheme for the XMC4300.

Figure 5 Power Connection Scheme

Every power supply pin needs to be connected. Different pins of the same supply need also to be externally connected. As example, all  $V_{\rm DDP}$  pins must be connected externally to one  $V_{\rm DDP}$  net. In this reference scheme one 100 nF capacitor is connected at each supply pin against  $V_{\rm SS}$ . An additional 10 µF capacitor is connected to the  $V_{\rm DDP}$  nets and an additional 10 uF capacitor to the  $V_{\rm DDC}$  nets.

Subject to Agreement on the Use of Product Information

### 3.2 DC Parameters

## 3.2.1 Input/Output Pins

The digital input stage of the shared analog/digital input pins is identical to the input stage of the standard digital input/output pins.

The Pull-up on the PORST pin is identical to the Pull-up on the standard digital input/output pins.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 19 Standard Pad Parameters

| Parameter                                                | Symbol              | Va                               | alues | Unit | Note / Test Condition                                    |

|----------------------------------------------------------|---------------------|----------------------------------|-------|------|----------------------------------------------------------|

|                                                          |                     | Min.                             | Max.  |      |                                                          |

| Pin capacitance (digital inputs/outputs)                 | $C_{IO}CC$          | _                                | 10    | pF   |                                                          |

| Pull-down current                                        | $ I_{PDL} $         | 150                              | _     | μΑ   | $^{1)}V_{\mathrm{IN}} \geq 0.6 	imes V_{\mathrm{DDP}}$   |

|                                                          | SR                  | _                                | 10    | μΑ   | $^{2)}V_{\mathrm{IN}} \leq 0.36 \times V_{\mathrm{DDP}}$ |

| Pull-Up current                                          | $ I_{\rm PUH} $ SR  | _                                | 10    | μΑ   | $^{2)}V_{IN} \geq 0.6 	imes V_{DDP}$                     |

|                                                          |                     | 100                              | _     | μΑ   | $^{1)}V_{\mathrm{IN}} \leq 0.36 \times V_{\mathrm{DDP}}$ |

| Input Hysteresis for pads of all A classes <sup>3)</sup> | HYSA<br>CC          | 0.1 ×<br><i>V</i> <sub>DDP</sub> | -     | V    |                                                          |

| PORST spike filter always blocked pulse duration         | t <sub>SF1</sub> CC | _                                | 10    | ns   |                                                          |

| PORST spike filter pass-through pulse duration           | $t_{SF2}CC$         | 100                              | _     | ns   |                                                          |

| PORST pull-down current                                  | $ I_{PPD} $ CC      | 13                               | _     | mA   | V <sub>IN</sub> = 1.0 V                                  |

Current required to override the pull device with the opposite logic level ("force current").

With active pull device, at load currents between force and keep current the input state is undefined.

Load current at which the pull device still maintains the valid logic level ("keep current").

With active pull device, at load currents between force and keep current the input state is undefined.

<sup>3)</sup> Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

Table 24 VADC Parameters (Operating Conditions apply)

| Parameter                                                              | Symbol                  | Values |      |       | Unit | Note /                                                                                     |  |

|------------------------------------------------------------------------|-------------------------|--------|------|-------|------|--------------------------------------------------------------------------------------------|--|

|                                                                        |                         | Min.   | Тур. | Max.  |      | Test Condition                                                                             |  |

| Total Unadjusted Error                                                 | TUE CC                  | -4     | -    | 4     | LSB  | 12-bit resolution;                                                                         |  |

| Differential Non-Linearity<br>Error <sup>8)</sup>                      | EA <sub>DNL</sub><br>CC | -3     | _    | 3     | LSB  | $V_{\text{DDA}} = 3.3 \text{ V};$ $V_{\text{AREF}} = V_{\text{DDA}}^{7)}$                  |  |

| Gain Error <sup>8)</sup>                                               | EA <sub>GAIN</sub> CC   | -4     | _    | 4     | LSB  |                                                                                            |  |

| Integral Non-Linearity <sup>8)</sup>                                   | $EA_{INL}CC$            | -3     | -    | 3     | LSB  |                                                                                            |  |

| Offset Error <sup>8)</sup>                                             | EA <sub>OFF</sub><br>CC | -4     | _    | 4     | LSB  |                                                                                            |  |

| Worst case ADC $V_{\rm DDA}$ power supply current per active converter | I <sub>DDAA</sub> CC    | -      | 1.5  | 2     | mA   | during conversion $V_{\rm DDP} = 3.6 \ \rm V,$ $T_{\rm J} = 150 \ ^{\rm o} \rm C$          |  |

| Charge consumption on $V_{AREF}$ per conversion <sup>5)</sup>          | $Q_{\mathrm{CONV}}$     | _      | 30   | _     | pC   | $\begin{array}{l} \text{O V} \leq V_{\text{AREF}} \\ \leq V_{\text{DDA}}^{9)} \end{array}$ |  |

| ON resistance of the analog input path                                 | R <sub>AIN</sub> CC     | _      | 600  | 1 200 | Ohm  |                                                                                            |  |

| ON resistance for the ADC test (pull down for AIN7)                    | R <sub>AIN7T</sub> CC   | 180    | 550  | 900   | Ohm  |                                                                                            |  |

| Resistance of the reference voltage input path                         | R <sub>AREF</sub><br>CC | _      | 700  | 1 700 | Ohm  |                                                                                            |  |

- 1) A running conversion may become imprecise in case the normal conditions are violated (voltage overshoot).

- If the analog reference voltage is below V<sub>DDA</sub>, then the ADC converter errors increase. If the reference voltage

is reduced by the factor k (k<1), TUE, DNL, INL, Gain, and Offset errors increase also by the factor 1/k.</li>

- 3) The leakage current definition is a continuous function, as shown in figure ADCx Analog Inputs Leakage. The numerical values defined determine the characteristic points of the given continuous linear approximation they do not define step function (see Figure 12).

- 4) The sampling capacity of the conversion C-network is pre-charged to V<sub>AREF</sub>/2 before the sampling moment. Because of the parasitic elements, the voltage measured at AINx can deviate from V<sub>AREF</sub>/2.

- 5) Applies to AINx, when used as alternate reference input.

- 6) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead, smaller capacitances are successively switched to the reference voltage.

- For 10-bit conversions, the errors are reduced to 1/4; for 8-bit conversions, the errors are reduced to 1/16.

Never less than ±1 LSB.

- 8) The sum of DNL/INL/GAIN/OFF errors does not exceed the related total unadjusted error TUE.

- 9) The resulting current for a conversion can be calculated with  $I_{AREF} = Q_{CONV} / t_c$ . The fastest 12-bit post-calibrated conversion of  $t_c = 459 \, \text{ns}$  results in a typical average current of  $I_{AREF} = 65.4 \, \mu\text{A}$ .

## 3.2.4 Out-of-Range Comparator (ORC)

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{\text{AIN}}$ ) above the analog reference<sup>1)</sup> ( $V_{\text{AREF}}$ ) on selected input pins (GxORCy) and generates a service request trigger (GxORCOUTy).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

The parameters in Table 27 apply for the maximum reference voltage  $V_{\rm AREF} = V_{\rm DDA} + 50$  mV.

Table 27

ORC Parameters (Operating Conditions apply)

| Parameter                 | Symbol        |    |      | Values | 3                | Unit | Note / Test Condition             |

|---------------------------|---------------|----|------|--------|------------------|------|-----------------------------------|

|                           |               |    | Min. | Тур.   | Max.             |      |                                   |

| DC Switching Level        | $V_{ODC}$     | CC | 100  | 125    | 210              | mV   | $V_{AIN} \geq V_{AREF} + V_{ODC}$ |

| Hysteresis                | $V_{OHYS}$    | CC | 50   | -      | $V_{\text{ODC}}$ | mV   |                                   |

| Detection Delay of a      | $t_{\sf ODD}$ | CC | 50   | _      | 450              | ns   | $V_{AIN} \geq V_{AREF}$ + 210 mV  |

| persistent<br>Overvoltage |               |    | 45   | -      | 105              | ns   | $V_{AIN} \geq V_{AREF}$ + 400 mV  |

| Always detected           | $t_{OPDD}$    | CC | 440  | -      | _                | ns   | $V_{AIN} \geq V_{AREF}$ + 210 mV  |

| Overvoltage Pulse         |               |    | 90   | -      | _                | ns   | $V_{AIN} \geq V_{AREF}$ + 400 mV  |

| Never detected            | $t_{OPDN}$    | CC | _    | -      | 45               | ns   | $V_{AIN} \geq V_{AREF}$ + 210 mV  |

| Overvoltage Pulse         |               |    | _    | _      | 30               | ns   | $V_{AIN} \geq V_{AREF}$ + 400 mV  |

| Release Delay             | $t_{ORD}$     | CC | 65   | -      | 105              | ns   | $V_{AIN} \leq V_{AREF}$           |

| Enable Delay              | $t_{\sf OED}$ | CC | _    | 100    | 200              | ns   |                                   |

Subject to Agreement on the Use of Product Information

<sup>1)</sup> Always the standard VADC reference, alternate references do not apply to the ORC.

# 3.2.9 Flash Memory Parameters

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 35 Flash Memory Parameters

| Parameter                                                                 | Symbol                 |       | Values | 5    | Unit   | Note /<br>Test Condition                                                                        |

|---------------------------------------------------------------------------|------------------------|-------|--------|------|--------|-------------------------------------------------------------------------------------------------|

|                                                                           |                        | Min.  | Тур.   | Max. |        |                                                                                                 |

| Erase Time per 256<br>Kbyte Sector                                        | $t_{ERP}CC$            | -     | 5      | 5.5  | S      |                                                                                                 |

| Erase Time per 64 Kbyte<br>Sector                                         | t <sub>ERP</sub> CC    | _     | 1.2    | 1.4  | S      |                                                                                                 |

| Erase Time per 16 Kbyte<br>Logical Sector                                 | t <sub>ERP</sub> CC    | _     | 0.3    | 0.4  | S      |                                                                                                 |

| Program time per page <sup>1)</sup>                                       | $t_{PRP}CC$            | _     | 5.5    | 11   | ms     |                                                                                                 |

| Erase suspend delay                                                       | t <sub>FL_ErSusp</sub> | _     | _      | 15   | ms     |                                                                                                 |

| Wait time after margin change                                             | t <sub>FL_Margin</sub> | 10    | _      | _    | μs     |                                                                                                 |

| Wake-up time                                                              | t <sub>WU</sub> CC     | _     | -      | 270  | μS     |                                                                                                 |

| Read access time                                                          | t <sub>a</sub> CC      | 22    | _      | _    | ns     | For operation with 1 / $f_{\rm CPU}$ < $t_{\rm a}$ wait states must be configured <sup>2)</sup> |

| Data Retention Time,<br>Physical Sector <sup>3)4)</sup>                   | t <sub>RET</sub> CC    | 20    | -      | -    | years  | Max. 1000<br>erase/program<br>cycles                                                            |

| Data Retention Time,<br>Logical Sector <sup>3)4)</sup>                    | t <sub>RETL</sub> CC   | 20    | -      | -    | years  | Max. 100<br>erase/program<br>cycles                                                             |

| Data Retention Time,<br>User Configuration Block<br>(UCB) <sup>3)4)</sup> | $t_{RTU}CC$            | 20    | _      | _    | years  | Max. 4<br>erase/program<br>cycles per UCB                                                       |

| Endurance on 64 Kbyte<br>Physical Sector PS4                              | N <sub>EPS4</sub> CC   | 10000 | -      | -    | cycles | Cycling<br>distributed over<br>life time <sup>5)</sup>                                          |

- In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes an additional time of 5.5 ms.

- 2) The following formula applies to the wait state configuration: FCON.WSPFLASH  $\times$  (1 /  $f_{CPU}$ )  $\geq t_a$ .

- 3) Storage and inactive time included.

- 4) Values given are valid for an average weighted junction temperature of  $T_J = 110$  °C.

- Only valid with robust EEPROM emulation algorithm, equally cycling the logical sectors. For more details see the Reference Manual.

# 3.3.2 Power-Up and Supply Monitoring

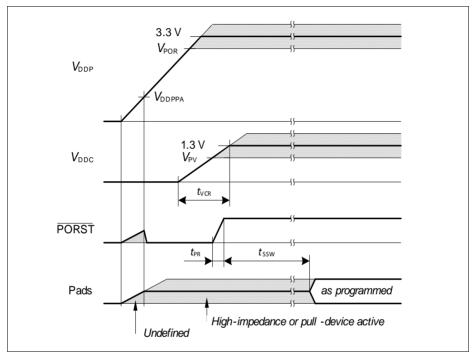

$\overline{ extsf{PORST}}$  is always asserted when  $V_{ extsf{DDP}}$  and/or  $V_{ extsf{DDC}}$  violate the respective thresholds.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

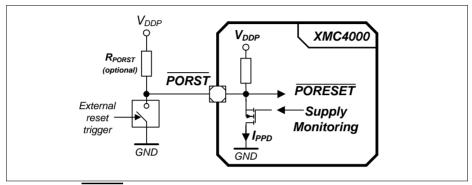

Figure 21 PORST Circuit

Table 36 Supply Monitoring Parameters

| Parameter                                                       | Symbol              | Values             |      |                    | Unit | Note /                                                                                    |

|-----------------------------------------------------------------|---------------------|--------------------|------|--------------------|------|-------------------------------------------------------------------------------------------|

|                                                                 |                     | Min.               | Тур. | Max.               |      | <b>Test Condition</b>                                                                     |

| Digital supply voltage reset threshold                          | $V_{POR}CC$         | 2.79 <sup>1)</sup> | -    | 3.05 <sup>2)</sup> | V    | 3)                                                                                        |

| Core supply voltage reset threshold                             | $V_{PV}$ CC         | -                  | _    | 1.17               | V    |                                                                                           |

| $V_{\mathrm{DDP}}$ voltage to ensure defined pad states         | $V_{DDPPA}$ CC      | -                  | 1.0  | -                  | V    |                                                                                           |

| PORST rise time                                                 | $t_{PR}$ SR         | -                  | _    | 2                  | μS   | 4)                                                                                        |

| Startup time from power-on reset with code execution from Flash | t <sub>SSW</sub> CC | -                  | 2.5  | 3.5                | ms   | Time to the first user code instruction                                                   |

| $\overline{V_{ m DDC}}$ ramp up time                            | t <sub>VCR</sub> CC | _                  | 550  | -                  | μѕ   | Ramp up after power-on or after a reset triggered by a violation of $V_{POR}$ or $V_{PV}$ |

<sup>1)</sup> Minimum threshold for reset assertion.

- 2) Maximum threshold for reset deassertion.

- 3) The  $V_{\rm DDP}$  monitoring has a typical hysteresis of  $V_{\rm PORHYS}$  = 180 mV.

- If t<sub>PR</sub> is not met, low spikes on PORST may be seen during start up (e.g. reset pulses generated by the supply monitoring due to a slow ramping V<sub>DDP</sub>).

Figure 22 Power-Up Behavior

# 3.3.3 Power Sequencing

While starting up and shutting down as well as when switching power modes of the system it is important to limit the current load steps. A typical cause for such load steps is changing the CPU frequency  $f_{\rm CPU}$ . Load steps exceeding the below defined values may cause a power on reset triggered by the supply monitor.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 46 USIC IIC Fast Mode Timing<sup>1)</sup>

| Parameter                                        | Symbol                   | Values                     |      |      | Unit | Note /         |

|--------------------------------------------------|--------------------------|----------------------------|------|------|------|----------------|

|                                                  |                          | Min.                       | Тур. | Max. |      | Test Condition |

| Fall time of both SDA and SCL                    | t <sub>1</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -    | 300  | ns   |                |

| Rise time of both SDA and SCL                    | t <sub>2</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -    | 300  | ns   |                |

| Data hold time                                   | t <sub>3</sub><br>CC/SR  | 0                          | -    | -    | μs   |                |

| Data set-up time                                 | t <sub>4</sub><br>CC/SR  | 100                        | -    | -    | ns   |                |

| LOW period of SCL clock                          | t <sub>5</sub><br>CC/SR  | 1.3                        | -    | -    | μs   |                |

| HIGH period of SCL clock                         | t <sub>6</sub><br>CC/SR  | 0.6                        | -    | -    | μs   |                |

| Hold time for (repeated)<br>START condition      | t <sub>7</sub><br>CC/SR  | 0.6                        | -    | -    | μs   |                |

| Set-up time for repeated START condition         | t <sub>8</sub><br>CC/SR  | 0.6                        | -    | -    | μs   |                |

| Set-up time for STOP condition                   | t <sub>9</sub><br>CC/SR  | 0.6                        | -    | -    | μs   |                |

| Bus free time between a STOP and START condition | t <sub>10</sub><br>CC/SR | 1.3                        | -    | -    | μs   |                |

| Capacitive load for each bus line                | C <sub>b</sub> SR        | -                          | -    | 400  | pF   |                |

<sup>1)</sup> Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

<sup>2)</sup> C<sub>b</sub> refers to the total capacitance of one bus line in pF.

Table 50 SD Card Bus Timing for Full-Speed Mode<sup>1)</sup> (cont'd)

| Parameter                 | Symbol     | Value | s    | Unit | Note/ Test<br>Condition |

|---------------------------|------------|-------|------|------|-------------------------|

|                           |            | Min.  | Max. |      |                         |

| SD card output valid time | $t_{ODLY}$ | _     | 14   | ns   |                         |

| SD card output hold time  | $t_{OH}$   | 0     | _    | ns   |                         |

<sup>1)</sup> Reference card timing values for calculation examples. Not subject to production test and not characterized.

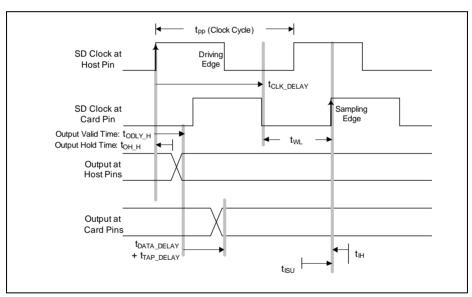

## **Full-Speed Output Path (Write)**

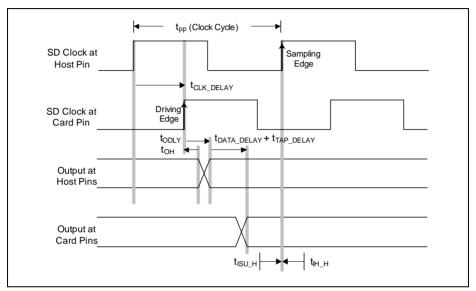

Figure 30 Full-Speed Output Path

## Full-Speed Write Meeting Setup (Maximum Delay)

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

No clock delay:

(1)

$t_{ODLY F} + t_{DATA DELAY} + t_{TAP DELAY} + t_{ISU} < t_{WL}$

Table 52 SD Card Bus Timing for High-Speed Mode<sup>1)</sup>

| Parameter                 | Symbol          | Values |      | Unit | Note/ Test |

|---------------------------|-----------------|--------|------|------|------------|

|                           |                 | Min.   | Max. |      | Condition  |

| SD card input setup time  | $t_{ISU}$       | 6      | _    | ns   |            |

| SD card input hold time   | $t_{IH}$        | 2      | _    | ns   |            |

| SD card output valid time | $t_{ODLY}$      | _      | 14   | ns   |            |

| SD card output hold time  | t <sub>OH</sub> | 2.5    | _    | ns   |            |

<sup>1)</sup> Reference card timing values for calculation examples. Not subject to production test and not characterized.

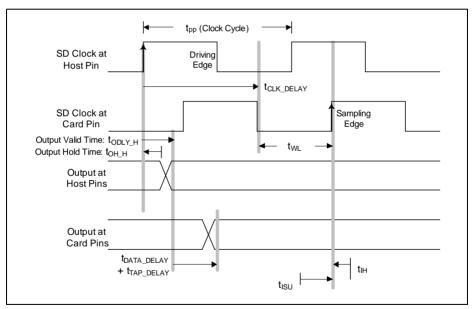

## **High-Speed Output Path (Write)**

Figure 32 High-Speed Output Path

## **High-Speed Write Meeting Setup (Maximum Delay)**

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

No clock delay:

$$t_{ODLY\_H} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL}$$

With clock delay:

$$t_{ODLY\_H} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL} + t_{CLK\_DELAY}$$

$$t_{\mathrm{DATA\_DELAY}} + t_{\mathrm{TAP\_DELAY}} - t_{\mathrm{CLK\_DELAY}} < t_{\mathrm{WL}} - t_{\mathrm{ISU}} - t_{\mathrm{ODLY\_H}}$$

$$t_{\mathrm{DATA\ DELAY}} - t_{\mathrm{CLK\ DELAY}} < t_{\mathrm{WL}} - t_{\mathrm{ISU}} - t_{\mathrm{ODLY\ H}} - t_{\mathrm{TAP\ DELAY}}$$

$$t_{DATA\_DELAY} - t_{CLK\_DELAY} < 10 - 6 - 14 - t_{TAP\_DELAY}$$

$$t_{DATA\ DELAY} - t_{CLK\ DELAY} < -10 - t_{TAP\ DELAY}$$

The data delay is less than the clock delay by at least 10 ns in the ideal case where  $t_{WL}$ = 10 ns.

## **High-Speed Write Meeting Hold (Minimum Delay)**

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(10)

$$\begin{split} t_{CLK\_DELAY} < t_{WL} + t_{OH\_H} + t_{DATA\_DELAY} + t_{TAP\_DELAY} - t_{IH} \\ \\ t_{CLK\_DELAY} - t_{DATA\_DELAY} < t_{WL} + t_{OH\_H} + t_{TAP\_DELAY} - t_{IH} \\ \\ t_{CLK\_DELAY} - t_{DATA\_DELAY} < 10 + 2 + t_{TAP\_DELAY} - 2 \end{split}$$

The clock can be delayed versus data up to 13.2 ns (external delay line) in ideal case of  $t_{\rm WL}$ = 10 ns, with maximum  $t_{\rm TAP\ DELAY}$  = 3.2 ns programmed.

$t_{CLK}$  DELAY -  $t_{DATA}$  DELAY < 10 +  $t_{TAP}$  DELAY

## **High-Speed Input Path (Read)**

Figure 33 High-Speed Input Path

## **High-Speed Read Meeting Setup (Maximum Delay)**

The following equations show how to calculate the allowed combined propagation delay range of the SD\_CLK and SD\_DAT/CMD signals on the PCB.

$$t_{\text{CLK\_DELAY}} + t_{\text{DATA\_DELAY}} + t_{\text{TAP\_DELAY}} + t_{\text{ODLY}} + t_{\text{ISU\_H}} < t_{pp}$$

$$t_{\text{CLK\_DELAY}} + t_{\text{DATA\_DELAY}} < t_{pp} - t_{\text{ODLY}} - t_{\text{ISU\_H}} - t_{\text{TAP\_DELAY}}$$

$$t_{\text{CLK\_DELAY}} + t_{\text{DATA\_DELAY}} < 20 - 14 - 2 - t_{\text{TAP\_DELAY}}$$

$$t_{\text{CLK\_DELAY}} + t_{\text{DATA\_DELAY}} < 4 - t_{\text{TAP\_DELAY}}$$

The data + clock delay can be up to 4 ns for a 20 ns clock cycle.

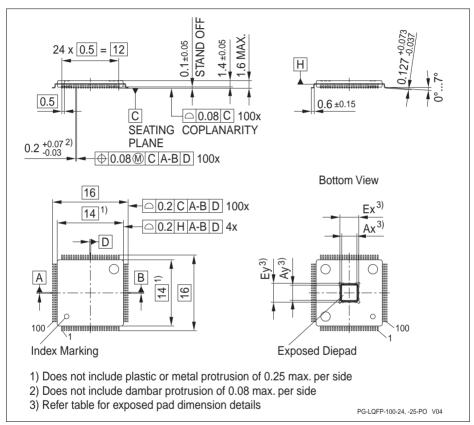

## Package and Reliability

# 4 Package and Reliability

The XMC4300 is a member of the XMC4000 Family of microcontrollers. It is also compatible to a certain extent with members of similar families or subfamilies.

Each package is optimized for the device it houses. Therefore, there may be slight differences between packages of the same pin-count but for different device types. In particular, the size of the Exposed Die Pad may vary.

If different device types are considered or planned for an application, it must be ensured that the board layout fits all packages under consideration.

## 4.1 Package Parameters

**Table 60** provides the thermal characteristics of the packages used in XMC4300.

Table 60 Thermal Characteristics of the Packages

| <u> </u>                                                                |                   |                     |           |     |                              |  |  |  |

|-------------------------------------------------------------------------|-------------------|---------------------|-----------|-----|------------------------------|--|--|--|

| Parameter                                                               | Symbol            | Symbol Limit Values |           |     | Package Types                |  |  |  |

|                                                                         |                   | Min.                | Max.      |     |                              |  |  |  |

| Exposed Die Pad<br>dimensions including U-<br>Groove                    | Ex × Ey<br>CC     | -                   | 7.0 × 7.0 | mm  | PG-LQFP-100-25               |  |  |  |

| Exposed Die Pad<br>dimensions excluding U-<br>Groove                    | Ax × Ay<br>CC     | -                   | 6.2 × 6.2 | mm  | PG-LQFP-100-25               |  |  |  |

| Thermal resistance Junction-Ambient $T_{\rm J} \le 150~{\rm ^{\circ}C}$ | $R_{ m \odot JA}$ | -                   | 22.5      | K/W | PG-LQFP-100-25 <sup>1)</sup> |  |  |  |

<sup>1)</sup> Device mounted on a 4-layer JEDEC board (JESD 51-7) with thermal vias; exposed pad soldered.

Note: For electrical reasons, it is required to connect the exposed pad to the board ground  $V_{SS}$ , independent of EMC and thermal requirements.

## 4.1.1 Thermal Considerations

When operating the XMC4300 in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

## Package and Reliability

# 4.2 Package Outlines

The exposed die pad dimensions are listed in Table 60.

Figure 43 PG-LQFP-100-25 (Plastic Green Low Profile Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages