Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                             |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, MMC/SD, SPI, UART/USART, USB OTG, USIC |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, Touch-Sense, WDT                                  |

| Number of I/O              | 75                                                                                 |

| Program Memory Size        | 256KB (256K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 128K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                      |

| Data Converters            | A/D 14x12b; D/A 2x12b                                                              |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-LQFP Exposed Pad                                                               |

| Supplier Device Package    | PG-LQFP-100-25                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4300f100k256aaxuma1  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### About this Document

# About this Document

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC4300 series devices.

The document describes the characteristics of a superset of the XMC4300 series devices. For simplicity, the various device types are referred to by the collective term XMC4300 throughout this manual.

## XMC4000 Family User Documentation

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

# Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by Users Guides and Application Notes.

Please refer to http://www.infineon.com/xmc4000 to get access to the latest versions of those documents.

#### **General Device Information**

| Table 9Package Pin Mapping (cont'd) |          |          |                                                                             |  |  |  |  |

|-------------------------------------|----------|----------|-----------------------------------------------------------------------------|--|--|--|--|

| Function                            | LQFP-100 | Pad Type | Notes                                                                       |  |  |  |  |

| P1.0                                | 79       | A1+      |                                                                             |  |  |  |  |

| P1.1                                | 78       | A1+      |                                                                             |  |  |  |  |

| P1.2                                | 77       | A2       |                                                                             |  |  |  |  |

| P1.3                                | 76       | A2       |                                                                             |  |  |  |  |

| P1.4                                | 75       | A1+      |                                                                             |  |  |  |  |

| P1.5                                | 74       | A1+      |                                                                             |  |  |  |  |

| P1.6                                | 83       | A2       |                                                                             |  |  |  |  |

| P1.7                                | 82       | A2       |                                                                             |  |  |  |  |

| P1.8                                | 81       | A2       |                                                                             |  |  |  |  |

| P1.9                                | 80       | A2       |                                                                             |  |  |  |  |

| P1.10                               | 73       | A1+      |                                                                             |  |  |  |  |

| P1.11                               | 72       | A1+      |                                                                             |  |  |  |  |

| P1.12                               | 71       | A2       |                                                                             |  |  |  |  |

| P1.13                               | 70       | A2       |                                                                             |  |  |  |  |

| P1.14                               | 69       | A2       |                                                                             |  |  |  |  |

| P1.15                               | 68       | A2       |                                                                             |  |  |  |  |

| P2.0                                | 52       | A2       |                                                                             |  |  |  |  |

| P2.1                                | 51       | A2       | After a system reset, via HWSEL<br>this pin selects the DB.TDO<br>function. |  |  |  |  |

| P2.2                                | 50       | A2       |                                                                             |  |  |  |  |

| P2.3                                | 49       | A2       |                                                                             |  |  |  |  |

| P2.4                                | 48       | A2       |                                                                             |  |  |  |  |

| P2.5                                | 47       | A2       |                                                                             |  |  |  |  |

| P2.6                                | 54       | A1+      |                                                                             |  |  |  |  |

| P2.7                                | 53       | A1+      |                                                                             |  |  |  |  |

| P2.8                                | 46       | A2       |                                                                             |  |  |  |  |

| P2.9                                | 45       | A2       |                                                                             |  |  |  |  |

| P2.10                               | 44       | A2       |                                                                             |  |  |  |  |

| P2.14                               | 41       | A2       |                                                                             |  |  |  |  |

| P2.15                               | 40       | A2       |                                                                             |  |  |  |  |

| P3.0                                | 7        | A2       |                                                                             |  |  |  |  |

| P3.1                                | 6        | A2       |                                                                             |  |  |  |  |

# 2.3 Power Connection Scheme

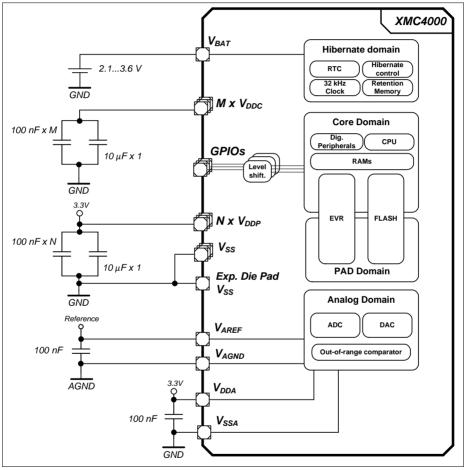

Figure 5. shows a reference power connection scheme for the XMC4300.

Figure 5 Power Connection Scheme

Every power supply pin needs to be connected. Different pins of the same supply need also to be externally connected. As example, all  $V_{\rm DDP}$  pins must be connected externally to one  $V_{\rm DDP}$  net. In this reference scheme one 100 nF capacitor is connected at each supply pin against  $V_{\rm SS}$ . An additional 10 µF capacitor is connected to the  $V_{\rm DDP}$  nets and an additional 10 µF capacitor to the  $V_{\rm DDP}$  nets.

The XMC4300 has a common ground concept, all  $V_{\rm SS}$ ,  $V_{\rm SSA}$  and  $V_{\rm SSO}$  pins share the same ground potential. In packages with an exposed die pad it must be connected to the common ground as well.

$V_{\rm AGND}$  is the low potential to the analog reference  $V_{\rm AREF}$ . Depending on the application it can share the common ground or have a different potential. In devices with shared  $V_{\rm DDA}/V_{\rm AREF}$  and  $V_{\rm SSA}/V_{\rm AGND}$  pins the reference is tied to the supply. Some analog channels can optionally serve as "Alternate Reference"; further details on this operating mode are described in the Reference Manual.

When  $V_{\text{DDP}}$  is supplied,  $V_{\text{BAT}}$  must be supplied as well. If no other supply source (e.g. battery) is connected to  $V_{\text{BAT}}$ , the  $V_{\text{BAT}}$  pin can also be connected directly to  $V_{\text{DDP}}$ .

# 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                                                                              | Symbol                                                     |    | Values |      |                                       | Unit | Note /                |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----|--------|------|---------------------------------------|------|-----------------------|

|                                                                                                                        |                                                            |    | Min.   | Тур. | Max.                                  |      | Test Con<br>dition    |

| Storage temperature                                                                                                    | $T_{\rm ST}$                                               | SR | -65    | -    | 150                                   | °C   | _                     |

| Junction temperature                                                                                                   | TJ                                                         | SR | -40    | -    | 150                                   | °C   | -                     |

| Voltage at 3.3 V power supply pins with respect to $V_{\rm SS}$                                                        | $V_{DDP}$                                                  | SR | -      | -    | 4.3                                   | V    | -                     |

| Voltage on any Class A and dedicated input pin with respect to $V_{\rm SS}$                                            | $V_{\rm IN}$                                               | SR | -1.0   | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Voltage on any analog input pin with respect to $V_{\rm AGND}$                                                         | $\begin{array}{c} V_{\rm AIN} \\ V_{\rm AREF} \end{array}$ | SR | -1.0   | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Input current on any pin during overload condition                                                                     | I <sub>IN</sub>                                            | SR | -10    | -    | +10                                   | mA   |                       |

| Absolute maximum sum of all<br>input circuit currents for one<br>port group during overload<br>condition <sup>1)</sup> | $\Sigma I_{\rm IN}$                                        | SR | -25    | -    | +25                                   | mA   |                       |

| Absolute maximum sum of all<br>input circuit currents during<br>overload condition                                     | $\Sigma I_{\rm IN}$                                        | SR | -100   | -    | +100                                  | mA   |                       |

#### Table 12 Absolute Maximum Rating Parameters

1) The port groups are defined in **Table 16**.

**Figure 6** explains the input voltage ranges of  $V_{\rm IN}$  and  $V_{\rm AIN}$  and its dependency to the supply level of  $V_{\rm DDP}$ . The input voltage must not exceed 4.3 V, and it must not be more than 1.0 V above  $V_{\rm DDP}$ . For the range up to  $V_{\rm DDP}$  + 1.0 V also see the definition of the overload conditions in Section 3.1.3.

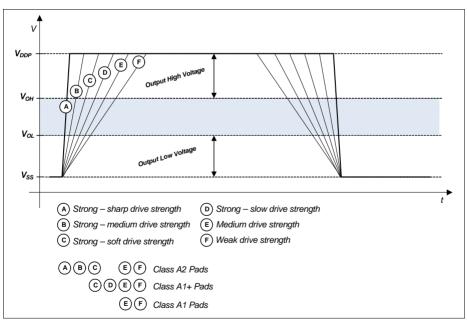

# 3.1.4 Pad Driver and Pad Classes Summary

This section gives an overview on the different pad driver classes and their basic characteristics.

| Table 17 Pad Driver and Pad Classe | s Overview |

|------------------------------------|------------|

|------------------------------------|------------|

| Class | Power<br>Supply | Туре         | Sub-Class                 | Speed<br>Grade | Load   | Termination                    |

|-------|-----------------|--------------|---------------------------|----------------|--------|--------------------------------|

| A     | 3.3 V           | LVTTL<br>I/O | <b>A1</b><br>(e.g. GPIO)  | 6 MHz          | 100 pF | No                             |

|       |                 |              | A1+<br>(e.g. serial I/Os) | 25 MHz         | 50 pF  | Series termination recommended |

|       |                 |              | A2<br>(e.g. ext. Bus)     | 80 MHz         | 15 pF  | Series termination recommended |

Figure 8 Output Slopes with different Pad Driver Modes

**Figure 8** is a qualitative display of the resulting output slope performance with different output driver modes. The detailed input and output characteristics are listed in **Section 3.2.1**.

32

# 3.1.5 Operating Conditions

The following operating conditions must not be exceeded in order to ensure correct operation and reliability of the XMC4300. All parameters specified in the following sections refer to these operating conditions, unless noted otherwise.

| Parameter                                                                | Symbol                     |                    | Values | 6                  | Unit | Note /                                                                                     |  |

|--------------------------------------------------------------------------|----------------------------|--------------------|--------|--------------------|------|--------------------------------------------------------------------------------------------|--|

|                                                                          |                            | Min. Typ. I        |        | Max.               |      | Test Condition                                                                             |  |

| Ambient Temperature                                                      | $T_{\rm A}$ SR             | -40                | -      | 85                 | °C   | Temp. Range F                                                                              |  |

|                                                                          |                            | -40                | -      | 125                | °C   | Temp. Range K                                                                              |  |

| Digital supply voltage                                                   | $V_{\rm DDP}{\rm SR}$      | 3.13 <sup>1)</sup> | 3.3    | 3.63 <sup>2)</sup> | V    |                                                                                            |  |

| Core Supply Voltage                                                      | V <sub>DDC</sub><br>CC     | _1)                | 1.3    | _                  | V    | Generated internally                                                                       |  |

| Digital ground voltage                                                   | $V_{\rm SS}~{\rm SR}$      | 0                  | -      | _                  | V    |                                                                                            |  |

| ADC analog supply voltage                                                | $V_{\rm DDA}{ m SR}$       | 3.0                | 3.3    | 3.6 <sup>2)</sup>  | V    |                                                                                            |  |

| Analog ground voltage for $V_{\rm DDA}$                                  | $V_{\rm SSA}{ m SR}$       | -0.1               | 0      | 0.1                | V    |                                                                                            |  |

| Battery Supply Voltage for<br>Hibernate Domain                           | $V_{BAT}SR$                | 1.95 <sup>3)</sup> | _      | 3.63               | V    | When $V_{\text{DDP}}$ is<br>supplied $V_{\text{BAT}}$<br>has to be<br>supplied as<br>well. |  |

| System Frequency                                                         | $f_{\rm SYS}~{\rm SR}$     | -                  | -      | 144                | MHz  |                                                                                            |  |

| Short circuit current of digital outputs                                 | I <sub>SC</sub> SR         | -5                 | -      | 5                  | mA   |                                                                                            |  |

| Absolute sum of short<br>circuit currents per pin<br>group <sup>4)</sup> | $\Sigma I_{SC_{PG}}$<br>SR | -                  | -      | 20                 | mA   |                                                                                            |  |

| Absolute sum of short<br>circuit currents of the<br>device               | $\Sigma I_{SC_D}$<br>SR    | _                  | -      | 100                | mA   |                                                                                            |  |

| Table 18 | Operating | Conditions | Parameters    |

|----------|-----------|------------|---------------|

|          | oporating | oonantiono | i ulullotoi o |

1) See also the Supply Monitoring thresholds, **Section 3.3.2**.

Voltage overshoot to 4.0 V is permissible at Power-Up and PORST low, provided the pulse duration is less than 100 μs and the cumulated sum of the pulses does not exceed 1 h over lifetime.

3) To start the hibernate domain it is required that  $V_{\text{BAT}} \ge 2.1 \text{ V}$ , for a reliable start of the oscillation of RTC\_XTAL in crystal mode it is required that  $V_{\text{BAT}} \ge 3.0 \text{ V}$ .

4) The port groups are defined in **Table 16**.

## Table 20 Standard Pads Class\_A1

| Parameter             | Symbol                  | Va                     | lues                        | Unit | Note /                                                   |

|-----------------------|-------------------------|------------------------|-----------------------------|------|----------------------------------------------------------|

|                       |                         | Min.                   | Max.                        |      | Test Condition                                           |

| Input leakage current | I <sub>OZA1</sub> CC    | -500                   | 500                         | nA   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$     |

| Input high voltage    | $V_{\rm IHA1}~{\rm SR}$ | $0.6 	imes V_{ m DDP}$ | $V_{\text{DDP}}$ + 0.3      | V    | max. 3.6 V                                               |

| Input low voltage     | $V_{\rm ILA1}{\rm SR}$  | -0.3                   | $0.36 	imes V_{\text{DDF}}$ | V    |                                                          |

| Output high voltage,  | $V_{OHA1}$              | V <sub>DDP</sub> - 0.4 | -                           | V    | $I_{OH} \ge$ -400 $\mu$ A                                |

| $POD^{1)} = weak$     | CC                      | 2.4                    | -                           | V    | $I_{OH} \ge$ -500 $\mu$ A                                |

| Output high voltage,  |                         | V <sub>DDP</sub> - 0.4 | -                           | V    | $I_{\rm OH} \ge$ -1.4 mA                                 |

| $POD^{1} = medium$    |                         | 2.4                    | -                           | V    | $I_{OH} \ge -2 \text{ mA}$                               |

| Output low voltage    | V <sub>OLA1</sub><br>CC | -                      | 0.4                         | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak    |

|                       |                         | _                      | 0.4                         | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium |

| Fall time             | t <sub>FA1</sub> CC     | _                      | 150                         | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak     |

|                       |                         | -                      | 50                          | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium       |

| Rise time             | t <sub>RA1</sub> CC     | -                      | 150                         | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak     |

|                       |                         | -                      | 50                          | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium   |

1) POD = Pin Out Driver

## Table 21 Standard Pads Class\_A1+

| Parameter             | Symbol Value          |                          |  | ies                       | Unit | Note /                                               |  |

|-----------------------|-----------------------|--------------------------|--|---------------------------|------|------------------------------------------------------|--|

|                       |                       | Min.                     |  | Max.                      |      | Test Condition                                       |  |

| Input leakage current | I <sub>OZA1+</sub> CC | -1                       |  | 1                         | μΑ   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$ |  |

| Input high voltage    | $V_{\rm IHA1+}\rm SR$ | $0.6 \times V_{\rm DDP}$ |  | $V_{\text{DDP}}$ + 0.3    | V    | max. 3.6 V                                           |  |

| Input low voltage     | $V_{\rm ILA1+}\rm SR$ | -0.3                     |  | $0.36 \times V_{\rm DDP}$ | V    |                                                      |  |

| Parameter                                          | Symbol                   | Va                     | lues                   | Unit | Note /                                                                |

|----------------------------------------------------|--------------------------|------------------------|------------------------|------|-----------------------------------------------------------------------|

|                                                    |                          | Min.                   | Max.                   |      | Test Condition                                                        |

| Input leakage current                              | I <sub>OZHIB</sub><br>CC | -500                   | 500                    | nA   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{BAT}}$                  |

| Input high voltage                                 | $V_{\rm IHHIB}$ SR       | $0.6 	imes V_{BAT}$    | V <sub>BAT</sub> + 0.3 | V    | max. 3.6 V                                                            |

| Input low voltage                                  | $V_{\rm ILHIB}$ SR       | -0.3                   | $0.36 	imes V_{BAT}$   | V    |                                                                       |

| Input Hysteresis for                               | HYSHIB                   | $0.1 	imes V_{BAT}$    | -                      | V    | $V_{BAT} \ge$ 3.13 V                                                  |

| HIB_IO pins <sup>1)</sup>                          | CC                       | $0.06 	imes V_{BAT}$   | -                      | V    | V <sub>BAT</sub> < 3.13 V                                             |

| Output high voltage,<br>POD <sup>1)</sup> = medium | $V_{\rm OHHIB}$ CC       | V <sub>BAT</sub> - 0.4 | -                      | V    | I <sub>OH</sub> ≥ -1.4 mA                                             |

| Output low voltage                                 | V <sub>OLHIB</sub><br>CC | -                      | 0.4                    | V    | $I_{\rm OL} \le 2  {\rm mA}$                                          |

| Fall time                                          | t <sub>FHIB</sub> CC     | -                      | 50                     | ns   | $V_{\text{BAT}} \ge 3.13 \text{ V}$<br>$C_{\text{L}} = 50 \text{ pF}$ |

|                                                    |                          | -                      | 100                    | ns   | $V_{\rm BAT}$ < 3.13 V<br>$C_{\rm L}$ = 50 pF                         |

| Rise time                                          | t <sub>RHIB</sub> CC     | -                      | 50                     | ns   | $V_{\rm BAT} \ge 3.13 \ { m V}$<br>$C_{\rm L}$ = 50 pF                |

|                                                    |                          | -                      | 100                    | ns   | $V_{\rm BAT}$ < 3.13 V<br>$C_{\rm L}$ = 50 pF                         |

## Table 23 HIB\_IO Class\_A1 special Pads

1) Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

# 3.2.2 Analog to Digital Converters (VADC)

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                                                    | Symbol                     |                            | Values | 5                            | Unit | Note /                                                                                                        |

|------------------------------------------------------------------------------|----------------------------|----------------------------|--------|------------------------------|------|---------------------------------------------------------------------------------------------------------------|

|                                                                              |                            | Min.                       | Тур.   | Max.                         |      | Test Condition                                                                                                |

| Analog reference voltage <sup>5)</sup>                                       | $V_{AREF}$ SR              | V <sub>AGND</sub><br>+ 1   | -      | $V_{\rm DDA}^{} + 0.05^{1)}$ | V    |                                                                                                               |

| Analog reference ground <sup>5)</sup>                                        | $V_{AGND}$ SR              | V <sub>SSM</sub> -<br>0.05 | -      | V <sub>AREF</sub> -<br>1     | V    |                                                                                                               |

| Analog reference voltage<br>range <sup>2)5)</sup>                            | $V_{AREF}$ - $V_{AGND}$ SR | 1                          | -      | V <sub>DDA</sub> + 0.1       | V    |                                                                                                               |

| Analog input voltage                                                         | $V_{\rm AIN}~{ m SR}$      | $V_{AGND}$                 | -      | $V_{DDA}$                    | V    |                                                                                                               |

| Input leakage at analog inputs <sup>3)</sup>                                 | I <sub>OZ1</sub> CC        | -100                       | -      | 200                          | nA   | $\begin{array}{c} 0.03 \times V_{\rm DDA} < \\ V_{\rm AIN} < 0.97 \times V_{\rm DD} \end{array}$              |

|                                                                              |                            | -500                       | -      | 100                          | nA   | $\begin{array}{l} 0 \ V \leq V_{AIN} \leq 0.03 \\ \times \ V_{DDA} \end{array}$                               |

|                                                                              |                            | -100                       | -      | 500                          | nA   | $\begin{array}{l} \textbf{0.97} \times V_{\text{DDA}} \\ \leq V_{\text{AIN}} \leq V_{\text{DDA}} \end{array}$ |

| Input leakage current at VAREF                                               | I <sub>OZ2</sub> CC        | -1                         | _      | 1                            | μA   | $\begin{array}{l} 0 \ V \leq V_{AREF} \\ \leq V_{DDA} \end{array}$                                            |

| Input leakage current at VAGND                                               | I <sub>OZ3</sub> CC        | -1                         | _      | 1                            | μA   | $0 V \le V_{AGND} \\ \le V_{DDA}$                                                                             |

| Internal ADC clock                                                           | $f_{\sf ADCI}\sf CC$       | 2                          | -      | 36                           | MHz  | $V_{\rm DDA}$ = 3.3 V                                                                                         |

| Switched capacitance at the analog voltage inputs <sup>4)</sup>              | C <sub>AINSW</sub><br>CC   | -                          | 4      | 6.5                          | pF   |                                                                                                               |

| Total capacitance of an analog input                                         | C <sub>AINTOT</sub><br>CC  | -                          | 12     | 20                           | pF   |                                                                                                               |

| Switched capacitance at the positive reference voltage input <sup>5)6)</sup> | $C_{\text{AREFSW}}$ CC     | -                          | 15     | 30                           | pF   |                                                                                                               |

| Total capacitance of the voltage reference inputs <sup>5)</sup>              | $C_{\text{AREFTOT}}$ CC    | -                          | 20     | 40                           | pF   |                                                                                                               |

Table 24

VADC Parameters (Operating Conditions apply)

# 3.2.3 Digital to Analog Converters (DAC)

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                      | Symbo                    | Ы    |      | Values | 5    | Unit          | Note /                                                                            |

|--------------------------------|--------------------------|------|------|--------|------|---------------|-----------------------------------------------------------------------------------|

|                                |                          |      | Min. | Тур.   | Max. | -             | Test Condition                                                                    |

| RMS supply current             | I <sub>DD</sub>          | CC   | -    | 2.5    | 4    | mA            | per active DAC<br>channel,<br>without load<br>currents of DAC<br>outputs          |

| Resolution                     | RES                      | CC   | -    | 12     | -    | Bit           |                                                                                   |

| Update rate                    | f <sub>urate_</sub> /    | ACC  | -    |        | 2    | Msam<br>ple/s | data rate, where<br>DAC can follow<br>64 LSB code jumps<br>to ± 1LSB accuracy     |

| Update rate                    | f <sub>urate_</sub> i    | F CC | _    |        | 5    | Msam<br>ple/s | data rate, where<br>DAC can follow<br>64 LSB code jumps<br>to ± 4 LSB accuracy    |

| Settling time                  | t <sub>SETTLE</sub>      | CC   | -    | 1      | 2    | μs            | at full scale jump,<br>output voltage<br>reaches target<br>value ± 20 LSB         |

| Slew rate                      | SR                       | CC   | 2    | 5      | -    | V/µs          |                                                                                   |

| Minimum output<br>voltage      | V <sub>OUT_M</sub><br>CC | IN   | -    | 0.3    | -    | V             | code value<br>unsigned: 000 <sub>H</sub> ;<br>signed: 800 <sub>H</sub>            |

| Maximum output<br>voltage      | V <sub>OUT_M</sub><br>CC | AX   | -    | 2.5    | -    | V             | code value<br>unsigned: FFF <sub>H</sub> ;<br>signed: 7FF <sub>H</sub>            |

| Integral non-linearity         | INL                      | CC   | -5.5 | ±2.5   | 5.5  | LSB           | $\begin{array}{l} R_L \geq 5 \text{ kOhm,} \\ C_L \leq 50 \text{ pF} \end{array}$ |

| Differential non-<br>linearity | DNL                      | СС   | -2   | ±1     | 2    | LSB           | $\begin{array}{l} R_L \geq 5 \text{ kOhm,} \\ C_L \leq 50 \text{ pF} \end{array}$ |

45

| Table 26 D | DAC Parameters | (Operating | Conditions apply) |

|------------|----------------|------------|-------------------|

|------------|----------------|------------|-------------------|

| Parameter                         | Symbol                      | Symbol Value |      |      | 5    | Unit | Note /                                                  |  |

|-----------------------------------|-----------------------------|--------------|------|------|------|------|---------------------------------------------------------|--|

|                                   |                             |              | Min. | Тур. | Max. |      | Test Condition                                          |  |

| Offset error                      | ED <sub>OFF</sub> (         | СС           |      | ±20  |      | mV   |                                                         |  |

| Gain error                        | $ED_{G_{IN}}C$              | C            | -6.5 | -1.5 | 3    | %    |                                                         |  |

| Startup time                      | t <sub>STARTUP</sub> (      | CC           | _    | 15   | 30   | μs   | time from output<br>enabling till code<br>valid ±16 LSB |  |

| 3dB Bandwidth of<br>Output Buffer | $f_{C1}$ (                  | СС           | 2.5  | 5    | _    | MHz  | verified by design                                      |  |

| Output sourcing current           | I <sub>OUT_SOUF</sub><br>CC | RCE          | -    | -30  | -    | mA   |                                                         |  |

| Output sinking current            | I <sub>OUT_SINK</sub><br>CC |              | _    | 0.6  | _    | mA   |                                                         |  |

| Output resistance                 | R <sub>OUT</sub> C          | CC           | -    | 50   | -    | Ohm  |                                                         |  |

| Load resistance                   | R <sub>L</sub> S            | SR           | 5    | -    | -    | kOhm |                                                         |  |

| Load capacitance                  | C <sub>L</sub> S            | SR           | _    | -    | 50   | pF   |                                                         |  |

| Signal-to-Noise<br>Ratio          | SNR C                       | С            | _    | 70   | _    | dB   | examination<br>bandwidth < 25 kHz                       |  |

| Total Harmonic<br>Distortion      | THD C                       | CC           | _    | 70   | _    | dB   | examination<br>bandwidth < 25 kHz                       |  |

| Power Supply<br>Rejection Ratio   | PSRR C                      | C            | _    | 56   | _    | dB   | to $V_{\rm DDA}$ verified by design                     |  |

## Table 26 DAC Parameters (Operating Conditions apply) (cont'd)

## **Conversion Calculation**

$\begin{array}{l} \text{Unsigned:} \\ \text{DACxDATA} = 4095 \times (V_{\text{OUT}} \text{-} V_{\text{OUT\_MIN}}) \, / \, (V_{\text{OUT\_MAX}} \text{-} V_{\text{OUT\_MIN}}) \\ \text{Signed:} \\ \text{DACxDATA} = 4095 \times (V_{\text{OUT}} \text{-} V_{\text{OUT\_MIN}}) \, / \, (V_{\text{OUT\_MAX}} \text{-} V_{\text{OUT\_MIN}}) \text{-} 2048 \\ \end{array}$

# 3.3.8 Peripheral Timing

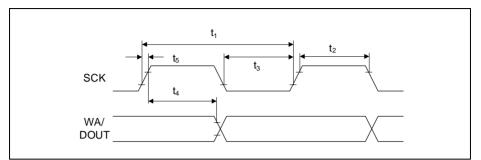

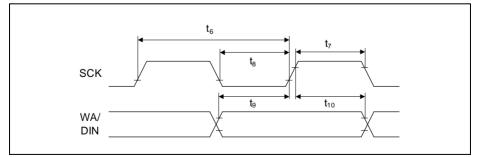

# 3.3.8.1 Synchronous Serial Interface (USIC SSC) Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                                               | Symbol              |                                            | Value | 5    | Unit | Note /         |

|-------------------------------------------------------------------------|---------------------|--------------------------------------------|-------|------|------|----------------|

|                                                                         |                     | Min. Typ.                                  |       | Max. |      | Test Condition |

| SCLKOUT master clock period                                             | t <sub>CLK</sub> CC | 33.3                                       | -     | -    | ns   |                |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC   | <i>t</i> <sub>PB</sub> - 6.5 <sup>1)</sup> | -     | -    | ns   |                |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC   | t <sub>PB</sub> -<br>8.5 <sup>1)</sup>     | -     | -    | ns   |                |

| Data output DOUT[3:0] valid time                                        | t <sub>3</sub> CC   | -6                                         | -     | 8    | ns   |                |

| Receive data input<br>DX0/DX[5:3] setup time to<br>SCLKOUT receive edge | t <sub>4</sub> SR   | 23                                         | -     | -    | ns   |                |

| Data input DX0/DX[5:3]<br>hold time from SCLKOUT<br>receive edge        | t <sub>5</sub> SR   | 1                                          | -     | -    | ns   |                |

## Table 43 USIC SSC Master Mode Timing

1)  $t_{PB} = 1 / f_{PB}$

# Table 44 USIC SSC Slave Mode Timing

| Parameter                                                                   | Symbol                    |      | Values | 5    | Unit | Note /         |  |

|-----------------------------------------------------------------------------|---------------------------|------|--------|------|------|----------------|--|

|                                                                             |                           | Min. | Тур.   | Max. |      | Test Condition |  |

| DX1 slave clock period                                                      | t <sub>CLK</sub> SR       | 66.6 | -      | -    | ns   |                |  |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup> | <i>t</i> <sub>10</sub> SR | 3    | -      | -    | ns   |                |  |

| Table 44 | USIC | SSC | Slave | Mode | Timing |

|----------|------|-----|-------|------|--------|

|          |      |     | 0.0.0 |      |        |

| Parameter                                                                                 |                        | nbol | Values |      |      | Unit | Note /         |

|-------------------------------------------------------------------------------------------|------------------------|------|--------|------|------|------|----------------|

|                                                                                           |                        |      | Min.   | Тур. | Max. |      | Test Condition |

| Select input DX2 hold after<br>last clock input DX1 receive<br>edge <sup>1)</sup>         | <i>t</i> <sub>11</sub> | SR   | 4      | -    | -    | ns   |                |

| Receive data input<br>DX0/DX[5:3] setup time to<br>shift clock receive edge <sup>1)</sup> | t <sub>12</sub>        | SR   | 6      | _    | -    | ns   |                |

| Data input DX0/DX[5:3] hold<br>time from clock input DX1<br>receive edge <sup>1)</sup>    | t <sub>13</sub>        | SR   | 4      | -    | -    | ns   |                |

| Data output DOUT[3:0] valid time                                                          | t <sub>14</sub>        | СС   | 0      | -    | 24   | ns   |                |

1) This input timing is valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

| Figure 28 | USIC IIS Master | Transmitter Timing | 1 |

|-----------|-----------------|--------------------|---|

|-----------|-----------------|--------------------|---|

| Parameter       | Symbol             |                             | Values | S    | Unit | Note /         |

|-----------------|--------------------|-----------------------------|--------|------|------|----------------|

|                 |                    | Min.                        | Тур.   | Max. |      | Test Condition |

| Clock period    | t <sub>6</sub> SR  | 66.6                        | -      | -    | ns   |                |

| Clock high time | t <sub>7</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -      | -    | ns   |                |

| Clock low time  | t <sub>8</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -      | _    | ns   |                |

| Set-up time     | t <sub>9</sub> SR  | 0.2 x<br>t <sub>6min</sub>  | _      | -    | ns   |                |

| Hold time       | t <sub>10</sub> SR | 0                           | -      | -    | ns   |                |

| Table 48 | USIC IIS Slave | <b>Receiver Timing</b> |

|----------|----------------|------------------------|

|----------|----------------|------------------------|

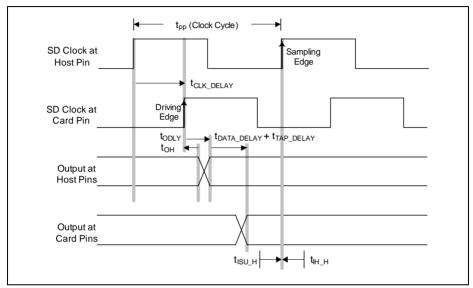

Figure 29 USIC IIS Slave Receiver Timing

| No clock delay:   |                                                                                                                                                            | (7) |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                   | $t_{ODLY\_H} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL}$                                                                                        |     |

| With clock delay: |                                                                                                                                                            |     |

|                   |                                                                                                                                                            | (8) |

|                   | $t_{\text{ODLY}\_H} + t_{\text{DATA}\_\text{DELAY}} + t_{\text{TAP}\_\text{DELAY}} + t_{\text{ISU}} < t_{\text{WL}} + t_{\text{CLK}\_\text{DELAY}}$        |     |

|                   |                                                                                                                                                            | (9) |

|                   | $t_{\text{DATA}\_\text{DELAY}} + t_{\text{TAP}\_\text{DELAY}} - t_{\text{CLK}\_\text{DELAY}} < t_{\text{WL}} - t_{\text{ISU}} - t_{\text{ODLY}\_\text{H}}$ |     |

|                   | $t_{\text{DATA}\_\text{DELAY}} - t_{\text{CLK}\_\text{DELAY}} < t_{\text{WL}} - t_{\text{ISU}} - t_{\text{ODLY}\_\text{H}} - t_{\text{TAP}\_\text{DELAY}}$ |     |

|                   | $t_{DATA\_DELAY} - t_{CLK\_DELAY} < 10 - 6 - 14 - t_{TAP\_DELAY}$                                                                                          |     |

|                   | $t_{\text{DATA}\_\text{DELAY}} - t_{\text{CLK}\_\text{DELAY}} < -10 - t_{\text{TAP}\_\text{DELAY}}$                                                        |     |

The data delay is less than the clock delay by at least 10 ns in the ideal case where  $t_{WL}$ = 10 ns.

#### High-Speed Write Meeting Hold (Minimum Delay)

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(10)

$t_{\mathrm{CLK\_DELAY}} < t_{WL} + t_{\mathrm{OH\_H}} + t_{\mathrm{DATA\_DELAY}} + t_{\mathrm{TAP\_DELAY}} - t_{\mathrm{IH}}$

$t_{\mathrm{CLK\_DELAY}} - t_{\mathrm{DATA\_DELAY}} < t_{\mathrm{WL}} + t_{\mathrm{OH\_H}} + t_{\mathrm{TAP\_DELAY}} - t_{\mathrm{IH}}$

$t_{\mathrm{CLK\_DELAY}} - t_{\mathrm{DATA\_DELAY}} < 10 + 2 + t_{\mathrm{TAP\_DELAY}} - 2$

$t_{\rm CLK\_DELAY} - t_{\rm DATA\_DELAY} < 10 + t_{\rm TAP\_DELAY}$

The clock can be delayed versus data up to 13.2 ns (external delay line) in ideal case of  $t_{WL}$ = 10 ns, with maximum  $t_{TAP DELAY}$  = 3.2 ns programmed.

# High-Speed Input Path (Read)

# Figure 33 High-Speed Input Path

## High-Speed Read Meeting Setup (Maximum Delay)

The following equations show how to calculate the allowed combined propagation delay range of the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(11)

```

t_{\mathrm{CLK\_DELAY}} + t_{\mathrm{DATA\_DELAY}} + t_{\mathrm{TAP\_DELAY}} + t_{\mathrm{ODLY}} + t_{\mathrm{ISU\_H}} < t_{pp}

```

```

t_{\mathrm{CLK\_DELAY}} + t_{\mathrm{DATA\_DELAY}} < t_{pp} - t_{\mathrm{ODLY}} - t_{ISU\_H} - t_{\mathrm{TAP\_DELAY}}

```

$t_{\text{CLK}\_\text{DELAY}} + t_{\text{DATA}\_\text{DELAY}} < 20 - 14 - 2 - t_{\text{TAP}\_\text{DELAY}}$

$t_{\mathrm{CLK\_DELAY}} + t_{\mathrm{DATA\_DELAY}} < 4 - t_{\mathrm{TAP\_DELAY}}$

The data + clock delay can be up to 4 ns for a 20 ns clock cycle.

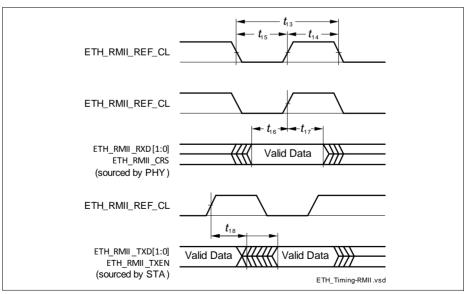

# 3.3.10.3 ETH RMII Parameters

In the following, the parameters of the RMII (Reduced Media Independent Interface) are described.

| Table 55 ETH RMII Signal Timing Parameters |

|--------------------------------------------|

|--------------------------------------------|

| Parameter                                      |                        | Symbol |      | Value | S    | Unit | Note /                            |

|------------------------------------------------|------------------------|--------|------|-------|------|------|-----------------------------------|

|                                                |                        |        | Min. | Тур.  | Max. |      | Test Condit<br>ion                |

| ETH_RMII_REF_CL clock period                   | <i>t</i> <sub>13</sub> | SR     | 20   | -     | _    | ns   | C <sub>L</sub> = 25 pF;<br>50 ppm |

| ETH_RMII_REF_CL clock high time                | t <sub>14</sub>        | SR     | 7    | -     | 13   | ns   | C <sub>L</sub> = 25 pF            |

| ETH_RMII_REF_CL clock low time                 | t <sub>15</sub>        | SR     | 7    | -     | 13   | ns   |                                   |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS setup time  | t <sub>16</sub>        | SR     | 4    | _     | _    | ns   |                                   |

| ETH_RMII_RXD[1:0],<br>ETH_RMII_CRS hold time   | t <sub>17</sub>        | SR     | 2    | -     | -    | ns   |                                   |

| ETH_RMII_TXD[1:0],<br>ETH_RMII_TXEN data valid | t <sub>18</sub>        | СС     | 4    | -     | 15   | ns   |                                   |

Figure 37 ETH RMII Signal Timing

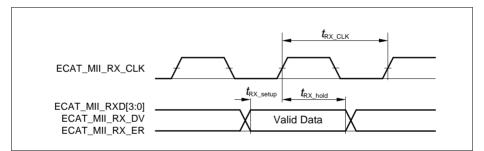

# 3.3.11.4 MII Timing RX Characteristics

| Parameter                                                     | Symbol                      | Values |      |      | Unit | Note /                                              |

|---------------------------------------------------------------|-----------------------------|--------|------|------|------|-----------------------------------------------------|

|                                                               |                             | Min.   | Тур. | Max. |      | Test Condition                                      |

| RX_CLK period                                                 | t <sub>RX_CLK</sub><br>SR   | -      | 40   | -    | ns   | C <sub>L</sub> = 25 pF,<br>IEEE802.3<br>requirement |

| RX_DV/RX_DV/RXD[3:0]<br>valid before rising<br>edge of RX_CLK | t <sub>RX_setup</sub><br>SR | 10     | -    | -    | ns   |                                                     |

| RX_DV/RX_DV/RXD[3:0]<br>valid after rising<br>edge of RX_CLK  | t <sub>RX_hold</sub><br>SR  | 10     | _    | -    | ns   |                                                     |

Figure 41 MII RX characteristics

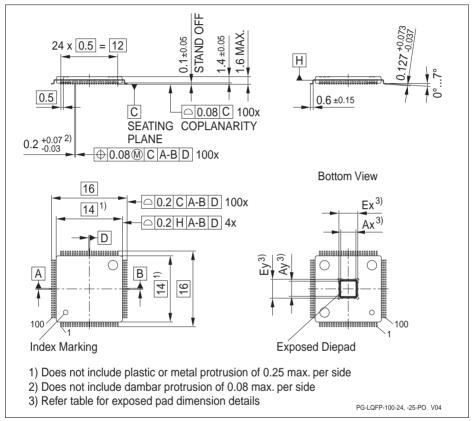

## Package and Reliability

# 4.2 Package Outlines

The exposed die pad dimensions are listed in Table 60.

Figure 43 PG-LQFP-100-25 (Plastic Green Low Profile Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages