# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 6                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1612-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC12(L)F1612/16(L)F1613

#### Value on Value on all Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR. BOR other Resets Bank 3 18Ch ANSELA ANSA4 ANSA2 ANSA1 ANSA0 ---1 -111 ---1 -111 \_\_\_\_ \_ 18Dh Unimplemented \_ ANSELC(4) ANSC3 18Eh ANSC2 ANSC1 ANSC0 ---- 1111 ---- 1111 \_\_\_\_ \_ 18Fh Unimplemented \_ \_\_\_\_ \_ 190h Unimplemented \_ 191h PMADRL Flash Program Memory Address Register Low Byte 0000 0000 0000 0000 \_\_(2) PMADRH Flash Program Memory Address Register High Byte 192h 1000 0000 1000 0000 193h PMDATL Flash Program Memory Read Data Register Low Byte XXXX XXXX uuuu uuuu PMDATH \_ Flash Program Memory Read Data Register High Byte 194h \_ --xx xxxx --uu uuuu \_(2) PMCON1 CFGS LWLO FREE WRERR WREN WR RD 195h 1000 x000 1000 q000 PMCON2 196h Flash Program Memory Control Register 2 0000 0000 0000 0000 VREGCON<sup>(1)</sup> 197h \_\_\_\_ \_ \_ \_ \_ \_ VREGPM Reserved ---- --01 ---- --01 198h Unimplemented to 19Fh Bank 4 WPUA WPUA5 WPUA4 WPUA3 WPUA2 WPUA1 WPUA0 20Ch --11 1111 --11 1111 \_\_\_\_ Unimplemented 20Dh WPUC(4) 20Eh WPUC5 WPUC4 WPUC3 WPUC2 WPUC1 WPUC0 --11 1111 --11 1111 \_\_\_\_ 20Fh Unimplemented to \_\_\_\_ \_\_\_\_ 21Fh

#### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC12F1612/16F1613 only.

2: Unimplemented, read as '1'.

3: PIC12(L)F1612 only.

4: PIC16(L)F1613 only.

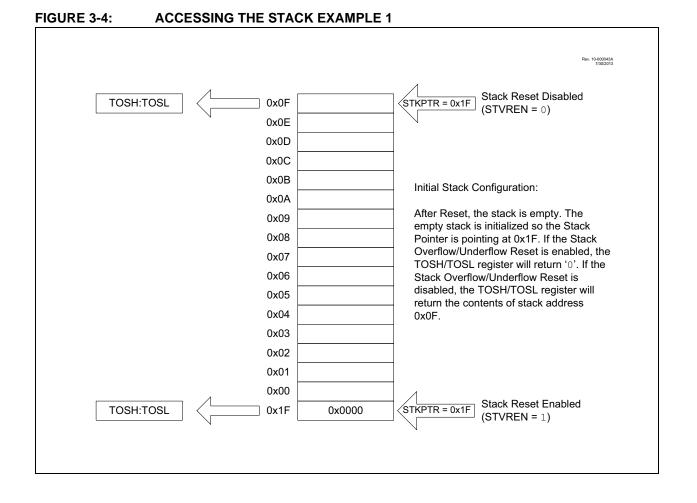

## 3.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-4 through 3-7). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

## 3.5.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement the STKPTR.

Reference Figure 3-4 through Figure 3-7 for examples of accessing the stack.

## 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4 "Write Protection"** for more information.

## 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC12(L)F1612/16(L)F161X Memory Programming Specification*" (DS40001720).

## PIC12(L)F1612/16(L)F1613

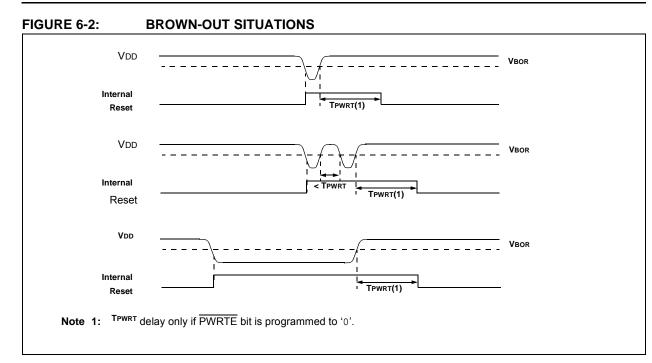

## 6.3 Register Definitions: BOR Control

## REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7      | <pre>SBOREN: Software Brown-Out Reset Enable bit If BOREN &lt;1:0&gt; in Configuration Words = 01: 1 = BOR Enabled 0 = BOR Disabled If BOREN &lt;1:0&gt; in Configuration Words ≠ 01: SBOREN is read/write, but has no effect on the BOR</pre>                                                                                                                                           |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6      | BORFS: Brown-Out Reset Fast Start bit <sup>(1)</sup><br>If BOREN <1:0> = 10 (Disabled in Sleep) or BOREN<1:0> = 01 (Under software control):<br>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)<br>0 = Band gap operates normally, and may turn off<br>If BOREN<1:0> = 11 (Always on) or BOREN<1:0> = 00 (Always off)<br>BORFS is Read/Write, but has no effect. |

| bit 5-1    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                               |

| bit 0      | BORRDY: Brown-Out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                             |

| Note 1. BC | REN<1:0> hits are located in Configuration Words                                                                                                                                                                                                                                                                                                                                         |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

POR

DC

BOR

С

SEN

Register on Page 71

75

21

99

| TABLE 6-5. SUMMART OF REGISTERS ASSOCIATED WITH RESETS |        |       |       |       |       |       |       |        |  |

|--------------------------------------------------------|--------|-------|-------|-------|-------|-------|-------|--------|--|

| Name                                                   | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  |  |

| BORCON                                                 | SBOREN | BORFS | _     | _     | _     | _     | _     | BORRDY |  |

RWDT

TO

RMCLR

PD

WDTPS<4:0>

RI

Ζ

#### TABLE 6-5:SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented bit, reads as '0'. <u>Shaded</u> cells are not used by Resets.

STKUNF

\_\_\_\_

WDTWV

PCON

STATUS

WDTCON0

STKOVF

\_\_\_\_

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

#### TABLE 6-6: SUMMARY OF CONFIGURATION WORD WITH RESETS

| Name        | Bits | Bit -/7 | Bit -/6 | Bit 13/5    | Bit 12/4 | Bit 11/3 | Bit 10/2    | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|-------------|------|---------|---------|-------------|----------|----------|-------------|-----------|---------|---------------------|

|             | 13:8 |         |         | _           |          | CLKOUTEN | BOREI       | N<1:0>    | _       | 50                  |

| CONFIG1 7:0 |      | CP      | MCLRE   | PWRTE       | _        | _        | _           | FOSC<1:0> |         | 52                  |

|             | 13:8 | _       | _       | LVP         | DEBUG    | LPBOR    | BORV        | STVREN    | PLLEN   | 50                  |

| CONFIG2     | 7:0  | ZCD     | _       | -           | _        | —        | _           | WRT       | <1:0>   | 53                  |

| 13          |      | _       | _       | WDTCCS<2:0> |          |          | WDTCWS<2:0> |           |         |                     |

| CONFIG3     | 7:0  | _       | WDT     | E<1:0>WD    |          |          | DTCPS<4:0>  |           |         | 53                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

## 8.3 Register Definitions: Voltage Regulator Control

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1  |  |

|-------------|-----|-----|-----|-----|-----|---------|----------|--|

| —           | —   | —   | _   | —   | —   | VREGPM  | Reserved |  |

| bit 7 bit 0 |     |     |     |     |     |         |          |  |

|             |     |     |     |     |     |         |          |  |

## **REGISTER 8-1:** VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-2 | Unimplemented: Read as '0'                               |

|---------|----------------------------------------------------------|

| bit 1   | VREGPM: Voltage Regulator Power Mode Selection bit       |

|         | 1 = Low-Power Sleep mode enabled in Sleep <sup>(2)</sup> |

|         | Draws lowest current in Sleep, slower wake-up            |

|         | 0 = Normal Power mode enabled in Sleep <sup>(2)</sup>    |

|         | Draws higher current in Sleep, faster wake-up            |

#### bit 0 **Reserved:** Read as '1'. Maintain this bit set.

Note 1: PIC12F1612/16F1613 only.

2: See Section 28.0 "Electrical Specifications".

| Name                 | Bit 7   | Bit 6               | Bit 5     | Bit 4     | Bit 3  | Bit 2     | Bit 1     | Bit 0  | Register on<br>Page |

|----------------------|---------|---------------------|-----------|-----------|--------|-----------|-----------|--------|---------------------|

| INTCON               | GIE     | PEIE                | TMR0IE    | INTE      | IOCIE  | TMR0IF    | INTF      | IOCIF  | 82                  |

| IOCAF                | —       | _                   | IOCAF5    | IOCAF4    | IOCAF3 | IOCAF2    | IOCAF1    | IOCAF0 | 148                 |

| IOCAN                | _       | _                   | IOCAN5    | IOCAN4    | IOCAN3 | IOCAN2    | IOCAN1    | IOCAN0 | 148                 |

| IOCAP                | _       | _                   | IOCAP5    | IOCAP4    | IOCAP3 | IOCAP2    | IOCAP1    | IOCAP0 | 148                 |

| IOCCP <sup>(1)</sup> | —       | —                   | IOCCP5    | IOCCP4    | IOCCP3 | IOCCP2    | IOCCP1    | IOCCP0 | 148                 |

| IOCCN <sup>(1)</sup> | —       | _                   | IOCCN5    | IOCCN4    | IOCCN3 | IOCCN2    | IOCCN1    | IOCCN0 | 148                 |

| IOCCF <sup>(1)</sup> | _       | _                   | IOCCF5    | IOCCF4    | IOCCF3 | IOCCF2    | IOCCF1    | IOCCF0 | 148                 |

| PIE1                 | TMR1GIE | ADIE                | —         | _         |        | CCP1IE    | TMR2IE    | TMR1IE | 83                  |

| PIE2                 | —       | C2IE <sup>(1)</sup> | C1IE      | _         |        | TMR6IE    | TMR4IE    | CCP2IE | 84                  |

| PIE3                 | _       | _                   | CWGIE     | ZCDIE     |        | _         | _         | _      | 85                  |

| PIE4                 | SCANIE  | CRCIE               | SMT2PWAIE | SMT2PRAIE | SMT2IE | SMT1PWAIE | SMT1PRAIE | SMT1IF | 86                  |

| PIR1                 | TMR1GIF | ADIF                | _         | _         | -      | CCP1IF    | TMR2IF    | TMR1IF | 87                  |

| PIR2                 | _       | C2IF <sup>(1)</sup> | C1IF      | _         |        | TMR6IF    | TMR4IF    | CCP2IF | 88                  |

| PIR3                 | —       | _                   | CWGIF     | ZCDIF     |        | —         | _         | _      | 89                  |

| PIR4                 | SCANIF  | CRCIF               | SMT2PWAIF | SMT2PRAIF | SMT2IF | SMT1PWAIF | SMT1PRAIF | SMT1IF | 90                  |

| STATUS               | —       | —                   | —         | TO        | PD     | Z         | DC        | С      | 21                  |

| WDTCON0              | _       | _                   |           |           |        | SEN       | 99        |        |                     |

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

Note 1: PIC16(L)F1613 only.

### 9.1 Independent Clock Source

The WDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of either the WDTCCS<2:0> configuration bits or the WDTCS<2:0> bits of WDTCON1. Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See **Section28.0 "Electrical Specifications**" for LFINTOSC and MFINTOSC tolerances.

## 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SEN bit of the WDTCON0 register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| WDTE<1:0> | SEN | Device<br>Mode | WDT<br>Mode |

|-----------|-----|----------------|-------------|

| 11        | Х   | Х              | Active      |

| 10        |     | Awake          | Active      |

| 10        | Х   | Sleep          | Disabled    |

| 0.1       | 1   | х              | Active      |

| 01        | 0   | х              | Disabled    |

| 0 0       | х   | х              | Disabled    |

| TABLE 9-1: | WDT OPERATING MODES |

|------------|---------------------|

| IADLL 3-1. |                     |

## 9.3 Time-Out Period

The WDTPS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

## 9.4 Watchdog Window

The Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WDT Reset, similar to a WDT time out. See Figure 9-2 for an example.

The window size is controlled by the WDTCWS<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

In the event of a <u>window</u> violation, a Reset will be generated and the WDTWV bit of the PCON register will be cleared. This bit is set by a POR or can be set in firmware.

## 9.5 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- Valid CLRWDT instruction is executed

- · Device enters Sleep

- Device wakes up from Sleep

- · WDT is disabled

- · Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1 registers

#### 9.5.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation.

See Table 9-2 for more information.

## 9.6 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

The WDT remains clear until the OST, if enabled, completes. See **Section5.0** "**Oscillator Module**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. The  $\overline{RWDT}$  bit in the PCON register can also be used. See **Section3.0** "Memory **Organization**" for more information.

| U-0                                     | U-0                                | R/W-1/1                                | R/W-1/1 | U-0                                                   | R/W-1/1          | R/W-1/1  | R/W-1/1 |  |

|-----------------------------------------|------------------------------------|----------------------------------------|---------|-------------------------------------------------------|------------------|----------|---------|--|

| _                                       | —                                  | SLRA5                                  | SLRA4   | —                                                     | SLRA2            | SLRA1    | SLRA0   |  |

| bit 7                                   |                                    |                                        |         |                                                       |                  |          | bit 0   |  |

| Logondu                                 |                                    |                                        |         |                                                       |                  |          |         |  |

| Legend:                                 |                                    |                                        |         |                                                       |                  |          |         |  |

| R = Readat                              | ole bit                            | W = Writable                           | bit     | U = Unimpler                                          | mented bit, read | l as '0' |         |  |

| u = Bit is unchanged x = Bit is unknown |                                    |                                        | nown    | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |

| '1' = Bit is s                          | et                                 | '0' = Bit is clea                      | ared    |                                                       |                  |          |         |  |

|                                         |                                    |                                        |         |                                                       |                  |          |         |  |

| bit 7-6                                 | Unimplemen                         | Unimplemented: Read as '0'             |         |                                                       |                  |          |         |  |

| bit 5-4                                 | SLRA<5:4>:                         | SLRA<5:4>: PORTA Slew Rate Enable bits |         |                                                       |                  |          |         |  |

|                                         | For RA<5:4> pins, respectively     |                                        |         |                                                       |                  |          |         |  |

|                                         | 1 = Port pin slew rate is limited  |                                        |         |                                                       |                  |          |         |  |

|                                         | 0 = Port pin slews at maximum rate |                                        |         |                                                       |                  |          |         |  |

| bit 3                                   | Unimplemen                         | Unimplemented: Read as '0'             |         |                                                       |                  |          |         |  |

| bit 2-0                                 | SLRA<2:0>:                         | SLRA<2:0>: PORTA Slew Rate Enable bits |         |                                                       |                  |          |         |  |

| For RA<2:0> pins, respectively          |                                    |                                        |         |                                                       |                  |          |         |  |

|                                         | 1 = Port pin slew rate is limited  |                                        |         |                                                       |                  |          |         |  |

|                                         | 0 = Port pin s                     | lews at maxim                          | um rate |                                                       |                  |          |         |  |

|                                         |                                    |                                        |         |                                                       |                  |          |         |  |

## REGISTER 12-8: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

## REGISTER 12-9: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 INLVLA<5:0>: PORTA Input Level Select bits

For RA<5:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

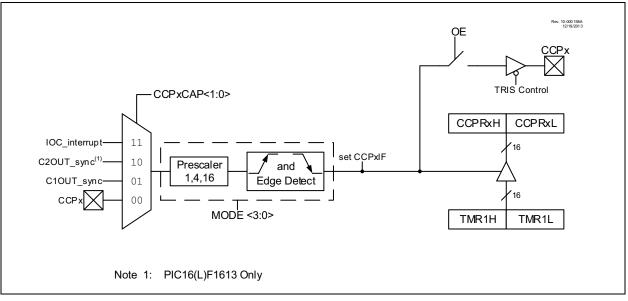

#### 23.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See **Section21.0 "Timer1/3/5 Module with Gate Control**" for more information on configuring Timer1.

#### 23.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

#### 23.1.4 CCP PRESCALER

There are four prescaler settings specified by the MODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the EN bit of the CCPxCON register before changing the prescaler.

## 23.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

#### 23.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section12.1 "Alternate Pin Function**" for more information.

## 23.1.7 CAPTURE OUTPUT

Whenever a capture occurs, the output of the CCP will go high for a period equal to one system clock period (1/FOSC). This output is available as an input signal to the CWG, as an auto-conversion trigger for the ADC, as an External Reset Signal for the TMR2 modules, as a window input to the SMT, and as an input to the CLC module.

#### 23.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2/4/6 registers

- T2CON/T4CON/T6CON registers

- CCPRxH:CCPRxL register pair

Figure shows a simplified block diagram of PWM operation.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### 23.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- 1. Disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Determine which timer will be used to clock the CCP; Timer2/4/6.

- 3. Load the associated PR2/4/6 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- 5. Load the CCPRxH:CCPRxL register pair with the PWM duty cycle value.

- 6. Configure and start Timer2/4/6:

- Clear the TMR2IF/TMR4IF/TMR6IF interrupt flag bit of the PIRx register. See Note below.

- Configure the CKPS bits of the TxCON register with the Timer prescale value.

- Enable the Timer by setting the ON bit of the TxCON register.

- 7. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF/TMR4IF/TMR6IF bit of the PIRx register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

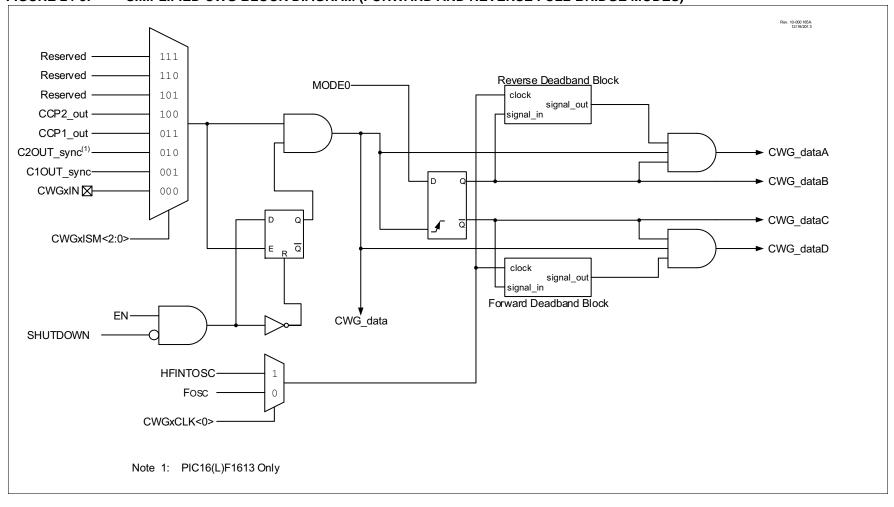

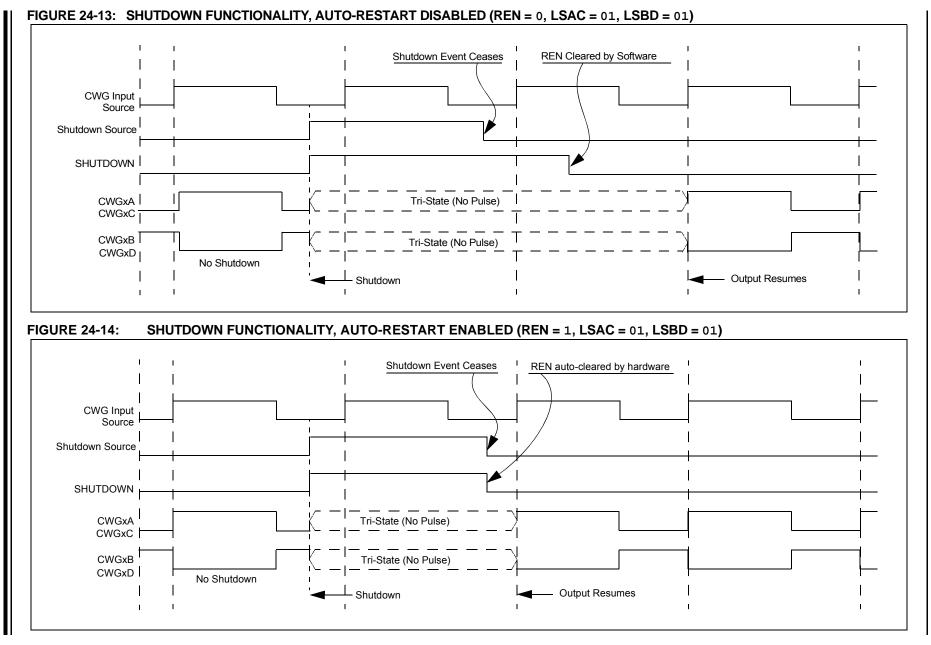

#### 24.1.2 PUSH-PULL MODE

In Push-Pull mode, two output signals are generated, alternating copies of the input as illustrated in Figure 24-2. This alternation creates the push-pull effect required for driving some transformer-based power supply designs.

The push-pull sequencer is reset whenever EN = 0 or if an auto-shutdown event occurs. The sequencer is clocked by the first input pulse, and the first output appears on CWGxA.

The unused outputs CWGxC and CWGxD drive copies of CWGxA and CWGxB, respectively, but with polarity controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

#### 24.1.3 FULL-BRIDGE MODES

In Forward and Reverse Full-Bridge modes, three outputs drive static values while the fourth is modulated by the input data signal. In Forward Full-Bridge mode, CWGxA is driven to its active state, CWGxB and CWGxC are driven to their inactive state, and CWGxD is modulated by the input signal. In Reverse Full-Bridge mode, CWGxC is driven to its active state, CWGxA and CWGxD are driven to their inactive states, and CWGxB is modulated by the input signal. In Full-Bridge mode, the dead-band period is used when there is a switch from forward to reverse or vice-versa. This dead-band control is described in Section 24.5 "Dead-Band Control", with additional details in Section 24.6 "Rising Edge and Reverse Dead Band" and Section 24.7 "Falling Edge and Forward Dead Band".

The mode selection may be toggled between forward and reverse by toggling the MODE<0> bit of the CWGxCON0 while keeping MODE<2:1> static, without disabling the CWG module.

#### FIGURE 24-3: SIMPLIFIED CWG BLOCK DIAGRAM (FORWARD AND REVERSE FULL-BRIDGE MODES)

PIC12(L)F1612/16(L)F1613

PIC12(L)F1612/16(L)F1613

#### 25.6.5 WINDOWED MEASURE MODE

This mode measures the window duration of the SMTWINx input of the SMT. It begins incrementing the timer on a rising edge of the SMTWINx input and updates the SMTxCPR register with the value of the timer and resets the timer on a second rising edge. See Figure 25-10 and Figure 25-11.

#### 25.6.7 TIME OF FLIGHT MEASURE MODE

This mode measures the time interval between a rising edge on the SMTWINx input and a rising edge on the SMTx\_signal input, beginning to increment the timer upon observing a rising edge on the SMTWINx input, while updating the SMTxCPR register and resetting the timer upon observing a rising edge on the SMTx\_signal input. In the event of two SMTWINx rising edges without an SMTx\_signal rising edge, it will update the SMTxCPW register with the current value of the timer and reset the timer value. See Figure 25-14 and Figure 25-15.

| R/W/HC-0/0       | R/W/HC-0/0                                                                                                                                                            | R/W/HC-0/0        | U-0  | U-0             | R-0/0                             | R-0/0    | R-0/0        |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|-----------------|-----------------------------------|----------|--------------|

| CPRUP            | CPWUP                                                                                                                                                                 | RST               |      | _               | TS                                | WS       | AS           |

| bit 7            |                                                                                                                                                                       |                   |      |                 |                                   |          | bit 0        |

| 1                |                                                                                                                                                                       |                   |      |                 |                                   |          |              |

| Legend:          | arad by bardwa                                                                                                                                                        |                   |      | LIC - Dit is as | t hy hardwara                     |          |              |

| R = Readable     | ared by hardwa                                                                                                                                                        | W = Writable      | hit  |                 | et by hardware                    | 1 00 '0' |              |

| u = Bit is unch  |                                                                                                                                                                       | x = Bit is unkr   |      | •               | nented bit, read<br>at POR and BO |          | othor Doooto |

| '1' = Bit is set | angeu                                                                                                                                                                 | 0' = Bit is clear |      |                 |                                   |          | other Resets |

| I = DILIS SEL    |                                                                                                                                                                       |                   | areu | q = value dep   | pends on condi                    | lion     |              |

| bit 7            | <ul> <li>7 CPRUP: SMT Manual Period Buffer Update bit</li> <li>1 = Request update to SMTxCPRx registers</li> <li>0 = SMTxCPRx registers update is complete</li> </ul> |                   |      |                 |                                   |          |              |

| bit 6            | <b>CPWUP:</b> SMT Manual Pulse Width Buffer Update bit<br>1 = Request update to SMTxCPW registers<br>0 = SMTxCPW registers update is complete                         |                   |      |                 |                                   |          |              |

| bit 5            | <ul> <li><b>RST:</b> SMT Manual Timer Reset bit</li> <li>1 = Request Reset to SMTxTMR registers</li> <li>0 = SMTxTMR registers update is complete</li> </ul>          |                   |      |                 |                                   |          |              |

| bit 4-3          | Unimplemented: Read as '0'                                                                                                                                            |                   |      |                 |                                   |          |              |

| bit 2            | <b>TS:</b> SMT GO Value Status bit<br>1 = SMT timer is incrementing<br>0 = SMT timer is not incrementing                                                              |                   |      |                 |                                   |          |              |

| bit 1            | WS: SMTxWIN Value Status bit<br>1 = SMT window is open<br>0 = SMT window is closed                                                                                    |                   |      |                 |                                   |          |              |

| bit 0            | AS: SMT_signal Value Status bit<br>1 = SMT acquisition is in progress<br>0 = SMT acquisition is not in progress                                                       |                   |      |                 |                                   |          |              |

## REGISTER 25-3: SMTxSTAT: SMT STATUS REGISTER

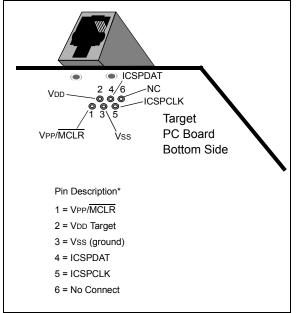

## 26.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "*PIC12(L)F1612/PIC16(L)F161X Memory Programming Specification*" (DS40001720).

## 26.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

## 26.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the ICSP Low-Voltage Programming Entry mode is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section6.5** "**MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

## 26.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>TM</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 26-1.

### FIGURE 26-1: ICD RJ-11 STYLE CONNECTOR INTERFACE

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 26-2.

## 28.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Т      |                                      |     |                |

|--------|--------------------------------------|-----|----------------|

| F      | Frequency                            | Т   | Time           |

| Lowerc | ase letters (pp) and their meanings: |     |                |

| рр     |                                      |     |                |

| сс     | CCP1                                 | osc | CLKIN          |

| ck     | CLKOUT                               | rd  | RD             |

| CS     | CS                                   | rw  | RD or WR       |

| di     | SDIx                                 | sc  | SCKx           |

| do     | SDO                                  | ss  | SS             |

| dt     | Data in                              | tO  | ТОСКІ          |

| io     | I/O PORT                             | t1  | T1CKI          |

| mc     | MCLR                                 | wr  | WR             |

| Upperc | ase letters and their meanings:      |     |                |

| S      |                                      |     |                |

| F      | Fall                                 | Р   | Period         |

| Н      | High                                 | R   | Rise           |

| I      | Invalid (High-impedance)             | V   | Valid          |

| L      | Low                                  | Z   | High-impedance |

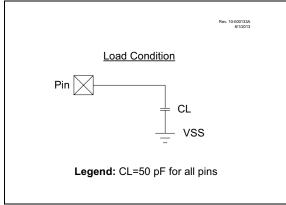

### FIGURE 28-4: LOAD CONDITIONS

## THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support