Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 6                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1612-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

### 1.1 Register and Bit Naming Conventions

#### 1.1.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

#### 1.1.2 BIT NAMES

There are two variants for bit names:

- Short name: Bit function abbreviation

- Long name: Peripheral abbreviation + short name

#### 1.1.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is *RegisterName*bits.*ShortName*. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

#### 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral, thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

#### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

COG1CON0bits.MD = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

Example 1:

MOVLW ~(1<<G1MD1) ANDWF COG1CON0,F MOVLW 1<<G1MD2 | 1<<G1MD0 IORWF COG1CON0,F

#### Example 2:

| BSF | COG1CON0,G1MD2 |

|-----|----------------|

| BCF | COG1CON0,G1MD1 |

| BSF | COG1CON0,G1MD0 |

#### 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

#### 1.1.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

#### 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

#### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### REGISTER 3-1: STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u u1uu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 27.0 "Instruction Set Summary").

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

| U-0                               | U-0                                     | U-0                                                 | R-1/q                                                 | R-1/q                              | R/W-0/u | R/W-0/u           | R/W-0/u          |  |

|-----------------------------------|-----------------------------------------|-----------------------------------------------------|-------------------------------------------------------|------------------------------------|---------|-------------------|------------------|--|

| _                                 | _                                       | _                                                   | TO                                                    | PD                                 | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |

| bit 7                             |                                         |                                                     |                                                       |                                    | •       | •                 | bit 0            |  |

|                                   |                                         |                                                     |                                                       |                                    |         |                   |                  |  |

| Legend:                           |                                         |                                                     |                                                       |                                    |         |                   |                  |  |

| R = Readable bit W = Writable bit |                                         |                                                     | bit                                                   | U = Unimplemented bit, read as '0' |         |                   |                  |  |

| u = Bit is uncha                  | u = Bit is unchanged x = Bit is unknown |                                                     | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |                   |                  |  |

| '1' = Bit is set                  |                                         | '0' = Bit is cleared q = Value depends on condition |                                                       |                                    |         |                   |                  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-Down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                               |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                             |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                                   |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

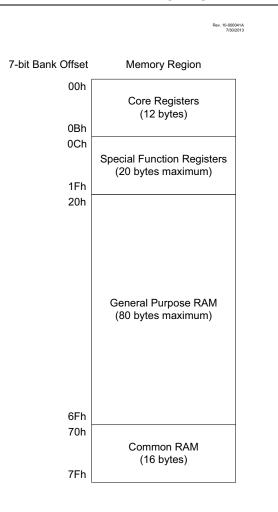

#### 3.3.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.3.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.3.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a nonbanked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2 "Linear Data Memory"** for more information.

#### 3.3.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### 3.3.5 DEVICE MEMORY MAPS

The memory maps are shown in Table 3-2 through Table 3-7.

## FIGURE 3-2:

#### BANKED MEMORY PARTITIONING

| TADLL | 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |                                                                                                          |               |         |         |        |         |                        |           |                      |                           |

|-------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------|---------|---------|--------|---------|------------------------|-----------|----------------------|---------------------------|

| Addr  | Name                                               | Bit 7                                                                                                    | Bit 6         | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1                  | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

| Bank  | Bank 2                                             |                                                                                                          |               |         |         |        |         |                        |           |                      |                           |

| 10Ch  | LATA                                               | —                                                                                                        | —             | LATA5   | LATA4   | —      | LATA2   | LATA1                  | LATA0     | xx -xxx              | uu -uuu                   |

| 10Dh  | _                                                  | Unimplemented                                                                                            | Inimplemented |         |         |        |         |                        |           | —                    | _                         |

| 10Eh  | LATC <sup>(4)</sup>                                | —                                                                                                        | —             | LATC5   | LATC4   | LATC3  | LATC2   | LATC1                  | LATC0     | xx xxxx              | uu uuuu                   |

| 10Fh  | _                                                  | Unimplemented                                                                                            | nimplemented  |         |         |        |         |                        |           |                      |                           |

| 110h  | _                                                  | Unimplemented                                                                                            | nimplemented  |         |         |        |         |                        |           | —                    | _                         |

| 111h  | CM1CON0                                            | C10N                                                                                                     | C1OUT         | C10E    | C1POL   |        | C1SP    | C1HYS                  | C1SYNC    | 0000 -100            | 0000 -100                 |

| 112h  | CM1CON1                                            | C1INTP                                                                                                   | C1INTN        | C1PCH   | 1<1:0>  |        |         | C1NCH<2:0>             |           | 0000 -000            | 0000 -000                 |

| 113h  | CM2CON0 <sup>(4)</sup>                             | C2ON                                                                                                     | C2OUT         | C2OE    | C2POL   | —      | C2SP    | C2HYS                  | C2SYNC    | 0000 -100            | 0000 -100                 |

| 114h  | CM2CON1 <sup>(4)</sup>                             | C2INTP                                                                                                   | C2INTN        | C2PCH   | 1<1:0>  | _      |         | C2NCH<2:0>             |           | 0000 -000            | 0000 -000                 |

| 115h  | CMOUT                                              | _                                                                                                        | —             | —       | —       |        | —       | MC2OUT <sup>(4)</sup>  | MC1OUT    | 00                   | 00                        |

| 116h  | BORCON                                             | SBOREN                                                                                                   | BORFS         | —       | —       | —      | —       | —                      | BORRDY    | 10q                  | uuu                       |

| 117h  | FVRCON                                             | FVREN                                                                                                    | FVRRDY        | TSEN    | TSRNG   | CDAFV  | ′R<1:0> | ADFVI                  | R<1:0>    | 0q00 0000            | 0q00 0000                 |

| 118h  | DAC1CON0                                           | DAC1EN                                                                                                   | —             | DAC10E1 | —       | DAC1PS | SS<1:0> | —                      | —         | 0-0- 00              | 0-0- 00                   |

| 119h  | DAC1CON1                                           |                                                                                                          |               |         | DAC1F   | R<7:0> |         |                        |           | 0000 0000            | 0000 0000                 |

| 11Ah  |                                                    | Unimplemented — —                                                                                        |               |         |         |        |         |                        | —         |                      |                           |

| 11Bh  | -                                                  | Unimplemented                                                                                            |               |         |         |        |         | —                      | —         |                      |                           |

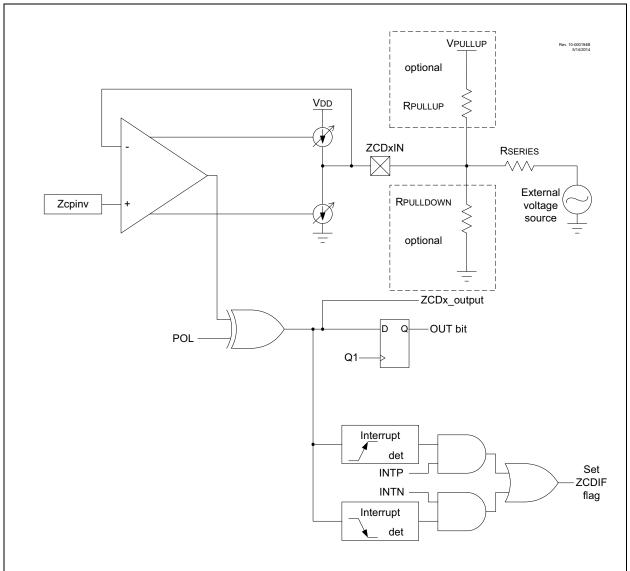

| 11Ch  | ZCD1CON                                            | ZCD1EN                                                                                                   | ZCD10E        | ZCD1OUT | ZCD1POL | _      | —       | ZCD1INTP               | ZCD1INTN  | 000000               | 000000                    |

| 11Dh  | APFCON                                             | - CWGASEL <sup>(3)</sup> CWGBSEL <sup>(3)</sup> - T1GSEL - CCP2SEL <sup>(4)</sup> CCP1SEL <sup>(3)</sup> |               |         |         |        |         | CCP1SEL <sup>(3)</sup> | -00- 0-00 | -00- 0-00            |                           |

| 11Eh  | _                                                  | Unimplemented —                                                                                          |               |         |         |        |         |                        | _         |                      |                           |

| 11Fh  |                                                    | Unimplemented                                                                                            |               |         |         |        |         |                        |           | _                    | _                         |

#### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: PIC12F1612/16F1613 only.

**2:** Unimplemented, read as '1'.

3: PIC12(L)F1612 only.

4: PIC16(L)F1613 only.

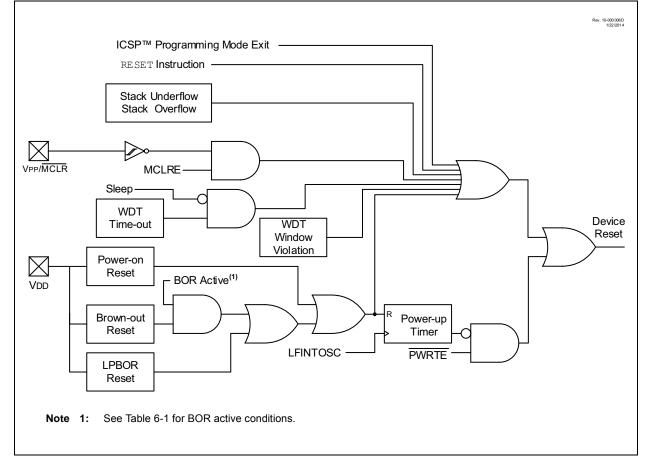

## 6.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- · Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-chip Reset Circuit is shown in Figure 6-1.

## 6.4 Low-Power Brown-Out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) operates like the BOR to detect low voltage conditions on the VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The BOR bit in PCON is used for both BOR and the LPBOR. Refer to Register 6-2.

The LPBOR voltage threshold (VLPBOR) has a wider tolerance than the BOR (VBOR), but requires much less current (LPBOR current) to operate. The LPBOR is intended for use when the BOR is configured as disabled (BOREN = 00) or disabled in Sleep mode (BOREN = 10).

Refer to Figure 6-1 to see how the LPBOR interacts with other modules.

#### 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

## 6.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

#### TABLE 6-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

## 6.5.1 MCLR ENABLED

When  $\overline{\text{MCLR}}$  is enabled and the pin is held low, the device is held in Reset. The  $\overline{\text{MCLR}}$  pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

## Note: A Reset does not drive the MCLR pin low.

## 6.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section12.3 "PORTA Registers"** for more information.

## 6.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period and the window is open. The TO and PD bits in the STATUS register are changed to indicate a WDT Reset caused by the timer overflowing, and WDTWV bit in the PCON register is changed to indicate a WDT Reset caused by a window violation. See **Section9.0 "Windowed Watchdog Timer (WDT)**" for more information.

## 6.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

## 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section3.5.2 "Overflow/Underflow Reset"** for more information.

## 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

## 6.10 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\mathsf{PWRTE}}$  bit of Configuration Words.

## 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section5.0** "Oscillator Module" for more information.

The Power-up Timer runs independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 FOSC cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

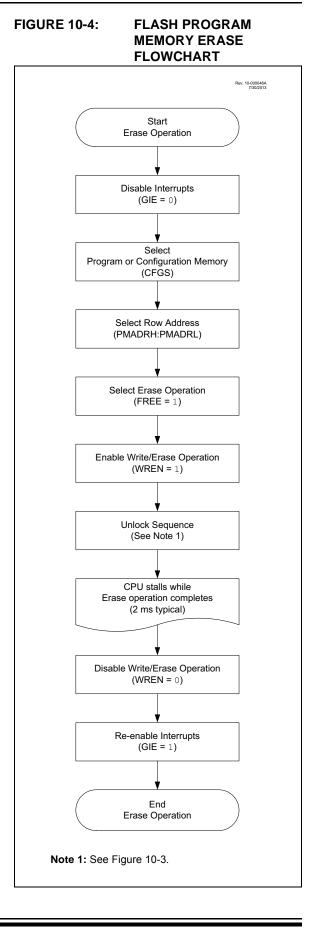

## 10.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

See Example 10-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions immediately following the WR bit set instruction. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

## 21.0 TIMER1/3/5 MODULE WITH GATE CONTROL

The Timer1/3/5 modules are a 16-bit timers/counters with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 2-bit prescaler

- Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- ADC Auto-Conversion Trigger(s)

- Selectable Gate Source Polarity

- · Gate Toggle mode

- · Gate Single-Pulse mode

- Gate Value Status

- · Gate Event Interrupt

Figure 21-1 is a block diagram of the Timer1 module.

Note: Three identical Timer1 modules are implemented on this device. The timers are named Timer1, Timer3, and Timer5. All references to Timer1 apply as well to Timer3 and Timer5, as well as references to their associated registers.

| FIGURE 21-5:   | TIMER1 GATE SINGLE-PULSE MOD | E                                                             |

|----------------|------------------------------|---------------------------------------------------------------|

| TMR1GE         |                              |                                                               |

| TMRTGE         |                              |                                                               |

| T1GPOL         |                              |                                                               |

| T1GSPM         |                              | Cleared by hardware on                                        |

| T1GG <u>O/</u> | Set by software              | ← falling edge of T1GVAL                                      |

| DONE           | Counting enabled on          |                                                               |

| T1G_in         | rising edge of T1G           |                                                               |

| т1СКІ          |                              |                                                               |

| T1GVAL         |                              |                                                               |

| Timer1         | N N + 1                      | N + 2                                                         |

| TMR1GIF        | — Cleared by software        | <ul> <li>Set by hardware on falling edge of T1GVAL</li> </ul> |

| REGISTER 23-3. COFRAE. COFA LOW DITE REGISTER | REGISTER 23-3: | CCPRxL: CCPx LOW BYTE REG | JSTER |

|-----------------------------------------------|----------------|---------------------------|-------|

|-----------------------------------------------|----------------|---------------------------|-------|

| R/W-0/0                                  | R/W-0/0          | R/W-0/0           | R/W-0/0            | R/W-0/0           | R/W-0/0                                              | R/W-0/0  | R/W-0/0 |  |  |

|------------------------------------------|------------------|-------------------|--------------------|-------------------|------------------------------------------------------|----------|---------|--|--|

|                                          |                  |                   | CCP                | R<7:0>            |                                                      |          |         |  |  |

| bit 7                                    |                  |                   |                    |                   |                                                      |          | bit 0   |  |  |

|                                          |                  |                   |                    |                   |                                                      |          |         |  |  |

| Legend:                                  |                  |                   |                    |                   |                                                      |          |         |  |  |

| R = Readable bit W = Writable            |                  |                   | bit                | U = Unimpler      | nented bit, read                                     | d as '0' |         |  |  |

| u = Bit is unchanged                     |                  | x = Bit is unkr   | x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Reset |          |         |  |  |

| '1' = Bit is set                         |                  | '0' = Bit is clea | ared               |                   |                                                      |          |         |  |  |

|                                          |                  |                   |                    |                   |                                                      |          |         |  |  |

| bit 7-0                                  | <u>MODE = Ca</u> | <u>pture Mode</u> |                    |                   |                                                      |          |         |  |  |

|                                          | CCPRxL<7:        | 0>: LSB of capt   | ured TMR1 v        | alue              |                                                      |          |         |  |  |

|                                          | MODE = Co        | <u>mpare Mode</u> |                    |                   |                                                      |          |         |  |  |

|                                          | CCPRxL<7:        | 0>: LSB compa     | red to TMR1        | value             |                                                      |          |         |  |  |

| MODE = PWM Mode && FMT = $\underline{0}$ |                  |                   |                    |                   |                                                      |          |         |  |  |

|                                          | CCPRxL<7:        | 0>: CCPW<7:0      | > — Pulse wie      | dth Least Signifi | cant eight bits                                      |          |         |  |  |

|                                          | MODE = PV        | VM Mode && FM     | <u>1T = 1</u>      |                   |                                                      |          |         |  |  |

|                                          |                  |                   |                    |                   |                                                      |          |         |  |  |

CCPRxL<7:6>: CCPW<1:0> — Pulse width Least Significant two bits CCPRxL<5:0>: Not used

| R/W-0/0                              | R/W-0/0                                 | R/W-0/0           | R/W-0/0        | R/W-0/0       | R/W-0/0          | R/W-0/0     | R/W-0/0 |  |  |

|--------------------------------------|-----------------------------------------|-------------------|----------------|---------------|------------------|-------------|---------|--|--|

|                                      |                                         |                   | CCPR           | <15:8>        |                  |             |         |  |  |

| bit 7                                |                                         |                   |                |               |                  |             | bit 0   |  |  |

|                                      |                                         |                   |                |               |                  |             |         |  |  |

| Legend:                              |                                         |                   |                |               |                  |             |         |  |  |

| R = Readable bit                     |                                         | W = Writable bit  |                | U = Unimpler  | nented bit, read | d as '0'    |         |  |  |

| u = Bit is unchanged x = Bit is unkn |                                         | own               | -n/n = Value a | at POR and BC | R/Value at all   | other Reset |         |  |  |

| '1' = Bit is set                     |                                         | '0' = Bit is clea | ared           |               |                  |             |         |  |  |

|                                      |                                         |                   |                |               |                  |             |         |  |  |

| bit 7-0 MODE = Capture Mode:         |                                         |                   |                |               |                  |             |         |  |  |

|                                      | CCPRxH<7:0>: MSB of captured TMR1 value |                   |                |               |                  |             |         |  |  |

|                                      |                                         |                   |                |               |                  |             |         |  |  |

## REGISTER 23-4: CCPRxH: CCPx HIGH BYTE REGISTER

MODE = Capture Mode:

CCPRxH<7:0>: MSB of captured TMR1 value

MODE = Compare Mode:

CCPRxH<7:0>: MSB compared to TMR1 value

MODE = PWM Mode && FMT = 0:

CCPRxH<7:2>: Not used

CCPRxH<1:0>: CCPW<9:8> — Pulse width Most Significant two bits

MODE = PWM Mode && FMT = 1:

CCPRxH<7:0>: CCPW<9:2> — Pulse width Most Significant eight bits

## REGISTER 23-5: CCPxCAP: CCPx CAPTURE INPUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | —   | —   | —   | CTS•    | <1:0>   |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:              |                      |                                                      |

|----------------------|----------------------|------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 CTS<1:0>: Capture Trigger Input Selection bits

- 11 = IOC\_interrupt

- $10 = C2_OUT_sync^{(1)}$

- 01 = C1\_OUT\_sync

- 00 = CCPx pin

Note 1: PIC16(L)F1613 only. Reserved on PIC12(L)F1612.

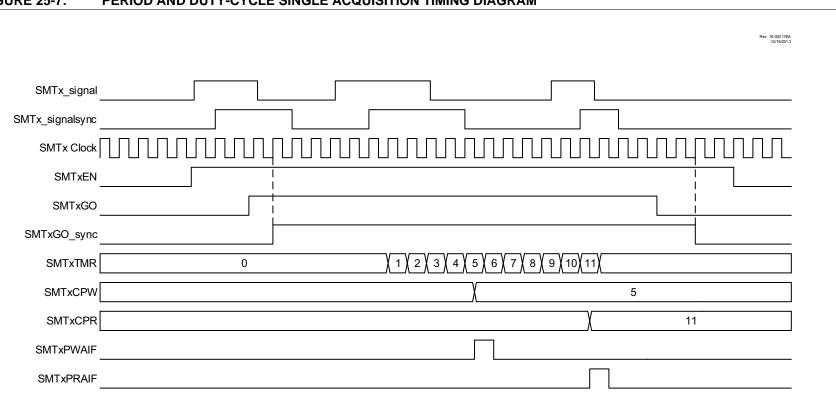

## FIGURE 25-7: PERIOD AND DUTY-CYCLE SINGLE ACQUISITION TIMING DIAGRAM

PIC12(L)F1612/16(L)F1613

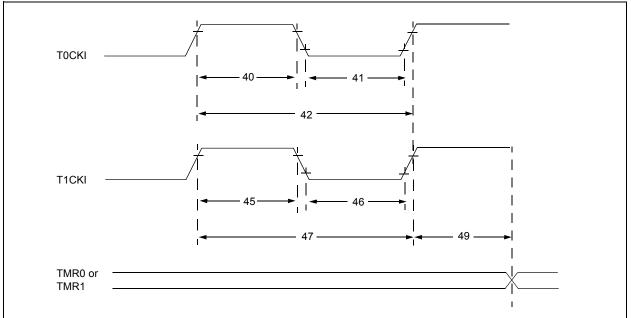

| <b>TABLE 28-12:</b> | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|---------------------|-----------------------------------------------|

|---------------------|-----------------------------------------------|

| Param.<br>No. | Sym.      |                                                      | Characterist              | Min.           | Тур†                                      | Max. | Units  | Conditions |                        |

|---------------|-----------|------------------------------------------------------|---------------------------|----------------|-------------------------------------------|------|--------|------------|------------------------|

| 40*           | T⊤0H      |                                                      |                           | No Prescaler   | 0.5 Tcy + 20                              | —    |        | ns         |                        |

|               |           |                                                      |                           | With Prescaler | 10                                        |      | _      | ns         |                        |

| 41*           | T⊤0L      | T0CKI Low Pulse Width No Prescaler With Prescale     |                           | No Prescaler   | 0.5 TCY + 20                              |      | _      | ns         |                        |

|               |           |                                                      |                           | 10             |                                           |      | ns     |            |                        |

| 42*           | Тт0Р      | T0CKI Period                                         |                           |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | _      | ns         | N = prescale value     |

| 45*           | T⊤1H      | T1CKI High<br>Time                                   | Synchronous, No Prescaler |                | 0.5 TCY + 20                              |      |        | ns         |                        |

|               |           |                                                      | Synchronous,              | with Prescaler | 15                                        |      | _      | ns         |                        |

|               |           |                                                      | Asynchronous              | i              | 30                                        | _    |        | ns         |                        |

| 46*           | TT1L      | T1CKI Low<br>Time                                    | Synchronous,              | No Prescaler   | 0.5 TCY + 20                              |      | _      | ns         |                        |

|               |           |                                                      | Synchronous,              | with Prescaler | 15                                        |      |        | ns         |                        |

|               |           |                                                      | Asynchronous              |                | 30                                        | _    | _      | ns         |                        |

| 47*           | T⊤1P      | T1CKI Input<br>Period                                | Synchronous               |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —    | _      | ns         | N = prescale value     |

|               |           |                                                      | Asynchronous              |                | 60                                        | _    | _      | ns         |                        |

| 49*           | TCKEZTMR1 | Delay from External Clock Edge to Timer<br>Increment |                           |                | 2 Tosc                                    | —    | 7 Tosc | -          | Timers in Sync<br>mode |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

### 30.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 30.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradeable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 30.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 30.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 30.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

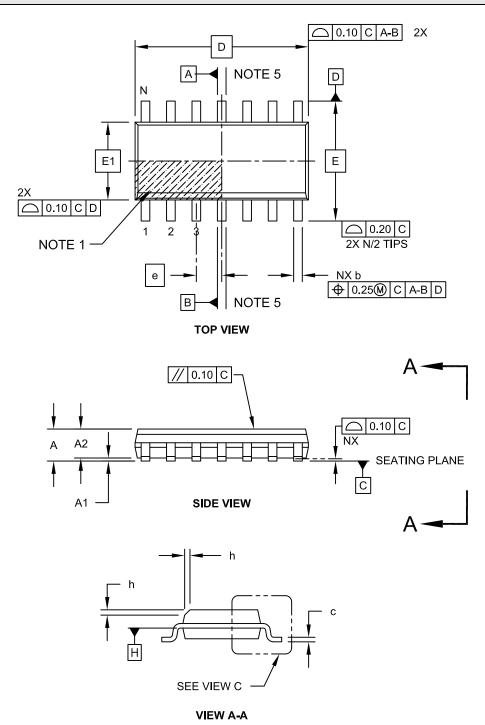

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065C Sheet 1 of 2

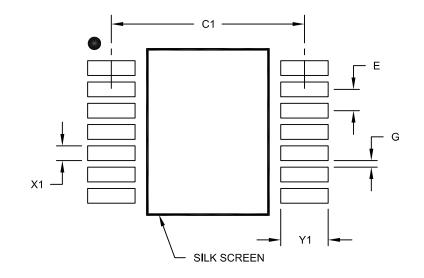

## 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |  |

|--------------------------|-------------|------|----------|------|--|

| Dimension                | MIN         | NOM  | MAX      |      |  |

| Contact Pitch            | E           |      | 0.65 BSC |      |  |

| Contact Pad Spacing      | C1          |      | 5.90     |      |  |

| Contact Pad Width (X14)  | X1          |      |          | 0.45 |  |

| Contact Pad Length (X14) | Y1          |      |          | 1.45 |  |

| Distance Between Pads    | G           | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A

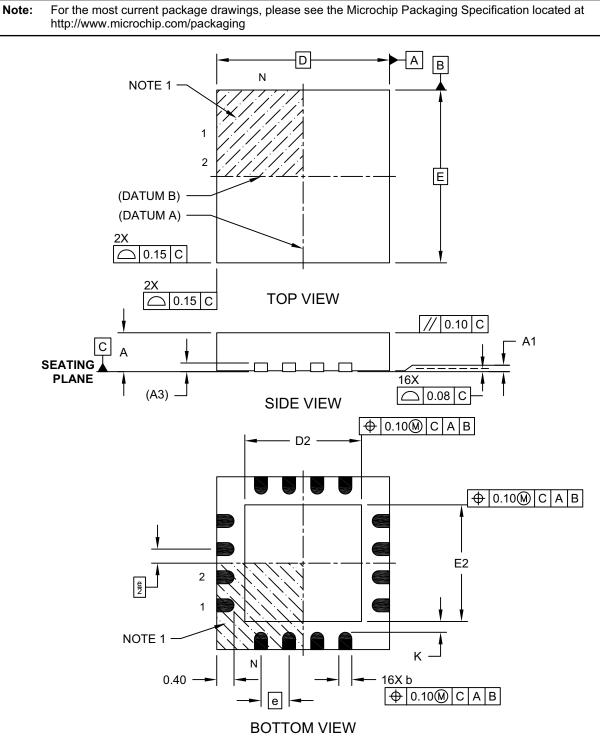

## 16-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4x0.9mm Body [QFN]

Microchip Technology Drawing C04-127D Sheet 1 of 2