Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 4x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 8-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1612-e-sn |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# REGISTER 4-3: CONFIG3: CONFIGURATION WORD 3 (CONTINUED)

bit 4-0 WDTCPS<4:0>: WDT Configuration Period Select bits

|                    |                    | WDTPS at   | POR             |                                       | 0                               |                         |

|--------------------|--------------------|------------|-----------------|---------------------------------------|---------------------------------|-------------------------|

| WDTCPS<br><4:0>    | Value              | Divider Ra | itio            | Typical<br>time out<br>(Fıℕ = 31 kHz) | Software<br>control of<br>WDTPS | _                       |

| 11111              | 01011              | 1:65536    | 2 <sup>16</sup> | 2 s                                   | Yes                             | Default<br>fuse = 11111 |

| 10011<br><br>11110 | 10011<br><br>11110 | 1:32       | 2 <sup>5</sup>  | 1 ms                                  | No                              |                         |

| 10010              | 10010              | 1:8388608  | 2 <sup>23</sup> | 256 s                                 |                                 |                         |

| 10001              | 10001              | 1:4194304  | 2 <sup>22</sup> | 128 s                                 |                                 |                         |

| 10000              | 10000              | 1:2097152  | 2 <sup>21</sup> | 64 s                                  |                                 |                         |

| 01111              | 01111              | 1:1048576  | 2 <sup>20</sup> | 32 s                                  |                                 |                         |

| 01110              | 01110              | 1:524299   | 2 <sup>19</sup> | 16 s                                  |                                 |                         |

| 01101              | 01101              | 1:262144   | 2 <sup>18</sup> | 8 s                                   |                                 |                         |

| 01100              | 01100              | 1:131072   | 2 <sup>17</sup> | 4 s                                   |                                 |                         |

| 01011              | 01011              | 1:65536    | 2 <sup>16</sup> | 2 s                                   |                                 |                         |

| 01010              | 01010              | 1:32768    | 2 <sup>15</sup> | 1 s                                   |                                 |                         |

| 01001              | 01001              | 1:16384    | 2 <sup>14</sup> | 512 ms                                | No                              |                         |

| 01000              | 01000              | 1:8192     | 2 <sup>13</sup> | 256 ms                                |                                 |                         |

| 00111              | 00111              | 1:4096     | 2 <sup>12</sup> | 128 ms                                |                                 |                         |

| 00110              | 00110              | 1:2048     | 2 <sup>11</sup> | 64 ms                                 |                                 |                         |

| 00101              | 00101              | 1:1024     | 2 <sup>10</sup> | 32 ms                                 |                                 |                         |

| 00100              | 00100              | 1:512      | 2 <sup>9</sup>  | 16 ms                                 |                                 |                         |

| 00011              | 00011              | 1:256      | 2 <sup>8</sup>  | 8 ms                                  |                                 |                         |

| 00010              | 00010              | 1:128      | 2 <sup>7</sup>  | 4 ms                                  |                                 |                         |

| 00001              | 00001              | 1:64       | 2 <sup>6</sup>  | 2 ms                                  |                                 |                         |

| 00000              | 00000              | 1:32       | 2 <sup>5</sup>  | 1 ms                                  |                                 |                         |

Note 1: A window delay of 12.5% is only available in Software Control mode via the WDTCON1 register.

| U-0            | U-0               | R/W-0/0                                                                                | R/W-0/0       | R/W-0/0                                        | R/W-0/0          | R/W-0/0  | R/W-0/0 |  |  |  |  |

|----------------|-------------------|----------------------------------------------------------------------------------------|---------------|------------------------------------------------|------------------|----------|---------|--|--|--|--|

| _              | _                 |                                                                                        |               | TUN                                            | <5:0>            |          |         |  |  |  |  |

| bit 7          |                   |                                                                                        |               |                                                |                  |          | bit 0   |  |  |  |  |

|                |                   |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

| Legend:        |                   |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

| R = Reada      | ble bit           | W = Writable                                                                           | bit           | U = Unimplen                                   | nented bit, read | d as '0' |         |  |  |  |  |

| u = Bit is ur  | nchanged          | x = Bit is unkr                                                                        | nown          | -n/n = Value at POR and BOR/Value at all other |                  |          |         |  |  |  |  |

| '1' = Bit is s | et                | '0' = Bit is clea                                                                      | ared          |                                                |                  |          |         |  |  |  |  |

|                |                   |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

| bit 7-6        | Unimpleme         | ented: Read as '                                                                       | 0'            |                                                |                  |          |         |  |  |  |  |

| bit 5-0        | TUN<5:0>:         | Frequency Tunir                                                                        | ng bits       |                                                |                  |          |         |  |  |  |  |

|                | 100000 <b>= N</b> | /linimum frequen                                                                       | су            |                                                |                  |          |         |  |  |  |  |

|                | •                 |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

|                | •                 |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

|                | •                 |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

|                |                   | 111111 =<br>000000 = Oscillator module is running at the factory-calibrated frequency. |               |                                                |                  |          |         |  |  |  |  |

|                |                   | Oscillator module                                                                      | is running at | the factory-call                               | prated frequend  | cy.      |         |  |  |  |  |

|                | 000001 =          |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

|                | •                 |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

|                | •                 |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

|                | 011110 =          |                                                                                        |               |                                                |                  |          |         |  |  |  |  |

|                | 011111 <b>= N</b> | Aaximum frequer                                                                        | ICV           |                                                |                  |          |         |  |  |  |  |

#### REGISTER 5-3: OSCTUNE: OSCILLATOR TUNING REGISTER

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7  | Bit 6 | Bit 5     | Bit 4    | Bit 3  | Bit 2  | Bit 1    | Bit 0  | Register<br>on Page |

|---------|--------|-------|-----------|----------|--------|--------|----------|--------|---------------------|

| OSCCON  | SPLLEN |       | IRCF<3:0> |          |        |        | SCS<1:0> |        | 66                  |

| OSCSTAT | _      | PLLR  | OSTS      | HFIOFR   | HFIOFL | MFIOFR | LFIOFR   | HFIOFS | 67                  |

| OSCTUNE | —      | _     |           | TUN<5:0> |        |        |          |        | 68                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### TABLE 5-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG1 | 13:8 | _       |         | _        | _        | CLKOUTEN | BORE     | N<1:0>  |         | 52                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | _        |          | _        | FOSC    | <1:0>   | 52                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

| U-0          | U-0                                    | R/W-0/0                    | R/W-0/0    | U-0            | U-0              | U-0              | U-0         |  |  |

|--------------|----------------------------------------|----------------------------|------------|----------------|------------------|------------------|-------------|--|--|

| —            | _                                      | CWGIF                      | ZCDIF      |                | —                |                  | —           |  |  |

| bit 7        |                                        |                            |            |                |                  |                  | bit 0       |  |  |

|              |                                        |                            |            |                |                  |                  |             |  |  |

| Legend:      |                                        |                            |            |                |                  |                  |             |  |  |

| R = Read     | lable bit                              | W = Writable               | bit        | U = Unimpler   | mented bit, read | as '0'           |             |  |  |

| u = Bit is   | unchanged                              | x = Bit is unkr            | nown       | -n/n = Value a | at POR and BOF   | R/Value at all o | ther Resets |  |  |

| '1' = Bit is | s set                                  | '0' = Bit is clea          | ared       |                |                  |                  |             |  |  |

|              |                                        |                            |            |                |                  |                  |             |  |  |

| bit 7-6      | Unimplemen                             | Unimplemented: Read as '0' |            |                |                  |                  |             |  |  |

| bit 5        | CWGIF: CWG                             | G Interrupt Flag           | bit        |                |                  |                  |             |  |  |

|              | 1 = Interrupt                          |                            |            |                |                  |                  |             |  |  |

|              | 0 = Interrupt                          | is not pending             |            |                |                  |                  |             |  |  |

| bit 4        |                                        | Interrupt Flag b           | it         |                |                  |                  |             |  |  |

|              | 1 = Interrupt                          |                            |            |                |                  |                  |             |  |  |

| 1.1.0.0      |                                        | is not pending             | - 1        |                |                  |                  |             |  |  |

| bit 3-0      | Unimplemen                             | ted: Read as '             | 0.         |                |                  |                  |             |  |  |

|              |                                        |                            |            |                |                  |                  |             |  |  |

| Note:        | Interrupt flag bits a                  |                            |            |                |                  |                  |             |  |  |

|              | condition occurs, r                    |                            |            |                |                  |                  |             |  |  |

|              | its corresponding<br>Enable bit, GIE o |                            |            |                |                  |                  |             |  |  |

|              | User software                          |                            | 0          |                |                  |                  |             |  |  |

|              | appropriate interru                    | pt flag bits are c         | lear prior |                |                  |                  |             |  |  |

|              | to enabling an inte                    | rrupt.                     |            |                |                  |                  |             |  |  |

|              |                                        |                            |            |                |                  |                  |             |  |  |

# REGISTER 7-8: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

#### REGISTER 11-12: SCANLADRH: SCAN LOW ADDRESS HIGH BYTE REGISTER

| R/W-0/0                                                                  | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                                       | R/W-0/0 | R/W-0/0 | R/W-0/0     |

|--------------------------------------------------------------------------|---------|-------------------|---------|-----------------------------------------------|---------|---------|-------------|

|                                                                          |         |                   | LADR<   | 15:8> <b>(1, 2)</b>                           |         |         |             |

| bit 7                                                                    |         |                   |         |                                               |         |         | bit 0       |

| -                                                                        |         |                   |         |                                               |         |         |             |

| Legend:                                                                  |         |                   |         |                                               |         |         |             |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |         |                   |         | l as '0'                                      |         |         |             |

| u = Bit is uncha                                                         | anged   | x = Bit is unkr   | nown    | wn -n/n = Value at POR and BOR/Value at all o |         |         | ther Resets |

| '1' = Bit is set                                                         |         | '0' = Bit is clea | ared    |                                               |         |         |             |

bit 7-0 LADR<15:8>: Scan Start/Current Address bits<sup>(1, 2)</sup> Most Significant bits of the current address to be fetched from, value increments on each fetch of memory.

- **Note 1:** Registers SCANLADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 11-13: SCANLADRL: SCAN LOW ADDRESS LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|--------------------|---------|---------|---------|

|         |         |         | LADR<   | 7:0> <b>(1, 2)</b> |         |         |         |

| bit 7   |         |         |         |                    |         |         | bit 0   |

|         |         |         |         |                    |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LADR<7:0>: Scan Start/Current Address bits<sup>(1, 2)</sup>

Least Significant bits of the current address to be fetched from, value increments on each fetch of memory

- **Note 1:** Registers SCANLADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

## 12.4 Register Definitions: PORTA

#### REGISTER 12-2: PORTA: PORTA REGISTER

| U-0                                                                                | U-0 | R/W-x/x           | R/W-x/x | R-x/x       | R/W-x/x          | R/W-x/x | R/W-x/x |

|------------------------------------------------------------------------------------|-----|-------------------|---------|-------------|------------------|---------|---------|

| _                                                                                  | _   | RA5               | RA4     | RA3         | RA2              | RA1     | RA0     |

| bit 7                                                                              |     |                   |         |             |                  |         | bit 0   |

|                                                                                    |     |                   |         |             |                  |         |         |

| Legend:                                                                            |     |                   |         |             |                  |         |         |

| R = Readable b                                                                     | bit | W = Writable      | bit     | U = Unimple | mented bit, read | as '0'  |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all o |     |                   |         | ther Resets |                  |         |         |

| '1' = Bit is set                                                                   |     | '0' = Bit is clea | ared    |             |                  |         |         |

| bit 7-6 | Unimplemented: Read as '0'                   |

|---------|----------------------------------------------|

| bit 5-0 | RA<5:0>: PORTA I/O Value bits <sup>(1)</sup> |

|         | 1 = Port pin is <u>&gt;</u> Vін              |

|         | 0 = Port pin is <u>&lt;</u> VIL              |

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 12-3: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | —   | TRISA5  | TRISA4  | (1) | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>TRISA&lt;5:4&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

| bit 3   | Unimplemented: Read as '1'                                                                                                                         |

| bit 2-0 | <b>TRISA&lt;2:0&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

Note 1: Unimplemented, read as '1'.

-n/n = Value at POR and BOR/Value at all other Resets

| R = Readable bit W = Writable bit |     |         | U = Unimplemented bit, read as '0' |         |         |         |         |

|-----------------------------------|-----|---------|------------------------------------|---------|---------|---------|---------|

| Legend:                           |     |         |                                    |         |         |         |         |

| bit 7                             |     |         |                                    |         |         |         | bit 0   |

| —                                 | —   | WPUC5   | WPUC4                              | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| U-0                               | U-0 | R/W-1/1 | R/W-1/1                            | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

# **REGISTER 12-14: WPUC: WEAK PULL-UP PORTC REGISTER**<sup>(1),(2)</sup>

x = Bit is unknown

'0' = Bit is cleared

| bit 7-6 | Unimplemented: Read as '0'            |

|---------|---------------------------------------|

| bit 5-0 | WPUC<5:0>: Weak Pull-up Register bits |

|         | 1 = Pull-up enabled                   |

|         | 0 = Pull-up disabled                  |

u = Bit is unchanged

'1' = Bit is set

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

#### REGISTER 12-15: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0 **ODC<5:0>:** PORTC Open Drain Enable bits

For RC<5:0> pins, respectively

- 1 = Port pin operates as open-drain drive (sink current only)

- 0 = Port pin operates as standard push-pull drive (source and sink current)

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

#### IOCCP: INTERRUPT-ON-CHANGE PORTC POSITIVE EDGE REGISTER<sup>(1)</sup> **REGISTER 13-4:**

| bit 7<br>Legend:<br>R = Readable bit | W = Writable bit |         | U = Unimpleme | nted bit, read as '0 | )'      |         |

|--------------------------------------|------------------|---------|---------------|----------------------|---------|---------|

|                                      |                  |         |               |                      |         |         |

| <br>bit 7                            |                  |         |               |                      |         |         |

|                                      |                  |         |               |                      |         | bit 0   |

|                                      | IOCCP5           | IOCCP4  | IOCCP3        | IOCCP2               | IOCCP1  | IOCCP0  |

| U-0 U-0                              | R/W-0/0          | R/W-0/0 | R/W-0/0       | R/W-0/0              | R/W-0/0 | R/W-0/0 |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-0 | IOC <sub>C</sub> P<5:0>: Interrupt-on-Change PORTC Positive Edge Enable bits                                                        |

|         | 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge. |

|         | _ = Interrupt-on-Change disabled for the associated pin.                                                                            |

#### Note 1: PIC16(L)F1613 only.

'1' = Bit is set

#### IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER<sup>(1)</sup> REGISTER 13-5:

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOC<sub>C</sub>N<5:0>: Interrupt-on-Change PORTC Negative Edge Enable bits

1 = 1 Interrupt-on-Change enabled on the pin for a negative going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

$_0$  = Interrupt-on-Change disabled for the associated pin.

'0' = Bit is cleared

Note 1: PIC16(L)F1613 only.

bit 5-0

bit 5-0

#### IOCCF: INTERRUPT-ON-CHANGE PORTC FLAG REGISTER<sup>(1)</sup> **REGISTER 13-6:**

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCCF5     | IOCCF4     | IOCCF3     | IOCCF2     | IOCCF1     | IOCCF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOC<sub>C</sub>F<5:0>: Interrupt-on-Change PORTC Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx.  $_{0}$  = No change was detected, or the user cleared the detected change.

Note 1: PIC16(L)F1613 only.

| Name                 | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------------------|-------|-------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELA               | —     | _     | _      | ANSA4  | —      | ANSA2  | ANSA1  | ANSA0  | 136                 |

| INTCON               | GIE   | PEIE  | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 82                  |

| IOCAF                | _     | -     | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 148                 |

| IOCAN                | —     | _     | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 148                 |

| IOCAP                | _     | -     | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 148                 |

| IOCCF <sup>(2)</sup> | —     | _     | IOCCF5 | IOCCF4 | IOCCF3 | IOCCF2 | IOCCF1 | IOCCF0 | 149                 |

| IOCCN <sup>(2)</sup> | _     | -     | IOCCN5 | IOCCN4 | IOCCN3 | IOCCN2 | IOCCN1 | IOCCN0 | 149                 |

| IOCCP <sup>(2)</sup> | —     | _     | IOCCP5 | IOCCP4 | IOCCP3 | IOCCP2 | IOCCP1 | IOCCP0 | 149                 |

| TRISA                | _     | _     | TRISA5 | TRISA4 | —(1)   | TRISA2 | TRISA1 | TRISA0 | 135                 |

| TRISC <sup>(2)</sup> | —     | _     | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 142                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

Note 1: Unimplemented, read as '1'.

2: only.

# 19.9 Register Definitions: ZCD Control

| R/W-q/q          | R/W-0/0                                                    | R-x/x                                                             | R/W-0/0        | U-0              | U-0             | R/W-0/0                          | R/W-0/0     |  |  |  |  |

|------------------|------------------------------------------------------------|-------------------------------------------------------------------|----------------|------------------|-----------------|----------------------------------|-------------|--|--|--|--|

| ZCDxEN           | ZCDxOE                                                     | ZCDxOUT                                                           | ZCDxPOL        |                  | _               | ZCDxINTP                         | ZCDxINTN    |  |  |  |  |

| bit 7            |                                                            |                                                                   |                |                  |                 |                                  | bit         |  |  |  |  |

|                  |                                                            |                                                                   |                |                  |                 |                                  |             |  |  |  |  |

| Legend:          |                                                            |                                                                   |                |                  |                 |                                  |             |  |  |  |  |

| R = Readable     |                                                            | W = Writable                                                      |                |                  | mented bit, rea |                                  |             |  |  |  |  |

| u = Bit is unc   | 0                                                          | x = Bit is unkr                                                   |                |                  |                 | OR/Value at all o                | ther Resets |  |  |  |  |

| '1' = Bit is set | t                                                          | '0' = Bit is clea                                                 | ared           | q = value dep    | pends on confi  | guration bits                    |             |  |  |  |  |

| bit 7            | ZCDxEN: Zei                                                | ro-Cross Detec                                                    | tion Enable bi | t                |                 |                                  |             |  |  |  |  |

|                  |                                                            | ss detect is ena<br>ss detect is dis                              |                |                  |                 | e and sink currer<br>S controls. | nt.         |  |  |  |  |

| bit 6            | ZCDxOE: Ze                                                 | <b>ZCDxOE:</b> Zero-Cross Detection Output Enable bit             |                |                  |                 |                                  |             |  |  |  |  |

|                  | 1 = ZCD pin output is enabled                              |                                                                   |                |                  |                 |                                  |             |  |  |  |  |

|                  | •                                                          | 0 = ZCD pin output is disabled                                    |                |                  |                 |                                  |             |  |  |  |  |

| bit 5            |                                                            | <b>ZCDxOUT:</b> Zero-Cross Detection Logic Level bit              |                |                  |                 |                                  |             |  |  |  |  |

|                  | $\frac{\text{ZCDxPOL bit} = 0}{2000}$                      |                                                                   |                |                  |                 |                                  |             |  |  |  |  |

|                  |                                                            | 1 = ZCD pin is sinking current<br>0 = ZCD pin is sourcing current |                |                  |                 |                                  |             |  |  |  |  |

|                  | -                                                          | 0 = 2CD pin is sourcing current<br>ZCDxPOL bit = 1:               |                |                  |                 |                                  |             |  |  |  |  |

|                  | 1 = ZCD pin is sourcing current                            |                                                                   |                |                  |                 |                                  |             |  |  |  |  |

|                  | 0 = ZCD pin                                                | 0 = ZCD pin is sinking current                                    |                |                  |                 |                                  |             |  |  |  |  |

| bit 4            | ZCDxPOL: Z                                                 | ero-Cross Dete                                                    | ection Logic O | utput Polarity b | oit             |                                  |             |  |  |  |  |

|                  |                                                            | 1 = ZCD logic output is inverted                                  |                |                  |                 |                                  |             |  |  |  |  |

|                  | C C                                                        | c output is not                                                   |                |                  |                 |                                  |             |  |  |  |  |

| bit 3-2          | Unimplemented: Read as '0'                                 |                                                                   |                |                  |                 |                                  |             |  |  |  |  |

| bit 1            |                                                            | ZCDxINTP: Zero-Cross Positive Edge Interrupt Enable bit           |                |                  |                 |                                  |             |  |  |  |  |

|                  | 1 = ZCDIF bit is set on low-to-high ZCDx_output transition |                                                                   |                |                  |                 |                                  |             |  |  |  |  |

|                  |                                                            | it is unaffected                                                  |                |                  |                 |                                  |             |  |  |  |  |

| bit 0            |                                                            | Zero-Cross Neg                                                    | -              | -                |                 |                                  |             |  |  |  |  |

|                  |                                                            | it is set on high                                                 |                |                  |                 |                                  |             |  |  |  |  |

|                  | $0 = \angle CDIF b$                                        | it is unaffected                                                  | by high-to-low | / ZCDx_output    | transition      |                                  |             |  |  |  |  |

#### REGISTER 19-1: ZCDxCON: ZERO-CROSS DETECTION CONTROL REGISTER

#### TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

| Name    | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1    | Bit 0    | Register<br>on page |

|---------|--------|--------|---------|---------|-------|-------|----------|----------|---------------------|

| PIE3    | _      |        | CWGIE   | ZCDIE   | _     |       |          | _        | 85                  |

| PIR3    | _      | _      | CWGIF   | ZCDIF   | _     | _     | _        | _        | 89                  |

| ZCD1CON | ZCD1EN | ZCD10E | ZCD10UT | ZCD1POL | _     | _     | ZCD1INTP | ZCD1INTN | 186                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### 23.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section21.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 23.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (MODE<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

#### 23.2.4 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 23.2.5 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section12.1** "Alternate Pin Function" for more information.

#### 23.2.6 CAPTURE OUTPUT

When in Compare mode, the CCP will provide an output upon the 16-bit value of the CCPRxH:CCPRxL register pair matching the TMR1H:TMR1L register pair. The compare output depends on which Compare mode the CCP is configured as. If the MODE bits of CCPxCON register are equal to '1011' or '1010', the CCP module will output high, while TMR1 is equal to CCPRxH:CCPRxL register pair. This means that the pulse width is determined by the TMR1 prescaler. If the MODE bits of CCPxCON are equal to '0001' or '0010', the output will toggle upon a match, going from '0' to '1' or vice-versa. If the MODE bits of CCPxCON are equal to '1001', the output is cleared on a match, and if the MODE bits are equal to '1000', the output is set on a match. This output is available as an input signal to the CWG, as an auto-conversion trigger for the ADC, as an external Reset signal for the TMR2 modules, as a window input to the SMT, and as an input to the CLC module.

# 23.4 CCP/PWM Clock Selection

The PIC12(L)F1612/16(L)F1613 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

As there are up to three 8-bit timers with auto-reload (Timer2/4/6), PWM mode on the CCP and PWM modules can use any of these timers.

The CCPTMRS register is used to select which timer is used.

# 23.4.1 USING THE TMR2/4/6 WITH THE CCP MODULE

This device has a new version of the TMR2 module that has many new modes, which allow for greater customization and control of the PWM signals than older parts. Refer to **Section23.5 "Operation Examples"** for examples of PWM signal generation using the different modes of Timer2. The CCP operation requires that the timer used as the PWM time base has the Fosc/4 clock source selected.

#### 23.4.2 PWM PERIOD

The PWM period is specified by the PR2/4/6 register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 23-1.

## EQUATION 23-1: PWM PERIOD

$$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$$

(TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When TMR2/4/6 is equal to its respective PR2/4/6 register, the following three events occur on the next increment cycle:

- TMR2/4/6 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from the CCPRxH:CCPRxL pair into the internal 10-bit latch.

| Note: | The Timer postscaler (see Figure ) is not |

|-------|-------------------------------------------|

|       | used in the determination of the PWM      |

|       | frequency.                                |

## 23.4.3 PWM DUTY CYCLE

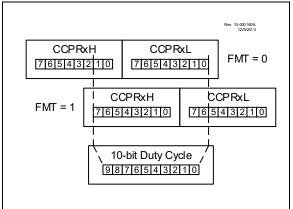

The PWM duty cycle is specified by writing a 10-bit value to two registers: the CCPRxH:CCPRxL register pair. Where the particular bits go is determined by the FMT bit of the CCPxCON register. If FMT = 0, the two Most Significant bits of the duty cycle value should be written to bits <1:0> of CCPRxH register and the remaining eight bits to the CCPRxL register. If FMT = 1, the Least Significant two bits of the duty cycle should be written to bits <7:6> of the CCPRxL register and the Most Significant eight bits to the CCPRxH register. This is illustrated in Figure 23-4. These bits can be written at any time. The duty cycle value is not latched into the internal latch until after the period completes (i.e., a match between PR2/4/6 and TMR2/4/6 registers occurs).

Equation 23-2 is used to calculate the PWM pulse width. Equation 23-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 23-2: PULSE WIDTH

• (TMR2 Prescale Value)

#### EQUATION 23-3: DUTY CYCLE RATIO

Duty Cycle Ratio =

$$\frac{(CCPRxH:CCPRxL)}{4(PRx+1)}$$

The PWM duty cycle registers are double buffered for glitchless PWM operation.

The 8-bit timer TMR2/4/6 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the internal buffer register, then the CCPx pin is cleared (see Figure ).

#### FIGURE 23-4: CCPx DUTY-CYCLE ALIGNMENT

## 23.4.4 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

© 2014-2017 Microchip Technology Inc.

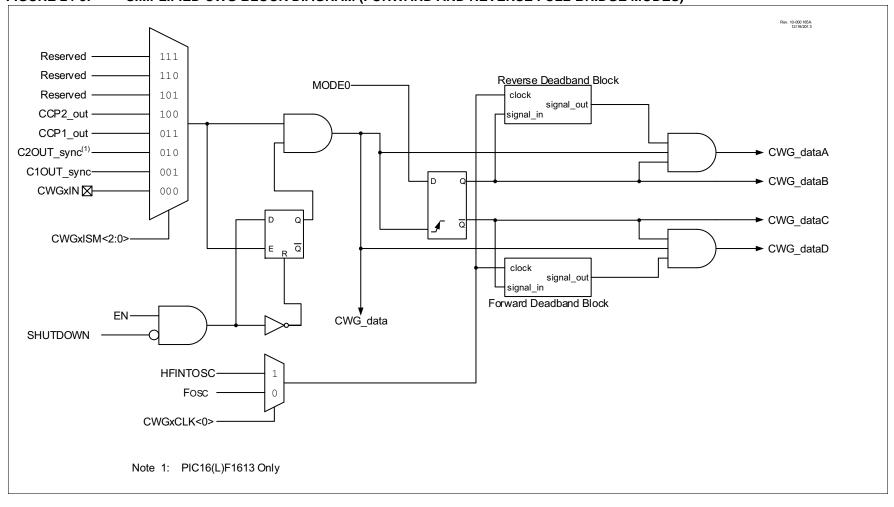

#### FIGURE 24-3: SIMPLIFIED CWG BLOCK DIAGRAM (FORWARD AND REVERSE FULL-BRIDGE MODES)

PIC12(L)F1612/16(L)F1613

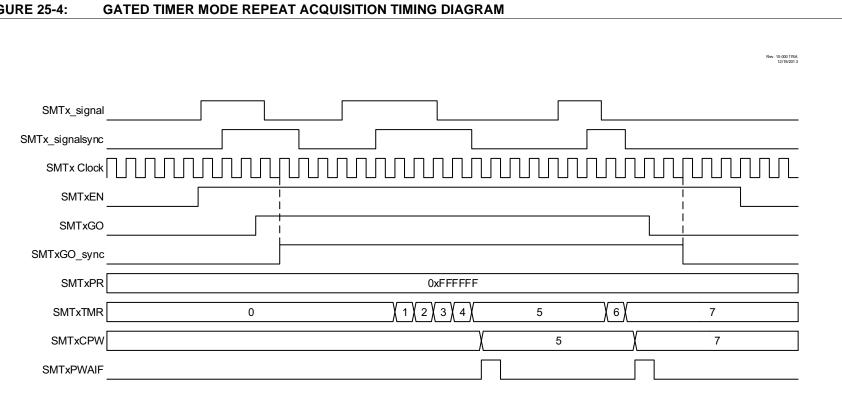

# 25.0 SIGNAL MEASUREMENT TIMER (SMT)

The SMT is a 24-bit counter with advanced clock and gating logic, which can be configured for measuring a variety of digital signal parameters such as pulse width, frequency and duty cycle, and the time difference between edges on two signals.

Features of the SMT include:

- · 24-bit timer/counter

- Four 8-bit registers (SMTxTMRL/H/U)

- Readable and writable

- Optional 16-bit operating mode

- Two 24-bit measurement capture registers

- One 24-bit period match register

- Multi-mode operation, including relative timing measurement

- Interrupt on period match

- Multiple clock, gate and signal sources

- Interrupt on acquisition complete

- · Ability to read current input values

Note: These devices implement two SMT modules. All references to SMTx apply to SMT1 and SMT2.

# FIGURE 25-4:

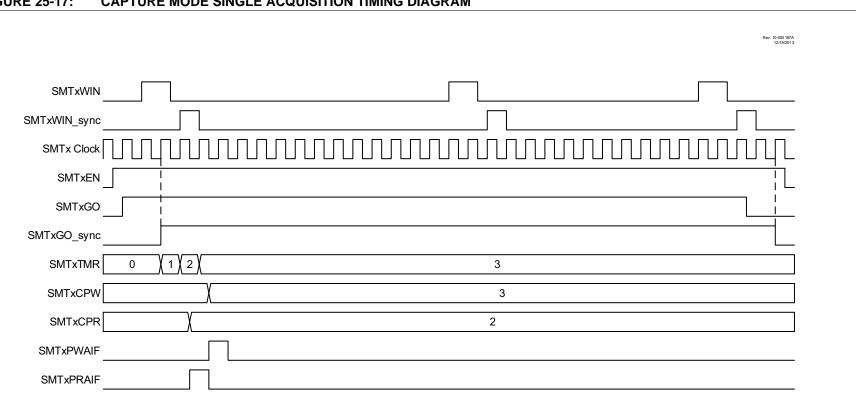

#### FIGURE 25-17: CAPTURE MODE SINGLE ACQUISITION TIMING DIAGRAM

PIC12(L)F1612/16(L)F1613

#### TABLE 28-14: ADC CONVERSION REQUIREMENTS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                                    |      |                           |      |       |                                              |  |  |

|---------------|---------------------------------------------------------|--------------------------------------------------------------------|------|---------------------------|------|-------|----------------------------------------------|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                                                     | Min. | Тур†                      | Max. | Units | Conditions                                   |  |  |

| AD130*        | TAD                                                     | ADC Clock Period (TADC)                                            | 1.0  | —                         | 6.0  | μS    | Fosc-based                                   |  |  |

|               |                                                         | ADC Internal FRC Oscillator Period (TFRC)                          | 1.0  | 2.0                       | 6.0  | μS    | ADCS<2:0> = x11 (ADC FRC mode)               |  |  |

| AD131         | TCNV                                                    | Conversion Time<br>(not including Acquisition Time) <sup>(1)</sup> | —    | 11                        | —    | Tad   | Set GO/DONE bit to conversion complete       |  |  |

| AD132*        | TACQ                                                    | Acquisition Time                                                   | -    | 5.0                       |      | μS    |                                              |  |  |

| AD133*        | Тнср                                                    | Holding Capacitor Disconnect Time                                  |      | 1/2 TAD<br>1/2 TAD + 1TCY | _    |       | Fosc-based<br>ADCS<2:0> = x11 (ADC FRC mode) |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.

# TABLE 28-15: COMPARATOR SPECIFICATIONS<sup>(1)</sup>

# Operating Conditions (unless otherwise stated)

| Param.<br>No. | Sym.                 | Characteristics                           | Min. | Тур. | Max. | Units | Comments                  |

|---------------|----------------------|-------------------------------------------|------|------|------|-------|---------------------------|

| CM01          | Vioff                | Input Offset Voltage                      |      | ±7.5 | ±60  | mV    | CxSP = 1,<br>Vicm = VDD/2 |

| CM02          | Vicm                 | Input Common Mode Voltage                 | 0    | —    | VDD  | V     |                           |

| CM03          | CMRR                 | Common Mode Rejection Ratio               | _    | 50   | _    | dB    |                           |

| CM04A         |                      | Response Time Rising Edge                 | _    | 400  | 800  | ns    | CxSP = 1                  |

| CM04B         | Tresp <sup>(2)</sup> | Response Time Falling Edge                |      | 200  | 400  | ns    | CxSP = 1                  |

| CM04C         | - Tresp/             | Response Time Rising Edge                 | _    | 1200 | _    | ns    | CxSP = 0                  |

| CM04D         |                      | Response Time Falling Edge                | _    | 550  |      | ns    | CxSP = 0                  |

| CM05*         | Tmc2ov               | Comparator Mode Change to<br>Output Valid | _    | —    | 10   | μS    |                           |

| CM06          | CHYSTER              | Comparator Hysteresis                     | _    | 25   |      | mV    | CxHYS = 1,<br>CxSP = 1    |

\* These parameters are characterized but not tested.

Note 1: See Section 29.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

2: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

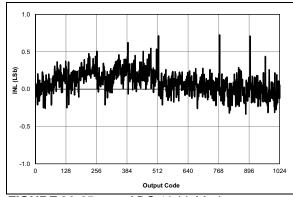

**FIGURE 29-65:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu$ S,  $25^{\circ}$ C.

**FIGURE 29-66:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $4 \mu$ S,  $25^{\circ}$ C.

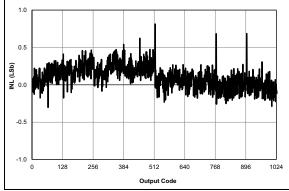

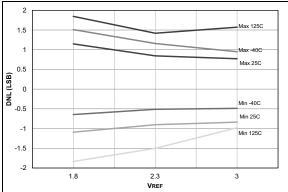

FIGURE 29-67: ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V, VREF = 3.0V.

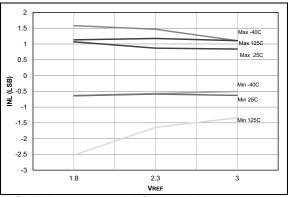

FIGURE 29-68: ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, VREF = 3.0V.

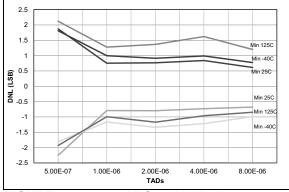

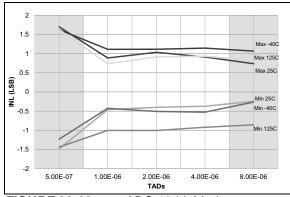

**FIGURE 29-69:** ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V, TAD =  $1 \mu$ S.

**FIGURE 29-70:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu$ S.

# 30.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 30.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

#### 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# 31.0 PACKAGING INFORMATION

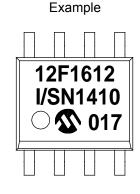

# 31.1 Package Marking Information

8-Lead PDIP (300 mil)

8-Lead SOIC (3.90 mm)

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>(©3)<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                                 | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                                         |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.