Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                   |

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 65                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                               |

| Data Converters            | A/D 8x12b; D/A 1x12b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 81-UFBGA, CSPBGA                                                           |

| Supplier Device Package    | 81-CSP (4.35x4.27)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32lg360f128g-e-csp81r |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.1.4 Direct Memory Access Controller (DMA)

The Direct Memory Access (DMA) controller performs memory operations independently of the CPU. This has the benefit of reducing the energy consumption and the workload of the CPU, and enables the system to stay in low energy modes when moving for instance data from the USART to RAM or from the External Bus Interface to a PWM-generating timer. The DMA controller uses the PL230 µDMA controller licensed from ARM.

### 3.1.5 Reset Management Unit (RMU)

The RMU is responsible for handling the reset functionality of the EFM32LG.

### 3.1.6 Energy Management Unit (EMU)

The Energy Management Unit (EMU) manage all the low energy modes (EM) in EFM32LG microcontrollers. Each energy mode manages if the CPU and the various peripherals are available. The EMU can also be used to turn off the power to unused SRAM blocks.

### 3.1.7 Clock Management Unit (CMU)

The Clock Management Unit (CMU) is responsible for controlling the oscillators and clocks on-board the EFM32LG. The CMU provides the capability to turn on and off the clock on an individual basis to all peripheral modules in addition to enable/disable and configure the available oscillators. The high degree of flexibility enables software to minimize energy consumption in any specific application by not wasting power on peripherals and oscillators that are inactive.

### 3.1.8 Watchdog (WDOG)

The purpose of the watchdog timer is to generate a reset in case of a system failure, to increase application reliability. The failure may e.g. be caused by an external event, such as an ESD pulse, or by a software failure.

### 3.1.9 Peripheral Reflex System (PRS)

The Peripheral Reflex System (PRS) system is a network which lets the different peripheral module communicate directly with each other without involving the CPU. Peripheral modules which send out Reflex signals are called producers. The PRS routes these reflex signals to consumer peripherals which apply actions depending on the data received. The format for the Reflex signals is not given, but edge triggers and other functionality can be applied by the PRS.

#### 3.1.10 External Bus Interface (EBI)

The External Bus Interface provides access to external parallel interface devices such as SRAM, FLASH, ADCs and LCDs. The interface is memory mapped into the address bus of the Cortex-M3. This enables seamless access from software without manually manipulating the IO settings each time a read or write is performed. The data and address lines are multiplexed in order to reduce the number of pins required to interface the external devices. The timing is adjustable to meet specifications of the external devices. The interface is limited to asynchronous devices.

#### 3.1.11 TFT Direct Drive

The EBI contains a TFT controller which can drive a TFT via a 565 RGB interface. The TFT controller supports programmable display and port sizes and offers accurate control of frequency and setup and hold timing. Direct Drive is supported for TFT displays which do not have their own frame buffer. In that case TFT Direct Drive can transfer data from either on-chip memory or from an external memory device to the TFT at low CPU load. Automatic alpha-blending and masking is also supported for transfers through the EBI interface.

#### 3.1.12 Universal Serial Bus Controller (USB)

The USB is a full-speed USB 2.0 compliant OTG host/device controller. The USB can be used in Device, On-the-go (OTG) Dual Role Device or Host-only configuration. In OTG mode the USB supports both Host Negotiation Protocol (HNP) and Session Request Protocol (SRP). The device supports both fullspeed (12MBit/s) and low speed (1.5MBit/s) operation. The USB device includes an internal dedicated Descriptor-Based Scatter/Gather DMA and supports up to 6 OUT endpoints and 6 IN endpoints, in addition to endpoint 0. The on-chip PHY includes all OTG features, except for the voltage booster for supplying 5V to VBUS when operating as host.

| Module | Configuration      | Pin Connections                                                   |

|--------|--------------------|-------------------------------------------------------------------|

| ACMP1  | Full configuration | ACMP1_CH[7:0], ACMP1_O                                            |

| VCMP   | Full configuration | NA                                                                |

| ADC0   | Full configuration | ADC0_CH[7:0]                                                      |

| DAC0   | Full configuration | DAC0_OUT[1:0], DAC0_OUTxALT                                       |

| OPAMP  | Full configuration | Outputs: OPAMP_OUTx, OPAMP_OUTxALT, Inputs: OPAMP_Px,<br>OPAMP_Nx |

| AES    | Full configuration | NA                                                                |

| GPIO   | 83 pins            | Available pins are shown in 5.9.3 GPIO Pinout Overview            |

| Module | Configuration      | Pin Connections                                                  |

|--------|--------------------|------------------------------------------------------------------|

| AES    | Full configuration | NA                                                               |

| GPIO   | 56 pins            | Available pins are shown in 5.12.3 GPIO Pinout Overview          |

| LCD    | Full configuration | LCD_SEG[19:0], LCD_COM[7:0], LCD_BCAP_P, LCD_BCAP_N,<br>LCD_BEXT |

| Module | Configuration      | Pin Connections                                                   |

|--------|--------------------|-------------------------------------------------------------------|

| ACMP1  | Full configuration | ACMP1_CH[7:0], ACMP1_O                                            |

| VCMP   | Full configuration | NA                                                                |

| ADC0   | Full configuration | ADC0_CH[7:0]                                                      |

| DAC0   | Full configuration | DAC0_OUT[1:0], DAC0_OUTxALT                                       |

| OPAMP  | Full configuration | Outputs: OPAMP_OUTx, OPAMP_OUTxALT, Inputs: OPAMP_Px,<br>OPAMP_Nx |

| AES    | Full configuration | NA                                                                |

| GPIO   | 81 pins            | Available pins are shown in 5.20.3 GPIO Pinout Overview           |

| LCD    | Full configuration | LCD_SEG[33:0], LCD_COM[7:0], LCD_BCAP_P, LCD_BCAP_N,<br>LCD_BEXT  |

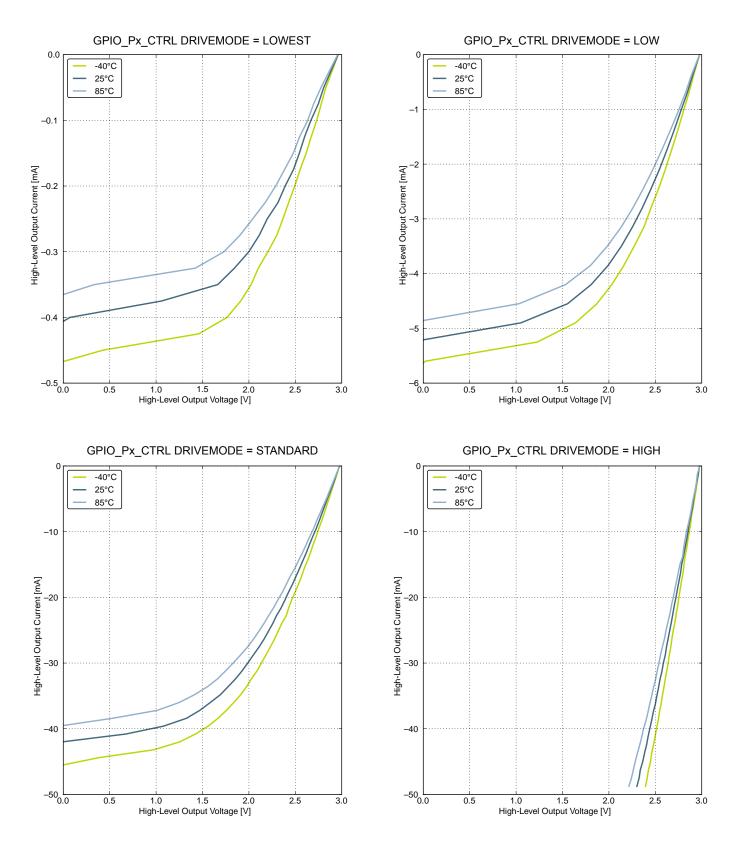

Figure 4.13. Typical High-Level Output Current, 3 V Supply Voltage

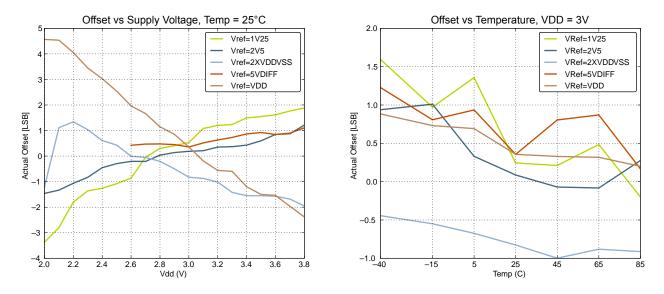

Figure 4.28. ADC Absolute Offset, Common Mode = VDD/2

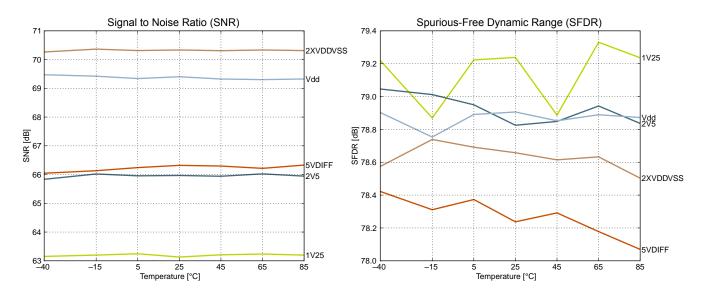

Figure 4.29. ADC Dynamic Performance vs Temperature for all ADC References, VDD = 3 V

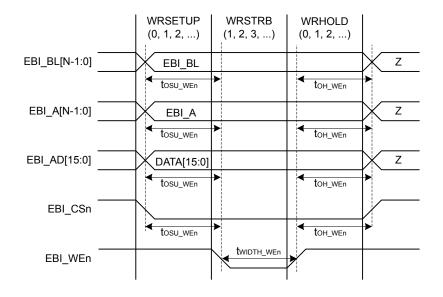

Figure 4.37. EBI Write Enable Timing

| Table 4.19. | EBI Write | Enable | Timing |

|-------------|-----------|--------|--------|

|-------------|-----------|--------|--------|

| Parameter                                                                                               | Symbol                                 | Min                                              | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------|-----|-----|------|

| Output hold time, from trailing EBI_WEn/EBI_NAND-WEn edge to EBI_AD, EBI_A, EBI_CSn, EBI_BLn invalid    | t <sub>OH_WEn</sub> <sup>1 2 3 4</sup> | -6.00 + (WRHOLD × t <sub>HFCORECLK</sub> )       | _   | _   | ns   |

| Output setup time, from EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn valid to leading EBI_WEn/EBI_NANDWEn<br>edge | t <sub>OSU_WEn</sub> 12345             | -14.00 + (WRSETUP × t <sub>HFCORECLK</sub> )     | _   | _   | ns   |

| EBI_WEn/EBI_NANDWEn pulse width                                                                         | twiDTH_WEn <sup>1 2 3 4</sup><br>5     | -7.00 + ((WRSTRB + 1) × t <sub>HFCORECLK</sub> ) |     | _   | ns   |

Note:

1. Applies for all addressing modes (figure only shows D16 addressing mode)

2. Applies for both EBI\_WEn and EBI\_NANWEn (figure only shows EBI\_WEn)

3. Applies for all polarities (figure only shows active low signals)

4. Measurement done at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $V_{\text{DD}})$

5. The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFWE=0. The leading edge of EBI\_WEn can be moved to the right by setting HALFWE=1. This decreases the length of  $t_{WIDTH_WEn}$  and increases the length of  $t_{OSU_WEn}$  by 1/2 ×  $t_{HFCLKNODIV}$ .

# Table 4.24. LCD

| Parameter                         | Symbol             | Test Condition                                                                                                                         | Min | Тур  | Мах | Unit |

|-----------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Frame rate                        | f <sub>LCDFR</sub> |                                                                                                                                        | 30  | _    | 200 | Hz   |

| Number of segments supported      | NUM <sub>SEG</sub> |                                                                                                                                        | _   | 36×8 | _   | seg  |

| LCD supply voltage range          | V <sub>LCD</sub>   | Internal boost circuit enabled                                                                                                         | 2.0 | —    | 3.8 | V    |

| Steady state current consumption. | I <sub>LCD</sub>   | Display disconnected, static<br>mode, framerate 32 Hz, all<br>segments on.                                                             | _   | 250  | _   | nA   |

|                                   |                    | Display disconnected, quad-<br>ruplex mode, framerate 32<br>Hz, all segments on, bias<br>mode to ONETHIRD in<br>LCD_DISPCTRL register. |     | 550  |     | nA   |

| Steady state Current contribution | ILCDBOOST          | Internal voltage boost off                                                                                                             | _   | 0    | _   | μA   |

| of internal boost.                |                    | Internal voltage boost on,<br>boosting from 2.2 V to 3.0 V.                                                                            | —   | 8.4  | _   | μA   |

| Boost Voltage                     | V <sub>BOOST</sub> | VBLEV of LCD_DISPCTRL register to LEVEL0                                                                                               | —   | 3.02 | _   | V    |

|                                   |                    | VBLEV of LCD_DISPCTRL register to LEVEL1                                                                                               |     | 3.15 |     | V    |

|                                   |                    | VBLEV of LCD_DISPCTRL register to LEVEL2                                                                                               | _   | 3.28 | _   | V    |

|                                   |                    | VBLEV of LCD_DISPCTRL register to LEVEL3                                                                                               | _   | 3.41 |     | V    |

|                                   |                    | VBLEV of LCD_DISPCTRL register to LEVEL4                                                                                               |     | 3.54 |     | V    |

|                                   |                    | VBLEV of LCD_DISPCTRL register to LEVEL5                                                                                               |     | 3.67 |     | V    |

|                                   |                    | VBLEV of LCD_DISPCTRL register to LEVEL6                                                                                               |     | 3.73 | _   | V    |

|                                   |                    | VBLEV of LCD_DISPCTRL register to LEVEL7                                                                                               | _   | 3.74 | —   | V    |

The total LCD current is given by the following equation.  $I_{LCDBOOST}$  is zero if internal boost is off.

$I_{LCDTOTAL} = I_{LCD} + I_{LCDBOOST}$

| QFP64 Pin# and Name Pin Alternate Functionality / Description |          |                                                           |                                                    |                                                         |                             |  |  |  |

|---------------------------------------------------------------|----------|-----------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------|-----------------------------|--|--|--|

| Pin #                                                         | Pin Name | Analog                                                    | Timers                                             | Communication                                           | Other                       |  |  |  |

| 3                                                             | PA2      |                                                           | TIM0_CC2 #0/1                                      |                                                         | CMU_CLK0 #0<br>ETM_TD0 #3   |  |  |  |

| 4                                                             | PA3      |                                                           | TIM0_CDTI0 #0                                      |                                                         | LES_ALTEX2 #0<br>ETM_TD1 #3 |  |  |  |

| 5                                                             | PA4      |                                                           | TIM0_CDTI1 #0                                      |                                                         | LES_ALTEX3 #0<br>ETM_TD2 #3 |  |  |  |

| 6                                                             | PA5      |                                                           | TIM0_CDTI2 #0                                      | LEU1_TX #1                                              | LES_ALTEX4 #0<br>ETM_TD3 #3 |  |  |  |

| 7                                                             | IOVDD_0  | Digital IO power supply 0.                                |                                                    |                                                         |                             |  |  |  |

| 8                                                             | VSS      | Ground.                                                   |                                                    |                                                         |                             |  |  |  |

| 9                                                             | PC0      | ACMP0_CH0<br>DAC0_OUT0ALT #0/<br>OPAMP_OUT0ALT            | TIM0_CC1 #4<br>PCNT0_S0IN #2                       | US0_TX #5 US1_TX #0<br>I2C0_SDA #4                      | LES_CH0 #0 PRS_CH2<br>#0    |  |  |  |

| 10                                                            | PC1      | ACMP0_CH1<br>DAC0_OUT0ALT #1/<br>OPAMP_OUT0ALT            | TIM0_CC2 #4<br>PCNT0_S1IN #2                       | US0_RX #5 US1_RX #0<br>I2C0_SCL #4                      | LES_CH1 #0 PRS_CH3<br>#0    |  |  |  |

| 11                                                            | PC2      | ACMP0_CH2<br>DAC0_OUT0ALT #2/<br>OPAMP_OUT0ALT            | TIM0_CDTI0 #4                                      | US2_TX #0                                               | LES_CH2 #0                  |  |  |  |

| 12                                                            | PC3      | ACMP0_CH3DAC0_OU<br>T0ALT #3/<br>OPAMP_OUT0ALT            | TIM0_CDTI1 #4                                      | US2_RX #0                                               | LES_CH3 #0                  |  |  |  |

| 13                                                            | PC4      | ACMP0_CH4<br>OPAMP_P0                                     | TIM0_CDTI2 #4 LE-<br>TIM0_OUT0 #3<br>PCNT1_S0IN #0 | US2_CLK #0 I2C1_SDA<br>#0                               | LES_CH4 #0                  |  |  |  |

| 14                                                            | PC5      | ACMP0_CH5<br>OPAMP_N0                                     | LETIM0_OUT1 #3<br>PCNT1_S1IN #0                    | US2_CS #0 I2C1_SCL<br>#0                                | LES_CH5 #0                  |  |  |  |

| 15                                                            | PB7      | LFXTAL_P                                                  | TIM1_CC0 #3                                        | US0_TX #4 US1_CLK<br>#0                                 |                             |  |  |  |

| 16                                                            | PB8      | LFXTAL_N                                                  | TIM1_CC1 #3                                        | US0_RX #4 US1_CS #0                                     |                             |  |  |  |

| 17                                                            | PA8      |                                                           | TIM2_CC0 #0                                        |                                                         |                             |  |  |  |

| 18                                                            | PA9      |                                                           | TIM2_CC1 #0                                        |                                                         |                             |  |  |  |

| 19                                                            | PA10     |                                                           | TIM2_CC2 #0                                        |                                                         |                             |  |  |  |

| 20                                                            | RESETn   | Reset input, active low. To low during reset, and let the |                                                    | source to this pin, it is requi that reset is released. | red to only drive this pin  |  |  |  |

| 21                                                            | PB11     | DAC0_OUT0 /<br>OPAMP_OUT0                                 | TIM1_CC2 #3 LE-<br>TIM0_OUT0 #1                    | I2C1_SDA #1                                             |                             |  |  |  |

| 22                                                            | VSS      | Ground.                                                   |                                                    |                                                         |                             |  |  |  |

| 23                                                            | AVDD_1   | Analog power supply 1.                                    |                                                    |                                                         |                             |  |  |  |

| 24                                                            | PB13     | HFXTAL_P                                                  |                                                    | US0_CLK #4/5<br>LEU0_TX #1                              |                             |  |  |  |

| 25                                                            | PB14     | HFXTAL_N                                                  |                                                    | US0_CS #4/5 LEU0_RX<br>#1                               |                             |  |  |  |

| 26                                                            | IOVDD_3  | Digital IO power supply 3.                                |                                                    |                                                         |                             |  |  |  |

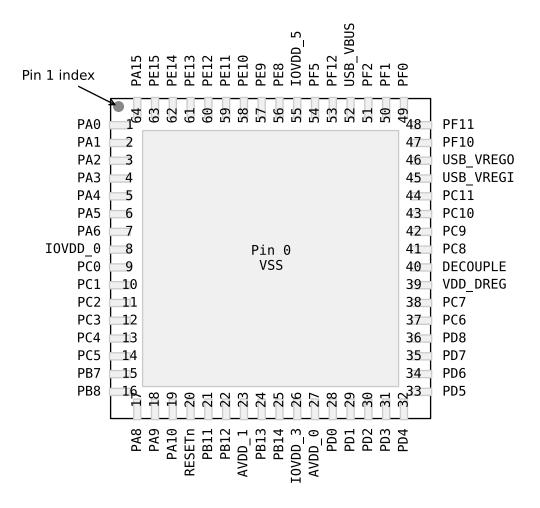

### 5.6 EFM32LG330 (QFN64)

### 5.6.1 Pinout

The EFM32LG330 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \* ROUTE register in the module in question.

Figure 5.11. EFM32LG330 Pinout (top view, not to scale)

| QFN   |          |         |                 |                           |                           |

|-------|----------|---------|-----------------|---------------------------|---------------------------|

| Pin # | Pin Name | Analog  | Timers          | Communication             | Other                     |

| 0     | VSS      | Ground. |                 |                           |                           |

| 1     | PA0      |         | TIM0_CC0 #0/1/4 | LEU0_RX #4 I2C0_SDA<br>#0 | PRS_CH0 #0<br>GPIO_EM4WU0 |

| Alternate     |      |      |      | LOCATIO | ON   |      |   |                                                                                       |

|---------------|------|------|------|---------|------|------|---|---------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3       | 4    | 5    | 6 | Description                                                                           |

| PCNT1_S0IN    | PC4  |      |      |         |      |      |   | Pulse Counter PCNT1 input number 0.                                                   |

| PCNT1_S1IN    | PC5  |      |      |         |      |      |   | Pulse Counter PCNT1 input number 1.                                                   |

| PCNT2_S0IN    | PD0  | PE8  |      |         |      |      |   | Pulse Counter PCNT2 input number 0.                                                   |

| PCNT2_S1IN    | PD1  | PE9  |      |         |      |      |   | Pulse Counter PCNT2 input number 1.                                                   |

| PRS_CH0       | PA0  |      |      |         |      |      |   | Peripheral Reflex System PRS, channel 0.                                              |

| PRS_CH1       | PA1  |      |      |         |      |      |   | Peripheral Reflex System PRS, channel 1.                                              |

| PRS_CH2       | PC0  | PF5  |      |         |      |      |   | Peripheral Reflex System PRS, channel 2.                                              |

| PRS_CH3       | PC1  | PE8  |      |         |      |      |   | Peripheral Reflex System PRS, channel 3.                                              |

| ТІМ0_СС0      | PA0  | PA0  |      | PD1     | PA0  | PF0  |   | Timer 0 Capture Compare input / output channel 0.                                     |

| TIM0_CC1      | PA1  | PA1  |      | PD2     | PC0  | PF1  |   | Timer 0 Capture Compare input / output channel 1.                                     |

| TIM0_CC2      | PA2  | PA2  |      | PD3     | PC1  | PF2  |   | Timer 0 Capture Compare input / output channel 2.                                     |

| TIM0_CDTI0    | PA3  |      |      |         | PC2  |      |   | Timer 0 Complimentary Deat Time Insertion channel 0.                                  |

| TIM0_CDTI1    | PA4  |      |      |         | PC3  |      |   | Timer 0 Complimentary Deat Time Insertion channel 1.                                  |

| TIM0_CDTI2    | PA5  |      | PF5  |         | PC4  | PF5  |   | Timer 0 Complimentary Deat Time Insertion channel 2.                                  |

| TIM1_CC0      |      | PE10 |      | PB7     | PD6  |      |   | Timer 1 Capture Compare input / output channel 0.                                     |

| TIM1_CC1      |      | PE11 |      | PB8     | PD7  |      |   | Timer 1 Capture Compare input / output channel 1.                                     |

| TIM1_CC2      |      | PE12 |      | PB11    |      |      |   | Timer 1 Capture Compare input / output channel 2.                                     |

| TIM2_CC0      | PA8  |      | PC8  |         |      |      |   | Timer 2 Capture Compare input / output channel 0.                                     |

| TIM2_CC1      | PA9  |      | PC9  |         |      |      |   | Timer 2 Capture Compare input / output channel 1.                                     |

| TIM2_CC2      | PA10 |      | PC10 |         |      |      |   | Timer 2 Capture Compare input / output channel 2.                                     |

| TIM3_CC0      | PE14 |      |      |         |      |      |   | Timer 3 Capture Compare input / output channel 0.                                     |

| TIM3_CC1      | PE15 |      |      |         |      |      |   | Timer 3 Capture Compare input / output channel 1.                                     |

| US0_CLK       | PE12 |      | PC9  |         | PB13 | PB13 |   | USART0 clock input / output.                                                          |

| US0_CS        | PE13 |      | PC8  |         | PB14 | PB14 |   | USART0 chip select input / output.                                                    |

|               |      |      |      |         |      |      |   | USART0 Asynchronous Receive.                                                          |

| US0_RX        | PE11 |      | PC10 | PE12    | PB8  | PC1  |   | USART0 Synchronous mode Master Input / Slave<br>Output (MISO).                        |

| LISO TY       | PE10 |      | PC11 | PE13    | PB7  | PC0  |   | USART0 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| US0_TX        |      |      |      | FE13    |      | FUU  |   | USART0 Synchronous mode Master Output / Slave<br>Input (MOSI).                        |

| US1_CLK       | PB7  | PD2  | PF0  |         |      |      |   | USART1 clock input / output.                                                          |

| US1_CS        | PB8  | PD3  | PF1  |         |      |      |   | USART1 chip select input / output.                                                    |

|               |      |      |      |         |      |      |   | USART1 Asynchronous Receive.                                                          |

| US1_RX        | PC1  | PD1  | PD6  |         |      |      |   | USART1 Synchronous mode Master Input / Slave Output (MISO).                           |

| Alternate     | E LOCATION    |     |     |   |   |   |   |                                                                                             |

|---------------|---------------|-----|-----|---|---|---|---|---------------------------------------------------------------------------------------------|

| Functionality | 0             | 1   | 2   | 3 | 4 | 5 | 6 | Description                                                                                 |

| US1 TX        | PC0           | PD0 | PD7 |   |   |   |   | USART1 Asynchronous Transmit. Also used as re-<br>ceive input in half duplex communication. |

|               |               |     |     |   |   |   |   | USART1 Synchronous mode Master Output / Slave Input (MOSI).                                 |

| US2_CLK       | PC4           |     |     |   |   |   |   | USART2 clock input / output.                                                                |

| US2_CS        | PC5           |     |     |   |   |   |   | USART2 chip select input / output.                                                          |

|               |               |     |     |   |   |   |   | USART2 Asynchronous Receive.                                                                |

| US2_RX        | PC3           |     |     |   |   |   |   | USART2 Synchronous mode Master Input / Slave<br>Output (MISO).                              |

| US2 TX        | PC2           |     |     |   |   |   |   | USART2 Asynchronous Transmit.Also used as re-<br>ceive input in half duplex communication.  |

| 032_17        | FG2           |     |     |   |   |   |   | USART2 Synchronous mode Master Output / Slave Input (MOSI).                                 |

| USB_DM        | PF10          |     |     |   |   |   |   | USB D- pin.                                                                                 |

| USB_DMPU      | PD2           |     |     |   |   |   |   | USB D- Pullup control.                                                                      |

| USB_DP        | PF11          |     |     |   |   |   |   | USB D+ pin.                                                                                 |

| USB_ID        | PF12          |     |     |   |   |   |   | USB ID pin. Used in OTG mode.                                                               |

| USB_VBUS      | USB_V<br>BUS  |     |     |   |   |   |   | USB 5 V VBUS input.                                                                         |

| USB_VBUSEN    | PF5           |     |     |   |   |   |   | USB 5 V VBUS enable.                                                                        |

| USB_VREGI     | USB_V<br>REGI |     |     |   |   |   |   | USB Input to internal 3.3 V regulator                                                       |

| USB_VREGO     | USB_V<br>REGO |     |     |   |   |   |   | USB Decoupling for internal 3.3 V USB regulator and regulator output                        |

# 5.7.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32LG332 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

### Table 5.21. GPIO Pinout

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | -         | -         | -         | -         | -         | PA10      | PA9   | PA8   | -     | -     | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| Port B | -         | PB14      | PB13      | -         | PB11      | -         | -     | PB8   | PB7   | -     | -     | -     | -     | -     | -     | -     |

| Port C | -         | -         | -         | -         | PC11      | PC10      | PC9   | PC8   | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| Port D | -         | -         | -         | -         | -         | -         | -     | PD8   | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9   | PE8   | -     | -     | -     | -     | -     | -     | -     | -     |

| Port F | -         | -         | -         | PF12      | PF11      | PF10      | -     | -     | -     | -     | PF5   | -     | -     | PF2   | PF1   | PF0   |

| Alternate     |      |      |     | LOCATIO | ON  |     |      |                                                                                      |  |

|---------------|------|------|-----|---------|-----|-----|------|--------------------------------------------------------------------------------------|--|

| Functionality | 0    | 1    | 2   | 3       | 4   | 5   | 6    | Description                                                                          |  |

| ETM_TD3       | PD5  |      | PD5 | PA5     |     |     |      | Embedded Trace Module ETM data 3.                                                    |  |

| GPIO_EM4WU0   | PA0  |      |     |         |     |     |      | Pin can be used to wake the system up from EM4                                       |  |

| GPIO_EM4WU1   | PA6  |      |     |         |     |     |      | Pin can be used to wake the system up from EM4                                       |  |

| GPIO_EM4WU2   | PC9  |      |     |         |     |     |      | Pin can be used to wake the system up from EM4                                       |  |

| GPIO_EM4WU3   | PF1  |      |     |         |     |     |      | Pin can be used to wake the system up from EM4                                       |  |

| GPIO_EM4WU4   | PF2  |      |     |         |     |     |      | Pin can be used to wake the system up from EM4                                       |  |

| GPIO_EM4WU5   | PE13 |      |     |         |     |     |      | Pin can be used to wake the system up from EM4                                       |  |

| HFXTAL_N      | PB14 |      |     |         |     |     |      | High Frequency Crystal negative pin. Also used as external optional clock input pin. |  |

| HFXTAL_P      | PB13 |      |     |         |     |     |      | High Frequency Crystal positive pin.                                                 |  |

| I2C0_SCL      | PA1  | PD7  | PC7 | PD15    | PC1 | PF1 | PE13 | I2C0 Serial Clock Line input / output.                                               |  |

| I2C0_SDA      | PA0  | PD6  | PC6 | PD14    | PC0 | PF0 | PE12 | I2C0 Serial Data input / output.                                                     |  |

| I2C1_SCL      | PC5  | PB12 | PE1 |         |     |     |      | I2C1 Serial Clock Line input / output.                                               |  |

| I2C1_SDA      | PC4  | PB11 | PE0 |         |     |     |      | I2C1 Serial Data input / output.                                                     |  |

| LES_ALTEX0    | PD6  |      |     |         |     |     |      | LESENSE alternate exite output 0.                                                    |  |

| LES_ALTEX1    | PD7  |      |     |         |     |     |      | LESENSE alternate exite output 1.                                                    |  |

| LES_ALTEX2    | PA3  |      |     |         |     |     |      | LESENSE alternate exite output 2.                                                    |  |

| LES_ALTEX3    | PA4  |      |     |         |     |     |      | LESENSE alternate exite output 3.                                                    |  |

| LES_ALTEX4    | PA5  |      |     |         |     |     |      | LESENSE alternate exite output 4.                                                    |  |

| LES_ALTEX5    | PE11 |      |     |         |     |     |      | LESENSE alternate exite output 5.                                                    |  |

| LES_ALTEX6    | PE12 |      |     |         |     |     |      | LESENSE alternate exite output 6.                                                    |  |

| LES_ALTEX7    | PE13 |      |     |         |     |     |      | LESENSE alternate exite output 7.                                                    |  |

| LES_CH0       | PC0  |      |     |         |     |     |      | LESENSE channel 0.                                                                   |  |

| LES_CH1       | PC1  |      |     |         |     |     |      | LESENSE channel 1.                                                                   |  |

| LES_CH2       | PC2  |      |     |         |     |     |      | LESENSE channel 2.                                                                   |  |

| LES_CH3       | PC3  |      |     |         |     |     |      | LESENSE channel 3.                                                                   |  |

| LES_CH4       | PC4  |      |     |         |     |     |      | LESENSE channel 4.                                                                   |  |

| LES_CH5       | PC5  |      |     |         |     |     |      | LESENSE channel 5.                                                                   |  |

| LES_CH6       | PC6  |      |     |         |     |     |      | LESENSE channel 6.                                                                   |  |

| LES_CH7       | PC7  |      |     |         |     |     |      | LESENSE channel 7.                                                                   |  |

| LES_CH8       | PC8  |      |     |         |     |     |      | LESENSE channel 8.                                                                   |  |

| LES_CH9       | PC9  |      |     |         |     |     |      | LESENSE channel 9.                                                                   |  |

| LES_CH10      | PC10 |      |     |         |     |     |      | LESENSE channel 10.                                                                  |  |

| LES_CH11      | PC11 |      |     |         |     |     |      | LESENSE channel 11.                                                                  |  |

| LETIM0_OUT0   | PD6  | PB11 | PF0 | PC4     |     |     |      | Low Energy Timer LETIM0, output channel 0.                                           |  |

| LETIM0_OUT1   | PD7  | PB12 | PF1 | PC5     |     |     |      | Low Energy Timer LETIM0, output channel 1.                                           |  |

| QFN   | 64 Pin# and Name | Pin Alternate Functionality / Description                      |                                                                |                             |                                                           |  |  |  |  |

|-------|------------------|----------------------------------------------------------------|----------------------------------------------------------------|-----------------------------|-----------------------------------------------------------|--|--|--|--|

| Pin # | Pin Name         | Analog                                                         | Timers                                                         | Communication               | Other                                                     |  |  |  |  |

| 27    | AVDD_0           | Analog power supply 0.                                         |                                                                |                             |                                                           |  |  |  |  |

| 28    | PD0              | ADC0_CH0<br>DAC0_OUT0ALT #4/<br>OPAMP_OUT0ALT<br>OPAMP_OUT2 #1 | PCNT2_S0IN #0                                                  | US1_TX #1                   |                                                           |  |  |  |  |

| 29    | PD1              | ADC0_CH1<br>DAC0_OUT1ALT #4/<br>OPAMP_OUT1ALT                  | TIM0_CC0 #3<br>PCNT2_S1IN #0                                   | US1_RX #1                   | DBG_SWO #2                                                |  |  |  |  |

| 30    | PD2              | ADC0_CH2                                                       | TIM0_CC1 #3                                                    | US1_CLK #1                  | DBG_SWO #3                                                |  |  |  |  |

| 31    | PD3              | ADC0_CH3 OPAMP_N2                                              | TIM0_CC2 #3                                                    | US1_CS #1                   | ETM_TD1 #0/2                                              |  |  |  |  |

| 32    | PD4              | ADC0_CH4 OPAMP_P2                                              |                                                                | LEU0_TX #0                  | ETM_TD2 #0/2                                              |  |  |  |  |

| 33    | PD5              | ADC0_CH5<br>OPAMP_OUT2 #0                                      |                                                                | LEU0_RX #0                  | ETM_TD3 #0/2                                              |  |  |  |  |

| 34    | PD6              | ADC0_CH6 OPAMP_P1                                              | TIM1_CC0 #4 LE-<br>TIM0_OUT0 #0<br>PCNT0_S0IN #3               | US1_RX #2 I2C0_SDA<br>#1    | LES_ALTEX0 #0<br>ACMP0_O #2<br>ETM_TD0 #0                 |  |  |  |  |

| 35    | PD7              | ADC0_CH7 OPAMP_N1                                              | TIM1_CC1 #4 LE-<br>TIM0_OUT1 #0<br>PCNT0_S1IN #3               | US1_TX #2 I2C0_SCL<br>#1    | CMU_CLK0 #2<br>LES_ALTEX1 #0<br>ACMP1_O #2<br>ETM_TCLK #0 |  |  |  |  |

| 36    | PD8              | BU_VIN                                                         |                                                                |                             | CMU_CLK1 #1                                               |  |  |  |  |

| 37    | PC6              | ACMP0_CH6                                                      |                                                                | LEU1_TX #0 I2C0_SDA<br>#2   | LES_CH6 #0<br>ETM_TCLK #2                                 |  |  |  |  |

| 38    | PC7              | ACMP0_CH7                                                      |                                                                | LEU1_RX #0 I2C0_SCL<br>#2   | LES_CH7 #0 ETM_TD0<br>#2                                  |  |  |  |  |

| 39    | VDD_DREG         | Power supply for on-chip                                       | voltage regulator.                                             |                             |                                                           |  |  |  |  |

| 40    | DECOUPLE         | Decouple output for on-ch at this pin.                         | ip voltage regulator. An e                                     | xternal capacitance of size | C <sub>DECOUPLE</sub> is required                         |  |  |  |  |

| 41    | PE4              | LCD_COM0                                                       |                                                                | US0_CS #1                   |                                                           |  |  |  |  |

| 42    | PE5              | LCD_COM1                                                       |                                                                | US0_CLK #1                  |                                                           |  |  |  |  |

| 43    | PE6              | LCD_COM2                                                       |                                                                | US0_RX #1                   |                                                           |  |  |  |  |

| 44    | PE7              | LCD_COM3                                                       |                                                                | US0_TX #1                   |                                                           |  |  |  |  |

| 45    | PC12             | ACMP1_CH4<br>DAC0_OUT1ALT #0/<br>OPAMP_OUT1ALT                 |                                                                |                             | CMU_CLK0 #1<br>LES_CH12 #0                                |  |  |  |  |

| 46    | PC13             | ACMP1_CH5<br>DAC0_OUT1ALT #1/<br>OPAMP_OUT1ALT                 | TIM0_CDTI0 #1/3<br>TIM1_CC0 #0<br>TIM1_CC2 #4<br>PCNT0_S0IN #0 |                             | LES_CH13 #0                                               |  |  |  |  |

| 47    | PC14             | ACMP1_CH6<br>DAC0_OUT1ALT #2/<br>OPAMP_OUT1ALT                 | TIM0_CDTI1 #1/3<br>TIM1_CC1 #0<br>PCNT0_S1IN #0                | US0_CS #3                   | LES_CH14 #0                                               |  |  |  |  |

| 48    | PC15             | ACMP1_CH7<br>DAC0_OUT1ALT #3/<br>OPAMP_OUT1ALT                 | TIM0_CDTI2 #1/3<br>TIM1_CC2 #0                                 | US0_CLK #3                  | LES_CH15 #0<br>DBG_SWO #1                                 |  |  |  |  |

### 5.13.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     |      |      | L    | OCATIC | N |   |   |                                                           |

|---------------|------|------|------|--------|---|---|---|-----------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3      | 4 | 5 | 6 | Description                                               |

| ACMP0_CH4     | PC4  |      |      |        |   |   |   | Analog comparator ACMP0, channel 4.                       |

| ACMP0_CH5     | PC5  |      |      |        |   |   |   | Analog comparator ACMP0, channel 5.                       |

| ACMP0_CH6     | PC6  |      |      |        |   |   |   | Analog comparator ACMP0, channel 6.                       |

| ACMP0_CH7     | PC7  |      |      |        |   |   |   | Analog comparator ACMP0, channel 7.                       |

| ACMP0_O       | PE13 |      | PD6  |        |   |   |   | Analog comparator ACMP0, digital output.                  |

| ACMP1_CH4     | PC12 |      |      |        |   |   |   | Analog comparator ACMP1, channel 4.                       |

| ACMP1_CH5     | PC13 |      |      |        |   |   |   | Analog comparator ACMP1, channel 5.                       |

| ACMP1_CH6     | PC14 |      |      |        |   |   |   | Analog comparator ACMP1, channel 6.                       |

| ACMP1_CH7     | PC15 |      |      |        |   |   |   | Analog comparator ACMP1, channel 7.                       |

| ACMP1_O       | PF2  |      | PD7  |        |   |   |   | Analog comparator ACMP1, digital output.                  |

| ADC0_CH0      | PD0  |      |      |        |   |   |   | Analog to digital converter ADC0, input channel number 0. |

| ADC0_CH1      | PD1  |      |      |        |   |   |   | Analog to digital converter ADC0, input channel number 1. |

| ADC0_CH2      | PD2  |      |      |        |   |   |   | Analog to digital converter ADC0, input channel number 2. |

| ADC0_CH3      | PD3  |      |      |        |   |   |   | Analog to digital converter ADC0, input channel number 3. |

| ADC0_CH4      | PD4  |      |      |        |   |   |   | Analog to digital converter ADC0, input channel number 4. |

| ADC0_CH5      | PD5  |      |      |        |   |   |   | Analog to digital converter ADC0, input channel number 5. |

| ADC0_CH6      | PD6  |      |      |        |   |   |   | Analog to digital converter ADC0, input channel number 6. |

| ADC0_CH7      | PD7  |      |      |        |   |   |   | Analog to digital converter ADC0, input channel number 7. |

| BOOT_RX       | PE11 |      |      |        |   |   |   | Bootloader RX.                                            |

| BOOT_TX       | PE10 |      |      |        |   |   |   | Bootloader TX.                                            |

| BU_VIN        | PD8  |      |      |        |   |   |   | Battery input for Backup Power Domain                     |

| CMU_CLK0      | PA2  | PC12 | PD7  |        |   |   |   | Clock Management Unit, clock output number 0.             |

| CMU_CLK1      | PA1  | PD8  | PE12 |        |   |   |   | Clock Management Unit, clock output number 1.             |

| OPAMP_N0      | PC5  |      |      |        |   |   |   | Operational Amplifier 0 external negative input.          |

| OPAMP_N1      | PD7  |      |      |        |   |   |   | Operational Amplifier 1 external negative input.          |

# Table 5.38. Alternate functionality overview

| Alternate     |      |      |      |     | ON  |   |   |                                                                                                                         |  |

|---------------|------|------|------|-----|-----|---|---|-------------------------------------------------------------------------------------------------------------------------|--|

| Functionality | 0    | 1    | 2    | 3   | 4   | 5 | 6 | Description                                                                                                             |  |

| LES_ALTEX6    | PE12 |      |      |     |     |   |   | LESENSE alternate exite output 6.                                                                                       |  |

| LES_ALTEX7    | PE13 |      |      |     |     |   |   | LESENSE alternate exite output 7.                                                                                       |  |

| LES_CH0       | PC0  |      |      |     |     |   |   | LESENSE channel 0.                                                                                                      |  |

| LES_CH1       | PC1  |      |      |     |     |   |   | LESENSE channel 1.                                                                                                      |  |

| LES_CH2       | PC2  |      |      |     |     |   |   | LESENSE channel 2.                                                                                                      |  |

| LES_CH3       | PC3  |      |      |     |     |   |   | LESENSE channel 3.                                                                                                      |  |

| LES_CH4       | PC4  |      |      |     |     |   |   | LESENSE channel 4.                                                                                                      |  |

| LES_CH5       | PC5  |      |      |     |     |   |   | LESENSE channel 5.                                                                                                      |  |

| LES_CH6       | PC6  |      |      |     |     |   |   | LESENSE channel 6.                                                                                                      |  |

| LES_CH7       | PC7  |      |      |     |     |   |   | LESENSE channel 7.                                                                                                      |  |

| LES_CH8       | PC8  |      |      |     |     |   |   | LESENSE channel 8.                                                                                                      |  |

| LES_CH9       | PC9  |      |      |     |     |   |   | LESENSE channel 9.                                                                                                      |  |

| LES_CH10      | PC10 |      |      |     |     |   |   | LESENSE channel 10.                                                                                                     |  |

| LES_CH11      | PC11 |      |      |     |     |   |   | LESENSE channel 11.                                                                                                     |  |

| LES_CH12      | PC12 |      |      |     |     |   |   | LESENSE channel 12.                                                                                                     |  |

| LES_CH13      | PC13 |      |      |     |     |   |   | LESENSE channel 13.                                                                                                     |  |

| LES_CH14      | PC14 |      |      |     |     |   |   | LESENSE channel 14.                                                                                                     |  |

| LES_CH15      | PC15 |      |      |     |     |   |   | LESENSE channel 15.                                                                                                     |  |

| LETIM0_OUT0   | PD6  | PB11 | PF0  | PC4 |     |   |   | Low Energy Timer LETIM0, output channel 0.                                                                              |  |

| LETIM0_OUT1   | PD7  | PB12 | PF1  | PC5 |     |   |   | Low Energy Timer LETIM0, output channel 1.                                                                              |  |

| LEU0_RX       | PD5  | PB14 | PE15 | PF1 | PA0 |   |   | LEUART0 Receive input.                                                                                                  |  |

| LEU0_TX       | PD4  | PB13 | PE14 | PF0 | PF2 |   |   | LEUART0 Transmit output. Also used as receive in-<br>put in half duplex communication.                                  |  |

| LEU1_RX       | PC7  | PA6  |      |     |     |   |   | LEUART1 Receive input.                                                                                                  |  |

| LEU1_TX       | PC6  | PA5  |      |     |     |   |   | LEUART1 Transmit output. Also used as receive in-<br>put in half duplex communication.                                  |  |

| LFXTAL_N      | PB8  |      |      |     |     |   |   | Low Frequency Crystal (typically 32.768 kHz) nega-<br>tive pin. Also used as an optional external clock in-<br>put pin. |  |

| LFXTAL_P      | PB7  |      |      |     |     |   |   | Low Frequency Crystal (typically 32.768 kHz) posi-<br>tive pin.                                                         |  |

| PCNT0_S0IN    | PC13 | PE0  | PC0  | PD6 |     |   |   | Pulse Counter PCNT0 input number 0.                                                                                     |  |

| PCNT0_S1IN    | PC14 | PE1  | PC1  | PD7 |     |   |   | Pulse Counter PCNT0 input number 1.                                                                                     |  |

| PCNT1_S0IN    | PC4  | PB3  |      |     |     |   |   | Pulse Counter PCNT1 input number 0.                                                                                     |  |

| PCNT1_S1IN    | PC5  | PB4  |      |     |     |   |   | Pulse Counter PCNT1 input number 1.                                                                                     |  |

| PCNT2_S0IN    | PD0  | PE8  |      |     |     |   |   | Pulse Counter PCNT2 input number 0.                                                                                     |  |

| PCNT2_S1IN    | PD1  | PE9  |      |     |     |   |   | Pulse Counter PCNT2 input number 1.                                                                                     |  |

| PRS_CH0       | PA0  | PF3  |      |     |     |   |   | Peripheral Reflex System PRS, channel 0.                                                                                |  |

| Alternate              | LOCATION |   |   |   | N |   |   |                                                                                                                       |

|------------------------|----------|---|---|---|---|---|---|-----------------------------------------------------------------------------------------------------------------------|

| Functionality          | 0        | 1 | 2 | 3 | 4 | 5 | 6 | Description                                                                                                           |

| LCD_SEG4               | PE8      |   |   |   |   |   |   | LCD segment line 4. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                  |

| LCD_SEG5               | PE9      |   |   |   |   |   |   | LCD segment line 5. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                  |

| LCD_SEG6               | PE10     |   |   |   |   |   |   | LCD segment line 6. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                  |

| LCD_SEG7               | PE11     |   |   |   |   |   |   | LCD segment line 7. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                  |

| LCD_SEG8               | PE12     |   |   |   |   |   |   | LCD segment line 8. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                                |

| LCD_SEG9               | PE13     |   |   |   |   |   |   | LCD segment line 9. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                                |

| LCD_SEG10              | PE14     |   |   |   |   |   |   | LCD segment line 10. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                               |

| LCD_SEG11              | PE15     |   |   |   |   |   |   | LCD segment line 11. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                               |

| LCD_SEG12              | PA15     |   |   |   |   |   |   | LCD segment line 12. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                             |

| LCD_SEG13              | PA0      |   |   |   |   |   |   | LCD segment line 13. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                             |

| LCD_SEG14              | PA1      |   |   |   |   |   |   | LCD segment line 14. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                             |

| LCD_SEG15              | PA2      |   |   |   |   |   |   | LCD segment line 15. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                             |

| LCD_SEG16              | PA3      |   |   |   |   |   |   | LCD segment line 16. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                             |

| LCD_SEG17              | PA4      |   |   |   |   |   |   | LCD segment line 17. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                             |

| LCD_SEG18              | PA5      |   |   |   |   |   |   | LCD segment line 18. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                             |

| LCD_SEG19              | PA6      |   |   |   |   |   |   | LCD segment line 19. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                             |

| LCD_SEG20/<br>LCD_COM4 | PB3      |   |   |   |   |   |   | LCD segment line 20. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 4 |

| LCD_SEG21/<br>LCD_COM5 | PB4      |   |   |   |   |   |   | LCD segment line 21. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 5 |

| LCD_SEG22/<br>LCD_COM6 | PB5      |   |   |   |   |   |   | LCD segment line 22. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 6 |

| LCD_SEG23/<br>LCD_COM7 | PB6      |   |   |   |   |   |   | LCD segment line 23. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 7 |

| LCD_SEG24              | PF6      |   |   |   |   |   |   | LCD segment line 24. Segments 24, 25, 26 and 27 are controlled by SEGEN6.                                             |

| QFN6  | 64 Pin# and Name |                                                           | Pin Alternate Funct                                | ionality / Description                                    |                             |

|-------|------------------|-----------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------|-----------------------------|

| Pin # | Pin Name         | Analog                                                    | Timers                                             | Communication                                             | Other                       |

| 2     | PA1              | LCD_SEG14                                                 | TIM0_CC1 #0/1                                      | 12C0_SCL #0                                               | CMU_CLK1 #0<br>PRS_CH1 #0   |

| 3     | PA2              | LCD_SEG15                                                 | TIM0_CC2 #0/1                                      |                                                           | CMU_CLK0 #0<br>ETM_TD0 #3   |

| 4     | PA3              | LCD_SEG16                                                 | TIM0_CDTI0 #0                                      |                                                           | LES_ALTEX2 #0<br>ETM_TD1 #3 |

| 5     | PA4              | LCD_SEG17                                                 | TIM0_CDTI1 #0                                      |                                                           | LES_ALTEX3 #0<br>ETM_TD2 #3 |

| 6     | PA5              | LCD_SEG18                                                 | TIM0_CDTI2 #0                                      | LEU1_TX #1                                                | LES_ALTEX4 #0<br>ETM_TD3 #3 |

| 7     | PA6              | LCD_SEG19                                                 |                                                    | LEU1_RX #1                                                | ETM_TCLK #3<br>GPIO_EM4WU1  |

| 8     | IOVDD_0          | Digital IO power supply 0.                                |                                                    |                                                           |                             |

| 9     | PB3              | LCD_SEG20/<br>LCD_COM4                                    | PCNT1_S0IN #1                                      | US2_TX #1                                                 |                             |

| 10    | PB4              | LCD_SEG21/<br>LCD_COM5                                    | PCNT1_S1IN #1                                      | US2_RX #1                                                 |                             |

| 11    | PB5              | LCD_SEG22/<br>LCD_COM6                                    |                                                    | US2_CLK #1                                                |                             |

| 12    | PB6              | LCD_SEG23/<br>LCD_COM7                                    |                                                    | US2_CS #1                                                 |                             |

| 13    | PC4              | ACMP0_CH4<br>OPAMP_P0                                     | TIM0_CDTI2 #4 LE-<br>TIM0_OUT0 #3<br>PCNT1_S0IN #0 | US2_CLK #0 I2C1_SDA<br>#0                                 | LES_CH4 #0                  |

| 14    | PC5              | ACMP0_CH5<br>OPAMP_N0                                     | LETIM0_OUT1 #3<br>PCNT1_S1IN #0                    | US2_CS #0 I2C1_SCL<br>#0                                  | LES_CH5 #0                  |

| 15    | PB7              | LFXTAL_P                                                  | TIM1_CC0 #3                                        | US0_TX #4 US1_CLK<br>#0                                   |                             |

| 16    | PB8              | LFXTAL_N                                                  | TIM1_CC1 #3                                        | US0_RX #4 US1_CS #0                                       |                             |

| 17    | PA12             | LCD_BCAP_P                                                | TIM2_CC0 #1                                        |                                                           |                             |

| 18    | PA13             | LCD_BCAP_N                                                | TIM2_CC1 #1                                        |                                                           |                             |

| 19    | PA14             | LCD_BEXT                                                  | TIM2_CC2 #1                                        |                                                           |                             |

| 20    | RESETn           | Reset input, active low. To low during reset, and let the |                                                    | source to this pin, it is require that reset is released. | red to only drive this pin  |

| 21    | PB11             | DAC0_OUT0 /<br>OPAMP_OUT0                                 | TIM1_CC2 #3 LE-<br>TIM0_OUT0 #1                    | I2C1_SDA #1                                               |                             |

| 22    | PB12             | DAC0_OUT1 /<br>OPAMP_OUT1                                 | LETIM0_OUT1 #1                                     | I2C1_SCL #1                                               |                             |

| 23    | AVDD_1           | Analog power supply 1.                                    |                                                    |                                                           |                             |

| 24    | PB13             | HFXTAL_P                                                  |                                                    | US0_CLK #4/5<br>LEU0_TX #1                                |                             |

| 25    | PB14             | HFXTAL_N                                                  |                                                    | US0_CS #4/5 LEU0_RX<br>#1                                 |                             |

| 26    | IOVDD_3          | Digital IO power supply 3.                                |                                                    |                                                           |                             |

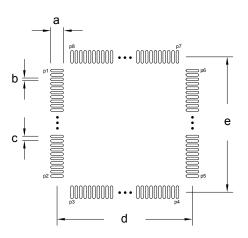

# 9.2 LQFP100 PCB Layout

Figure 9.2. LQFP100 PCB Land Pattern

# Table 9.2. LQFP100 PCB Land Pattern Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) | Symbol | Pin Number | Symbol | Pin Number |

|--------|-----------|--------|------------|--------|------------|

| а      | 1.45      | P1     | 1          | P6     | 75         |

| b      | 0.30      | P2     | 25         | P7     | 76         |

| с      | 0.50      | P3     | 26         | P8     | 100        |

| d      | 15.40     | P4     | 50         |        |            |

| e      | 15.40     | P5     | 51         |        |            |

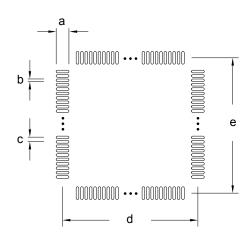

Figure 9.3. LQFP100 PCB Solder Mask

### Table 9.3. LQFP100 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 1.57      |

| b      | 0.42      |

# 10. TQFP64 Package Specifications

### 10.1 TQFP64 Package Dimensions

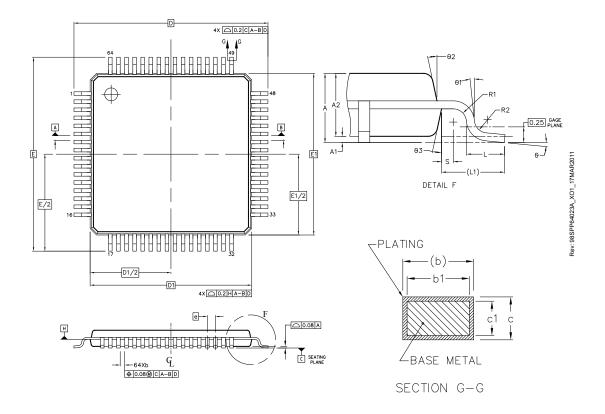

Figure 10.1. TQFP64

#### Note:

- 1. All dimensions & tolerancing confirm to ASME Y14.5M-1994.

- 2. The top package body size may be smaller than the bottom package body size.

- 3. Datum 'A,B', and 'B' to be determined at datum plane 'H'.

- 4. To be determined at seating place 'C'.

- 5. Dimension 'D1' and 'E1' do not include mold protrusions. Allowable protrusion is 0.25mm per side.'D1' and 'E1' are maximum plastic body size dimension including mold mismatch. Dimension 'D1' and'E1' shall be determined at datum plane 'H'.

- 6. Detail of Pin 1 indicatifier are option all but must be located within the zone indicated.

- 7. Dimension 'b' does not include dambar protrusion. Allowable dambar protrusion shall not cause thelead width to exceed the maximum 'b' dimension by more than 0.08 mm. Dambar can not be locatedon the lower radius or the foot. Minimum space between protrusion and an adjacent lead is 0.07 mm.

- 8. Exact shape of each corner is optional.

- 9. These dimension apply to the flat section of the lead between 0.10 mm and 0.25 mm from the lead tip.

- 10. All dimensions are in millimeters.

| DIM | MIN  | NOM  | MAX  | DIM | MIN  | NOM | МАХ  |

|-----|------|------|------|-----|------|-----|------|

| A   | _    | 1.10 | 1.20 | L1  |      | —   |      |

| A1  | 0.05 | —    | 0.15 | R1  | 0.08 | —   | —    |

| A2  | 0.95 | 1.00 | 1.05 | R2  | 0.08 | —   | 0.20 |

#### Table 10.1. QFP64 (Dimensions in mm)