Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                   |

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 65                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                               |

| Data Converters            | A/D 8x12b; D/A 1x12b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 81-UFBGA, CSPBGA                                                           |

| Supplier Device Package    | 81-CSP (4.35x4.27)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32lg360f256g-e-csp81r |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Module | Configuration      | Pin Connections                                                   |  |  |  |  |  |

|--------|--------------------|-------------------------------------------------------------------|--|--|--|--|--|

| OPAMP  | Full configuration | Outputs: OPAMP_OUTx, OPAMP_OUTxALT, Inputs: OPAMP_Px,<br>OPAMP_Nx |  |  |  |  |  |

| AES    | Full configuration | NA                                                                |  |  |  |  |  |

| GPIO   | 50 pins            | Available pins are shown in 5.7.3 GPIO Pinout Overview            |  |  |  |  |  |

| Parameter                                           | Symbol           | Test Condition                                                                                                  | Min | Тур               | Мах              | Unit   |

|-----------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------|-----|-------------------|------------------|--------|

| EM1 current (Production test<br>condition = 14 MHz) | I <sub>EM1</sub> | 48 MHz HFXO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=25 $^\circ\mathrm{C}$                         | _   | 63                | 75               | µA/MHz |

|                                                     |                  | 48 MHz HFXO, all peripheral clocks disabled, V_DD= 3.0 V, T_AMB=85°C                                            | _   | 65                | 76               | µA/MHz |

|                                                     |                  | 28 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=25 $^\circ\text{C}$                          | _   | 64                | 75               | µA/MHz |

|                                                     |                  | 28 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=85 $^\circ\text{C}$                          | _   | 65                | 77               | µA/MHz |

|                                                     |                  | 21 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=25 $^\circ\text{C}$                          | _   | 65                | 76               | µA/MHz |

|                                                     |                  | 21 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=85 $^\circ\text{C}$                          | _   | 66                | 78               | µA/MHz |

|                                                     |                  | 14 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=25 $^\circ\text{C}$                          | _   | 67                | 79               | µA/MHz |

|                                                     |                  | 14 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=85 $^\circ\text{C}$                          | _   | 68                | 82               | µA/MHz |

|                                                     |                  | 11 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=25 $^\circ\text{C}$                          | _   | 68                | 81               | µA/MHz |

|                                                     |                  | 11 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=85 $^\circ\text{C}$                          | _   | 70                | 83               | µA/MHz |

|                                                     |                  | 6.6 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=25 $^\circ\mathrm{C}$                       | _   | 74                | 87               | µA/MHz |

|                                                     |                  | 6.6 MHz HFRCO, all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=85 $^\circ\mathrm{C}$                       | _   | 76                | 89               | µA/MHz |

|                                                     |                  | 1.2 MHz HFRCO. all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=25 $^\circ\mathrm{C}$                       | _   | 106               | 120              | µA/MHz |

|                                                     |                  | 1.2 MHz HFRCO. all peripheral clocks disabled, V_DD= 3.0 V, T_{AMB}=85 $^\circ\mathrm{C}$                       | _   | 112               | 129              | µA/MHz |

| EM2 current                                         | I <sub>EM2</sub> | EM2 current with RTC prescaled to 1 Hz,<br>32.768 kHz LFRCO, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C               | _   | 0.95 <sup>1</sup> | 1.7 <sup>1</sup> | μA     |

|                                                     |                  | EM2 current with RTC prescaled to 1 Hz,<br>32.768 kHz LFRCO, V <sub>DD</sub> = 3.0 V,<br>T <sub>AMB</sub> =85°C | _   | 3.0 <sup>1</sup>  | 4.0 <sup>1</sup> | μA     |

| EM3 current                                         | I <sub>EM3</sub> | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =25°C                                                                 | _   | 0.65              | 1.3              | μA     |

|                                                     |                  | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =85°C                                                                 | _   | 2.65              | 4.0              | μA     |

| EM4 current                                         | I <sub>EM4</sub> | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =25°C                                                                 | —   | 0.020             | 0.055            | μA     |

|                                                     |                  | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =85°C                                                                 | _   | 0.44              | 0.90             | μA     |

Note:

1. Using backup RTC.

| Parameter                                        | Symbol               | Test Condition                                                       | Min | Тур | Max | Unit |

|--------------------------------------------------|----------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| Signal-to-Noise And Distortion-<br>ratio (SINAD) | SINAD <sub>ADC</sub> | 1 MSamples/s, 12 bit, single<br>ended, internal 1.25V reference      | _   | 58  | _   | dB   |

|                                                  |                      | 1 MSamples/s, 12 bit, single<br>ended, internal 2.5 V reference      | —   | 62  | —   | dB   |

|                                                  |                      | 1 MSamples/s, 12 bit, single ended, VDD reference                    | —   | 64  | _   | dB   |

|                                                  |                      | 1 MSamples/s, 12 bit, differen-<br>tial, internal 1.25 V reference   | —   | 60  | —   | dB   |

|                                                  |                      | 1 MSamples/s, 12 bit, differen-<br>tial, internal 2.5 V reference    | —   | 64  | —   | dB   |

|                                                  |                      | 1 MSamples/s, 12 bit, differen-<br>tial, 5 V reference               | —   | 54  | _   | dB   |

|                                                  |                      | 1 MSamples/s, 12 bit, differen-<br>tial, VDD reference               | —   | 66  | _   | dB   |

|                                                  |                      | 1 MSamples/s, 12 bit, differen-<br>tial, 2xVDD reference             | —   | 68  | _   | dB   |

|                                                  |                      | 200 kSamples/s, 12 bit, single<br>ended, internal 1.25 V reference   | —   | 61  | _   | dB   |

|                                                  |                      | 200 kSamples/s, 12 bit, single<br>ended, internal 2.5 V reference    | —   | 65  | —   | dB   |

|                                                  |                      | 200 kSamples/s, 12 bit, single ended, VDD reference                  | —   | 66  | —   | dB   |

|                                                  |                      | 200 kSamples/s, 12 bit, differen-<br>tial, internal 1.25 V reference | —   | 63  | —   | dB   |

|                                                  |                      | 200 kSamples/s, 12 bit, differen-<br>tial, internal 2.5 V reference  | —   | 66  | —   | dB   |

|                                                  |                      | 200 kSamples/s, 12 bit, differen-<br>tial, 5V reference              | —   | 66  | _   | dB   |

| Signal-to-Noise And Distortion-<br>ratio (SINAD) | SINAD <sub>ADC</sub> | 200 kSamples/s, 12 bit, differen-<br>tial, VDD reference             | 62  | 66  | _   | dB   |

|                                                  |                      | 200 kSamples/s, 12 bit, differen-<br>tial, 2xVDD reference           | _   | 69  | _   | dB   |

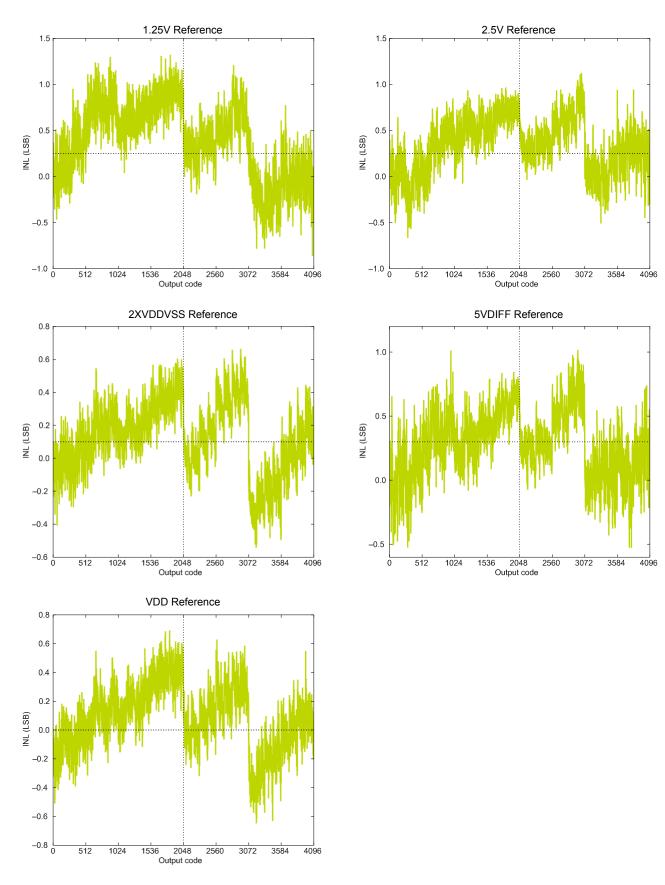

Figure 4.26. ADC Integral Linearity Error vs Code, VDD = 3 V, Temp = 25 °C

# 5. Pin Definitions

**Note:** Please refer to the application note AN0002 EFM32 Hardware Design Considerations for guidelines on designing Printed Circuit Boards (PCBs) for the EFM32LG.

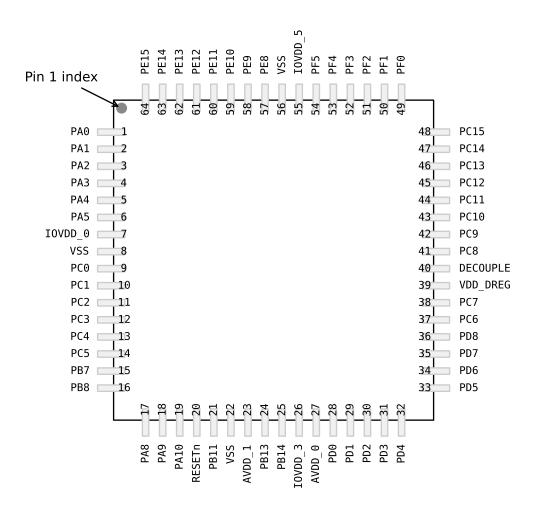

# 5.1 EFM32LG230 (QFN64)

### 5.1.1 Pinout

The EFM32LG230 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.1. EFM32LG230 Pinout (top view, not to scale)

| Alternate                         |           |      |      | LOCATIO | ON  |   |   |                                                                                                 |

|-----------------------------------|-----------|------|------|---------|-----|---|---|-------------------------------------------------------------------------------------------------|

| Functionality                     | 0         | 1    | 2    | 3       | 4   | 5 | 6 | Description                                                                                     |

| ADC0_CH7                          | PD7       |      |      |         |     |   |   | Analog to digital converter ADC0, input channel number 7.                                       |

| BOOT_RX                           | PE11      |      |      |         |     |   |   | Bootloader RX.                                                                                  |

| BOOT_TX                           | PE10      |      |      |         |     |   |   | Bootloader TX.                                                                                  |

| BU_VIN                            | PD8       |      |      |         |     |   |   | Battery input for Backup Power Domain                                                           |

| CMU_CLK0                          | PA2       | PC12 | PD7  |         |     |   |   | Clock Management Unit, clock output number 0.                                                   |

| CMU_CLK1                          | PA1       | PD8  | PE12 |         |     |   |   | Clock Management Unit, clock output number 1.                                                   |

| OPAMP_N0                          | PC5       |      |      |         |     |   |   | Operational Amplifier 0 external negative input.                                                |

| OPAMP_N1                          | PD7       |      |      |         |     |   |   | Operational Amplifier 1 external negative input.                                                |

| OPAMP_N2                          | PD3       |      |      |         |     |   |   | Operational Amplifier 2 external negative input.                                                |

| DAC0_OUT0 /<br>OPAMP_OUT0         | PB11      |      |      |         |     |   |   | Digital to Analog Converter DAC0_OUT0 /OPAMP output channel number 0.                           |

| DAC0_OUT0ALT<br>OPAMP_OUT0A<br>LT |           | PC1  | PC2  | PC3     | PD0 |   |   | Digital to Analog Converter DAC0_OUT0ALT /<br>OPAMP alternative output for channel 0.           |

| DAC0_OUT1 /<br>OPAMP_OUT1         | PB12      |      |      |         |     |   |   | Digital to Analog Converter DAC0_OUT1 / OPAMP output channel number 1.                          |

| DAC0_OUT1ALT<br>OPAMP_OUT1A<br>LT | /<br>PC12 | PC13 | PC14 | PC15    | PD1 |   |   | Digital to Analog Converter DAC0_OUT1ALT /<br>OPAMP alternative output for channel 1.           |

| OPAMP_OUT2                        | PD5       | PD0  |      |         |     |   |   | Operational Amplifier 2 output.                                                                 |

| OPAMP_P0                          | PC4       |      |      |         |     |   |   | Operational Amplifier 0 external positive input.                                                |

| OPAMP_P1                          | PD6       |      |      |         |     |   |   | Operational Amplifier 1 external positive input.                                                |

| OPAMP_P2                          | PD4       |      |      |         |     |   |   | Operational Amplifier 2 external positive input.                                                |

|                                   |           |      |      |         |     |   |   | Debug-interface Serial Wire clock input.                                                        |

| DBG_SWCLK                         | PF0       | PF0  | PF0  | PF0     |     |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull down.           |

|                                   |           |      |      |         |     |   |   | Debug-interface Serial Wire data input / output.                                                |

| DBG_SWDIO                         | PF1       | PF1  | PF1  | PF1     |     |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull up.             |

|                                   |           |      |      |         |     |   |   | Debug-interface Serial Wire viewer Output.                                                      |

| DBG_SWO                           | PF2       | PC15 | PD1  | PD2     |     |   |   | Note that this function is not enabled after reset, and must be enabled by software to be used. |

| ETM_TCLK                          | PD7       |      | PC6  | PA6     |     |   |   | Embedded Trace Module ETM clock .                                                               |

| ETM_TD0                           | PD6       |      | PC7  | PA2     |     |   |   | Embedded Trace Module ETM data 0.                                                               |

| ETM_TD1                           | PD3       |      | PD3  | PA3     |     |   |   | Embedded Trace Module ETM data 1.                                                               |

| ETM_TD2                           | PD4       |      | PD4  | PA4     |     |   |   | Embedded Trace Module ETM data 2.                                                               |

| ETM_TD3                           | PD5       | PF3  | PD5  | PA5     |     |   |   | Embedded Trace Module ETM data 3.                                                               |

| GPIO_EM4WU0                       | PA0       |      |      |         |     |   |   | Pin can be used to wake the system up from EM4                                                  |

| GPIO_EM4WU1                       | PA6       |      |      |         |     |   |   | Pin can be used to wake the system up from EM4                                                  |

| QFP6  | 64 Pin# and Name |                            | Pin Alternate Funct             | ionality / Description               |                                            |

|-------|------------------|----------------------------|---------------------------------|--------------------------------------|--------------------------------------------|

| Pin # | Pin Name         | Analog                     | Timers                          | Communication                        | Other                                      |

| 49    | PF0              |                            | TIM0_CC0 #5 LE-<br>TIM0_OUT0 #2 | US1_CLK #2 LEU0_TX<br>#3 I2C0_SDA #5 | DBG_SWCLK #0/1/2/3                         |

| 50    | PF1              |                            | TIM0_CC1 #5 LE-<br>TIM0_OUT1 #2 | US1_CS #2 LEU0_RX<br>#3 I2C0_SCL #5  | DBG_SWDIO #0/1/2/3<br>GPIO_EM4WU3          |

| 51    | PF2              |                            | TIM0_CC2 #5                     | LEU0_TX #4                           | ACMP1_O #0<br>DBG_SWO #0<br>GPIO_EM4WU4    |

| 52    | PF3              |                            | TIM0_CDTI0 #2/5                 |                                      | PRS_CH0 #1 ETM_TD3<br>#1                   |

| 53    | PF4              |                            | TIM0_CDTI1 #2/5                 |                                      | PRS_CH1 #1                                 |

| 54    | PF5              |                            | TIM0_CDTI2 #2/5                 |                                      | PRS_CH2 #1                                 |

| 55    | IOVDD_5          | Digital IO power supply 5. |                                 |                                      |                                            |

| 56    | VSS              | Ground.                    |                                 |                                      |                                            |

| 57    | PE8              |                            | PCNT2_S0IN #1                   |                                      | PRS_CH3 #1                                 |

| 58    | PE9              |                            | PCNT2_S1IN #1                   |                                      |                                            |

| 59    | PE10             |                            | TIM1_CC0 #1                     | US0_TX #0                            | BOOT_TX                                    |

| 60    | PE11             |                            | TIM1_CC1 #1                     | US0_RX #0                            | LES_ALTEX5 #0<br>BOOT_RX                   |

| 61    | PE12             |                            | TIM1_CC2 #1                     | US0_RX #3 US0_CLK<br>#0 I2C0_SDA #6  | CMU_CLK1 #2<br>LES_ALTEX6 #0               |

| 62    | PE13             |                            |                                 | US0_TX #3 US0_CS #0<br>I2C0_SCL #6   | LES_ALTEX7 #0<br>ACMP0_O #0<br>GPIO_EM4WU5 |

| 63    | PE14             |                            | TIM3_CC0 #0                     | LEU0_TX #2                           |                                            |

| 64    | PE15             |                            | TIM3_CC1 #0                     | LEU0_RX #2                           |                                            |

## 5.7.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     |      |   | L   | OCATIO | DN |   |   |                                                           |

|---------------|------|---|-----|--------|----|---|---|-----------------------------------------------------------|

| Functionality | 0    | 1 | 2   | 3      | 4  | 5 | 6 | Description                                               |

| ACMP0_CH0     | PC0  |   |     |        |    |   |   | Analog comparator ACMP0, channel 0.                       |

| ACMP0_CH1     | PC1  |   |     |        |    |   |   | Analog comparator ACMP0, channel 1.                       |

| ACMP0_CH2     | PC2  |   |     |        |    |   |   | Analog comparator ACMP0, channel 2.                       |

| ACMP0_CH3     | PC3  |   |     |        |    |   |   | Analog comparator ACMP0, channel 3.                       |

| ACMP0_CH4     | PC4  |   |     |        |    |   |   | Analog comparator ACMP0, channel 4.                       |

| ACMP0_CH5     | PC5  |   |     |        |    |   |   | Analog comparator ACMP0, channel 5.                       |

| ACMP0_CH6     | PC6  |   |     |        |    |   |   | Analog comparator ACMP0, channel 6.                       |

| ACMP0_CH7     | PC7  |   |     |        |    |   |   | Analog comparator ACMP0, channel 7.                       |

| ACMP0_O       | PE13 |   | PD6 |        |    |   |   | Analog comparator ACMP0, digital output.                  |

| ACMP1_CH0     | PC8  |   |     |        |    |   |   | Analog comparator ACMP1, channel 0.                       |

| ACMP1_CH1     | PC9  |   |     |        |    |   |   | Analog comparator ACMP1, channel 1.                       |

| ACMP1_CH2     | PC10 |   |     |        |    |   |   | Analog comparator ACMP1, channel 2.                       |

| ACMP1_CH3     | PC11 |   |     |        |    |   |   | Analog comparator ACMP1, channel 3.                       |

| ACMP1_0       | PF2  |   | PD7 |        |    |   |   | Analog comparator ACMP1, digital output.                  |

| ADC0_CH0      | PD0  |   |     |        |    |   |   | Analog to digital converter ADC0, input channel number 0. |

| ADC0_CH1      | PD1  |   |     |        |    |   |   | Analog to digital converter ADC0, input channel number 1. |

| ADC0_CH2      | PD2  |   |     |        |    |   |   | Analog to digital converter ADC0, input channel number 2. |

| ADC0_CH3      | PD3  |   |     |        |    |   |   | Analog to digital converter ADC0, input channel number 3. |

| ADC0_CH4      | PD4  |   |     |        |    |   |   | Analog to digital converter ADC0, input channel number 4. |

| ADC0_CH5      | PD5  |   |     |        |    |   |   | Analog to digital converter ADC0, input channel number 5. |

| ADC0_CH6      | PD6  |   |     |        |    |   |   | Analog to digital converter ADC0, input channel number 6. |

| ADC0_CH7      | PD7  |   |     |        |    |   |   | Analog to digital converter ADC0, input channel number 7. |

| BOOT_RX       | PE11 |   |     |        |    |   |   | Bootloader RX.                                            |

| BOOT_TX       | PE10 |   |     |        |    |   |   | Bootloader TX.                                            |

| BU_VIN        | PD8  |   |     |        |    |   |   | Battery input for Backup Power Domain                     |

## Table 5.20. Alternate functionality overview

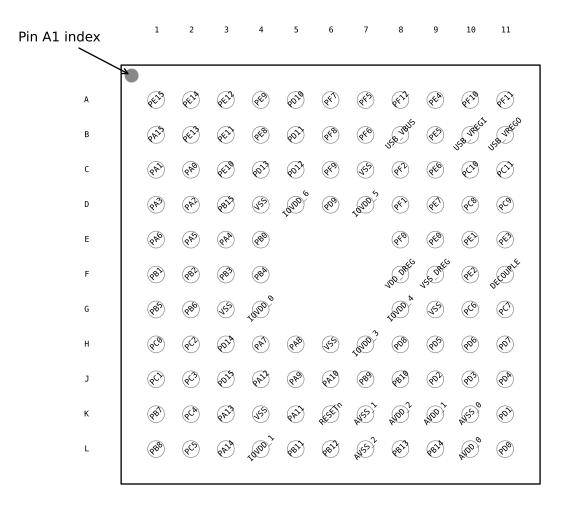

## 5.10 EFM32LG390 (BGA112)

#### 5.10.1 Pinout

The EFM32LG390 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.19. EFM32LG390 Pinout (top view, not to scale)

| Table 5.28. | Device | Pinout |

|-------------|--------|--------|

|-------------|--------|--------|

| BG    | A112 Pin# and<br>Name | Pin Alternate Functionality / Description |                 |             |               |       |  |  |  |  |

|-------|-----------------------|-------------------------------------------|-----------------|-------------|---------------|-------|--|--|--|--|

| Pin # | Pin Name              | Analog                                    | EBI             | Timers      | Communication | Other |  |  |  |  |

| A1    | PE15                  |                                           | EBI_AD07 #0/1/2 | TIM3_CC1 #0 | LEU0_RX #2    |       |  |  |  |  |

| A2    | PE14                  |                                           | EBI_AD06 #0/1/2 | TIM3_CC0 #0 | LEU0_TX #2    |       |  |  |  |  |

| Alternate     |      |      |      | LOCATIO | ON   |      |   |                                                                                                                         |

|---------------|------|------|------|---------|------|------|---|-------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3       | 4    | 5    | 6 | Description                                                                                                             |

| LEU0_TX       | PD4  | PB13 | PE14 | PF0     | PF2  |      |   | LEUART0 Transmit output. Also used as receive in-<br>put in half duplex communication.                                  |

| LEU1_RX       | PC7  |      |      |         |      |      |   | LEUART1 Receive input.                                                                                                  |

| LEU1_TX       | PC6  | PA5  |      |         |      |      |   | LEUART1 Transmit output. Also used as receive in-<br>put in half duplex communication.                                  |

| LFXTAL_N      | PB8  |      |      |         |      |      |   | Low Frequency Crystal (typically 32.768 kHz) nega-<br>tive pin. Also used as an optional external clock in-<br>put pin. |

| LFXTAL_P      | PB7  |      |      |         |      |      |   | Low Frequency Crystal (typically 32.768 kHz) posi-<br>tive pin.                                                         |

| PCNT0_S0IN    | PC13 |      |      | PD6     |      |      |   | Pulse Counter PCNT0 input number 0.                                                                                     |

| PCNT0_S1IN    | PC14 |      |      | PD7     |      |      |   | Pulse Counter PCNT0 input number 1.                                                                                     |

| PCNT1_S0IN    | PC4  | PB3  |      |         |      |      |   | Pulse Counter PCNT1 input number 0.                                                                                     |

| PCNT1_S1IN    | PC5  | PB4  |      |         |      |      |   | Pulse Counter PCNT1 input number 1.                                                                                     |

| PCNT2_S0IN    | PD0  | PE8  |      |         |      |      |   | Pulse Counter PCNT2 input number 0.                                                                                     |

| PCNT2_S1IN    | PD1  | PE9  |      |         |      |      |   | Pulse Counter PCNT2 input number 1.                                                                                     |

| PRS_CH0       | PA0  | PF3  |      |         |      |      |   | Peripheral Reflex System PRS, channel 0.                                                                                |

| PRS_CH1       | PA1  | PF4  |      |         |      |      |   | Peripheral Reflex System PRS, channel 1.                                                                                |

| PRS_CH2       |      | PF5  |      |         |      |      |   | Peripheral Reflex System PRS, channel 2.                                                                                |

| PRS_CH3       |      | PE8  |      |         |      |      |   | Peripheral Reflex System PRS, channel 3.                                                                                |

| TIM0_CC0      | PA0  | PA0  |      | PD1     | PA0  | PF0  |   | Timer 0 Capture Compare input / output channel 0.                                                                       |

| TIM0_CC1      | PA1  | PA1  |      | PD2     |      | PF1  |   | Timer 0 Capture Compare input / output channel 1.                                                                       |

| TIM0_CC2      | PA2  | PA2  |      | PD3     |      | PF2  |   | Timer 0 Capture Compare input / output channel 2.                                                                       |

| TIM0_CDTI0    | PA3  | PC13 | PF3  | PC13    |      | PF3  |   | Timer 0 Complimentary Deat Time Insertion channel 0.                                                                    |

| TIM0_CDTI1    | PA4  | PC14 | PF4  | PC14    |      | PF4  |   | Timer 0 Complimentary Deat Time Insertion channel 1.                                                                    |

| TIM0_CDTI2    | PA5  | PC15 | PF5  | PC15    | PC4  | PF5  |   | Timer 0 Complimentary Deat Time Insertion channel 2.                                                                    |

| TIM1_CC0      | PC13 | PE10 |      | PB7     | PD6  |      |   | Timer 1 Capture Compare input / output channel 0.                                                                       |

| TIM1_CC1      | PC14 | PE11 |      | PB8     | PD7  |      |   | Timer 1 Capture Compare input / output channel 1.                                                                       |

| TIM1_CC2      | PC15 | PE12 |      | PB11    |      |      |   | Timer 1 Capture Compare input / output channel 2.                                                                       |

| TIM2_CC0      |      | PA12 |      |         |      |      |   | Timer 2 Capture Compare input / output channel 0.                                                                       |

| TIM2_CC1      |      | PA13 |      |         |      |      |   | Timer 2 Capture Compare input / output channel 1.                                                                       |

| TIM2_CC2      |      | PA14 |      |         |      |      |   | Timer 2 Capture Compare input / output channel 2.                                                                       |

| TIM3_CC0      | PE14 |      |      |         |      |      |   | Timer 3 Capture Compare input / output channel 0.                                                                       |

| TIM3_CC1      | PE15 |      |      |         |      |      |   | Timer 3 Capture Compare input / output channel 1.                                                                       |

| US0_CLK       | PE12 | PE5  |      | PC15    | PB13 | PB13 |   | USART0 clock input / output.                                                                                            |

| US0_CS        | PE13 | PE4  |      | PC14    | PB14 | PB14 |   | USART0 chip select input / output.                                                                                      |

| Alternate                         |      |      | l    |      | ON  |   |   |                                                                                                 |

|-----------------------------------|------|------|------|------|-----|---|---|-------------------------------------------------------------------------------------------------|

| Functionality                     | 0    | 1    | 2    | 3    | 4   | 5 | 6 | Description                                                                                     |

| ADC0_CH7                          | PD7  |      |      |      |     |   |   | Analog to digital converter ADC0, input channel number 7.                                       |

| BOOT_RX                           | PE11 |      |      |      |     |   |   | Bootloader RX.                                                                                  |

| BOOT_TX                           | PE10 |      |      |      |     |   |   | Bootloader TX.                                                                                  |

| BU_STAT                           | PE3  |      |      |      |     |   |   | Backup Power Domain status, whether or not the system is in backup mode                         |

| BU_VIN                            | PD8  |      |      |      |     |   |   | Battery input for Backup Power Domain                                                           |

| BU_VOUT                           | PE2  |      |      |      |     |   |   | Power output for Backup Power Domain                                                            |

| CMU_CLK0                          | PA2  | PC12 | PD7  |      |     |   |   | Clock Management Unit, clock output number 0.                                                   |

| CMU_CLK1                          | PA1  | PD8  | PE12 |      |     |   |   | Clock Management Unit, clock output number 1.                                                   |

| OPAMP_N0                          | PC5  |      |      |      |     |   |   | Operational Amplifier 0 external negative input.                                                |

| OPAMP_N1                          | PD7  |      |      |      |     |   |   | Operational Amplifier 1 external negative input.                                                |

| OPAMP_N2                          | PD3  |      |      |      |     |   |   | Operational Amplifier 2 external negative input.                                                |

| DAC0_OUT0 /<br>OPAMP_OUT0         | PB11 |      |      |      |     |   |   | Digital to Analog Converter DAC0_OUT0 /OPAMP output channel number 0.                           |

| DAC0_OUT0ALT<br>OPAMP_OUT0A<br>LT |      | PC1  | PC2  | PC3  | PD0 |   |   | Digital to Analog Converter DAC0_OUT0ALT /<br>OPAMP alternative output for channel 0.           |

| DAC0_OUT1 /<br>OPAMP_OUT1         | PB12 |      |      |      |     |   |   | Digital to Analog Converter DAC0_OUT1 /OPAMP output channel number 1.                           |

| DAC0_OUT1ALT<br>OPAMP_OUT1A<br>LT |      | PC13 | PC14 | PC15 | PD1 |   |   | Digital to Analog Converter DAC0_OUT1ALT /<br>OPAMP alternative output for channel 1.           |

| OPAMP_OUT2                        | PD5  | PD0  |      |      |     |   |   | Operational Amplifier 2 output.                                                                 |

| OPAMP_P0                          | PC4  |      |      |      |     |   |   | Operational Amplifier 0 external positive input.                                                |

| OPAMP_P1                          | PD6  |      |      |      |     |   |   | Operational Amplifier 1 external positive input.                                                |

| OPAMP_P2                          | PD4  |      |      |      |     |   |   | Operational Amplifier 2 external positive input.                                                |

|                                   |      |      |      |      |     |   |   | Debug-interface Serial Wire clock input.                                                        |

| DBG_SWCLK                         | PF0  | PF0  | PF0  | PF0  |     |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull down.           |

|                                   |      |      |      |      |     |   |   | Debug-interface Serial Wire data input / output.                                                |

| DBG_SWDIO                         | PF1  | PF1  | PF1  | PF1  |     |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull up.             |

|                                   |      |      |      |      |     |   |   | Debug-interface Serial Wire viewer Output.                                                      |

| DBG_SWO                           | PF2  |      | PD1  | PD2  |     |   |   | Note that this function is not enabled after reset, and must be enabled by software to be used. |

| EBI_A00                           | PA12 | PA12 | PA12 |      |     |   |   | External Bus Interface (EBI) address output pin 00.                                             |

| EBI_A01                           | PA13 | PA13 | PA13 |      |     |   |   | External Bus Interface (EBI) address output pin 01.                                             |

| EBI_A02                           | PA14 | PA14 | PA14 |      |     |   |   | External Bus Interface (EBI) address output pin 02.                                             |

| EBI_A03                           | PB9  | PB9  | PB9  |      |     |   |   | External Bus Interface (EBI) address output pin 03.                                             |

| Alternate              |      |   | L | OCATIO | N |   |   |                                                                                                                       |

|------------------------|------|---|---|--------|---|---|---|-----------------------------------------------------------------------------------------------------------------------|

| Functionality          | 0    | 1 | 2 | 3      | 4 | 5 | 6 | Description                                                                                                           |

| LCD_SEG22/<br>LCD_COM6 | PB5  |   |   |        |   |   |   | LCD segment line 22. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 6 |

| LCD_SEG23/<br>LCD_COM7 | PB6  |   |   |        |   |   |   | LCD segment line 23. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 7 |

| LCD_SEG24              | PF6  |   |   |        |   |   |   | LCD segment line 24. Segments 24, 25, 26 and 27 are controlled by SEGEN6.                                             |

| LCD_SEG25              | PF7  |   |   |        |   |   |   | LCD segment line 25. Segments 24, 25, 26 and 27 are controlled by SEGEN6.                                             |

| LCD_SEG26              | PF8  |   |   |        |   |   |   | LCD segment line 26. Segments 24, 25, 26 and 27 are controlled by SEGEN6.                                             |

| LCD_SEG27              | PF9  |   |   |        |   |   |   | LCD segment line 27. Segments 24, 25, 26 and 27 are controlled by SEGEN6.                                             |

| LCD_SEG28              | PD9  |   |   |        |   |   |   | LCD segment line 28. Segments 28, 29, 30 and 31 are controlled by SEGEN7.                                             |

| LCD_SEG29              | PD10 |   |   |        |   |   |   | LCD segment line 29. Segments 28, 29, 30 and 31 are controlled by SEGEN7.                                             |

| LCD_SEG30              | PD11 |   |   |        |   |   |   | LCD segment line 30. Segments 28, 29, 30 and 31 are controlled by SEGEN7.                                             |

| LCD_SEG31              | PD12 |   |   |        |   |   |   | LCD segment line 31. Segments 28, 29, 30 and 31 are controlled by SEGEN7.                                             |

| LCD_SEG32              | PB0  |   |   |        |   |   |   | LCD segment line 32. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                             |

| LCD_SEG33              | PB1  |   |   |        |   |   |   | LCD segment line 33. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                             |

| LCD_SEG34              | PB2  |   |   |        |   |   |   | LCD segment line 34. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                             |

| LCD_SEG35              | PA7  |   |   |        |   |   |   | LCD segment line 35. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                             |

| LCD_SEG36              | PA8  |   |   |        |   |   |   | LCD segment line 36. Segments 36, 37, 38 and 39 are controlled by SEGEN9.                                             |

| LCD_SEG37              | PA9  |   |   |        |   |   |   | LCD segment line 37. Segments 36, 37, 38 and 39 are controlled by SEGEN9.                                             |

| LCD_SEG38              | PA10 |   |   |        |   |   |   | LCD segment line 38. Segments 36, 37, 38 and 39 are controlled by SEGEN9.                                             |

| LCD_SEG39              | PA11 |   |   |        |   |   |   | LCD segment line 39. Segments 36, 37, 38 and 39 are controlled by SEGEN9.                                             |

| LES_ALTEX0             | PD6  |   |   |        |   |   |   | LESENSE alternate exite output 0.                                                                                     |

| LES_ALTEX1             | PD7  |   |   |        |   |   |   | LESENSE alternate exite output 1.                                                                                     |

| LES_ALTEX2             | PA3  |   |   |        |   |   |   | LESENSE alternate exite output 2.                                                                                     |

| LES_ALTEX3             | PA4  |   |   |        |   |   |   | LESENSE alternate exite output 3.                                                                                     |

| LES_ALTEX4             | PA5  |   |   |        |   |   |   | LESENSE alternate exite output 4.                                                                                     |

| LES_ALTEX5             | PE11 |   |   |        |   |   |   | LESENSE alternate exite output 5.                                                                                     |

| BG    | A120 Pin# and<br>Name | Pin Alternate Functionality / Description |                 |                                 |                                        |                                            |  |  |  |  |

|-------|-----------------------|-------------------------------------------|-----------------|---------------------------------|----------------------------------------|--------------------------------------------|--|--|--|--|

| Pin # | Pin Name              | Analog                                    | EBI             | Timers                          | Communication                          | Other                                      |  |  |  |  |

| A3    | PE12                  | LCD_SEG8                                  | EBI_AD04 #0/1/2 | TIM1_CC2 #1                     | US0_RX #3<br>US0_CLK #0<br>I2C0_SDA #6 | CMU_CLK1 #2<br>LES_ALTEX6 #0               |  |  |  |  |

| A4    | PE9                   | LCD_SEG5                                  | EBI_AD01 #0/1/2 | PCNT2_S1IN #1                   |                                        |                                            |  |  |  |  |

| A5    | PD11                  | LCD_SEG30                                 | EBI_CS2 #0/1/2  |                                 |                                        |                                            |  |  |  |  |

| A6    | PD9                   | LCD_SEG28                                 | EBI_CS0 #0/1/2  |                                 |                                        |                                            |  |  |  |  |

| A7    | PF7                   | LCD_SEG25                                 | EBI_BL1 #0/1/2  | TIM0_CC1 #2                     | U0_RX #0                               |                                            |  |  |  |  |

| A8    | PF5                   | LCD_SEG3                                  | EBI_REn #0/2    | TIM0_CDTI2 #2/5                 |                                        | PRS_CH2 #1                                 |  |  |  |  |

| A9    | PF4                   | LCD_SEG2                                  | EBI_WEn #0/2    | TIM0_CDTI1 #2/5                 |                                        | PRS_CH1 #1                                 |  |  |  |  |

| A10   | PF2                   | LCD_SEG0                                  | EBI_ARDY #0/1/2 | TIM0_CC2 #5                     | LEU0_TX #4                             | ACMP1_O #0<br>DBG_SWO #0<br>GPIO_EM4WU4    |  |  |  |  |

| A11   | USB_VREGI             |                                           |                 |                                 |                                        |                                            |  |  |  |  |

| A12   | USB_VREGO             |                                           |                 |                                 |                                        |                                            |  |  |  |  |

| A13   | PF11                  |                                           |                 |                                 |                                        |                                            |  |  |  |  |

| B1    | PA15                  | LCD_SEG12                                 | EBI_AD08 #0/1/2 | TIM3_CC2 #0                     |                                        |                                            |  |  |  |  |

| B2    | PE13                  | LCD_SEG9                                  | EBI_AD05 #0/1/2 |                                 | US0_TX #3<br>US0_CS #0<br>I2C0_SCL #6  | LES_ALTEX7 #0<br>ACMP0_O #0<br>GPIO_EM4WU5 |  |  |  |  |

| B3    | PE11                  | LCD_SEG7                                  | EBI_AD03 #0/1/2 | TIM1_CC1 #1                     | US0_RX #0                              | LES_ALTEX5 #0<br>BOOT_RX                   |  |  |  |  |

| B4    | PE8                   | LCD_SEG4                                  | EBI_AD00 #0/1/2 | PCNT2_S0IN #1                   |                                        | PRS_CH3 #1                                 |  |  |  |  |

| B5    | PD12                  | LCD_SEG31                                 | EBI_CS3 #0/1/2  |                                 |                                        |                                            |  |  |  |  |

| B6    | PD10                  | LCD_SEG29                                 | EBI_CS1 #0/1/2  |                                 |                                        |                                            |  |  |  |  |

| B7    | PF8                   | LCD_SEG26                                 | EBI_WEn #1      | TIM0_CC2 #2                     |                                        | ETM_TCLK #1                                |  |  |  |  |

| B8    | PF6                   | LCD_SEG24                                 | EBI_BL0 #0/1/2  | TIM0_CC0 #2                     | U0_TX #0                               |                                            |  |  |  |  |

| В9    | PF3                   | LCD_SEG1                                  | EBI_ALE #0      | TIM0_CDTI0 #2/5                 |                                        | PRS_CH0 #1<br>ETM_TD3 #1                   |  |  |  |  |

| B10   | PF1                   |                                           |                 | TIM0_CC1 #5 LE-<br>TIM0_OUT1 #2 | US1_CS #2<br>LEU0_RX #3<br>I2C0_SCL #5 | DBG_SWDIO<br>#0/1/2/3<br>GPIO_EM4WU3       |  |  |  |  |

| B11   | PF12                  |                                           |                 |                                 |                                        |                                            |  |  |  |  |

| B12   | USB_VBUS              | USB 5.0 V VBUS inp                        | but.            |                                 |                                        |                                            |  |  |  |  |

| B13   | PF10                  |                                           |                 |                                 | U1_TX #1                               |                                            |  |  |  |  |

| C1    | PA1                   | LCD_SEG14                                 | EBI_AD10 #0/1/2 | TIM0_CC1 #0/1                   | I2C0_SCL #0                            | CMU_CLK1 #0<br>PRS_CH1 #0                  |  |  |  |  |

| C2    | PA0                   | LCD_SEG13                                 | EBI_AD09 #0/1/2 | TIM0_CC0 #0/1/4                 | LEU0_RX #4<br>I2C0_SDA #0              | PRS_CH0 #0<br>GPIO_EM4WU0                  |  |  |  |  |

| C3    | PE10                  | LCD_SEG6                                  | EBI_AD02 #0/1/2 | TIM1_CC0 #1                     | US0_TX #0                              | BOOT_TX                                    |  |  |  |  |

| C4    | PD13                  |                                           |                 |                                 |                                        | ETM_TD1 #1                                 |  |  |  |  |

| Alternate              | LOCATION |   |   |   | N |   |   |                                                                                                                       |

|------------------------|----------|---|---|---|---|---|---|-----------------------------------------------------------------------------------------------------------------------|

| Functionality          | 0        | 1 | 2 | 3 | 4 | 5 | 6 | Description                                                                                                           |

| LCD_SEG7               | PE11     |   |   |   |   |   |   | LCD segment line 7. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                  |

| LCD_SEG8               | PE12     |   |   |   |   |   |   | LCD segment line 8. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                                |

| LCD_SEG9               | PE13     |   |   |   |   |   |   | LCD segment line 9. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                                |

| LCD_SEG10              | PE14     |   |   |   |   |   |   | LCD segment line 10. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                               |

| LCD_SEG11              | PE15     |   |   |   |   |   |   | LCD segment line 11. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                               |

| LCD_SEG12              | PA15     |   |   |   |   |   |   | LCD segment line 12. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                             |

| LCD_SEG13              | PA0      |   |   |   |   |   |   | LCD segment line 13. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                             |

| LCD_SEG14              | PA1      |   |   |   |   |   |   | LCD segment line 14. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                             |

| LCD_SEG15              | PA2      |   |   |   |   |   |   | LCD segment line 15. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                             |

| LCD_SEG16              | PA3      |   |   |   |   |   |   | LCD segment line 16. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                             |

| LCD_SEG17              | PA4      |   |   |   |   |   |   | LCD segment line 17. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                             |

| LCD_SEG18              | PA5      |   |   |   |   |   |   | LCD segment line 18. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                             |

| LCD_SEG19              | PA6      |   |   |   |   |   |   | LCD segment line 19. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                             |

| LCD_SEG20/<br>LCD_COM4 | PB3      |   |   |   |   |   |   | LCD segment line 20. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 4 |

| LCD_SEG21/<br>LCD_COM5 | PB4      |   |   |   |   |   |   | LCD segment line 21. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 5 |

| LCD_SEG22/<br>LCD_COM6 | PB5      |   |   |   |   |   |   | LCD segment line 22. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 6 |

| LCD_SEG23/<br>LCD_COM7 | PB6      |   |   |   |   |   |   | LCD segment line 23. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 7 |

| LCD_SEG24              | PF6      |   |   |   |   |   |   | LCD segment line 24. Segments 24, 25, 26 and 27 are controlled by SEGEN6.                                             |

| LCD_SEG25              | PF7      |   |   |   |   |   |   | LCD segment line 25. Segments 24, 25, 26 and 27 are controlled by SEGEN6.                                             |

| LCD_SEG26              | PF8      |   |   |   |   |   |   | LCD segment line 26. Segments 24, 25, 26 and 27 are controlled by SEGEN6.                                             |

| LCD_SEG27              | PF9      |   |   |   |   |   |   | LCD segment line 27. Segments 24, 25, 26 and 27 are controlled by SEGEN6.                                             |

| Alternate     | rnate LOCATION |      |     |      |     |     |      |                                                                                                                                                                                                                                           |

|---------------|----------------|------|-----|------|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0              | 1    | 2   | 3    | 4   | 5   | 6    | Description                                                                                                                                                                                                                               |

| ETM_TD3       | PD5            |      | PD5 | PA5  |     |     |      | Embedded Trace Module ETM data 3.                                                                                                                                                                                                         |

| GPIO_EM4WU0   | PA0            |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                                                                                            |

| GPIO_EM4WU1   | PA6            |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                                                                                            |

| GPIO_EM4WU2   | PC9            |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                                                                                            |

| GPIO_EM4WU3   | PF1            |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                                                                                            |

| GPIO_EM4WU4   | PF2            |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                                                                                            |

| GPIO_EM4WU5   | PE13           |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                                                                                            |

| HFXTAL_N      | PB14           |      |     |      |     |     |      | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                                                                                      |

| HFXTAL_P      | PB13           |      |     |      |     |     |      | High Frequency Crystal positive pin.                                                                                                                                                                                                      |

| I2C0_SCL      | PA1            | PD7  | PC7 | PD15 | PC1 | PF1 | PE13 | I2C0 Serial Clock Line input / output.                                                                                                                                                                                                    |

| I2C0_SDA      | PA0            | PD6  | PC6 | PD14 | PC0 | PF0 | PE12 | I2C0 Serial Data input / output.                                                                                                                                                                                                          |

| I2C1_SCL      | PC5            | PB12 | PE1 |      |     |     |      | I2C1 Serial Clock Line input / output.                                                                                                                                                                                                    |

| I2C1_SDA      | PC4            | PB11 | PE0 |      |     |     |      | I2C1 Serial Data input / output.                                                                                                                                                                                                          |

| LCD_BCAP_N    | PA13           |      |     |      |     |     |      | LCD voltage booster (optional), boost capacitor,<br>negative pin. If using the LCD voltage booster, con-<br>nect a 22 nF capacitor between LCD_BCAP_N and<br>LCD_BCAP_P.                                                                  |

| LCD_BCAP_P    | PA12           |      |     |      |     |     |      | LCD voltage booster (optional), boost capacitor,<br>positive pin. If using the LCD voltage booster, con-<br>nect a 22 nF capacitor between LCD_BCAP_N and<br>LCD_BCAP_P.                                                                  |

| LCD_BEXT      | PA14           |      |     |      |     |     |      | LCD voltage booster (optional), boost output. If us-<br>ing the LCD voltage booster, connect a 1 uF capaci-<br>tor between this pin and VSS.<br>An external LCD voltage may also be applied to this<br>pin if the booster is not enabled. |

|               |                |      |     |      |     |     |      | If AVDD is used directly as the LCD supply voltage,<br>this pin may be left unconnected or used as a GPIO.                                                                                                                                |

| LCD_COM0      | PE4            |      |     |      |     |     |      | LCD driver common line number 0.                                                                                                                                                                                                          |

| LCD_COM1      | PE5            |      |     |      |     |     |      | LCD driver common line number 1.                                                                                                                                                                                                          |

| LCD_COM2      | PE6            |      |     |      |     |     |      | LCD driver common line number 2.                                                                                                                                                                                                          |

| LCD_COM3      | PE7            |      |     |      |     |     |      | LCD driver common line number 3.                                                                                                                                                                                                          |

| LCD_SEG0      | PF2            |      |     |      |     |     |      | LCD segment line 0. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                      |

| LCD_SEG3      | PF5            |      |     |      |     |     |      | LCD segment line 3. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                      |

| LCD_SEG4      | PE8            |      |     |      |     |     |      | LCD segment line 4. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                      |

| LCD_SEG5      | PE9            |      |     |      |     |     |      | LCD segment line 5. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                      |

| LCD_SEG6      | PE10           |      |     |      |     |     |      | LCD segment line 6. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                      |

| Alternate     | LOCATION |   |   |   | N |   |   |                                                                           |

|---------------|----------|---|---|---|---|---|---|---------------------------------------------------------------------------|

| Functionality | 0        | 1 | 2 | 3 | 4 | 5 | 6 | Description                                                               |

| LCD_SEG25     | PF7      |   |   |   |   |   |   | LCD segment line 25. Segments 24, 25, 26 and 27 are controlled by SEGEN6. |

| LCD_SEG26     | PF8      |   |   |   |   |   |   | LCD segment line 26. Segments 24, 25, 26 and 27 are controlled by SEGEN6. |

| LCD_SEG27     | PF9      |   |   |   |   |   |   | LCD segment line 27. Segments 24, 25, 26 and 27 are controlled by SEGEN6. |

| LCD_SEG28     | PD9      |   |   |   |   |   |   | LCD segment line 28. Segments 28, 29, 30 and 31 are controlled by SEGEN7. |

| LCD_SEG29     | PD10     |   |   |   |   |   |   | LCD segment line 29. Segments 28, 29, 30 and 31 are controlled by SEGEN7. |

| LCD_SEG30     | PD11     |   |   |   |   |   |   | LCD segment line 30. Segments 28, 29, 30 and 31 are controlled by SEGEN7. |

| LCD_SEG31     | PD12     |   |   |   |   |   |   | LCD segment line 31. Segments 28, 29, 30 and 31 are controlled by SEGEN7. |

| LCD_SEG32     | PB0      |   |   |   |   |   |   | LCD segment line 32. Segments 32, 33, 34 and 35 are controlled by SEGEN8. |

| LCD_SEG33     | PB1      |   |   |   |   |   |   | LCD segment line 33. Segments 32, 33, 34 and 35 are controlled by SEGEN8. |

| LCD_SEG34     | PB2      |   |   |   |   |   |   | LCD segment line 34. Segments 32, 33, 34 and 35 are controlled by SEGEN8. |

| LCD_SEG35     | PA7      |   |   |   |   |   |   | LCD segment line 35. Segments 32, 33, 34 and 35 are controlled by SEGEN8. |

| LCD_SEG36     | PA8      |   |   |   |   |   |   | LCD segment line 36. Segments 36, 37, 38 and 39 are controlled by SEGEN9. |

| LCD_SEG37     | PA9      |   |   |   |   |   |   | LCD segment line 37. Segments 36, 37, 38 and 39 are controlled by SEGEN9. |

| LCD_SEG38     | PA10     |   |   |   |   |   |   | LCD segment line 38. Segments 36, 37, 38 and 39 are controlled by SEGEN9. |

| LCD_SEG39     | PA11     |   |   |   |   |   |   | LCD segment line 39. Segments 36, 37, 38 and 39 are controlled by SEGEN9. |

| LES_ALTEX0    | PD6      |   |   |   |   |   |   | LESENSE alternate exite output 0.                                         |

| LES_ALTEX1    | PD7      |   |   |   |   |   |   | LESENSE alternate exite output 1.                                         |

| LES_ALTEX2    | PA3      |   |   |   |   |   |   | LESENSE alternate exite output 2.                                         |

| LES_ALTEX3    | PA4      |   |   |   |   |   |   | LESENSE alternate exite output 3.                                         |

| LES_ALTEX4    | PA5      |   |   |   |   |   |   | LESENSE alternate exite output 4.                                         |

| LES_ALTEX5    | PE11     |   |   |   |   |   |   | LESENSE alternate exite output 5.                                         |

| LES_ALTEX6    | PE12     |   |   |   |   |   |   | LESENSE alternate exite output 6.                                         |

| LES_ALTEX7    | PE13     |   |   |   |   |   |   | LESENSE alternate exite output 7.                                         |

| LES_CH0       | PC0      |   |   |   |   |   |   | LESENSE channel 0.                                                        |

| LES_CH1       | PC1      |   |   |   |   |   |   | LESENSE channel 1.                                                        |

| LES_CH2       | PC2      |   |   |   |   |   |   | LESENSE channel 2.                                                        |

| LES_CH3       | PC3      |   |   |   |   |   |   | LESENSE channel 3.                                                        |

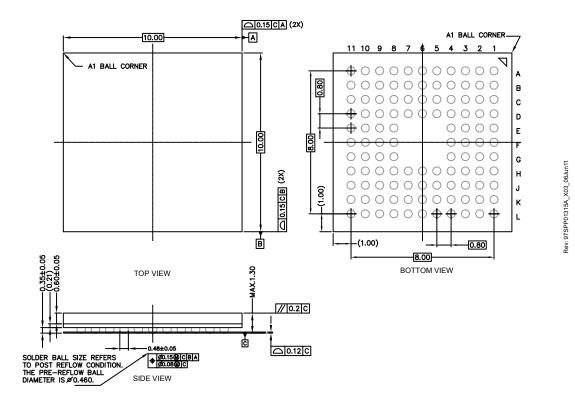

# 6. BGA112 Package Specifications

# 6.1 BGA112 Package Dimensions

Figure 6.1. BGA112

#### Note:

- 1. The dimensions in parenthesis are reference.

- 2. Datum 'C' and seating plane are defined by the crown of the solder balls.

- 3. All dimensions are in millimeters.

The BGA112 Package uses SAC105 solderballs.

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx.

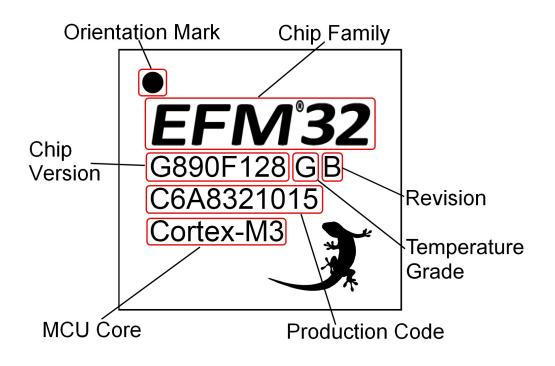

# 10.3 TQFP64 Package Marking

In the illustration below package fields and position are shown.

Figure 10.5. Example Chip Marking (Top View)

| Symbol | Min      | Nom  | Мах  |  |  |  |  |  |  |

|--------|----------|------|------|--|--|--|--|--|--|

| e      | 0.50 BSC |      |      |  |  |  |  |  |  |

| L      | 0.40     | 0.45 | 0.50 |  |  |  |  |  |  |

| L1     | 0.00     | _    | 0.10 |  |  |  |  |  |  |

| ааа    | 0.10     |      |      |  |  |  |  |  |  |

| bbb    | 0.10     |      |      |  |  |  |  |  |  |

| ССС    | 0.10     |      |      |  |  |  |  |  |  |

| ddd    | 0.05     |      |      |  |  |  |  |  |  |

| eee    | 0.08     |      |      |  |  |  |  |  |  |

The QFN64 Package uses Nickel-Palladium-Gold preplated leadframe.

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx.

# 14. Revision History

### 14.1 Revision 2.00

April 17th, 2017

Consolidated all EFM32LG data sheets:

- EFM32LG230

- EFM32LG232

- EFM32LG280

- EFM32LG290

- EFM32LG295

- EFM32LG330

- EFM32LG332

- EFM32LG360

- EFM32LG380

- EFM32LG390

- EFM32LG395

- EFM32LG840

- EFM32LG842

- EFM32LG880

- EFM32LG890

- EFM32LG895

- EFM32LG900

- EFM32LG940

- EFM32LG942

- EFM32LG980

- EFM32LG990

- EFM32LG995

Added a Feature List section.

2. Ordering Information – Added ordering code decoder.

3.3 Memory Map – Separated the Memory Map into two figures – one for core and code space listing and one for peripheral listing.

4.2 Absolute Maximum Ratings - Removed the footnote about storage temperature and added max source/sink current per I/O pin.

Environmental - Removed this section. Environmental specifications are available in the qualification report.

4.4 Current Consumption - Added maximum current specifications for the highest energy mode, IEM0.

4.8 General Purpose Input Output - Reduced maximum input leakage current (I<sub>IOLEAK</sub>, max).

4.9.1 LFXO - Replaced "energyAware Designer" with "Configurator tool".

4.9.3 LFRCO – Added (min, typ, max) specifications for oscillation frequency over full power supply and full temperature range. Also added typical voltage drift and temperature drift specs.

4.9.3 LFRCO – Updated graphs for calibrated LFRCO Frequency vs. Temperature and Supply Range, and also fixed y-axis unit [kHz].

4.9.4 HFRCO – Added specifications for oscillation frequency over full power supply and temperature range, added typical voltage drift and temperature drift specs at each frequency band, and removed the duty cycle spec (DC<sub>HFRCO</sub>).

4.9.4 HFRCO – Updated all HFRCO graphs (various frequency bands).

4.9.6 ULFRCO – Removed the duty cycle spec for AUXHFRCO (DC<sub>AUXHFRCO</sub>).

# 4.10 Analog Digital Converter (ADC) – Added the following specs:

- Input bias current (I<sub>ADCBIASIN</sub>) added max (source and sink).

- Input offset current (I<sub>ADCOFFSETIN</sub>) added max (source and sink).

- VREF output voltage (V<sub>REF</sub>) added min, typ, max.