#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB                 |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                         |

| Number of I/O              | 53                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                            |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-WFQFN Exposed Pad                                                    |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32lg940f128-qfn64t |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

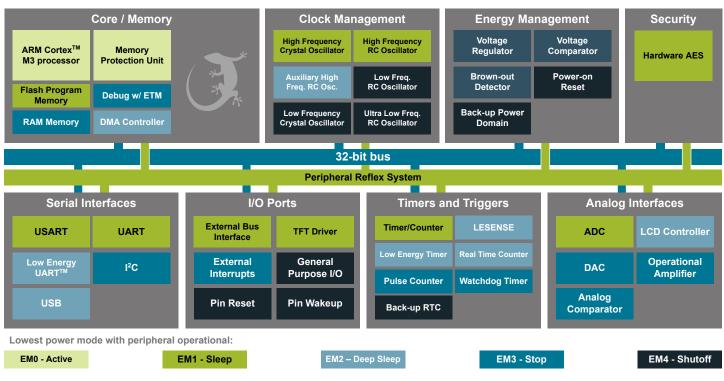

# 3. System Summary

## 3.1 System Introduction

The EFM32 MCUs are the world's most energy friendly microcontrollers. With a unique combination of the powerful 32-bit ARM Cortex-M3, innovative low energy techniques, short wake-up time from energy saving modes, and a wide selection of peripherals, the EFM32LG microcontroller is well suited for any battery operated application as well as other systems requiring high performance and low-energy consumption. This section gives a short introduction to each of the modules in general terms and also shows a summary of the configuration for the EFM32LG devices. For a complete feature set and in-depth information on the modules, the reader is referred to the EFM32LG Reference Manual.

A block diagram of the EFM32LG is shown in the following figure.

## 3.1.1 ARM Cortex-M3 Core

The ARM Cortex-M3 includes a 32-bit RISC processor which can achieve as much as 1.25 Dhrystone MIPS/MHz. A Memory Protection Unit with support for up to 8 memory segments is included, as well as a Wake-up Interrupt Controller handling interrupts triggered while the CPU is asleep. The EFM32 implementation of the Cortex-M3 is described in detail in EFM32LG Reference Manual.

## 3.1.2 Debug Interface (DBG)

This device includes hardware debug support through a 2-pin serial-wire debug interface and an Embedded Trace Module (ETM) for data/instruction tracing . In addition there is also a 1-wire Serial Wire Viewer pin which can be used to output profiling information, data trace and software-generated messages.

## 3.1.3 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the EFM32LG microcontroller. The flash memory is readable and writable from both the Cortex-M3 and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block. Additionally, the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in the energy modes EM0 and EM1.

| Module | Configuration      | Pin Connections                                                  |

|--------|--------------------|------------------------------------------------------------------|

| AES    | Full configuration | NA                                                               |

| GPIO   | 53 pins            | Available pins are shown in 5.13.3 GPIO Pinout Overview          |

| LCD    | Full configuration | LCD_SEG[17:0], LCD_COM[7:0], LCD_BCAP_P, LCD_BCAP_N,<br>LCD_BEXT |

EFM32LG Data Sheet System Summary

| Module | Configuration      | Pin Connections                                                   |

|--------|--------------------|-------------------------------------------------------------------|

| VCMP   | Full configuration | NA                                                                |

| ADC0   | Full configuration | ADC0_CH[7:0]                                                      |

| DAC0   | Full configuration | DAC0_OUT[1:0], DAC0_OUTxALT                                       |

| OPAMP  | Full configuration | Outputs: OPAMP_OUTx, OPAMP_OUTxALT, Inputs: OPAMP_Px,<br>OPAMP_Nx |

| AES    | Full configuration | NA                                                                |

| GPIO   | 93 pins            | Available pins are shown in Table 4.3 (p. 70)                     |

| LCD    | Full configuration | LCD_SEG[35:0], LCD_COM[7:0], LCD_BCAP_P, LCD_BCAP_N,<br>LCD_BEXT  |

## 4.11 Digital Analog Converter (DAC)

#### **Test Condition** Unit Parameter Symbol Min Typ Max Output voltage range 0 V VDD voltage reference, single ended V<sub>DD</sub> VDACOUT \_\_\_\_ V VDD voltage reference, differential -V<sub>DD</sub> VDD Output common mode voltage VDACCM 0 VDD V range 400<sup>1</sup> Active current including referen-IDAC 500 kSamples/s, 12 bit μA ces for 2 channels 100 kSamples/s, 12 bit 200<sup>1</sup> μA 1 kSamples/s 12 bit NORMAL 17<sup>1</sup> μΑ Sample rate SRDAC \_ \_\_\_\_ 500 ksamples/ s DAC clock frequency f<sub>DAC</sub> Continuous Mode 1000 kHz kHz Sample/Hold Mode 250 Sample/Off Mode 250 kHz CYC<sub>DAC-</sub> Clock cyckles per conversion 2 cycles CONV Conversion time **t**DACCONV 2 \_\_\_ \_\_\_\_ μs 5 Settling time tDACSETμs \_\_\_\_ TLE Signal to Noise Ratio (SNR) **SNR**DAC 500 kSamples/s, 12 bit, single ended, 58 dB internal 1.25V reference 500 kSamples/s, 12 bit, single ended, dB 59 internal 2.5V reference 500 kSamples/s, 12 bit, differential, in-58 dB \_\_\_\_ \_\_\_\_ ternal 1.25V reference 500 kSamples/s, 12 bit, differential, in-58 dB ternal 2.5V reference 500 kSamples/s, 12 bit, differential, 59 dB \_ \_\_\_\_ V<sub>DD</sub> reference Signal to Noisepulse Distortion **SNDR**DAC 500 kSamples/s, 12 bit, single ended, 57 dB Ratio (SNDR) internal 1.25V reference 500 kSamples/s, 12 bit, single ended, dB 54 internal 2.5V reference 500 kSamples/s, 12 bit, differential, indB 56 \_ \_\_\_\_ ternal 1.25V reference 500 kSamples/s, 12 bit, differential, indB 53 ternal 2.5V reference dB 500 kSamples/s, 12 bit, differential, 55 \_ \_\_\_\_ V<sub>DD</sub> reference

### Table 4.15. DAC

| Parameter                 | Symbol               | Test Condition                                              | Min | Тур                | Max | Unit |

|---------------------------|----------------------|-------------------------------------------------------------|-----|--------------------|-----|------|

| Gain Bandwidth<br>Product | GBW <sub>OPAMP</sub> | (OPA0)BIASPROG=0x0,(OPA0)HALF-<br>BIAS=0x1, DC bias = 0.3 V | _   | 0.393 <sup>1</sup> | —   | MHz  |

|                           |                      | (OPA0)BIASPROG=0x0,(OPA0)HALF-<br>BIAS=0x1, DC bias = 1 V   | -   | 0.487 <sup>1</sup> |     | MHz  |

|                           |                      | (OPA0)BIASPROG=0x0,(OPA0)HALF-<br>BIAS=0x1, DC bias = 2 V   | -   | 0.392 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA0)BIASPROG=0x0,(OPA0)HALF-<br>BIAS=0x1, DC bias = 2.7 V | _   | 0.318 <sup>1</sup> | —   | MHz  |

|                           |                      | (OPA0)BIASPROG=0x4,(OPA0)HALF-<br>BIAS=0x1, DC bias = 0.3 V | _   | 1.595 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA0)BIASPROG=0x4,(OPA0)HALF-<br>BIAS=0x1, DC bias = 1 V   | -   | 2.661 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA0)BIASPROG=0x4,(OPA0)HALF-<br>BIAS=0x1, DC bias = 2 V   | _   | 2.566 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA0)BIASPROG=0x4,(OPA0)HALF-<br>BIAS=0x1, DC bias = 2.7 V | -   | 1.787 <sup>1</sup> | —   | MHz  |

|                           |                      | (OPA1)BIASPROG=0x0,(OPA1)HALF-<br>BIAS=0x1, DC bias = 0.3 V | -   | 0.460 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA1)BIASPROG=0x0,(OPA1)HALF-<br>BIAS=0x1, DC bias = 1 V   | -   | 0.447 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA1)BIASPROG=0x0,(OPA1)HALF-<br>BIAS=0x1, DC bias = 2 V   | -   | 0.372 <sup>1</sup> |     | MHz  |

|                           |                      | (OPA1)BIASPROG=0x0,(OPA1)HALF-<br>BIAS=0x1, DC bias = 2.7 V | _   | 0.295 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA1)BIASPROG=0x4,(OPA1)HALF-<br>BIAS=0x1, DC bias = 0.3 V | _   | 1.890 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA1)BIASPROG=0x4,(OPA1)HALF-<br>BIAS=0x1, DC bias = 1 V   | -   | 2.849 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA1)BIASPROG=0x4,(OPA1)HALF-<br>BIAS=0x1, DC bias = 2 V   | -   | 2.561 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA1)BIASPROG=0x4,(OPA1)HALF-<br>BIAS=0x1, DC bias = 2.7 V | -   | 1.705 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA2)BIASPROG=0x0,(OPA2)HALF-<br>BIAS=0x1, DC bias = 0.3 V | -   | 0.339 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA2)BIASPROG=0x0,(OPA2)HALF-<br>BIAS=0x1, DC bias = 1 V   | -   | 0.432 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA2)BIASPROG=0x0,(OPA2)HALF-<br>BIAS=0x1, DC bias = 2 V   | -   | 0.347 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA2)BIASPROG=0x0,(OPA2)HALF-<br>BIAS=0x1, DC bias = 2.7 V | -   | 0.286 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA2)BIASPROG=0x4,(OPA2)HALF-<br>BIAS=0x1, DC bias = 0.3 V | -   | 1.271 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA2)BIASPROG=0x4,(OPA2)HALF-<br>BIAS=0x1, DC bias = 1 V   | -   | 1.429 <sup>1</sup> | _   | MHz  |

|                           |                      | (OPA2)BIASPROG=0x4,(OPA2)HALF-<br>BIAS=0x1, DC bias = 2 V   | -   | 1.283 <sup>1</sup> | —   | MHz  |

## Table 4.25. I2C Standard-mode (Sm)

| Parameter                                          | Symbol              | Min | Тур | Max                 | Unit |

|----------------------------------------------------|---------------------|-----|-----|---------------------|------|

| SCL clock frequency                                | f <sub>SCL</sub>    | 0   | _   | 100 <sup>1</sup>    | kHz  |

| SCL clock low time                                 | t <sub>LOW</sub>    | 4.7 | _   | —                   | μs   |

| SCL clock high time                                | t <sub>HIGH</sub>   | 4.0 | _   | —                   | μs   |

| SDA set-up time                                    | t <sub>SU,DAT</sub> | 250 | _   | —                   | ns   |

| SDA hold time                                      | t <sub>HD,DAT</sub> | 8   | _   | 3450 <sup>2,3</sup> | ns   |

| Repeated START condition set-up time               | t <sub>SU,STA</sub> | 4.7 | _   | —                   | μs   |

| (Repeated) START condition hold time               | t <sub>HD,STA</sub> | 4.0 | _   | —                   | μs   |

| STOP condition set-up time                         | tsu,sto             | 4.0 | _   | —                   | μs   |

| Bus free time between a STOP and a START condition | t <sub>BUF</sub>    | 4.7 | _   | _                   | μs   |

## Note:

1. For the minimum HFPERCLK frequency required in Standard-mode, see the I2C chapter in the EFM32LG Reference Manual.

2. The maximum SDA hold time ( $t_{HD,DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ).

3. When transmitting data, this number is guaranteed only when I2Cn\_CLKDIV < ((3450\*10<sup>-9</sup> [s] \* f<sub>HFPERCLK</sub> [Hz]) - 4).

## Table 4.26. I2C Fast-mode (Fm)

| Parameter                                          | Symbol              | Min | Тур | Max                | Unit |

|----------------------------------------------------|---------------------|-----|-----|--------------------|------|

| SCL clock frequency                                | f <sub>SCL</sub>    | 0   |     | 400 <sup>1</sup>   | kHz  |

| SCL clock low time                                 | t <sub>LOW</sub>    | 1.3 |     |                    | μs   |

| SCL clock high time                                | t <sub>HIGH</sub>   | 0.6 |     |                    | μs   |

| SDA set-up time                                    | t <sub>SU,DAT</sub> | 100 |     |                    | ns   |

| SDA hold time                                      | t <sub>HD,DAT</sub> | 8   |     | 900 <sup>2,3</sup> | ns   |

| Repeated START condition set-up time               | tsu,sta             | 0.6 |     |                    | μs   |

| (Repeated) START condition hold time               | t <sub>hd,sta</sub> | 0.6 |     |                    | μs   |

| STOP condition set-up time                         | t <sub>SU,STO</sub> | 0.6 |     |                    | μs   |

| Bus free time between a STOP and a START condition | t <sub>BUF</sub>    | 1.3 |     |                    | μs   |

### Note:

1. For the minimum HFPERCLK frequency required in Fast-mode, see the I2C chapter in the EFM32LG Reference Manual.

2. The maximum SDA hold time ( $t_{HD,DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ).

3. When transmitting data, this number is guaranteed only when  $I2Cn_CLKDIV < ((900*10^{-9} [s] * f_{HFPERCLK} [Hz]) - 4)$ .

| Alternate                         | ate LOCATION |      |      |      |     |   |   |                                                                                                 |

|-----------------------------------|--------------|------|------|------|-----|---|---|-------------------------------------------------------------------------------------------------|

| Functionality                     | 0            | 1    | 2    | 3    | 4   | 5 | 6 | Description                                                                                     |

| ADC0_CH7                          | PD7          |      |      |      |     |   |   | Analog to digital converter ADC0, input channel number 7.                                       |

| BOOT_RX                           | PE11         |      |      |      |     |   |   | Bootloader RX.                                                                                  |

| BOOT_TX                           | PE10         |      |      |      |     |   |   | Bootloader TX.                                                                                  |

| BU_VIN                            | PD8          |      |      |      |     |   |   | Battery input for Backup Power Domain                                                           |

| CMU_CLK0                          | PA2          | PC12 | PD7  |      |     |   |   | Clock Management Unit, clock output number 0.                                                   |

| CMU_CLK1                          | PA1          | PD8  | PE12 |      |     |   |   | Clock Management Unit, clock output number 1.                                                   |

| OPAMP_N0                          | PC5          |      |      |      |     |   |   | Operational Amplifier 0 external negative input.                                                |

| OPAMP_N1                          | PD7          |      |      |      |     |   |   | Operational Amplifier 1 external negative input.                                                |

| OPAMP_N2                          | PD3          |      |      |      |     |   |   | Operational Amplifier 2 external negative input.                                                |

| DAC0_OUT0 /<br>OPAMP_OUT0         | PB11         |      |      |      |     |   |   | Digital to Analog Converter DAC0_OUT0 /OPAMP output channel number 0.                           |

| DAC0_OUT0ALT<br>OPAMP_OUT0A<br>LT |              | PC1  | PC2  | PC3  | PD0 |   |   | Digital to Analog Converter DAC0_OUT0ALT /<br>OPAMP alternative output for channel 0.           |

| DAC0_OUT1 /<br>OPAMP_OUT1         | PB12         |      |      |      |     |   |   | Digital to Analog Converter DAC0_OUT1 / OPAMP output channel number 1.                          |

| DAC0_OUT1ALT<br>OPAMP_OUT1A<br>LT | /<br>PC12    | PC13 | PC14 | PC15 | PD1 |   |   | Digital to Analog Converter DAC0_OUT1ALT /<br>OPAMP alternative output for channel 1.           |

| OPAMP_OUT2                        | PD5          | PD0  |      |      |     |   |   | Operational Amplifier 2 output.                                                                 |

| OPAMP_P0                          | PC4          |      |      |      |     |   |   | Operational Amplifier 0 external positive input.                                                |

| OPAMP_P1                          | PD6          |      |      |      |     |   |   | Operational Amplifier 1 external positive input.                                                |

| OPAMP_P2                          | PD4          |      |      |      |     |   |   | Operational Amplifier 2 external positive input.                                                |

|                                   |              |      |      |      |     |   |   | Debug-interface Serial Wire clock input.                                                        |

| DBG_SWCLK                         | PF0          | PF0  | PF0  | PF0  |     |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull down.           |

|                                   |              |      |      |      |     |   |   | Debug-interface Serial Wire data input / output.                                                |

| DBG_SWDIO                         | PF1          | PF1  | PF1  | PF1  |     |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull up.             |

|                                   |              |      |      |      |     |   |   | Debug-interface Serial Wire viewer Output.                                                      |

| DBG_SWO                           | PF2          | PC15 | PD1  | PD2  |     |   |   | Note that this function is not enabled after reset, and must be enabled by software to be used. |

| ETM_TCLK                          | PD7          |      | PC6  | PA6  |     |   |   | Embedded Trace Module ETM clock .                                                               |

| ETM_TD0                           | PD6          |      | PC7  | PA2  |     |   |   | Embedded Trace Module ETM data 0.                                                               |

| ETM_TD1                           | PD3          |      | PD3  | PA3  |     |   |   | Embedded Trace Module ETM data 1.                                                               |

| ETM_TD2                           | PD4          |      | PD4  | PA4  |     |   |   | Embedded Trace Module ETM data 2.                                                               |

| ETM_TD3                           | PD5          | PF3  | PD5  | PA5  |     |   |   | Embedded Trace Module ETM data 3.                                                               |

| GPIO_EM4WU0                       | PA0          |      |      |      |     |   |   | Pin can be used to wake the system up from EM4                                                  |

| GPIO_EM4WU1                       | PA6          |      |      |      |     |   |   | Pin can be used to wake the system up from EM4                                                  |

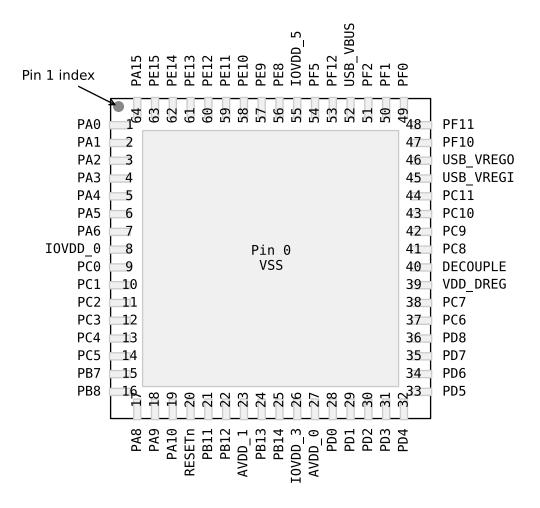

### 5.6 EFM32LG330 (QFN64)

#### 5.6.1 Pinout

The EFM32LG330 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \* ROUTE register in the module in question.

Figure 5.11. EFM32LG330 Pinout (top view, not to scale)

| QFN   | 64 Pin# and Name | Pin Alternate Functionality / Description |                 |                           |                           |  |  |  |

|-------|------------------|-------------------------------------------|-----------------|---------------------------|---------------------------|--|--|--|

| Pin # | Pin Name         | Analog                                    | Timers          | Communication             | Other                     |  |  |  |

| 0     | VSS              | Ground.                                   |                 |                           |                           |  |  |  |

| 1     | PA0              |                                           | TIM0_CC0 #0/1/4 | LEU0_RX #4 I2C0_SDA<br>#0 | PRS_CH0 #0<br>GPIO_EM4WU0 |  |  |  |

| Alternate     |      |      | L    | OCATIO | N |   |   |                                                                           |

|---------------|------|------|------|--------|---|---|---|---------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3      | 4 | 5 | 6 | Description                                                               |

| EBI_A06       | PC7  | PC7  | PC7  |        |   |   |   | External Bus Interface (EBI) address output pin 06.                       |

| EBI_A07       | PE0  | PE0  | PE0  |        |   |   |   | External Bus Interface (EBI) address output pin 07.                       |

| EBI_A08       | PE1  | PE1  | PE1  |        |   |   |   | External Bus Interface (EBI) address output pin 08.                       |

| EBI_A09       | PE2  | PC9  | PC9  |        |   |   |   | External Bus Interface (EBI) address output pin 09.                       |

| EBI_A10       | PE3  | PC10 | PC10 |        |   |   |   | External Bus Interface (EBI) address output pin 10.                       |

| EBI_A11       | PE4  | PE4  | PE4  |        |   |   |   | External Bus Interface (EBI) address output pin 11.                       |

| EBI_A12       | PE5  | PE5  | PE5  |        |   |   |   | External Bus Interface (EBI) address output pin 12.                       |

| EBI_A13       | PE6  | PE6  | PE6  |        |   |   |   | External Bus Interface (EBI) address output pin 13.                       |

| EBI_A14       | PE7  | PE7  | PE7  |        |   |   |   | External Bus Interface (EBI) address output pin 14.                       |

| EBI_A15       | PC8  | PC8  | PC8  |        |   |   |   | External Bus Interface (EBI) address output pin 15.                       |

| EBI_A16       | PB0  | PB0  | PB0  |        |   |   |   | External Bus Interface (EBI) address output pin 16.                       |

| EBI_A17       | PB1  | PB1  | PB1  |        |   |   |   | External Bus Interface (EBI) address output pin 17.                       |

| EBI_A18       | PB2  | PB2  | PB2  |        |   |   |   | External Bus Interface (EBI) address output pin 18.                       |

| EBI_A19       | PB3  | PB3  | PB3  |        |   |   |   | External Bus Interface (EBI) address output pin 19.                       |

| EBI_A20       | PB4  | PB4  | PB4  |        |   |   |   | External Bus Interface (EBI) address output pin 20.                       |

| EBI_A21       | PB5  | PB5  | PB5  |        |   |   |   | External Bus Interface (EBI) address output pin 21.                       |

| EBI_A22       | PB6  | PB6  | PB6  |        |   |   |   | External Bus Interface (EBI) address output pin 22.                       |

| EBI_A23       | PC0  | PC0  | PC0  |        |   |   |   | External Bus Interface (EBI) address output pin 23.                       |

| EBI_A24       | PC1  | PC1  | PC1  |        |   |   |   | External Bus Interface (EBI) address output pin 24.                       |

| EBI_A25       | PC2  | PC2  | PC2  |        |   |   |   | External Bus Interface (EBI) address output pin 25.                       |

| EBI_A26       | PC4  | PC4  | PC4  |        |   |   |   | External Bus Interface (EBI) address output pin 26.                       |

| EBI_A27       | PD2  | PD2  | PD2  |        |   |   |   | External Bus Interface (EBI) address output pin 27.                       |

| EBI_AD00      | PE8  | PE8  | PE8  |        |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 00. |

| EBI_AD01      | PE9  | PE9  | PE9  |        |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 01. |

| EBI_AD02      | PE10 | PE10 | PE10 |        |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 02. |

| EBI_AD03      | PE11 | PE11 | PE11 |        |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 03. |

| EBI_AD04      | PE12 | PE12 | PE12 |        |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 04. |

| EBI_AD05      | PE13 | PE13 | PE13 |        |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 05. |

| EBI_AD06      | PE14 | PE14 | PE14 |        |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 06. |

| EBI_AD07      | PE15 | PE15 | PE15 |        |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 07. |

| EBI_AD08      | PA15 | PA15 | PA15 |        |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 08. |

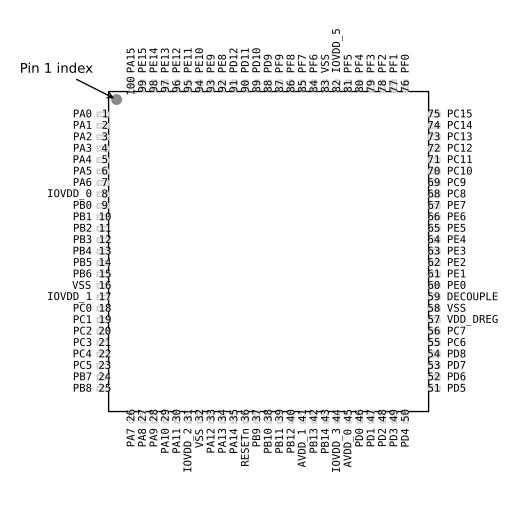

#### 5.14 EFM32LG880 (LQFP100)

#### 5.14.1 Pinout

The EFM32LG880 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.27. EFM32LG880 Pinout (top view, not to scale)

| LQF   | P100 Pin# and<br>Name |           | Pin Altern      | ate Functionality / D | escription                |                           |

|-------|-----------------------|-----------|-----------------|-----------------------|---------------------------|---------------------------|

| Pin # | Pin Name              | Analog    | EBI             | Timers                | Communication             | Other                     |

| 1     | PA0                   | LCD_SEG13 | EBI_AD09 #0/1/2 | TIM0_CC0 #0/1/4       | LEU0_RX #4<br>I2C0_SDA #0 | PRS_CH0 #0<br>GPIO_EM4WU0 |

| 2     | PA1                   | LCD_SEG14 | EBI_AD10 #0/1/2 | TIM0_CC1 #0/1         | 12C0_SCL #0               | CMU_CLK1 #0<br>PRS_CH1 #0 |

| Alternate     | LOCATION |      |      |   |   |   |   |                                                                           |

|---------------|----------|------|------|---|---|---|---|---------------------------------------------------------------------------|

| Functionality | 0        | 1    | 2    | 3 | 4 | 5 | 6 | Description                                                               |

| EBI_AD07      | PE15     | PE15 | PE15 |   |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 07. |

| EBI_AD08      | PA15     | PA15 | PA15 |   |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 08. |

| EBI_AD09      | PA0      | PA0  | PA0  |   |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 09. |

| EBI_AD10      | PA1      | PA1  | PA1  |   |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 10. |

| EBI_AD11      | PA2      | PA2  | PA2  |   |   |   |   | External Bus Interface (EBI) address and data input / output pin 11.      |

| EBI_AD12      | PA3      | PA3  | PA3  |   |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 12. |

| EBI_AD13      | PA4      | PA4  | PA4  |   |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 13. |

| EBI_AD14      | PA5      | PA5  | PA5  |   |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 14. |

| EBI_AD15      | PA6      | PA6  | PA6  |   |   |   |   | External Bus Interface (EBI) address and data in-<br>put / output pin 15. |

| EBI_ALE       |          | PC11 | PC11 |   |   |   |   | External Bus Interface (EBI) Address Latch Enable output.                 |

| EBI_ARDY      | PF2      | PF2  | PF2  |   |   |   |   | External Bus Interface (EBI) Hardware Ready Con-<br>trol input.           |

| EBI_BL0       | PF6      | PF6  | PF6  |   |   |   |   | External Bus Interface (EBI) Byte Lane/Enable pin 0.                      |

| EBI_BL1       | PF7      | PF7  | PF7  |   |   |   |   | External Bus Interface (EBI) Byte Lane/Enable pin 1.                      |

| EBI_CS0       | PD9      | PD9  | PD9  |   |   |   |   | External Bus Interface (EBI) Chip Select output 0.                        |

| EBI_CS1       | PD10     | PD10 | PD10 |   |   |   |   | External Bus Interface (EBI) Chip Select output 1.                        |

| EBI_CS2       | PD11     | PD11 | PD11 |   |   |   |   | External Bus Interface (EBI) Chip Select output 2.                        |

| EBI_CS3       | PD12     | PD12 | PD12 |   |   |   |   | External Bus Interface (EBI) Chip Select output 3.                        |

| EBI_CSTFT     | PA7      | PA7  | PA7  |   |   |   |   | External Bus Interface (EBI) Chip Select output TFT.                      |

| EBI_DCLK      | PA8      | PA8  | PA8  |   |   |   |   | External Bus Interface (EBI) TFT Dot Clock pin.                           |

| EBI_DTEN      | PA9      | PA9  | PA9  |   |   |   |   | External Bus Interface (EBI) TFT Data Enable pin.                         |

| EBI_HSNC      | PA11     | PA11 | PA11 |   |   |   |   | External Bus Interface (EBI) TFT Horizontal Syn-<br>chronization pin.     |

| EBI_NANDREn   | PC3      | PC3  | PC3  |   |   |   |   | External Bus Interface (EBI) NAND Read Enable output.                     |

| EBI_NANDWEn   | PC5      | PC5  | PC5  |   |   |   |   | External Bus Interface (EBI) NAND Write Enable output.                    |

| EBI_REn       | PF5      | PF9  | PF5  |   |   |   |   | External Bus Interface (EBI) Read Enable output.                          |

| EBI_VSNC      | PA10     | PA10 | PA10 |   |   |   |   | External Bus Interface (EBI) TFT Vertical Synchroni-<br>zation pin.       |

| BGA   | A112 Pin# and<br>Name |                                                   | Pin Altern              | ate Functionality / D                            | escription                            |                                           |

|-------|-----------------------|---------------------------------------------------|-------------------------|--------------------------------------------------|---------------------------------------|-------------------------------------------|

| Pin # | Pin Name              | Analog                                            | EBI                     | Timers                                           | Communication                         | Other                                     |

| F2    | PB2                   | LCD_SEG34                                         | EBI_A18 #0/1/2          | TIM1_CC2 #2                                      |                                       |                                           |

| F3    | PB3                   | LCD_SEG20/<br>LCD_COM4                            | EBI_A19 #0/1/2          | PCNT1_S0IN #1                                    | US2_TX #1                             |                                           |

| F4    | PB4                   | LCD_SEG21/<br>LCD_COM5                            | EBI_A20 #0/1/2          | PCNT1_S1IN #1                                    | US2_RX #1                             |                                           |

| F8    | VDD_DREG              | Power supply for on-                              | chip voltage regulator. |                                                  |                                       |                                           |

| F9    | VSS_DREG              | Ground for on-chip vo                             | oltage regulator.       |                                                  |                                       |                                           |

| F10   | PE2                   | BU_VOUT                                           | EBI_A09 #0              | TIM3_CC2 #1                                      | U1_TX #3                              | ACMP0_O #1                                |

| F11   | DECOUPLE              | Decouple output for c pin.                        | on-chip voltage regulat | or. An external capaci                           | tance of size C <sub>DECOU</sub>      | <sub>PLE</sub> is required at this        |

| G1    | PB5                   | LCD_SEG22/<br>LCD_COM6                            | EBI_A21 #0/1/2          |                                                  | US2_CLK #1                            |                                           |

| G2    | PB6                   | LCD_SEG23/<br>LCD_COM7                            | EBI_A22 #0/1/2          |                                                  | US2_CS #1                             |                                           |

| G3    | VSS                   | Ground.                                           |                         |                                                  |                                       |                                           |

| G4    | IOVDD_0               | Digital IO power supp                             | bly 0.                  |                                                  |                                       |                                           |

| G8    | IOVDD_4               | Digital IO power supp                             | bly 4.                  |                                                  |                                       |                                           |

| G9    | VSS                   | Ground.                                           |                         |                                                  |                                       |                                           |

| G10   | PC6                   | ACMP0_CH6                                         | EBI_A05 #0/1/2          |                                                  | LEU1_TX #0<br>I2C0_SDA #2             | LES_CH6 #0<br>ETM_TCLK #2                 |

| G11   | PC7                   | ACMP0_CH7                                         | EBI_A06 #0/1/2          |                                                  | LEU1_RX #0<br>I2C0_SCL #2             | LES_CH7 #0<br>ETM_TD0 #2                  |

| H1    | PC0                   | ACMP0_CH0<br>DAC0_OUT0ALT<br>#0/<br>OPAMP_OUT0ALT | EBI_A23 #0/1/2          | TIM0_CC1 #4<br>PCNT0_S0IN #2                     | US0_TX #5<br>US1_TX #0<br>I2C0_SDA #4 | LES_CH0 #0<br>PRS_CH2 #0                  |

| H2    | PC2                   | ACMP0_CH2<br>DAC0_OUT0ALT<br>#2/<br>OPAMP_OUT0ALT | EBI_A25 #0/1/2          | TIM0_CDTI0 #4                                    | US2_TX #0                             | LES_CH2 #0                                |

| НЗ    | PD14                  |                                                   |                         |                                                  | I2C0_SDA #3                           |                                           |

| H4    | PA7                   | LCD_SEG35                                         | EBI_CSTFT #0/1/2        |                                                  |                                       |                                           |

| H5    | PA8                   | LCD_SEG36                                         | EBI_DCLK #0/1/2         | TIM2_CC0 #0                                      |                                       |                                           |

| H6    | VSS                   | Ground.                                           | 1                       |                                                  | 1                                     |                                           |

| H7    | IOVDD_3               | Digital IO power supp                             | bly 3.                  |                                                  |                                       |                                           |

| H8    | PD8                   | BU_VIN                                            |                         |                                                  |                                       | CMU_CLK1 #1                               |

| Н9    | PD5                   | ADC0_CH5<br>OPAMP_OUT2 #0                         |                         |                                                  | LEU0_RX #0                            | ETM_TD3 #0/2                              |

| H10   | PD6                   | ADC0_CH6<br>OPAMP_P1                              |                         | TIM1_CC0 #4 LE-<br>TIM0_OUT0 #0<br>PCNT0_S0IN #3 | US1_RX #2<br>I2C0_SDA #1              | LES_ALTEX0 #0<br>ACMP0_O #2<br>ETM_TD0 #0 |

| Alternate     | LOCATION |      |     |      | N   |     |      |                                                                                                                                                                          |

|---------------|----------|------|-----|------|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0        | 1    | 2   | 3    | 4   | 5   | 6    | Description                                                                                                                                                              |

| EBI_WEn       | PF4      | PF8  | PF4 |      |     |     |      | External Bus Interface (EBI) Write Enable output.                                                                                                                        |

| ETM_TCLK      | PD7      | PF8  | PC6 | PA6  |     |     |      | Embedded Trace Module ETM clock .                                                                                                                                        |

| ETM_TD0       | PD6      | PF9  | PC7 | PA2  |     |     |      | Embedded Trace Module ETM data 0.                                                                                                                                        |

| ETM_TD1       | PD3      | PD13 | PD3 | PA3  |     |     |      | Embedded Trace Module ETM data 1.                                                                                                                                        |

| ETM_TD2       | PD4      | PB15 | PD4 | PA4  |     |     |      | Embedded Trace Module ETM data 2.                                                                                                                                        |

| ETM_TD3       | PD5      | PF3  | PD5 | PA5  |     |     |      | Embedded Trace Module ETM data 3.                                                                                                                                        |

| GPIO_EM4WU0   | PA0      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU1   | PA6      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU2   | PC9      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU3   | PF1      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU4   | PF2      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU5   | PE13     |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| HFXTAL_N      | PB14     |      |     |      |     |     |      | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                     |

| HFXTAL_P      | PB13     |      |     |      |     |     |      | High Frequency Crystal positive pin.                                                                                                                                     |

| I2C0_SCL      | PA1      | PD7  | PC7 | PD15 | PC1 | PF1 | PE13 | I2C0 Serial Clock Line input / output.                                                                                                                                   |

| I2C0_SDA      | PA0      | PD6  | PC6 | PD14 | PC0 | PF0 | PE12 | I2C0 Serial Data input / output.                                                                                                                                         |

| I2C1_SCL      | PC5      | PB12 | PE1 |      |     |     |      | I2C1 Serial Clock Line input / output.                                                                                                                                   |

| I2C1_SDA      | PC4      | PB11 | PE0 |      |     |     |      | I2C1 Serial Data input / output.                                                                                                                                         |

| LCD_BCAP_N    | PA13     |      |     |      |     |     |      | LCD voltage booster (optional), boost capacitor,<br>negative pin. If using the LCD voltage booster, con-<br>nect a 22 nF capacitor between LCD_BCAP_N and<br>LCD_BCAP_P. |

| LCD_BCAP_P    | PA12     |      |     |      |     |     |      | LCD voltage booster (optional), boost capacitor,<br>positive pin. If using the LCD voltage booster, con-<br>nect a 22 nF capacitor between LCD_BCAP_N and<br>LCD_BCAP_P. |

|               |          |      |     |      |     |     |      | LCD voltage booster (optional), boost output. If us-<br>ing the LCD voltage booster, connect a 1 uF capaci-<br>tor between this pin and VSS.                             |

| LCD_BEXT      | PA14     |      |     |      |     |     |      | An external LCD voltage may also be applied to this pin if the booster is not enabled.                                                                                   |

|               |          |      |     |      |     |     |      | If AVDD is used directly as the LCD supply voltage, this pin may be left unconnected or used as a GPIO.                                                                  |

| LCD_COM0      | PE4      |      |     |      |     |     |      | LCD driver common line number 0.                                                                                                                                         |

| LCD_COM1      | PE5      |      |     |      |     |     |      | LCD driver common line number 1.                                                                                                                                         |

| LCD_COM2      | PE6      |      |     |      |     |     |      | LCD driver common line number 2.                                                                                                                                         |

| LCD_COM3      | PE7      |      |     |      |     |     |      | LCD driver common line number 3.                                                                                                                                         |

| LCD_SEG0      | PF2      |      |     |      |     |     |      | LCD segment line 0. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                     |

| Alternate                       | LOCATION |      |      |      |     |   |   |                                                                                                    |

|---------------------------------|----------|------|------|------|-----|---|---|----------------------------------------------------------------------------------------------------|

| Functionality                   | 0        | 1    | 2    | 3    | 4   | 5 | 6 | Description                                                                                        |

| ADC0_CH7                        | PD7      |      |      |      |     |   |   | Analog to digital converter ADC0, input channel number 7.                                          |

| BOOT_RX                         | PE11     |      |      |      |     |   |   | Bootloader RX.                                                                                     |

| BOOT_TX                         | PE10     |      |      |      |     |   |   | Bootloader TX.                                                                                     |

| BU_STAT                         | PE3      |      |      |      |     |   |   | Backup Power Domain status, whether or not the system is in backup mode                            |

| BU_VIN                          | PD8      |      |      |      |     |   |   | Battery input for Backup Power Domain                                                              |

| BU_VOUT                         | PE2      |      |      |      |     |   |   | Power output for Backup Power Domain                                                               |

| CMU_CLK0                        | PA2      | PC12 | PD7  |      |     |   |   | Clock Management Unit, clock output number 0.                                                      |

| CMU_CLK1                        | PA1      | PD8  | PE12 |      |     |   |   | Clock Management Unit, clock output number 1.                                                      |

| OPAMP_N0                        | PC5      |      |      |      |     |   |   | Operational Amplifier 0 external negative input.                                                   |

| OPAMP_N1                        | PD7      |      |      |      |     |   |   | Operational Amplifier 1 external negative input.                                                   |

| OPAMP_N2                        | PD3      |      |      |      |     |   |   | Operational Amplifier 2 external negative input.                                                   |

| DAC0_OUT0 /<br>OPAMP_OUT0       | PB11     |      |      |      |     |   |   | Digital to Analog Converter DAC0_OUT0 / OPAMP output channel number 0.                             |

| DAC0_OUT0ALT /<br>OPAMP_OUT0ALT | PC0      | PC1  | PC2  | PC3  | PD0 |   |   | Digital to Analog Converter DAC0_OUT0ALT / OPAMP alternative output for channel 0.                 |

| DAC0_OUT1 /<br>OPAMP_OUT1       | PB12     |      |      |      |     |   |   | Digital to Analog Converter DAC0_OUT1 / OPAMP output channel number 1.                             |

| DAC0_OUT1ALT /<br>OPAMP_OUT1ALT | PC12     | PC13 | PC14 | PC15 | PD1 |   |   | Digital to Analog Converter DAC0_OUT1ALT /<br>OPAMP alternative output for channel 1.              |

| OPAMP_OUT2                      | PD5      | PD0  |      |      |     |   |   | Operational Amplifier 2 output.                                                                    |

| OPAMP_P0                        | PC4      |      |      |      |     |   |   | Operational Amplifier 0 external positive input.                                                   |

| OPAMP_P1                        | PD6      |      |      |      |     |   |   | Operational Amplifier 1 external positive input.                                                   |

| OPAMP_P2                        | PD4      |      |      |      |     |   |   | Operational Amplifier 2 external positive input.                                                   |

|                                 |          |      |      |      |     |   |   | Debug-interface Serial Wire clock input.                                                           |

| DBG_SWCLK                       | PF0      | PF0  | PF0  | PF0  |     |   |   | Note that this function is enabled to pin out of re-<br>set, and has a built-in pull down.         |

|                                 |          |      |      |      |     |   |   | Debug-interface Serial Wire data input / output.                                                   |

| DBG_SWDIO                       | PF1      | PF1  | PF1  | PF1  |     |   |   | Note that this function is enabled to pin out of re-<br>set, and has a built-in pull up.           |

|                                 |          |      |      |      |     |   |   | Debug-interface Serial Wire viewer Output.                                                         |

| DBG_SWO                         | PF2      | PC15 | PD1  | PD2  |     |   |   | Note that this function is not enabled after reset,<br>and must be enabled by software to be used. |

| EBI_A00                         | PA12     | PA12 | PA12 |      |     |   |   | External Bus Interface (EBI) address output pin 00.                                                |

| EBI_A01                         | PA13     | PA13 | PA13 |      |     |   |   | External Bus Interface (EBI) address output pin 01.                                                |

| EBI_A02                         | PA14     | PA14 | PA14 |      |     |   |   | External Bus Interface (EBI) address output pin 02.                                                |

| EBI_A03                         | PB9      | PB9  | PB9  |      |     |   |   | External Bus Interface (EBI) address output pin 03.                                                |

| EBI_A04                         | PB10     | PB10 | PB10 |      |     |   |   | External Bus Interface (EBI) address output pin 04.                                                |

| EBI_A05                         | PC6      | PC6  | PC6  |      |     |   |   | External Bus Interface (EBI) address output pin 05.                                                |

| Alternate     | LOCATION |      |     |      |     |     |      |                                                                                                                                                                          |

|---------------|----------|------|-----|------|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0        | 1    | 2   | 3    | 4   | 5   | 6    | Description                                                                                                                                                              |

| ETM_TD2       | PD4      | PB15 | PD4 | PA4  |     |     |      | Embedded Trace Module ETM data 2.                                                                                                                                        |

| ETM_TD3       | PD5      | PF3  | PD5 | PA5  |     |     |      | Embedded Trace Module ETM data 3.                                                                                                                                        |

| GPIO_EM4WU0   | PA0      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU1   | PA6      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU2   | PC9      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU3   | PF1      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU4   | PF2      |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| GPIO_EM4WU5   | PE13     |      |     |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                           |

| HFXTAL_N      | PB14     |      |     |      |     |     |      | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                     |

| HFXTAL_P      | PB13     |      |     |      |     |     |      | High Frequency Crystal positive pin.                                                                                                                                     |

| I2C0_SCL      | PA1      | PD7  | PC7 | PD15 | PC1 | PF1 | PE13 | I2C0 Serial Clock Line input / output.                                                                                                                                   |

| I2C0_SDA      | PA0      | PD6  | PC6 | PD14 | PC0 | PF0 | PE12 | I2C0 Serial Data input / output.                                                                                                                                         |

| I2C1_SCL      | PC5      | PB12 | PE1 |      |     |     |      | I2C1 Serial Clock Line input / output.                                                                                                                                   |

| I2C1_SDA      | PC4      | PB11 | PE0 |      |     |     |      | I2C1 Serial Data input / output.                                                                                                                                         |

| LCD_BCAP_N    | PA13     |      |     |      |     |     |      | LCD voltage booster (optional), boost capacitor,<br>negative pin. If using the LCD voltage booster,<br>connect a 22 nF capacitor between LCD_BCAP_N<br>and LCD_BCAP_P.   |

| LCD_BCAP_P    | PA12     |      |     |      |     |     |      | LCD voltage booster (optional), boost capacitor,<br>positive pin. If using the LCD voltage booster, con-<br>nect a 22 nF capacitor between LCD_BCAP_N<br>and LCD_BCAP_P. |

|               |          |      |     |      |     |     |      | LCD voltage booster (optional), boost output. If us-<br>ing the LCD voltage booster, connect a 1 uF ca-<br>pacitor between this pin and VSS.                             |

| LCD_BEXT      | PA14     |      |     |      |     |     |      | An external LCD voltage may also be applied to this pin if the booster is not enabled.                                                                                   |

|               |          |      |     |      |     |     |      | If AVDD is used directly as the LCD supply volt-<br>age, this pin may be left unconnected or used as a<br>GPIO.                                                          |

| LCD_COM0      | PE4      |      |     |      |     |     |      | LCD driver common line number 0.                                                                                                                                         |

| LCD_COM1      | PE5      |      |     |      |     |     |      | LCD driver common line number 1.                                                                                                                                         |

| LCD_COM2      | PE6      |      |     |      |     |     |      | LCD driver common line number 2.                                                                                                                                         |

| LCD_COM3      | PE7      |      |     |      |     |     |      | LCD driver common line number 3.                                                                                                                                         |

| LCD_SEG0      | PF2      |      |     |      |     |     |      | LCD segment line 0. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                     |

| LCD_SEG1      | PF3      |      |     |      |     |     |      | LCD segment line 1. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                     |

| LCD_SEG2      | PF4      |      |     |      |     |     |      | LCD segment line 2. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                     |

| LCD_SEG3      | PF5      |      |     |      |     |     |      | LCD segment line 3. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                     |

| QFP6  | 4 Pin# and Name |                                                                | Pin Alternate Funct                              | tionality / Description              |                                                           |

|-------|-----------------|----------------------------------------------------------------|--------------------------------------------------|--------------------------------------|-----------------------------------------------------------|

| Pin # | Pin Name        | Analog                                                         | Timers                                           | Communication                        | Other                                                     |

| 28    | PD0             | ADC0_CH0<br>DAC0_OUT0ALT #4/<br>OPAMP_OUT0ALT<br>OPAMP_OUT2 #1 | PCNT2_S0IN #0                                    | US1_TX #1                            |                                                           |

| 29    | PD1             | ADC0_CH1<br>DAC0_OUT1ALT #4/<br>OPAMP_OUT1ALT                  | TIM0_CC0 #3<br>PCNT2_S1IN #0                     | US1_RX #1                            | DBG_SWO #2                                                |

| 30    | PD2             | ADC0_CH2                                                       | TIM0_CC1 #3                                      | USB_DMPU #0<br>US1_CLK #1            | DBG_SWO #3                                                |

| 31    | PD3             | ADC0_CH3 OPAMP_N2                                              | TIM0_CC2 #3                                      | US1_CS #1                            | ETM_TD1 #0/2                                              |

| 32    | PD4             | ADC0_CH4 OPAMP_P2                                              |                                                  | LEU0_TX #0                           | ETM_TD2 #0/2                                              |

| 33    | PD5             | ADC0_CH5<br>OPAMP_OUT2 #0                                      |                                                  | LEU0_RX #0                           | ETM_TD3 #0/2                                              |

| 34    | PD6             | ADC0_CH6 OPAMP_P1                                              | TIM1_CC0 #4 LE-<br>TIM0_OUT0 #0<br>PCNT0_S0IN #3 | US1_RX #2 I2C0_SDA<br>#1             | LES_ALTEX0 #0<br>ACMP0_O #2<br>ETM_TD0 #0                 |

| 35    | PD7             | ADC0_CH7 OPAMP_N1                                              | TIM1_CC1 #4 LE-<br>TIM0_OUT1 #0<br>PCNT0_S1IN #3 | US1_TX #2 I2C0_SCL<br>#1             | CMU_CLK0 #2<br>LES_ALTEX1 #0<br>ACMP1_O #2<br>ETM_TCLK #0 |

| 36    | PD8             | BU_VIN                                                         |                                                  |                                      | CMU_CLK1 #1                                               |

| 37    | PC6             | ACMP0_CH6                                                      |                                                  | LEU1_TX #0 I2C0_SDA<br>#2            | LES_CH6 #0<br>ETM_TCLK #2                                 |

| 38    | PC7             | ACMP0_CH7                                                      |                                                  | LEU1_RX #0 I2C0_SCL<br>#2            | LES_CH7 #0 ETM_TD0<br>#2                                  |

| 39    | VDD_DREG        | Power supply for on-chip                                       | oltage regulator.                                |                                      |                                                           |

| 40    | DECOUPLE        | Decouple output for on-ch at this pin.                         | ip voltage regulator. An e                       | external capacitance of size         | C <sub>DECOUPLE</sub> is required                         |

| 41    | PE4             | LCD_COM0                                                       |                                                  | US0_CS #1                            |                                                           |

| 42    | PE5             | LCD_COM1                                                       |                                                  | US0_CLK #1                           |                                                           |

| 43    | PE6             | LCD_COM2                                                       |                                                  | US0_RX #1                            |                                                           |

| 44    | PE7             | LCD_COM3                                                       |                                                  | US0_TX #1                            |                                                           |

| 45    | USB_VREGI       |                                                                |                                                  |                                      |                                                           |

| 46    | USB_VREGO       |                                                                |                                                  |                                      |                                                           |

| 47    | PF10            |                                                                |                                                  | USB_DM                               |                                                           |

| 48    | PF11            |                                                                |                                                  | USB_DP                               |                                                           |

| 49    | PF0             |                                                                | TIM0_CC0 #5 LE-<br>TIM0_OUT0 #2                  | US1_CLK #2 LEU0_TX<br>#3 I2C0_SDA #5 | DBG_SWCLK #0/1/2/3                                        |

| 50    | PF1             |                                                                | TIM0_CC1 #5 LE-<br>TIM0_OUT1 #2                  | US1_CS #2 LEU0_RX<br>#3 I2C0_SCL #5  | DBG_SWDIO #0/1/2/3<br>GPIO_EM4WU3                         |

| 51    | PF2             | LCD_SEG0                                                       | TIM0_CC2 #5                                      | LEU0_TX #4                           | ACMP1_O #0<br>DBG_SWO #0<br>GPIO_EM4WU4                   |

| 52    | USB_VBUS        | USB 5.0 V VBUS input.                                          |                                                  | 1                                    | 1                                                         |

| Alternate              |      |      |      |     | ON  |   |   |                                                                                                                         |

|------------------------|------|------|------|-----|-----|---|---|-------------------------------------------------------------------------------------------------------------------------|

| Functionality          | 0    | 1    | 2    | 3   | 4   | 5 | 6 | Description                                                                                                             |

| LCD_SEG18              | PA5  |      |      |     |     |   |   | LCD segment line 18. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                               |

| LCD_SEG20/<br>LCD_COM4 | PB3  |      |      |     |     |   |   | LCD segment line 20. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 4   |

| LCD_SEG21/<br>LCD_COM5 | PB4  |      |      |     |     |   |   | LCD segment line 21. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 5   |

| LCD_SEG22/<br>LCD_COM6 | PB5  |      |      |     |     |   |   | LCD segment line 22. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 6   |

| LCD_SEG23/<br>LCD_COM7 | PB6  |      |      |     |     |   |   | LCD segment line 23. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 7   |

| LES_ALTEX0             | PD6  |      |      |     |     |   |   | LESENSE alternate exite output 0.                                                                                       |

| LES_ALTEX1             | PD7  |      |      |     |     |   |   | LESENSE alternate exite output 1.                                                                                       |

| LES_ALTEX2             | PA3  |      |      |     |     |   |   | LESENSE alternate exite output 2.                                                                                       |

| LES_ALTEX3             | PA4  |      |      |     |     |   |   | LESENSE alternate exite output 3.                                                                                       |

| LES_ALTEX4             | PA5  |      |      |     |     |   |   | LESENSE alternate exite output 4.                                                                                       |

| LES_ALTEX5             | PE11 |      |      |     |     |   |   | LESENSE alternate exite output 5.                                                                                       |

| LES_ALTEX6             | PE12 |      |      |     |     |   |   | LESENSE alternate exite output 6.                                                                                       |

| LES_ALTEX7             | PE13 |      |      |     |     |   |   | LESENSE alternate exite output 7.                                                                                       |

| LES_CH4                | PC4  |      |      |     |     |   |   | LESENSE channel 4.                                                                                                      |

| LES_CH5                | PC5  |      |      |     |     |   |   | LESENSE channel 5.                                                                                                      |

| LES_CH6                | PC6  |      |      |     |     |   |   | LESENSE channel 6.                                                                                                      |

| LES_CH7                | PC7  |      |      |     |     |   |   | LESENSE channel 7.                                                                                                      |

| LETIM0_OUT0            | PD6  | PB11 | PF0  | PC4 |     |   |   | Low Energy Timer LETIM0, output channel 0.                                                                              |

| LETIM0_OUT1            | PD7  |      | PF1  | PC5 |     |   |   | Low Energy Timer LETIM0, output channel 1.                                                                              |

| LEU0_RX                | PD5  | PB14 | PE15 | PF1 | PA0 |   |   | LEUART0 Receive input.                                                                                                  |

| LEU0_TX                | PD4  | PB13 | PE14 | PF0 | PF2 |   |   | LEUART0 Transmit output. Also used as receive in-<br>put in half duplex communication.                                  |

| LEU1_RX                | PC7  |      |      |     |     |   |   | LEUART1 Receive input.                                                                                                  |

| LEU1_TX                | PC6  | PA5  |      |     |     |   |   | LEUART1 Transmit output. Also used as receive in-<br>put in half duplex communication.                                  |

| LFXTAL_N               | PB8  |      |      |     |     |   |   | Low Frequency Crystal (typically 32.768 kHz) nega-<br>tive pin. Also used as an optional external clock in-<br>put pin. |

| LFXTAL_P               | PB7  |      |      |     |     |   |   | Low Frequency Crystal (typically 32.768 kHz) posi-<br>tive pin.                                                         |

| PCNT0_S0IN             |      |      |      | PD6 |     |   |   | Pulse Counter PCNT0 input number 0.                                                                                     |

| PCNT0_S1IN             |      |      |      | PD7 |     |   |   | Pulse Counter PCNT0 input number 1.                                                                                     |

| PCNT1_S0IN             | PC4  | PB3  |      |     |     |   |   | Pulse Counter PCNT1 input number 0.                                                                                     |

| Alternate     | Iternate LOCATION |     |     |   |   |   |   |                                                                                            |

|---------------|-------------------|-----|-----|---|---|---|---|--------------------------------------------------------------------------------------------|

| Functionality | 0                 | 1   | 2   | 3 | 4 | 5 | 6 | Description                                                                                |

| US1_TX        |                   | PD0 | PD7 |   |   |   |   | USART1 Asynchronous Transmit.Also used as re-<br>ceive input in half duplex communication. |

|               |                   |     |     |   |   |   |   | USART1 Synchronous mode Master Output / Slave Input (MOSI).                                |

| US2_CLK       | PC4               | PB5 |     |   |   |   |   | USART2 clock input / output.                                                               |

| US2_CS        | PC5               | PB6 |     |   |   |   |   | USART2 chip select input / output.                                                         |

|               |                   |     |     |   |   |   |   | USART2 Asynchronous Receive.                                                               |

| US2_RX        |                   | PB4 |     |   |   |   |   | USART2 Synchronous mode Master Input / Slave<br>Output (MISO).                             |

| US2 TX        |                   | PB3 |     |   |   |   |   | USART2 Asynchronous Transmit.Also used as re-<br>ceive input in half duplex communication. |

| 052_1X        |                   | PBJ |     |   |   |   |   | USART2 Synchronous mode Master Output / Slave Input (MOSI).                                |

| USB_DM        | PF10              |     |     |   |   |   |   | USB D- pin.                                                                                |

| USB_DMPU      | PD2               |     |     |   |   |   |   | USB D- Pullup control.                                                                     |

| USB_DP        | PF11              |     |     |   |   |   |   | USB D+ pin.                                                                                |

| USB_ID        | PF12              |     |     |   |   |   |   | USB ID pin. Used in OTG mode.                                                              |

| USB_VBUS      | USB_V<br>BUS      |     |     |   |   |   |   | USB 5 V VBUS input.                                                                        |

| USB_VBUSEN    | PF5               |     |     |   |   |   |   | USB 5 V VBUS enable.                                                                       |

| USB_VREGI     | USB_V<br>REGI     |     |     |   |   |   |   | USB Input to internal 3.3 V regulator                                                      |

| USB_VREGO     | USB_V<br>REGO     |     |     |   |   |   |   | USB Decoupling for internal 3.3 V USB regulator and regulator output                       |

## 5.19.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32LG942 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

## Table 5.57. GPIO Pinout

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | _         | PA14      | PA13      | PA12      | —         | _         | _     | _     | _     | _     | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| Port B | _         | PB14      | PB13      | _         | PB11      | —         | —     | PB8   | PB7   | PB6   | PB5   | PB4   | PB3   | —     | —     | —     |

| Port C | _         | —         | —         | _         | —         | —         | —     | —     | PC7   | PC6   | PC5   | PC4   | —     | _     | —     | —     |

| Port D | _         | —         | _         | _         | —         | _         | _     | PD8   | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9   | PE8   | PE7   | PE6   | PE5   | PE4   | _     | _     | _     | _     |

| Port F | _         | —         | _         | PF12      | PF11      | PF10      | _     | _     | _     | _     | PF5   | _     | _     | PF2   | PF1   | PF0   |